### A Probabilistic Approach for the System-Level Design of Multi-ASIP Platforms

Micconi, Laura

Publication date: 2015

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Micconi, L. (2015). *A Probabilistic Approach for the System-Level Design of Multi-ASIP Platforms*. Technical University of Denmark. DTU Compute PHD-2014 No. 347

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### A Probabilistic Approach for the System-Level Design of Multi-ASIP Platforms

Laura Micconi

Kongens Lyngby 2014 PhD-2014-347

Technical University of Denmark Department of Applied Mathematics and Computer Science Building 324, DK-2800 Kongens Lyngby, Denmark Phone +45 45253031 compute@compute.dtu.dk www.compute.dtu.dk PhD-2014-347

# Summary (English)

Application Specific Instruction-set Processors (ASIPs) offer a good trade off between performance and flexibility when compared to general purpose processors or ASICs. Additionally, multiple ASIPs can be included in a single platform and they allow the generation of customized heterogeneous MPSoC with a relatively short time-to-market. While there are several commercial tools for the design of a single ASIP, there is still a lack of automation in the design of multi-ASIP platforms.

In this thesis we consider multi-ASIP platforms for real-time applications. Each ASIP is designed to run a specific group of tasks that we identifies as a *task cluster*. With real-time applications, to decide how the tasks should be clustered, we perform a schedulability analysis of the system to verify if the deadlines of the applications can be met. However, to run a schedulability analysis, we need to know the WCET of each task that is available only after an ASIP is designed. Therefore, there is a circular dependency between the definition of the task clusters and the impossibility of defining them without knowing the WCET of the tasks as the ASIPs have not been defined yet.

Many approaches available in the literature break this circular dependency considering pre-defined task clusters or considering a small set of micro-architecture configurations for each ASIP. We propose an alternative approach that uses a probabilistic model to consider the design space of all possible micro-architecture configurations. We introduce a system-level Design Space Exploration (DSE) for the very early phases of the design that automatizes part of the multi-ASIP design flow. Our DSE is responsible for assigning the tasks to the different ASIPs exploring different platform alternatives. We perform a schedulability analysis for each solution to determine which one has the highest chances of meeting the deadlines of the applications and that should be considered in the next stages of the multi-ASIP design flow. <u>ii</u>\_\_\_\_\_

# Summary (Danish)

Applikations specifikke instruktionssæt processorer (ASIPs) tilbyder en god afvejning mellem ydeevne og fleksibilitet i forhold til generelle processorer og dedikerede hardware acceleratorer (ASICs). Flere ASIPs kan inkluderes i en enkelt platform, hvilket tillader realisering af applikations tilpassede heterogen multiprocessor systemer med en relativ kort time-to-market. Mens der er flere kommercielle værktøjer til design og konfigurering af en enkelt ASIP, er der stadig mangel påautomatiseret design af multi-ASIP platforme. Denne afhandling fokuserer påmulti-ASIP platforme til realtids applikationer. Hver ASIP er designet til at køre en specifik gruppe af opgaver. For at afgøre hvordan de enkelte opgaver i realtids applikationen skal fordeles påde forskellige ASIPs, udføres en schedulerbarheds analyse af systemet for at kontrollere, at tidsfristerne kan imødekommes. Men for at kunne køre en schedulerbarheds analyse, er det nødvendigt til at kende den øvre grænse for de enkelte opgavers eksekveringstid (WCET), efter at ASIP'en er konstrueret. Derfor er der en cirkulær afhængighed mellem identifikationen af grupper af opgaver for den enkelte ASIP, som kun kan foretages når WCET kendes, dvs. når ASIP'en er fuldt konfigureret, og det faktum at den korrekte konfigurering først kan bestemmes når der vides hvilke opgaver der skal afvikles påASIP'en.

Eksisterende metoder bryde denne cirkulær afhængighed ved at bruge foruddefinerede grupper af opgaver eller ved kun at betragte et lille sæt af de mulige ASIP konfigureringer. Denne afhandling foreslår en alternativ tilgang, der bruger en probabilistisk model til at repræsentere alle mulige ASIP konfigurationer. Det gør det muligt at automatisere metoden til udforskning af løsningsrummet for en multi-ASIP løsning i de meget tidlige faser af designprocessen. Metoden udforsker forskellige alternative multi-ASIP platforme, ved gennem en statistisk analyse at finde den tildeling af opgaver til de enkelte ASIPs, der giver den højeste sandsynlighed for at opnåen løsning der lever op til kravene, efter en fuld implementering er gennemført.

iv

### Preface

This thesis was prepared at the Department of Applied Mathematics and Computer Science at the Technical University of Denmark in fulfillment of the requirements of the Ph.D. program. The Ph.D. program was partially funded by ASAM, a project in the framework of the European ARTEMIS Research Program and ARTEMIS Joint Undertaking.

This work was supervised by Professor Jan Madsen and Associate Professor Paul Pop and conducted occasionally in collaboration with Dr. Deepak Gangadharan.

The thesis describes a system-level design space exploration for the design of multi-ASIP platforms, i.e. MPSoC that contains multiple Application-Specific Instruction set Processors. The approach described is based on a probabilistic performance model that finds its application in the very early phases of the multi-ASIP design flow. The thesis consists of nine chapters (including Introduction and Conclusion) and two appendices.

The thesis does not contain any material that has been accepted for the award of any other degree or diploma in my name, in any university or other institution and, to the best of my knowledge does not contain any material previously published by another person, except where due reference is made in the text of the thesis.

Part of the experimental evaluation presented in this thesis has been done using Silicon Hive (now Intel Benelux B.V.) technology and tools. The results obtained using Intel's tools should not be used in any way as a reference to evaluate Intel technology or to compare Intel's tools with other commercial or research tools, as only a subset of the functionalities and optimization offered by the tools has been used and/or made available under our University license agreement.

Lyngby, July 2014

Laura Micconi

doens Miccaei

# Publications and technical reports

#### **Peer reviewed publications**

- Jozwiak, L.; Lindwer, M.; Corvino, R.; Meloni, P.; Micconi, L.; Madsen, J.; Diken, E.; Gangadharan, D.; Jordans, R.; Pomata, S.; Pop, P.; Tuveri, G.; Raffo, L. and Notarangelo, G.: "ASAM: Automatic architecture synthesis and application mapping". In Microprocessors and Microsystems, Volume 37, Issue 8, Part C, November 2013, Pages 1002-1019.

- Gangadharan, D.; Micconi, L.; Pop, P. and Madsen, J.: "Multi-ASIP Platform Synthesis for Event-Triggered Applications with Cost/Performance Trade-offs". In IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, Taipei, Taiwan, 2013.

- Micconi, L.; Gangadharan, D.; Pop, P. and Madsen, J.: "Multi-ASIP Platform Synthesis for Real-Time Applications". In Proceedings of SIES 2013 - 8th IEEE International Symposium on Industrial Embedded Systems, Porto, Portugal, June 2013.

- Micconi, L.; Corvino, R.; Gangadharan, D.; Madsen, J.; Pop, P. and Jóźwiak, L.: "Hierarchical DSE for multi-ASIP platforms". In ECyPS 2013 - EUROMI-CRO/IEEE Workshop on Embedded and Cyber-Physical Systems, pages 50-53, Budva, Montenegro, 2013 [Received best student paper award].

- 5. Jóźwiak, L.; Lindwer, M.; Corvino, R.; Meloni, P.; Micconi, L.; Madsen, J.; Diken, E.; Gangadharan, D.; Jordans, R.; Pomata, S.; Pop, P.; Tuveri, G. and

Raffo, L.: "ASAM: Automatic Architecture Synthesis and Application Mapping". In Proceedings of DSD 2012 - 15th Euromicro Conference on Digital System Design, pages 216-225, Cesme, Izmir, Turkey, 2012.

### Miscellaneous

**Micconi, L.**: "Multi-ASIP Platform Synthesis for Real-Time Applications". Student research abstract (SRC) competition at SAC 2013 – 28th Symposium on Applied Computing. Coimbra, Portugal, March 2013 [1st price winner].

#### **Technical reports**

- Micconi, L.; Gangadharan, D.; Madsen, J. and Pop, P.: "Demonstrator of DSE tool". Deliverable 2.7, ASAM Project, November 2013. [Set of videos, Public]

- Micconi, L.; Gangadharan, D.; Madsen, J. and Pop, P.: "Prototype tools for design space exploration". Deliverable 2.6, ASAM Project, January 2013. [Restricted]

- Micconi, L.; Boesen, M. R.; Gangadharan, D.; Madsen, J. and Pop, P.: "Prototype tools for system analysis". Deliverable 2.5, ASAM Project, April 2012. [*Restricted*]

- 4. Micconi, L.; Madsen, J. and Boesen, M. R.: "Method of and report on system analysis". Deliverable 2.3, ASAM Project, November, 2011. [Public]

- Micconi, L.; Madsen, J.; Pop, P.; Kienhuis, B.; Corvino, R. and Jóźwiak, L.: "Report on initial version of the hierarchical application model". Deliverable 2.2, ASAM Project, May, 2011. [*Public*]

- Micconi, L.; Iordache, G.; Madsen, J.; Pop, P.; Meloni, P.; Lindwer, M.; Cocco, M.; Notarangelo, G. and Guidetti, E.: "Initial version of generic platform model". Deliverable 2.1, ASAM Project, January, 2011. [Public]

### **Under review**

**Micconi, L.**; Madsen, J. and Pop, P.: "An Uncertainty Model for System-Level design of Multi-ASIP Platforms". Under review at *Integration, the VLSI Journal*, Special Issue On Application and Domain-Specific Computing.

# Acknowledgements

I would like to express my special appreciation to my advisors Professor Jan Madsen and Associate Professor Paul Pop. A special thank to Jan for his precious suggestions, guidance and support when needed; he is always thinking ahead and every discussion with him has been very enlightening and stimulating. I would like to thank Paul that has helped me with a methodic and disciplined critical thinking. He has contributed in improving the formulation of the ideas and his scrutiny of my technical writing has been invaluable. Without Jan's and Paul's supervision and constant help this dissertation would have not been possible.

Moreover, my gratitude goes to Dr. Deepak Gangadharan that with helpful comments and guidance has taught me how to approach and investigate a research problem.

I would also like to thank my committee members, Professor Jens Sparsø, Professor Ingo Sander and Professor Andrew David Pimentel for reviewing the thesis and providing invaluable comments and suggestions during the defense.

My appreciation goes to all the partners of the ASAM project; it has been extremely stimulating and motivating to work with them. I learned a lot from all of them, especially from Dr. Rosilde Corvino. I will always remember our Skype meeting for discussing the project; Rosilde has always been available with suggestions and comments and has been there when a good laugh was needed in the critical phases of the project. I would like to thanks also Dr. Menno Lindwer that supervised and guided me during the external stay period at Intel Benelux, I will never forget those months in which I had an insight of the industrial world in a stimulating and innovative environment such as Intel.

A giant thank to my colleagues from embedded system engineering (ESE) group at DTU, especially Alessio, Alex, Aske, Davide, Domi, Eduardo, Fontas, George, Massimo (with Valette), Sahar, Valia and Wolfgang. I will always have good memories of the lunches and of the breaks with the coffee-crew and the best coffee of whole DTU. My time at DTU has been great especially thanks to them. I need to thank Alessio, Alex, Domi and Sahar also for reviewing part of the thesis and for their precious feedback. I will miss the great fun I had while biking with Alessio and during the tango classes with Valia. A big thank to Karin, she has always been very kind, willing to help and answer all my questions. Thanks to her I always felt very welcomed in the ESE group. Thanks also to Giovanni, Gosia and Paolo; I have great memories with them: I love their company and the dinners at their place.

My immense appreciation and thanks go to German, Letizia and Eduard. German has always been there for me, he has been my reference point before, during and after the PhD studies; he has given me precious suggestions and guidance and he has also offered me affection and a sincere friendship; I have always felt loved, I really learned a lot from him. Bella Leti has been the person that cheered me up when needed. I feel so lucky that I met her at the beginning of my PhD studies; she is the most generous, understanding and fun friend that someone can hope for. I love each one of our conversations and Skype-vinate. Eduard has been my main reference point during the external stay period, I loved cooking and chatting with him, he has been my happy thought in Eindhoven.

Finally, but not least, I want to thank my pillars of strength during these years: my parents. They have always given me constant support through the ups and downs of my academic career and they have always been there for me when needed, I have never felt alone. I cannot imagine being the person I am today without such a great mum and dad. And a giant thank to my grandma that has supported me even if this means living far away from home.

Thanks to everyone that helped me get to this day.

xi

### Contents

| St               | ımma    | ry (English)                                          | i   |  |

|------------------|---------|-------------------------------------------------------|-----|--|

| Summary (Danish) |         |                                                       |     |  |

| Pr               | Preface |                                                       |     |  |

| Pı               | ıblica  | tions and technical reports                           | vii |  |

| A                | cknow   | vledgements                                           | ix  |  |

| A                | bbrev   | iations                                               | XXV |  |

| 1                | Intr    | oduction                                              | 1   |  |

|                  | 1.1     | Why ASIPs?                                            | 2   |  |

|                  |         | 1.1.1 Application-specific instruction set processors | 2   |  |

|                  |         | 1.1.2 ASIP design                                     | 3   |  |

|                  | 1.2     | Why a multi-ASIP platform?                            | 5   |  |

|                  | 1.3     | Challenges in multi-ASIP design                       | 6   |  |

|                  | 1.4     | Related work                                          | 9   |  |

|                  | 1.5     | Objective                                             | 12  |  |

|                  | 1.6     | Contributions                                         | 13  |  |

|                  | 1.7     | Thesis outline                                        | 14  |  |

|                  | 1.8     | Notes for the reader                                  | 15  |  |

| 2                | Syst    | em models                                             | 17  |  |

|                  | 2.1     | Application Model                                     | 18  |  |

|                  | 2.2     | Platform Model                                        | 19  |  |

|                  | 2.3     | Modeling WCET uncertainties                           | 21  |  |

|                  |         | 2.3.1 Validation of the normal distribution for UM    | 24  |  |

|   | 2.4                      | Summary                                                                                                                                                                                                                                                                      | 34                                                        |

|---|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 3 | Mac<br>3.1<br>3.2<br>3.3 | cro-architecture level DSEMotivational ExampleProblem FormulationPlatform Definition using an Evolutionary Approach3.3.1Schedulability Analysis3.3.2Comparison of task clustering solutions3.3.3Evolutionary Algorithm3.3.4Example of schedulability analysis with UMSummary | <b>35</b><br>35<br>36<br>38<br>38<br>43<br>43<br>44<br>47 |

|   |                          | •                                                                                                                                                                                                                                                                            |                                                           |

| 4 | -                        | erimental evaluation with Task Graph model                                                                                                                                                                                                                                   | <b>49</b>                                                 |

|   | 4.1                      | Comparison of DSE with UM and SFM                                                                                                                                                                                                                                            | 49<br>52                                                  |

|   | 4.2                      | Experimental evaluation of DSE with UM using SH tools                                                                                                                                                                                                                        | 52                                                        |

|   | 4.2                      | 4.2.1 Additional considerations                                                                                                                                                                                                                                              | 59                                                        |

|   | 4.3                      | Accuracy of $C_j^l$ and $C_j^u$                                                                                                                                                                                                                                              | 59                                                        |

|   | 4.4                      | Summary                                                                                                                                                                                                                                                                      | 62                                                        |

| 5 | Unc                      | ertainty model with SDFG                                                                                                                                                                                                                                                     | 65                                                        |

|   | 5.1                      | Application model                                                                                                                                                                                                                                                            | 66                                                        |

|   | 5.2                      | Schedulability Analysis                                                                                                                                                                                                                                                      | 67                                                        |

|   |                          | 5.2.1 Example of Task-level Analysis                                                                                                                                                                                                                                         | 68                                                        |

|   |                          | 5.2.2 Example of Pipeline Analysis                                                                                                                                                                                                                                           | 71                                                        |

|   |                          | 5.2.3 Algorithms for schedulability analysis                                                                                                                                                                                                                                 | 71                                                        |

|   | 5.3                      | Comparison of clustering solutions and DSE                                                                                                                                                                                                                                   | 73                                                        |

|   | 5.4                      | Summary                                                                                                                                                                                                                                                                      | 75                                                        |

| 6 | Exp                      | erimental evaluation with the SDFG model                                                                                                                                                                                                                                     | 77                                                        |

|   | 6.1                      | Case study: MJPEG encoder                                                                                                                                                                                                                                                    | 78                                                        |

|   | 6.2                      | Case studies: ECG and SC                                                                                                                                                                                                                                                     | 84                                                        |

|   | 6.3                      | Comparison of SDFG and task graph application models                                                                                                                                                                                                                         | 85                                                        |

|   | 6.4                      | Accuracy of $C_i^l$ and $C_i^u$                                                                                                                                                                                                                                              | 89                                                        |

|   | 6.5                      | Additional discussion of the results                                                                                                                                                                                                                                         | 90                                                        |

|   | 6.6                      | Experimental evaluation with a NoC                                                                                                                                                                                                                                           | 91                                                        |

|   |                          | 6.6.1 Network model                                                                                                                                                                                                                                                          | 93                                                        |

|   |                          | 6.6.2 Schedulability analysis                                                                                                                                                                                                                                                | 94                                                        |

|   |                          | 6.6.3 Results                                                                                                                                                                                                                                                                | 95                                                        |

|   | 6.7                      | Summary                                                                                                                                                                                                                                                                      | 97                                                        |

| 7 |                          | Manajaat                                                                                                                                                                                                                                                                     | 99                                                        |

| 7 |                          | AM project                                                                                                                                                                                                                                                                   |                                                           |

|   | 7.1                      | ASAM design flow                                                                                                                                                                                                                                                             | 100                                                       |

|   | 7.2                      | Tools in ASAM design flow     7.2.1                                                                                                                                                                                                                                          | 101                                                       |

|   |                          | 7.2.1 Compaan Compiler                                                                                                                                                                                                                                                       | 101                                                       |

xiv

| Bi | bliogr            | raphy                                                                 | 167               |

|----|-------------------|-----------------------------------------------------------------------|-------------------|

|    |                   | B.4.3 Output of deterministic DSE                                     | 163               |

|    |                   | 1                                                                     | 159               |

|    |                   | 1 1                                                                   | 156               |

|    | B.4               | e                                                                     | 156               |

|    | B.3               | 11                                                                    | 152               |

|    | B.2               |                                                                       | 152               |

|    | B.1               | <u>I</u>                                                              | 151               |

| B  |                   |                                                                       | 151               |

| n  | <b>X</b> /X /     |                                                                       |                   |

|    |                   | •                                                                     | 141               |

|    |                   |                                                                       | 136               |

|    | A.2               |                                                                       | 133               |

|    | A.1               | Additional results from Experiment 2                                  | 133               |

| A  | Add               | itional results                                                       | 133               |

|    | 9.2               | Open issues                                                           | 131               |

|    |                   |                                                                       | 129<br>131        |

| 9  | <b>Con</b><br>9.1 |                                                                       | <b>129</b><br>129 |

| •  | G                 |                                                                       | 1.0.0             |

|    | 8.5               |                                                                       | 126               |

|    | 8.4               | · ·                                                                   | 123               |

|    | 8.3               |                                                                       | 122               |

|    |                   |                                                                       | 120               |

|    |                   |                                                                       | 120               |

|    |                   |                                                                       | 117               |

|    | 8.2               | •                                                                     | 117               |

|    | 8.1               |                                                                       | 116               |

| 8  | Unce              | ertainty model and task similarities                                  | 115               |

|    | 7.4               | Summary                                                               | 112               |

|    | 7.3               | 1                                                                     | 109               |

|    |                   |                                                                       | 106               |

|    |                   | 25                                                                    | 104               |

|    |                   | 7.2.3 Micro-architecture DSE tool - Phase 2 of micro-architecture DSE |                   |

|    |                   |                                                                       | 103               |

## **List of Figures**

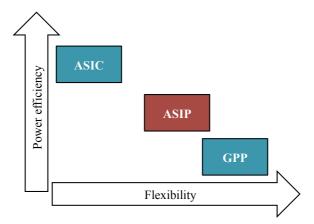

| 1.1  | Flexibility-power trade-off of different architectural options [12]                                                                           | 3  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

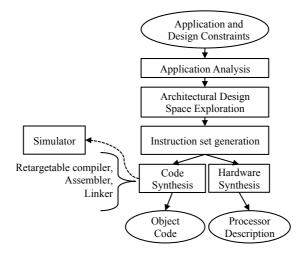

| 1.2  | Example of ASIP micro-architecture synthesis flow [40]                                                                                        | 5  |

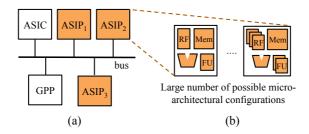

| 1.3  | Example of micro-architecture configurations for an ASIP [69]                                                                                 | 7  |

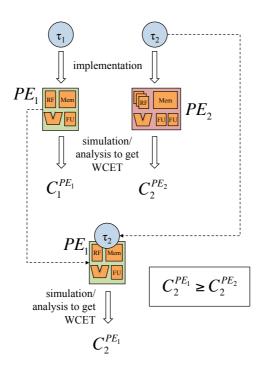

| 1.4  | Effect of a task clustering on the WCET                                                                                                       | 8  |

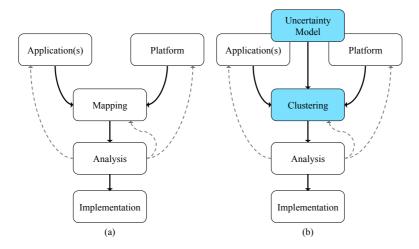

| 1.5  | Y-chart model for MPSoC design (a) and Y-chart model with Uncer-                                                                              |    |

|      | tainty Model (UM) for multi-ASIP design (b)                                                                                                   | 10 |

| 2.1  | Example of an application model [69]                                                                                                          | 19 |

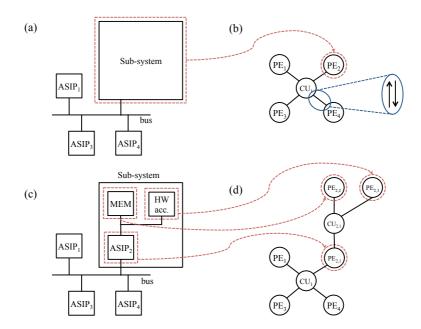

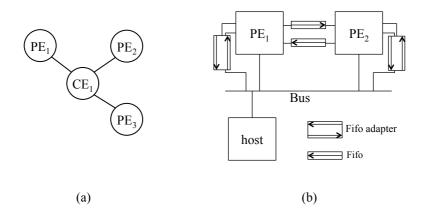

| 2.2  | Examples of platform (a,c) and its corresponding CP models (b,d)                                                                              | 21 |

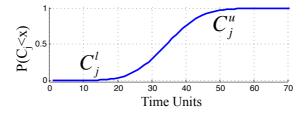

| 2.3  | Example of UM for a task $\tau_j$ [69]                                                                                                        | 23 |

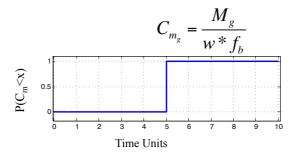

| 2.4  | Example of $C_{m_q}$ for a task $m_g$ [69]                                                                                                    | 23 |

| 2.5  | Default VEX micro-architecture configuration [25]                                                                                             | 25 |

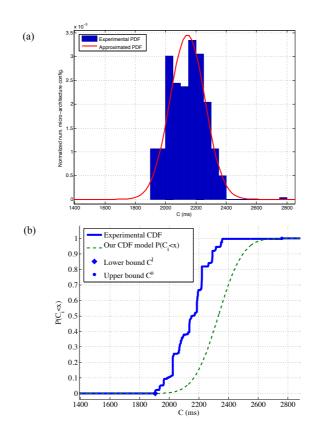

| 2.6  | (a) Histogram of the probability density function of the $C_i$ obtained                                                                       |    |

|      | with VEX and (b) comparison of our proposed CDF $(P(C_i < x))$ with                                                                           |    |

|      | the simulation results for mp3 decoder task                                                                                                   | 27 |

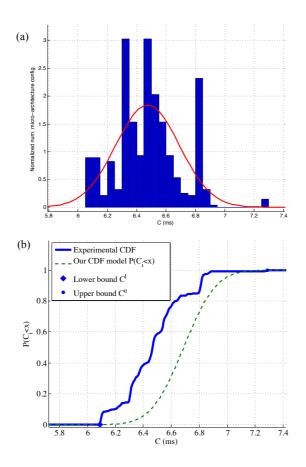

| 2.7  | (a) Histogram of the probability density function of the $C_i$ obtained with VEX and (b) comparison of our proposed CDF ( $P(C_i < x)$ ) with |    |

|      | the simulation results for jpeg decoder task                                                                                                  | 28 |

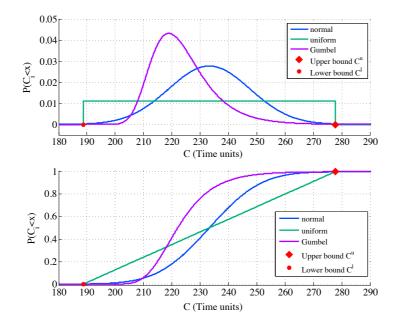

| 2.8  | (a) Probability density function and (b) Cumulative distribution func-                                                                        |    |

|      | tion (CDF)                                                                                                                                    | 30 |

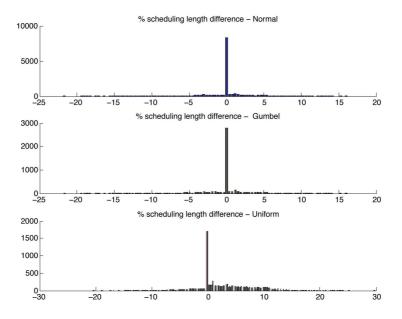

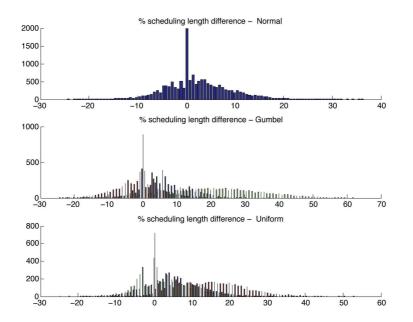

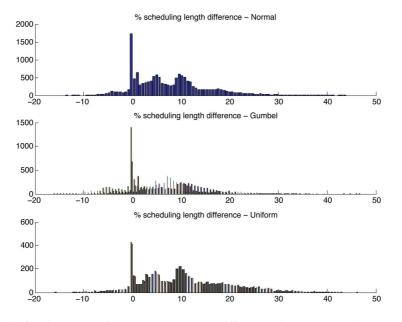

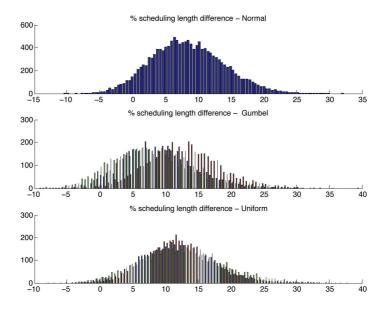

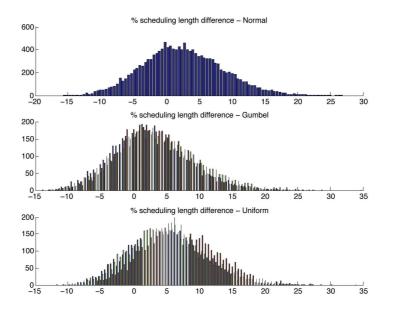

| 2.9  | Histogram of the percentage (%) differences in the scheduling length                                                                          |    |

|      | for Case Study 1                                                                                                                              | 33 |

| 2.10 | Histogram of the percentage (%) differences in the scheduling length for Case Study 4                                                         | 33 |

|      |                                                                                                                                               |    |

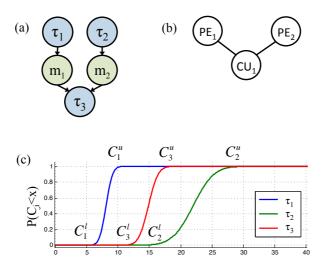

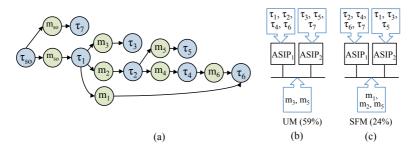

| 3.1  | Example of schedulability analysis: (a) input application, (b) PC model of the input platform and (c) $UM$ of the tasks [69]                  | 36 |

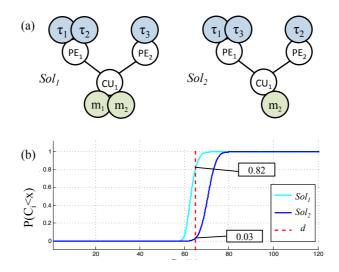

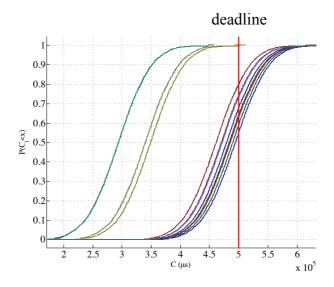

| 3.2 | (a) Task clustering solutions and (b) corresponding cumulative distribution functions (CDFs) produced by the schedulability analysis of the |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | example in Figure 3.1 [69]                                                                                                                  | 37  |

| 3.3 | Multi-ASIP platform design flow [69]                                                                                                        | 37  |

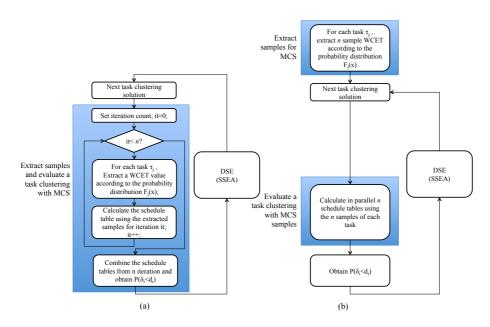

| 3.4 | Steps for performing design space exploration with MCS (a) Reordered steps for performing design space exploration with MCS (b)             | 40  |

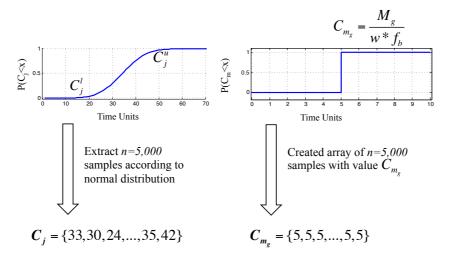

| 3.5 | Extraction of $n$ samples to build the arrays $C_j$ and $C_{m_g}$                                                                           | 41  |

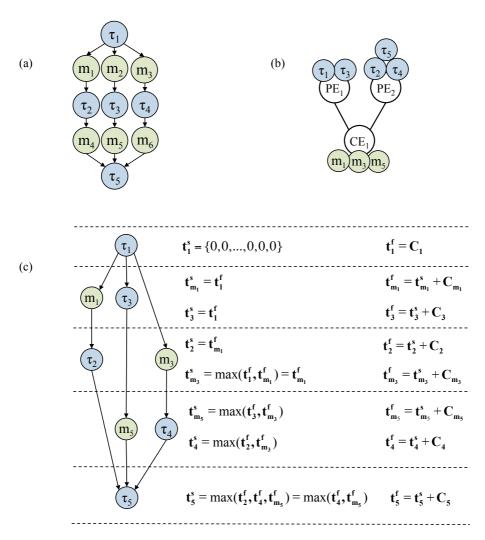

| 3.6 | Example of application $A_i$ (a), of task clustering solution for $A_i$ (b) and of $\delta_{A_i}$ calculation (c) [69]                      | 42  |

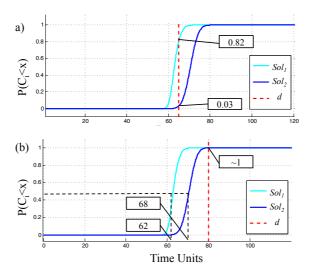

| 3.7 | Comparison between task clustering solutions                                                                                                | 43  |

| 3.8 | Comparison between WCET Uncertainty Model (UM) and straightfor-                                                                             |     |

|     | ward method (SFM) approaches                                                                                                                | 46  |

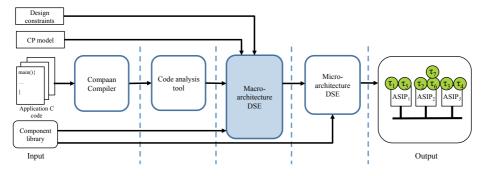

| 4.1 | Semi-automatic design flow for multi-ASIP design using the UM                                                                               | 52  |

| 4.2 | (a) KPN and (b) TG models for MJPEG encoder                                                                                                 | 53  |

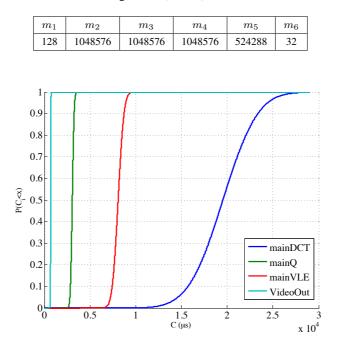

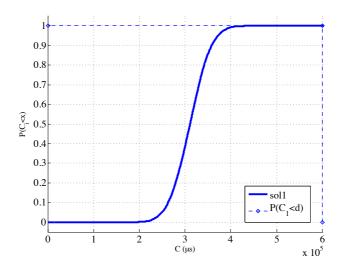

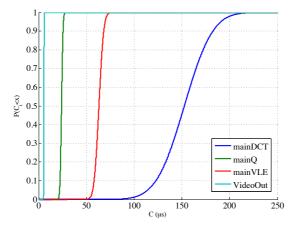

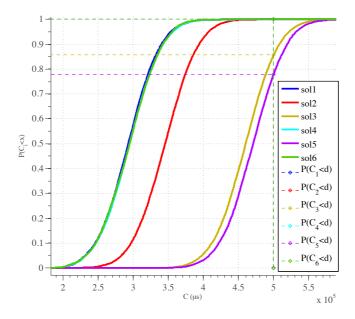

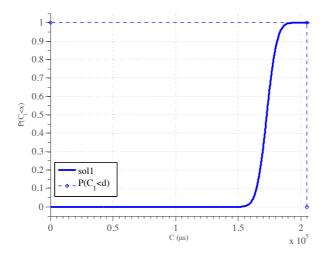

| 4.3 | Cumulative distribution functions for the tasks of the MJPEG encoder application (with $f = 166MHz$ )                                       | 55  |

| 4.4 | Results from the macro-architecture DSE for MJPEG encoder                                                                                   | 56  |

| 4.5 | (a) CP model of the initial platform and (b) designed platform for MJPEG encoder case study                                                 | 57  |

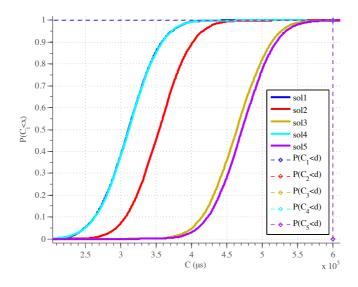

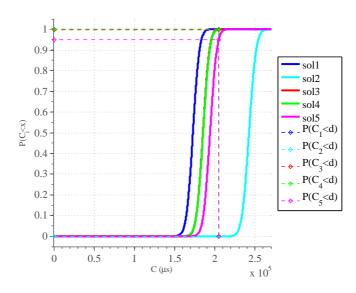

| 4.6 | Comparison of the CDF of different clustering solutions for MJPEG encoder                                                                   | 58  |

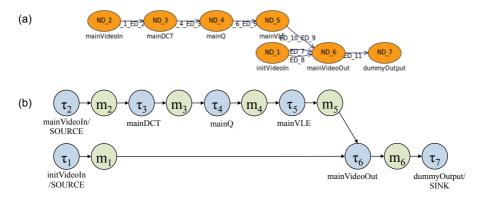

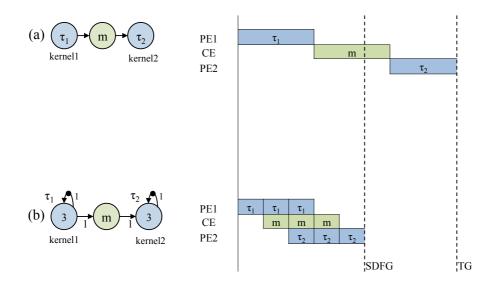

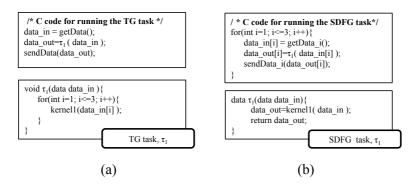

| 5.1 | Examples of TG (a) and SDFG models (b) of the same application .                                                                            | 66  |

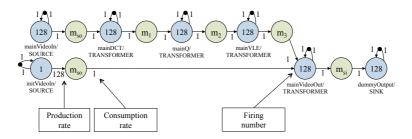

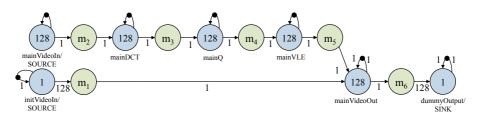

| 5.2 | SDFG model of MJPEG encoder                                                                                                                 | 67  |

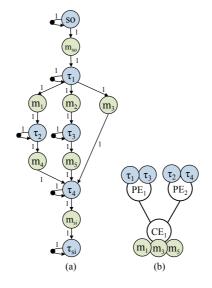

| 5.3 | Example of application and clustering for $\delta_{A_i}$ calculation                                                                        | 69  |

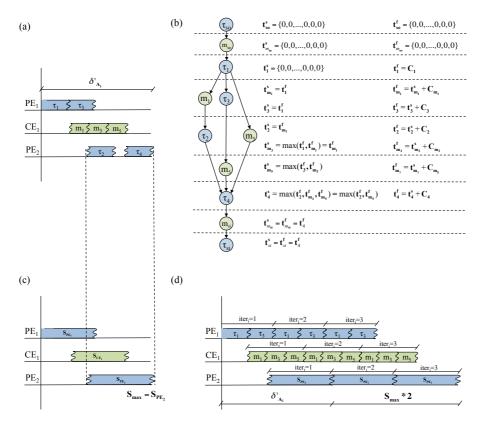

| 5.4 | Examples of TLA, (a) and (b), PA, (c) and (d), for a SDFG $\ldots \ldots$                                                                   | 70  |

| 5.5 | Reading and writing policy: $\tau_1$ reads from local memory and writes to remote memory                                                    | 72  |

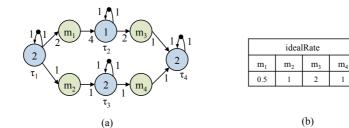

| 5.6 | (a) Input SDFG, (b) idealRate for each message of the SDFG, (c) re-                                                                         | , 2 |

| 5.0 | sults of the first eight iteration of Algorithm 5                                                                                           | 76  |

| 6.1 | Example of C code for a task part of a task graph (a) or of a SDFG (b)                                                                      | 79  |

| 6.2 | SDFG model for the MJPEG encoder                                                                                                            | 79  |

| 6.3 | Cumulative distribution functions for the tasks of the MJPEG encoder application (with $f = 166MHz$ )                                       | 80  |

| 6.4 | Results from the macro-architecture DSE for the MJPEG encoder                                                                               | 81  |

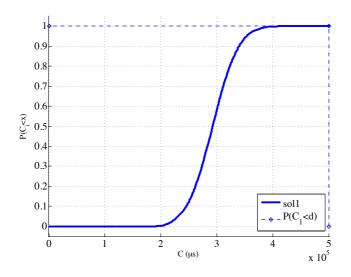

| 6.5 | Comparison of the CDF of different clustering solutions for the MJPEG encoder                                                               | 82  |

| 6.6 | Block schematic of the platform generated for $Sol_1$ for MJPEG encoder                                                                     | 84  |

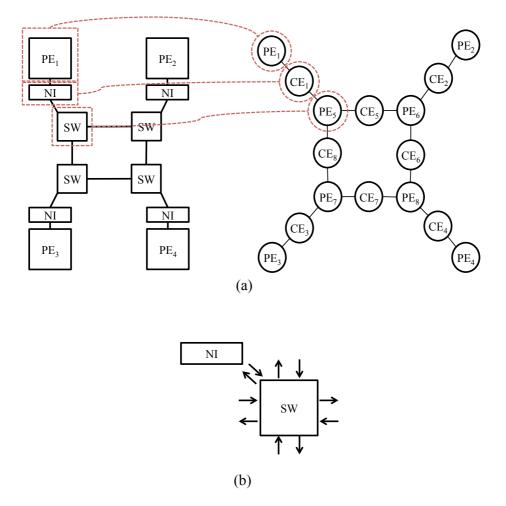

| 6.7 | Example of CP model for a 2x2 MESH NoC (a) Switch (SW) model (b)                                                                            | 94  |

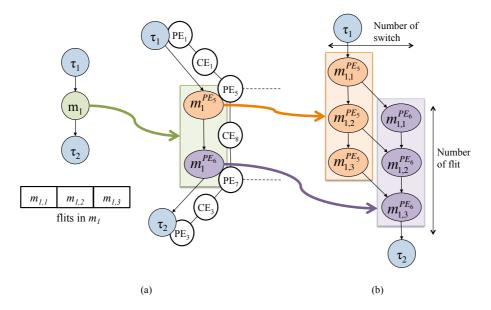

| 6.8 | Clustering of a message, $m_1$ , on the NoC $\dots \dots \dots \dots \dots \dots$                                                           | 96  |

| 6.9 | Output CDFs for MJPEG application clustered on a MESH NoC                                                                                   | 97  |

|     |                                                                                                                                             |     |

#### **LIST OF FIGURES**

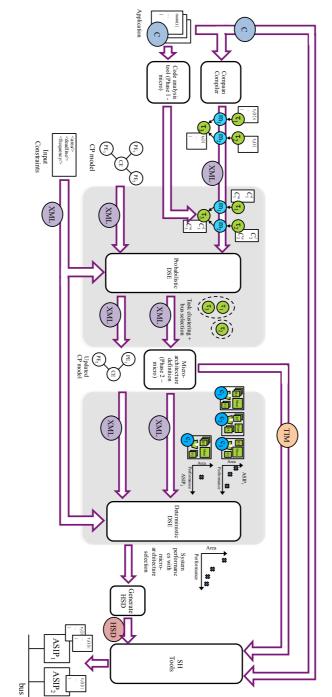

| 7.1  | ASAM design flow and interfaces with macro-architecture DSE                                | 102 |

|------|--------------------------------------------------------------------------------------------|-----|

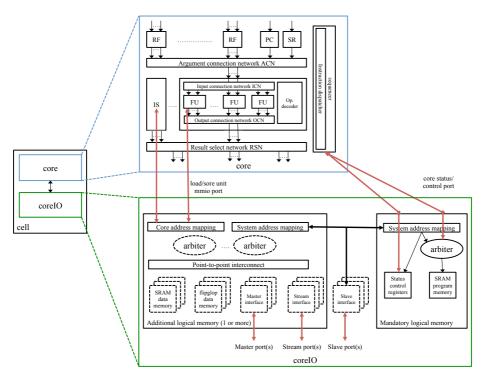

| 7.2  | Example of micro-architecture of a SH ASIP [62]                                            | 105 |

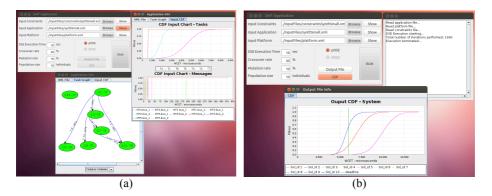

| 7.3  | GUI of the probabilistic DSE tool, input (a) and output (b)                                | 106 |

| 7.4  | GUI of the deterministic DSE tool, input (a) and output (b)                                | 107 |

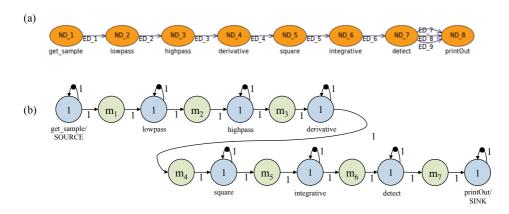

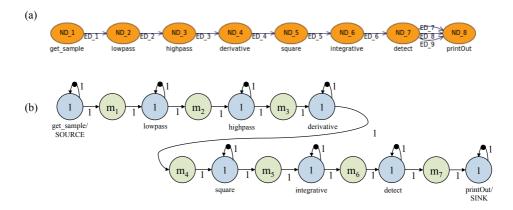

| 7.5  | KPN model generated by Compaan for the ECG (a) and corresponding                           |     |

|      | SDFG model (b)                                                                             | 110 |

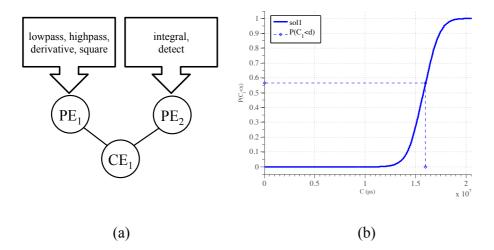

| 7.6  | Task clustering solution (a) and its CDF (b) produced by the probabilis-                   |     |

|      | tic DSE                                                                                    | 110 |

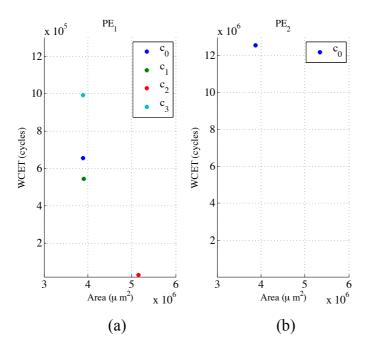

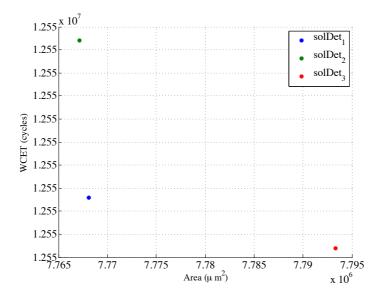

| 7.7  | Output of the micro-architecture DSE for clusters $PE_1$ (a) and $PE_2$ (b)                | 112 |

| 7.8  | Output of the deterministic DSE                                                            | 113 |

|      | •                                                                                          |     |

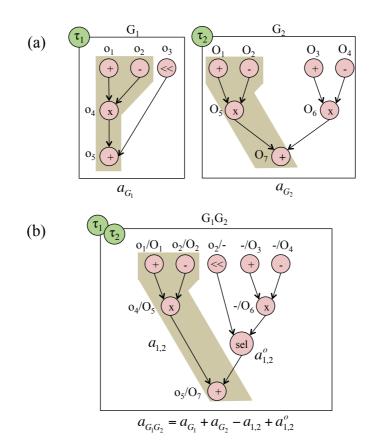

| 8.1  | A Graph Merging (or Task Clustering) Example, (a) DFG for $\tau_1$ and $\tau_2$            |     |

|      | (b) Merged DFG for $\tau_1$ and $\tau_2$ [28]                                              | 119 |

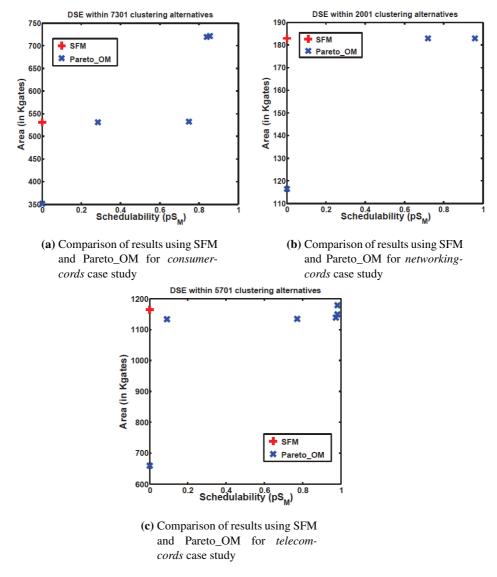

| 8.2  | Results obtained for the real-life benchmarks [28]                                         | 127 |

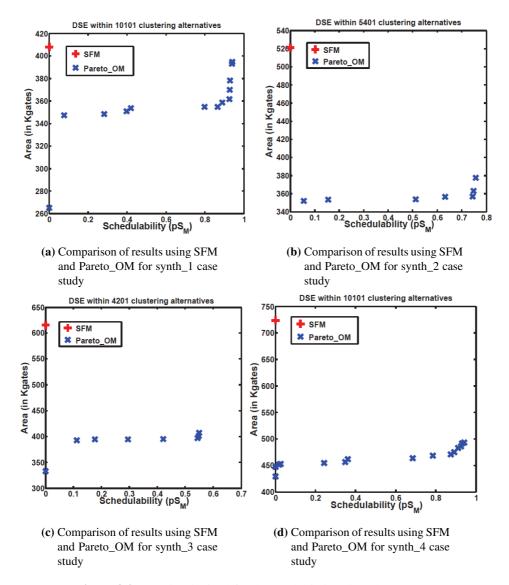

| 8.3  | Results obtained for the synthetic benchmarks [28]                                         | 128 |

|      |                                                                                            |     |

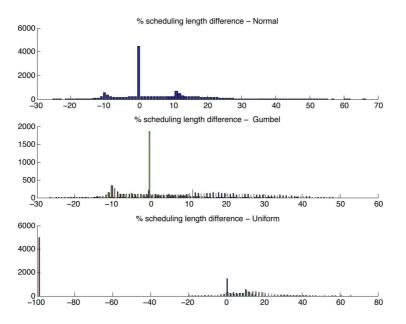

| A.1  | Histogram of the percentage (%) differences in the scheduling length                       |     |

|      | for Case Study 2                                                                           | 134 |

| A.2  | Histogram of the percentage (%) differences in the scheduling length                       |     |

|      | for Case Study 3                                                                           | 134 |

| A.3  | Histogram of the percentage (%) differences in the scheduling length                       | 105 |

|      | for Case Study 5                                                                           | 135 |

| A.4  | Histogram of the percentage (%) differences in the scheduling length                       | 105 |

|      | for Case Study 6                                                                           | 135 |

| A.5  | KPN model generated by Compaan for the ECG (a) and corresponding                           |     |

|      | SDFG model (b)                                                                             | 137 |

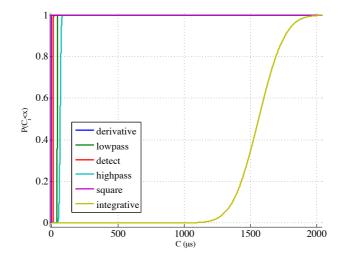

| A.6  | Cumulative distribution functions for the tasks of the ECG application                     | 100 |

|      | $(\text{with } f = 1MHz)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 138 |

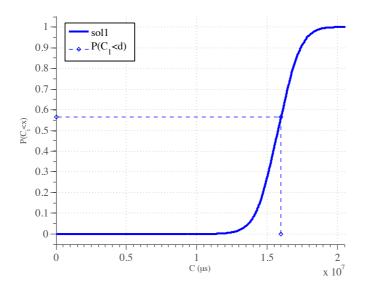

| A.7  | Results from the macro-architecture DSE for ECG                                            | 138 |

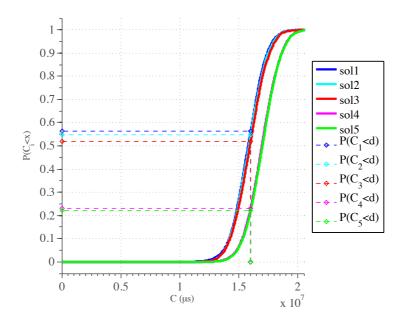

| A.8  | Comparison of the CDF of different clustering solutions for ECG                            | 140 |

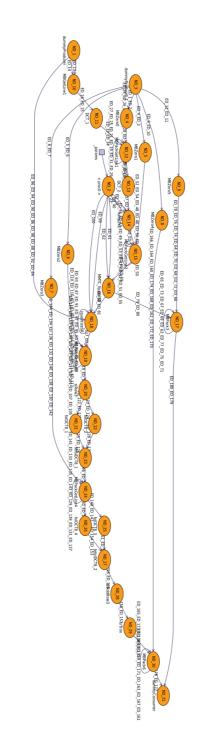

| A.9  | KPN model generated by Compaan for Spatial Coding case study                               | 142 |

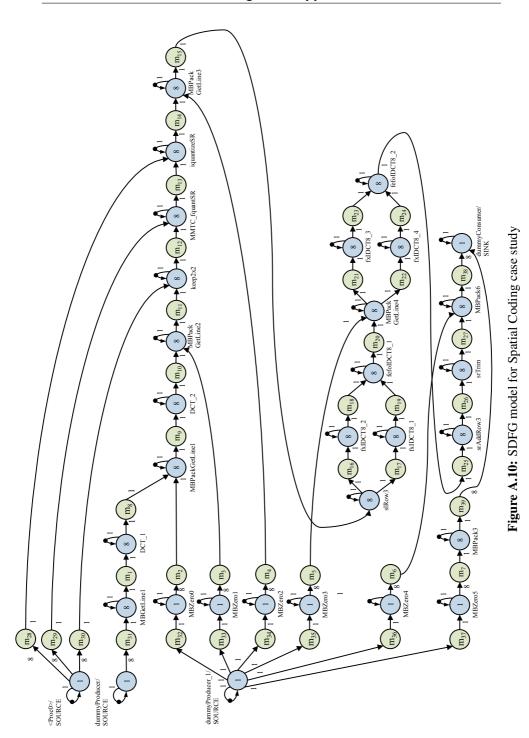

|      | SDFG model for Spatial Coding case study                                                   | 143 |

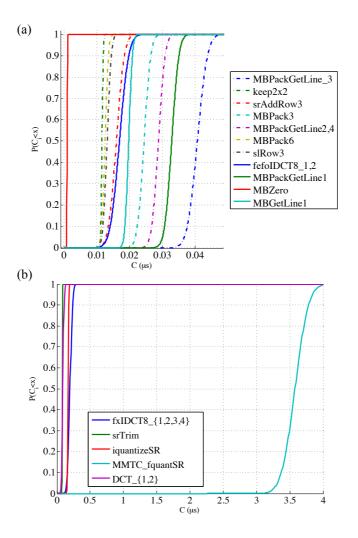

| A.11 | (a) and (b) Cumulative distribution functions of the tasks of the SC                       |     |

|      | application (with $f = 1,600 MHz$ )                                                        | 145 |

|      | Block schematic of the platform generated for $Sol_1$ for SC                               | 146 |

|      | Results from the macro-architecture DSE for SC                                             | 147 |

| A.14 | Comparison of the CDF of different clustering solutions for SC                             | 147 |

### **List of Tables**

| 2.1 | Micro-architecture features explored                                | 26 |

|-----|---------------------------------------------------------------------|----|

| 2.2 | Micro-architectures associated with the WCET upper and lower bounds | 29 |

| 2.3 | Case studies for the comparison of CDF types                        | 32 |

| 2.4 | Results of the comparison of CDF types (% average relative error)   | 32 |

| 3.1 | $C$ values for the motivation example (in $\mu s$ )                 | 46 |

| 4.1 | Comparison of UM and SFM [69]                                       | 50 |

| 4.2 | Clustering results for real-life and synthetic case studies         | 51 |

| 4.3 | C values for MJPEG encoder (average number of cycles for a single   |    |

|     | iteration of the task)                                              | 55 |

| 4.4 | Message sizes (in bits) for MJPEG encoder                           | 55 |

| 4.5 | Comparison of clustering solutions for MJPEG encoder                | 60 |

| 4.6 | Comparison between the number of cycles estimated by the profiling  |    |

|     | tool [43] and the ones obtained from simulation for MJPEG           | 62 |

| 6.1 | Input constraints for MJPEG encoder                                 | 78 |

| 6.2 | C values for MJPEG encoder (average number of cycles for a single   |    |

|     | iteration of the task)                                              | 80 |

| 6.3 | Message sizes (in bits) for MJPEG encoder                           | 80 |

| 6.4 | Comparison of clustering solutions for MJPEG encoder                | 83 |

| 6.5 | Comparison of clustering solutions for ECG                          | 85 |

| 6.6 | Comparison of clustering solutions for SC                           | 86 |

| 6.7 | Comparison of clustering solutions for MJPEG encoder using SDFG     |    |

|     | and task graph (TG) application models                              | 88 |

| 6.8 | Comparison between the number of cycles estimated by the profiling  |    |

|     | tool [43] and the ones obtained from simulation for MJPEG           | 90 |

| 6.9        | Comparison of clustering solutions for MJPEG encoder using updated upper and lower bound values | 92  |

|------------|-------------------------------------------------------------------------------------------------|-----|

| 6.10       | Clustering solutions for MJPEG encoder with MESH NoC                                            | 97  |

| 7.1<br>7.2 | Input constraints for ECG                                                                       | 109 |

| ,.2        | the task)                                                                                       | 109 |

| 8.1        | Results for the realistic case studies [28]                                                     | 124 |

| 8.2        | Results for the synthetic case studies [28]                                                     | 124 |

| A.1        | Input constraints for ECG and SC applications                                                   | 137 |

| A.2        | C values for ECG (average number of cycles for a single iteration of                            |     |

|            | the task)                                                                                       | 137 |

| A.3        | Message sizes (in bits) for ECG                                                                 | 137 |

| A.4        | Comparison of clustering solutions for ECG                                                      | 139 |

| A.5        | Comparison between the number of cycles estimated by the profiling                              |     |

|            | tool [43] and the ones obtained from simulation for ECG                                         | 140 |

| A.6        | C values for SC (average number of cycles for a single iteration of the                         |     |

|            | task)                                                                                           | 144 |

| A.7        | Message sizes (in bits) for SC                                                                  | 144 |

| A.8        | Comparison of clustering solutions for SC                                                       | 148 |

| A.9        | Comparison between the number of cycles estimated by the profiling                              |     |

|            | tool [43] and the ones obtained from simulation for SC                                          | 149 |

### Listings

| <b>B</b> .1 | Input constraints of ECG application                                    | 151 |

|-------------|-------------------------------------------------------------------------|-----|

| B.2         | Input platform for ECG application                                      | 152 |

| B.3         | Application model for ECG application annotated with the upper and      |     |

|             | lower bounds by Phase 1 of micro-architecture DSE (input of the prob-   |     |

|             | abilistic DSE)                                                          | 153 |

| <b>B.</b> 4 | Task clustering solution found by the probabilistic DSE (input of Phase |     |

|             | 2 of micro-architecture DSE)                                            | 156 |

| B.5         | Task clustering solution annotated with area and performance for mul-   |     |

|             | tiple micro-architecture for each ASIP (input of the deterministic DSE) | 159 |

| B.6         | Task clustering with selected micro-architecture for each ASIP and to-  |     |

|             | tal system area and performance                                         | 163 |

### Abbreviations

- **API** application programming interface.

- ASAM Automatic Architecture Synthesis and Application Mapping.

- **ASAP** as soon as possible.

- ASIC Application Specific Integrated Circuit.

- ASIP Application Specific Instruction-set Processor.

- **CDF** cumulative distribution function.

- CE communication element.

- DFG data flow graph.

- **DSE** Design Space Exploration.

- DSP Digital Signal Processor.

- ET event-triggered.

- FFT fast fourier transform.

- fpps fixed priority preemptive scheduling.

- fps frame-per-second.

- FU functional unit.

- GPP General-Purpose Processor.

GUI graphical user interface. HDL hardware description language. ILP instruction level parallelism. **IP** intellectual property. ISA instruction-set architecture. KPN Kahn process network. MCS Monte Carlo simulation. MEM memory. MPSoC Multi-Processor System-on-Chip. NI network interface. NoC Network-on-Chip. PA Pipeline Analysis. PDF probability density function. PE processing element. RF register file. **RTA** response time analysis. SDFG synchronous dataflow graph. SFM straightforward method. SH Silicon Hive. SoC System-on-Chip. SSEA Steady-State Evolutionary Algorithm. TDM time-division multiplexing. TG task graph. TLA Task-Level Analysis.

UM WCET Uncertainty Model.

**VEX** VLIW Example.

**VLIW** Very Long Instruction Word.

WCET worst-case execution time.

### CHAPTER 1

### Introduction

Today embedded systems include an increasing number of processors as an answer to higher performance and energy efficiency requirements; they are currently used for executing a wide variety of real time applications from the automotive, multimedia and networking domains. Multi-Processor System-on-Chip (MPSoC), especially when used in portable devices, have tight area, power and performance constraints that are given by the applications they implement. This increases the complexity of the design of the system which key design constraints are flexibility and performance. General-Purpose Processors (GPPs) are flexible platforms and run applications from various domains, but they fall behind on performance in comparison to ASICs. On the other hand, ASICs are designed to run specific applications and therefore lack flexibility. Application Specific Instruction-set Processors (ASIPs) combine the best of both worlds by incorporating application specific custom instructions, thereby giving more flexibility than ASICs and better performance than GPPs. ASIPs are designed such that they are optimized to run a specific set of functions.

Recently, an increasing number of ASIPs is used in embedded platforms, together with heterogeneous processing elements (PEs), for the implementation of real-time systems (especially image/video processing systems) [21, 83, 41]. Therefore, there is an increased tendency in designing multi-ASIP platforms, i.e. heterogeneous platforms that may contain multiple ASIPs.

Many companies are providing tools for the design of single ASIPs; among them Ca-

dence with the Tensilica toolchain for the XTensa processor [95] and Synopsys with the *Processor Designer tool* (using Lisa language) [92]. Additionally, ASIPs are now used in commercial processors, e.g., the Intel Atom Clovertrail+, a SoC for smartphones, that includes an ASIP for image signal processing [67].

In this thesis, we focus on the system-level (or macro-architectural level) design of multi-ASIP platforms. This chapter is organized as follows. First, we present the characteristics of an ASIP and the design flows that can be used for the implementation of a single ASIP (Section 1.1). Second, we described the motivations behind the inclusion of multiple ASIPs in a platform and the challenges in the design of a multi-ASIP platform (Sections 1.2 and 1.3). Then we present the related work (Section 1.4), the objective of this thesis (Section 1.5), our contributions (Section 1.6) and the structure of the thesis (Section 1.7).

#### 1.1 Why ASIPs?

#### **1.1.1** Application-specific instruction set processors

An ASIP is a programmable processor that is optimized for a particular application. ASIPs can be used as *custom processors* or *programmable accelerators*. They can be used to satisfy the need of modern embedded systems of having multiple functionalities integrated on a single System-on-Chip (SoC) [92]. The design of an ASIP requires the definition of the processor architecture (i.e. micro-architecture and instruction set) and the development of the corresponding simulator and software toolchain (compiler, assembler and linker). The micro-architecture, ISA (as described in Section 1.1.2). ASIPs provide a good trade-off between performance and power efficiency. In Figure 1.1, an intuitive comparison between ASIPs and other families of processors is shown.

ASICs are highly power efficient, but there are multiple factors that make ASICs design and manufacturing expensive [68], such as the high non-recurring engineering cost and the long time-to-market. The non-recurring engineering costs for ASICs increase together with the transistor density and the use of sub-micron technology. The mask-set can exceed one million dollars and the development of new tools for ASIC design demands a high cost as well [16]. Using ASIPs, more flexible designs can be generated and the non-recurring design costs can be reduced: ASIPs can be configured to run multiple applications and, vice versa, a design can be reused across multiple applications; this allows producing higher volumes of processors and amortizing design and manufacturing costs [68]. At the same time, the time-to-market is reduced.

Figure 1.1: Flexibility-power trade-off of different architectural options [12]

Compared to GPPs, ASIPs offer an energy efficient alternative still providing good performance; for example, they can be used in all portable devices that are targeting specific applications and where a GPP cannot be used due to its inefficient power management.

Additionally, an ASIP designer can count on tools for the automatic generation of the software toolchain and evaluation of their designs (as presented in Section 1.1.2). As a result, ASIPs can satisfy the requirements of those designers seeking high-performance and low power with the advantages of an automated design methodology [16].

#### 1.1.2 ASIP design

Figure 1.2 highlights the generic steps for the design of a single ASIP, as described in [40]. An ASIP is designed according to the application it has to run and the input constraints (e.g. performance, cost); hence, the first step is the analysis/profiling of the application code. A common approach is to define the micro-architecture starting from an ASIP template (selected from a library). The definition of a specific ASIP micro-architecture includes then a micro-architecture DSE for the identification of the appropriate number and type of functional units, memory, issue slot, etc., required by the application. After an initial micro-architecture is defined, the instruction set is generated, which can include custom instructions to speed up the execution.

There are multiple tools for the design of a single ASIP. Examples of ASIP designs are described in [46, 73, 79, 76, 101, 33, 45, 43]. In particular, [46, 73, 79, 76] employ the LISATek tool (now part of Synopsis [92]), [101] applies Target Compiler Tech-

nologies's tools (now also part of Synopsis [92]), [33] uses the Tensilica AutoTIE tool, [45] describes NoGAP and [43] uses the Silicon Hive (SH) toolchain. Following, we provide a brief description of the design flow proposed by these tools.

The LISA description language speeds up the design flow in Figure 1.2 by supporting the automatic generation of the software toolchain (retargetable compiler, assembler and linker), of the simulator and of a synthesizable HDL code, out of a processor description [76]. The processor description contains the instruction-set architecture (ISA) and the behavioral and timing model of the processor. Additionally, LISA is inserted into the LISATek tool suite that provides support for the design space exploration of the architecture. The simulator and synthesized HDL description can be used to evaluate the performance and cost of a LISA processor description and adjust it to the designer's requirements. The authors in [76] use the LISATek tool for the creation of two differently optimized ASIPs for an FFT algorithm. The development of the two ASIPs required three man weeks.

Target Compiler Technologies provide a tool suite called IP Designer to support the design of ASIPs. Each processor is described using nML description language which captures the structural characteristics of the design (i.e., the datapath architecture) and the instruction set architecture. IP Designer implements an entire retargetable toolchain for the ASIP design, a simulator and an HDL generator. In [101], the authors use IP Designer for the design of a ultra-low-power ASIP for an Electrocardiogram (ECG) application with software and hardware optimization to improve performance and minimize the power consumption.

A Tensilica processor [95] is described using the TIE (Tensilica Instruction Extension) language that specifies the ISA and its extensions. Additionally, TIE allows having the ISA extension implemented in hardware and have them recognized by the Tensilica software toolchain. Tensilica AutoTIE described in [33] is a tool for the automatic extension of the base ASIP's ISA with Very Long Instruction Word (VLIW) instructions, vector operations and custom operations. AutoTIE explores a large number of ISA extensions (based on the profile of the loops of the input application) and then uses performance and area estimations to evaluate the combinations of multiple extensions and to generate an ASIP.

NoGAP [45] is a research tool that aims at the automatic generation of a software toolchain for ASIPs. The tool provides assembler, simulator and a hardware generator. NoGAP provides the designer with a very flexible architecture and does not use an initial ISA template. However, NoGAP does not provide an automatic DSE; the designer is responsible for the definition of the initial architecture that he considers compatible with the application or application domain. In [45], NoGAP is used to generate a single issue RISC processor with DSP extensions. The development required three man weeks, but considering that an expert designer is involved in the architecture definition.

Figure 1.2: Example of ASIP micro-architecture synthesis flow [40]

SH tools constitute a toolchain for the development of VLIW ASIPs [62]. SH offers proprietary languages for the hardware description of the processors and of the multi-processor platform. Additionally, it provides a retargetable compiler and a simulator for the execution of the application C code on the user-defined platform. In this section, we do not provide additional details about SH tools that are thoroughly described in Section 7.2.4. We use SH tools for the experimental evaluation of the design approach described in this thesis. Silicon Hive is now part of Intel Benelux B.V.

#### **1.2** Why a multi-ASIP platform?

In the previous section, we mentioned the advantages derived from employing ASIPs. In this section, we look into reasons for using multi-ASIP platforms, i.e. MPSoCs containing multiple ASIPs.

Future embedded systems will demand higher computational efficiency and cheap implementations. ASIPs represent an attractive solution especially in areas such as multimedia, networking, and signal processing [68]. As an example, let us consider the multiple applications for image processing running on today mobile phones. These applications require specialized hardware for efficient execution; however, as the number of different applications is growing, also the number of specialized PEs for their execution has to increase. Integrating multiple ASIPs in a single SoC is a promising solution with high flexibility; it allows having customized PEs to run applications (or part of them) and minimizing the energy consumption differentiating between the architecture implemented by each ASIP. Having multiple heterogeneous ASIPs, we can partition the applications into tasks, assign the tasks to the different PEs and exploit the task level and pipeline parallelism, intrinsic to signal processing and multimedia domains.

## **1.3** Challenges in multi-ASIP design

In Section 1.1.2 we described possible design methodologies for the design of a single ASIP. An ASIP is designed according to the application(s) that it has to execute.

However, when we consider multiple ASIPs and multiple input applications or a single input application partitioned into multiple tasks, we add an extra degree of complexity to the design problem. In fact, we need to establish how these tasks are assigned to the different ASIPs that are then designed according to the tasks they have to run. This task assignment is not straightforward, as it involves inter-dependent decisions on macro-architecture (or system-level) and micro-architecture (i.e. ASIP) levels. These decisions affect the number of ASIPs, their micro-architecture and interconnection together with the assignment of tasks to the different ASIPs; the optimization of the multi-ASIP platform is, therefore, a NP-complete problem [29].

We call the assignment of tasks to the different ASIPs *task clustering*. Each group of tasks is a *task cluster* and corresponds to a single ASIP. In order to determine the task clustering for one or more applications, we need to perform a schedulability analysis that requires information about the execution performance of the tasks and of the data dependencies among them. It is possible to know the performance of each task when an ASIP is implemented/designed.

However, the ASIP design approaches described in Section 1.1.2 imply that an ASIP is implemented only after knowing which tasks it has to run.

Therefore, we have a tight connection between the task clustering and the design of each ASIP as they depend on each other.

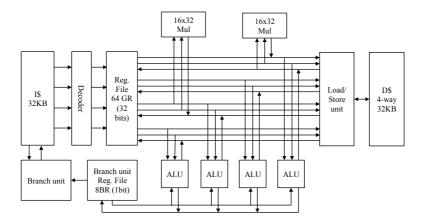

Depending on the number of tasks and ASIPs included in the platform, a very large number of task clusters has to be evaluated during DSE. For each task cluster, the micro-architecture design of a *single* ASIP involves a number of steps and the design of a single ASIP can requires multiple days (Section 1.1.2). Further, the design space of a ASIP micro-architecture is very large and depends on the number and data widths of register files (RFs) and memory blocks (*MEM*), and number of functional units (FUs) (Figure 1.3). Hence, platform design with multiple ASIPs is non-trivial as it needs to take the design space of the ASIP micro-architecture into consideration when exploring various platform solutions. In the rest of the thesis, we use the term *micro-architectural configuration* to indicate the micro-architecture resulting from a specific ASIP design.

Figure 1.3: Example of micro-architecture configurations for an ASIP [69]

Consider an example with three tasks  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  for which a multi-ASIP bus-based platform has to be designed. We use the worst-case execution time (WCET) as the performance value for the tasks. We define a *task cluster*  $tc_k$ , as the set of tasks used at the input of the flow in Figure 1.2 to design an ASIP  $PE_k$ . Let us now consider two different ways of clustering the three tasks: case (a) and (b). In case (a), tasks are assigned to three different ASIPs,  $PE_1$ ,  $PE_2$  and  $PE_3$ , with the corresponding clusters  $tc_1 = {\tau_1}$ ,  $tc_2 = {\tau_2}$  and  $tc_3 = {\tau_3}$ . The single ASIP design flow (Figure 1.2) can be followed and each ASIP micro-architecture can be optimized to satisfy the particular task. Now that we have each ASIP defined for case (a), we can determine the worst-case execution time (WCET) of each task. Let us denote by  $C_j^{PE_k}$ , the WCET of task  $\tau_j$  on ASIP  $PE_k$ . Although an ASIP  $PE_k$  has been designed and tuned for a certain set of tasks  $tc_k$ , it could also run a task  $\tau_j \notin tc_k$  (if binaries are compatible). Let us consider that we run  $\tau_2$  on  $PE_1$ , tuned for  $\tau_1$ . The micro-architecture of  $PE_1$  has not been specifically tuned for the functionality of  $\tau_2$ , as a consequence we can expect that  $C_2^{PE_2} \leq C_2^{PE_1}$  (note that the increase in  $C_2^{PE_1}$  also depends on the similarity between  $\tau_1$  and  $\tau_2$ ) (this example is depicted in Figure 1.4).

In case (b),  $\tau_1$  is clustered with  $\tau_2$  such that  $tc'_1 = {\tau_1, \tau_2}$  and  $tc'_2 = {\tau_3}$ . Since the task clustering has changed, we need to re-design all the ASIPs from case (a), otherwise the WCET of  $\tau_2$  may increase too much. This will again impact the WCETs of the tasks. In our case, the WCET of  $\tau_2$  will decrease and that of  $\tau_1$  might increase, depending on how much the ASIP design will satisfy the functionality required by one task compared to the other.

This example shows that every time a task clustering changes, the WCETs will change. For every WCET change, we need to evaluate again the schedulability of the applications. However, we cannot know the WCET of a task before we have designed the corresponding ASIP. Therefore, after each re-clustering decision we would have to run a complete ASIP design flow, as described in Section 1.1.2, for each affected ASIP. As mentioned, an ASIP design takes days, so it cannot be done during the DSE at the platform level. Hence, to perform DSE during platform design, we need the WCETs to evaluate the schedulability, and WCETs can only be known after the platform has

Figure 1.4: Effect of a task clustering on the WCET

been fully designed. This *circular dependency* drastically limits the number of platform alternatives that can be considered during DSE.

Possible options to break this circular dependency, include having one ASIP for each task or a single ASIP for all tasks. Then, the designer will have to split or merge the tasks to get to feasible implementations that meet the performance requirements and do not exceed the platform cost (e.g. the total area of the platform). However, these approaches require the work of an experienced designer. Another possible alternative that is adopted in many design methods described in literature (Section 1.4), is to consider only a small set of predefined micro-architecture configurations for each ASIP so that the design flow of a multi-ASIP platform falls back into a classic MPSoC design. In this case the risk is to ignore potentially good solutions as the micro-architecture DSE is limited beforehand.

The goal of this thesis is to offer an alternative approach to break this **circular dependency**, considering the space of all possible micro-architecture configurations, and to define a multi-ASIP platform given one or more applications and its constraints as input.

## **1.4 Related work**

There has been a significant effort in research for supporting the design and evaluation of MPSoCs. There are design approaches that target the optimization of a platform implementation including the number and type of processors, their interconnections and the memory sizes. In other approaches the platform is already available and the focus is on the performance evaluation of different mapping and scheduling. Application partitioning is also considered. Some work proposes general design approaches that can be applied to a wide variety of application domains. For example, the Platform-based design paradigm [82, 49] in which a design is defined by a *meeting-in-the-middle* process: the specifications of the system to implement are gradually refined and matched with possible *platforms*<sup>1</sup> at different level of abstractions. The work in [47] proposes a simulation frameworks for accurate performance estimation of applications executing on multi-threaded multi-processor platform. The authors adopt separate models for the application and the platform that are combined during the DSE of mappings. They also consider a temporal (allocation of time budget) mapping to capture multi-threading. However, the platform composition is well known and therefore an accurate model of the performance/cost of each processing and communication architecture is available. In a similar manner, in [98, 24], the authors assume that the platform is already available (predefined PEs and communication architecture) and they focus on the exploration, using ant colony optimization, of different partitionings of the application considering the data dependencies of the tasks. In this thesis, we provide a technique for the evaluation of different task clustering solutions that is also used to guide the platform definition.

There is then a large body of work for the design of application and domain specific MPSoCs, i.e design methods that produce multi-core platforms targeting specific applications. Many of these works do not use ASIPs [66, 9, 44, 52, 11, 78, 54, 23, 57]. [66, 9] adopt a high level description of the application and initial platform to define the number and type of processors to use (taken from a library), the number of I/O ports of each PE, the size of the memories (dedicated and shared memories) and the interconnection according to an application mapping established by the designer. However, the authors do not consider the effect of different task clusterings or the potential of using ASIPs.

In [44, 52], the authors use UML to model the application, the platform and the design constraints; they explore different macro-architecture possibilities but always considering PEs taken from a library with well known performance and cost.

The approaches in [11, 78, 54, 23, 57] target multimedia or signal processing applications. In [11], MP-ARM, a SystemC simulation engine for MPSoC has been developed. The simulator supposes an AMBA-like bus as communication architecture and ARM CPU as PEs. Although the authors explore different arbitration policies, cache sizes and

<sup>&</sup>lt;sup>1</sup>a platform is a library of components that can be assembled to generate a design at that abstraction level

the effect of different application partitioning, they consider a fixed macro-architecture composition with predefined PEs and do not perform mapping or scheduling DSE.

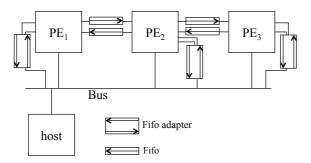

Daedalus is described in [78]; it is an automated design environment for for systemlevel architectural exploration, system-level synthesis, programming, and prototyping on FPGA. It adopts Sesame [23] for the system-level modeling and simulation. Daedalus builds an MPSoC using the PEs from a library and interconnects them using a crossbar switch or a shared bus [77] given a Kahn process network (KPN) model of the input application. This design flow allows the generation of multi-processor systems targeting multimedia or signal processing applications; it optimizes the processing and communication element, defining a customization at platform level, but does not take into account the customization of the micro-architecture of each PE that is one of the goals of this thesis.

Sesame [23] follows a Y-chart approach (Figure 1.5a) with separated models for the applications, modeled as a KPN, and the platform. Application and platform are combined and evaluated during mapping; its multi-objective DSE can be used in the early phases of the design to guide the designer towards the most promising solutions. The work presented in this thesis has some similarities with Sesame: we also propose a method to be applied in the very early phases of the design and that is based on a Y-chart model (Figure 1.5b). On the other hand, we are focusing on ASIPs not yet synthesized without a precise performance and area model for each task/processor as the one available in Sesame. Therefore, we have an additional level of complexity in our design due to the unknown micro-architecture of the PEs.

Another design approach for the definition of an MPSoC platform for a specific ap-

Figure 1.5: Y-chart model for MPSoC design (a) and Y-chart model with Uncertainty Model (UM) for multi-ASIP design (b)

plication is presented in [57] where DSE is used to select the PEs, partitioning the application, modeled as a task graph, and scheduling it. It also runs an optimization

#### 1.4 Related work

for the communication architecture using a hierarchy of buses. The DSE is guided by a greedy exploration algorithm defined by the authors. The optimization objectives are the platform cost and the performance of the application. As for the other works previously mentioned, the platform is built out of components from a library, whose behavior and performance are well known.

In [54], the MAMPS approach for MPSoC synthesis is described. The authors present a technique that considers multiple use-cases (or scenarios) of execution, in which there are multiple input applications active at different instant of time, and design a custom platform, in which multiple cores are interconnected through FIFOs. The applications are modeled as synchronous dataflow graphs (SDFGs). The authors do not explore multiple mapping solutions (there is an arbitrary assignment of the SDFG actors to the PEs) or interconnections type; as in the previous cases, a set of already synthesized core is available (e.g. Xilinx Microblaze).