## **Advances in Very High Frequency Power Conversion**

Kovacevic, Milovan

Publication date: 2015

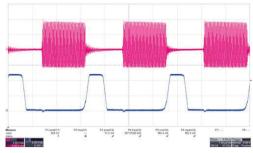

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Kovacevic, M. (2015). *Advances in Very High Frequency Power Conversion*. Technical University of Denmark, Department of Electrical Engineering.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Technical University of Denmark

Milovan Kovacevic

# Advances in Very High Frequency Power Conversion

PhD Thesis, February 2015

**DTU Electrical Engineering** Department of Electrical Engineering

Milovan Kovacevic

# Advances in Very High Frequency Power Conversion

PhD Thesis, February 2015

Advances in Very High Frequency Power Conversion

This report was prepared by Milovan Kovacevic

### Supervisors

Michael A.E. Andersen Arnold Knott

| Release date:<br>Category: | 4th February 2015<br>1 (public)                                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Edition:                   | Final                                                                                                                                    |

| Comments:                  | This thesis is submitted in partial fulfillment of the requirements for obtaining the PhD degree at the Technical University of Denmark. |

| Rights:                    | ©Milovan Kovacevic, 2015                                                                                                                 |

Department of Electrical Engineering Electronics Group (ELE) Technical University of Denmark Oersteds Plads bygning 349 DK-2800 Kgs. Lyngby Denmark

www.ele.elektro.dtu.dk Tel: (+45) 45 25 25 25 Fax: (+45) 45 88 01 17 E-mail: elektro@elektro.dtu.dk

## Preface and Acknowledgment

The PhD thesis titled "Advances in Very High Frequency Power Conversion" has been carried out at the Electronics group, Department of Electrical Engineering, Technical University of Denmark (DTU) during the period November 2011 to February 2015. The PhD project was co-funded by Danish Lighting Innovation Network, Copenhagen, Denmark, and FINsix Corporation in Menlo Park, California, where external research visit was carried out.

It is a matter of great pleasure and privilege to be able to express deep gratitude to all who stood by me and helped me throughout the project. Most of all:

- My PhD supervisors, Prof. Michael A. E. Andersen and Assoc. Prof. Arnold Knot, for providing me an opportunity to approach, and expand, the very boundaries of our understanding of power electronics. Their unwavering support, insightful suggestions, encouragement, and innumerable fruitful discussions throughout my PhD. Their advice on the subjects of power electronics was immensely helpful in carrying out my research.

- Anthony Sagneri, CTO of FINsix Corporation, for providing a unique opportunity to be in the world's first company developing VHF-based power supplies, and be a part of an amazing and versatile engineering team. His extraordinary understanding of physics and power electronics, and electronics in general, were and still are of immeasurable value for my own professional development.

- All the colleagues at Electronics group for their support, encouragement, constructive discussions, suggestions, comments, and all the great time we had together.

Special thanks to:

- Henriette Dalby Wolff and Bertil Morelli for their limitless kindness, patience, and support.

- Riccardo Pittini, Maria Carmen del Mira Albert, Juan Carlos Hernandez Botella - for being the best friends and colleagues one could possibly hope for.

- Mickey Pierre Madsen for invaluable discussions, sanity checks, and guidance through the world of patent attorneys.

- I am eternally indebted to my parents, Ljiljana and Dragutin Kovacevic, and my elder sister Ruzica, for their never-fading love, support, and encouragement during my PhD in Denmark.

- Finally, I express my gratitude to all those who helped me directly or indirectly in the successful completion of my PhD.

## Abstract

Resonant and quasi-resonant converters operated at frequencies above 30 MHz have attracted special attention in the last two decades. Compared to conventional converters operated at ~100 kHz, they offer significant advantages: smaller volume and weight, lower cost, and faster transient performance. Excellent performance and small size of magnetic components and capacitors at very high frequencies, along with constant advances in performance of power semiconductor devices, suggests a sizable shift in consumer power supplies market into this area in the near future.

To operate dc-dc converter power devices at very high frequencies, switching loss needs to reduced or eliminated, as it would become prohibitively large. In addition, as the frequency increases, hard-switched gate driving becomes less and less of an option, as it embodies the same loss mechanism. A low-loss gate drive methods may need to be applied, especially at low power levels where gating loss becomes a significant percentage of the total loss budget. Various resonant gate drive methods have been proposed to address this design challenge, with varying size, cost, and complexity. This dissertation presents a self-oscillating resonant gate drive solution, which is applicable in cases when there are at least two power stages, and with minimal additional hardware requirements. It is experimentally confirmed that the method is suitable for both parallel and serial input configurations. Compared to state-of-the-art solutions, the proposed method provides low complexity and low gate loss simultaneously. A direct design synthesis method is provided for resonant SEPIC converters employing this technique. Most experimental prototypes were developed using low cost, commercially available power semiconductors.

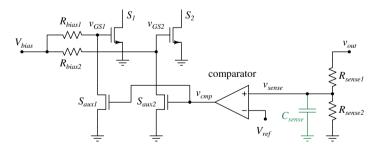

Due to very fast transient response of VHF converters, on/off control schemes are often used for their output control. The options presented so far demonstrated excellent performance, but with very strict timing constraints on all functional blocks in the feedback loop. Therefore, an on/off control method is proposed which allows the use of conventional ICs, while still providing high control bandwidth and performance comparable to state-of-the-art solutions.

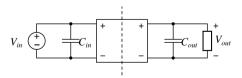

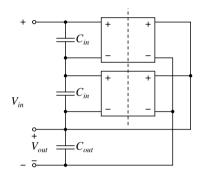

Since in many applications of interest galvanic isolation is not a requirement, the thesis proposes a method for providing a DC power path from input to output of a previously galvanic isolated converter. The method requires connection rearrangement in the existing converter only, and provides higher output power and converter efficiency for the same or lower voltage and/or current stresses in the converter components.

Achieved results demonstrated that low-cost solutions, based on silicon power semiconductors and ICs, can achieve formidable performance even when operated at very high frequencies. The power devices employed in this thesis were not optimized for such operation. With proper optimization and new semiconductor materials, it is expected that VHF converters become frequent occurrence within the power conversion domain, rather than a curiosity.

**Keywords:** on/off control, very high frequency, dc-dc power conversion, resonant converters, switch-mode power supplies, zero-voltage switching

## Resumé

Resonante og quasi resonante konvertere med skifte frekvenser over 30 MHz har tiltrukket stor opmærksomhed inden for de sidste to årtier. Sammenlignet med konventionelle konvertere med skifte frekvenser omkring ~100 KHz udmærker de sig ved mindre størrelse, mindre vægt, lavere pris og hurtigere respons tider. Konverternes gode ydeevne, samt mindre magnetiske komponenter og kapacitanser ved disse høje frekvenser, og en fortsat udvikling af halvledere, peger på at der kommer et paradigme skift inden for effektelektronik henvendt til forbrugeren inden for få år.

For at operere DC-DC konverternes halvledere ved Very High Frequency skal skifte tabene minimeres eller helt fjernes, da de ville blive alt for store. Derudover når frekvenserne øges mindskes muligheden for at benytte hard-switched gate drive, da de lider at samme tabs problemer. Lav tabs gate drive metoder kan være den eneste mulighed, specielt ved laveffekt løsninger hvor tabene i gate drivet ikke må dominere det samlede tab. Der findes forskellige resonante gate drive metoder til at overkomme tabs udfordringerne, alle med forskellig fokus såsom størrelse, pris og kompleksitet. Denne afhandling præsentere en selvoscillerende resonant gate drive metode, der kan benyttes når der som minimum er to effekttrin, metoden kan implementeres med relativt få ekstra komponenter. Det er eksperimentelt bekræftet at man kan benytte metoden både med serielt og parallelt forbundne indgange af konvertere. Sammenlignet med state-of-the-art løsninger, udmærker den beskrevne metode sig ved at have lav kompleksitet samt lave gate tab. En design metode for at benytte dette gate drive sammen med en resonant SEPIC konverter er beskrevet. Næsten alle prototyper beskrevet i denne afhandling er udviklet med billige konventionelle halvledere.

Hurtige respons tider på VHF konverter gør dem velegnet til tænd/sluk kontrol af udgangen. Tidligere implementeringer af denne kontrol metode har vidst gode resultater, men det stiller høje timing krav til alle blokkene i tilbagekoblingen. En tænd/sluk kontrol metode præsenteres der tillader brug af konventionelle integrerede chips, denne metode giver mulighed for en stabil kontrol samt høj båndbredde sammenlignet med state-of-the-art løsninger.

Mange anvendelser har ikke noget krav om galvanisk isolering. Denne afhandling beskriver en metode der skaber en DC forbindelse fra indgang til udgang af en tidligere galvanisk isoleret konverter. Denne metode består af en om konfiguration af ind og udgange, således at både udgangs effekten og effektiviteten stiger af det samlede system, uden at der skaber yderlige stress eller ændringer i konverteren.

De opnåede resultater demonstrere at billige løsninger, baseret på silicium halvledere og ICer, kan levere god ydeevne selv med skifte frekvenser i VHF området. Halvlederne benyttet i denne afhandling har ikke været optimeret til at blive brugt ved så høje frekvenser. Med fokus på at optimering af kendte samt nye halvlederteknologier er det forventet, at VHF konvertere bliver en fast del af effektelektronikken.

**Nøgleord:** tænd/sluk kontrol, very high frequency, dc-dc strøm konverter, resonant konverter, switch-mode strøm forsyninger, zero-voltage switching

# Contents

| Pr  | eface |                                     | i   |

|-----|-------|-------------------------------------|-----|

| Ał  | ostra | ct                                  | iii |

| Re  | esum  | é                                   | v   |

| Co  | onten | ts v                                | ii  |

| Lis | st of | Figures                             | xi  |

| Li  | st of | Tables xi                           | ii  |

| In  | trodı | action                              | 1   |

| 1   | Intr  | oduction                            | 1   |

|     | 1.1   | Background and Motivation           | 1   |

|     | 1.2   | Thesis Scope                        | 2   |

|     | 1.3   | Thesis Objectives                   | 2   |

|     | 1.4   | Thesis Structure and Content        | 2   |

| 2   | Ove   | rview and State-of-the-Art          | 5   |

|     | 2.1   | VHF SMPS: Topologies                | 5   |

|     |       | 2.1.1 Resonant Inverters/Rectifiers | 6   |

|     |       | 2.1.2 Quasi-Resonant Converters     | 11  |

|     | 2.2   | Control Schemes                     | 12  |

|     |       | 2.2.1 On/Off Control                | 13  |

|     |       | 2.2.2 Cycle-Skipping Control 1      | 14  |

|         |            | 2.2.3 Frequency Modulation Control                                           | 16        |

|---------|------------|------------------------------------------------------------------------------|-----------|

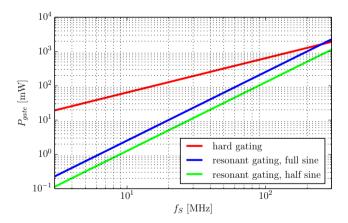

|         | 2.3        | Gate Drives                                                                  | 16        |

|         |            | 2.3.1 Hard Switching Gate Drives                                             | 16        |

|         |            | 2.3.2 Resonant Gate Drives                                                   | 17        |

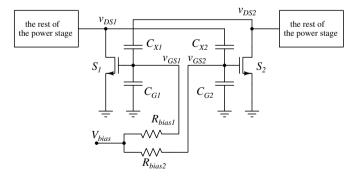

|         |            | 2.3.3 Self-Oscillating Gate Drives                                           | 17        |

|         |            | 2.3.4 Conclusion                                                             | 18        |

|         | 2.4        | Summary                                                                      | 20        |

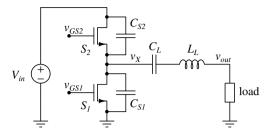

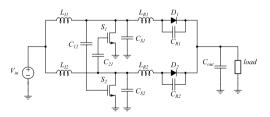

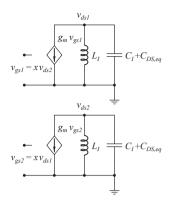

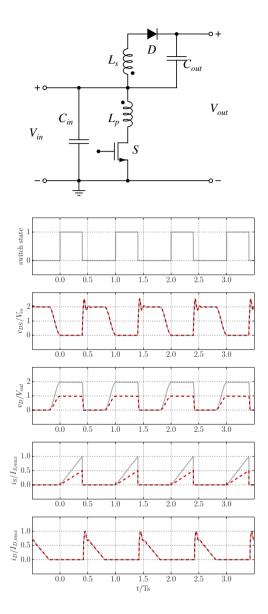

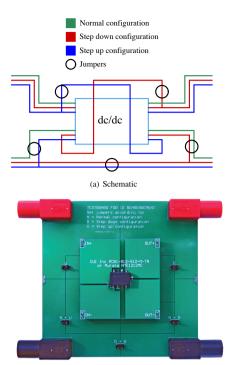

| 3       | Inte       | erleaved Self-Oscillating Resonant (ISOR) Gate Drive                         | <b>21</b> |

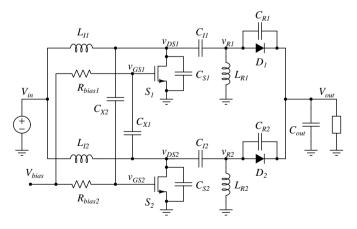

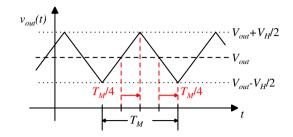

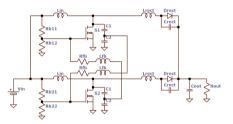

|         | 3.1        | Principle of Operation                                                       | 21        |

|         | 3.2        | Design Considerations                                                        | 22        |

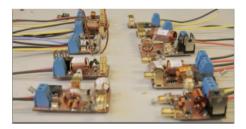

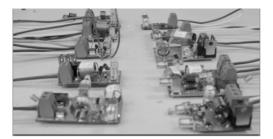

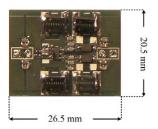

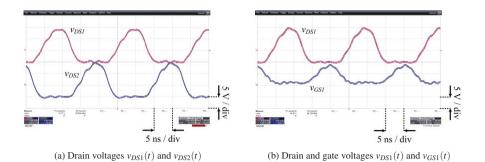

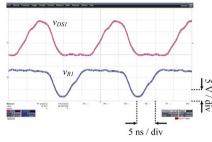

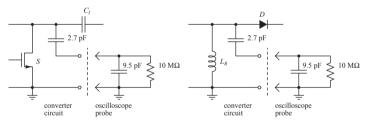

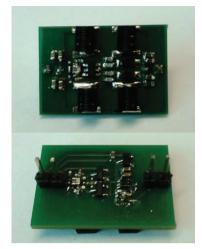

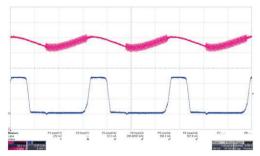

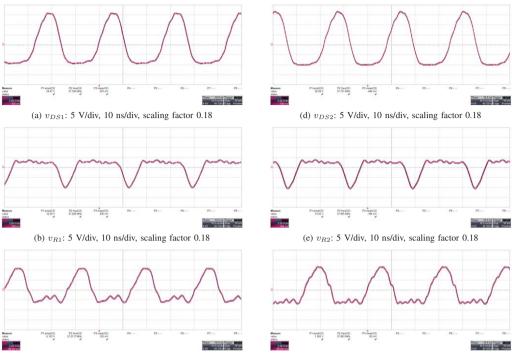

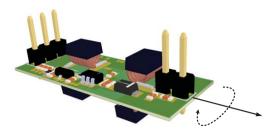

|         | 3.3        | Experimental Results                                                         | 23        |

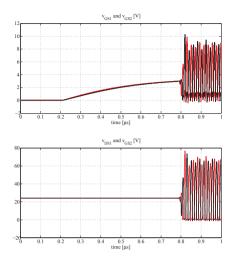

| 4       | Pha        | sse-Shift Burst-Mode Control                                                 | <b>25</b> |

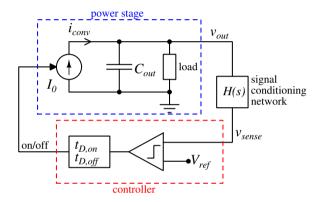

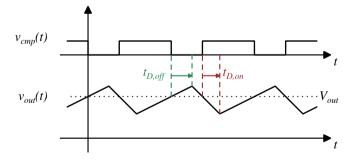

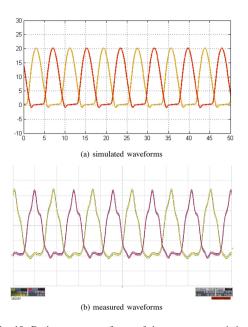

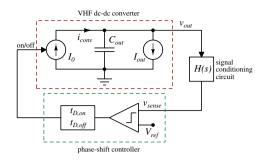

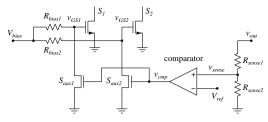

|         | 4.1        | Principle of Operation                                                       | 25        |

|         | 4.2        | Design Considerations                                                        | 27        |

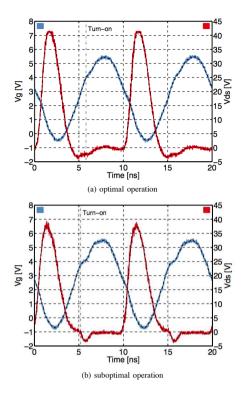

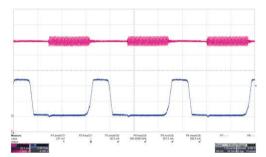

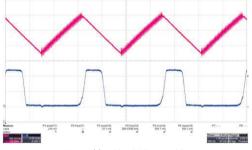

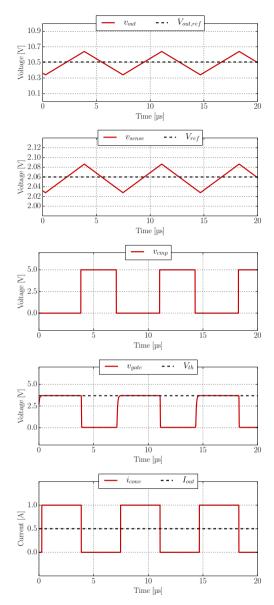

|         | 4.3        | Experimental Results                                                         | 27        |

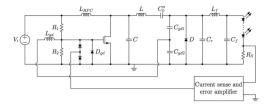

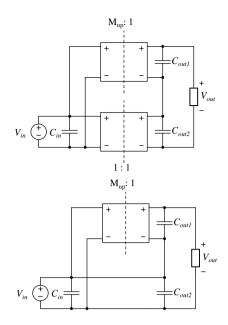

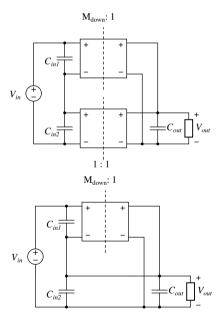

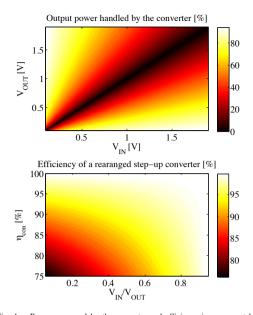

| 5       | Cel        | l Stacking                                                                   | 29        |

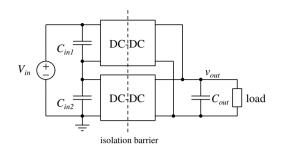

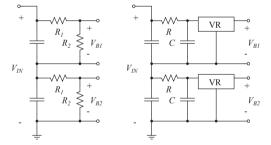

|         | 5.1        | Two-Cell Stack                                                               | 29        |

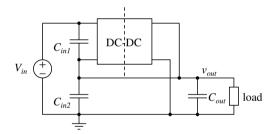

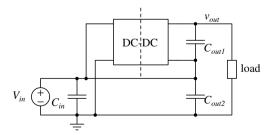

|         | 5.2        | Modified Stack                                                               | 30        |

|         | 5.3        | Design Considerations                                                        | 32        |

|         | 5.4        | Experimental Results                                                         | 32        |

| 6       | Cor        | clusion and Future Work                                                      | 35        |

|         | 6.1        | Conclusion                                                                   | 35        |

|         | 6.2        | Perspectives on Future Research                                              | 36        |

|         |            | •                                                                            |           |

| Bi      | bliog      |                                                                              | 37        |

|         | bliog      | graphy                                                                       | 37 $43$   |

| Aj      | ppen       | graphy                                                                       | 43        |

| Aj<br>A | ppen<br>On | graphy<br>dix<br>the Ongoing Evolution of Very High Frequency Power Supplies | 43        |

| verters | ì |

|---------|---|

|---------|---|

| D | Very High Frequency Interleaved Self-Oscillating Resonant SEPIC Converter                          | ;<br>71  |

|---|----------------------------------------------------------------------------------------------------|----------|

| Е | A VHF Interleaved Self-Oscillating Resonant SEPIC Converter<br>with Phase-Shift Burst-Mode Control | 81       |

| F | Phase-Shift Control For Very High Frequency DC-DC Converters                                       | 89       |

| G | VHF Series-Input Parallel-Output Interleaved Self-Oscillating Resonant SEPIC Converter             | -<br>101 |

| н | Input-Output Rearrangement of Isolated Converters                                                  | 107      |

# List of Figures

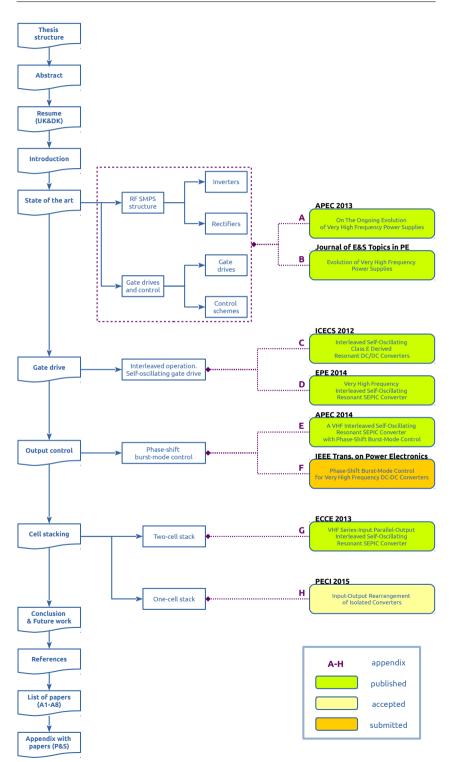

| 1.1  | PhD thesis structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

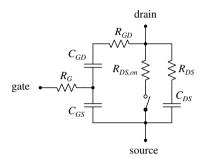

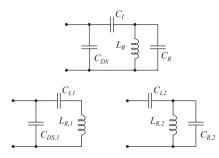

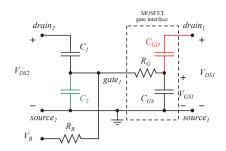

| 2.1  | MOSFET device model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6  |

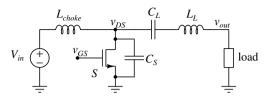

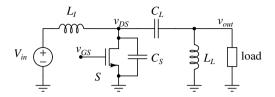

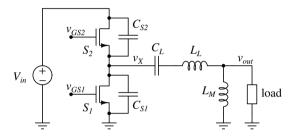

| 2.2  | Class E inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7  |

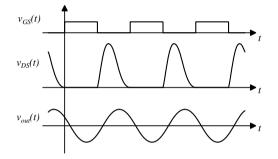

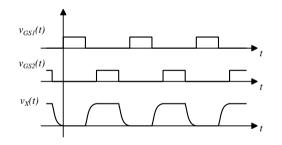

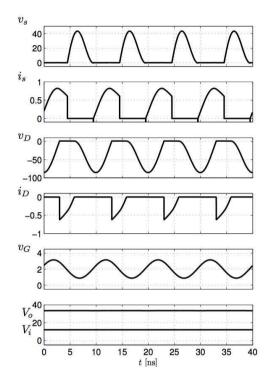

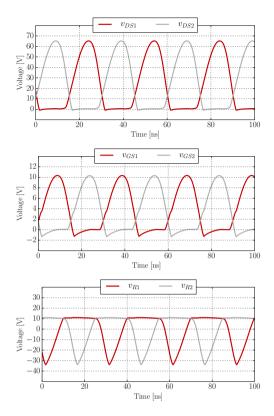

| 2.3  | Typical waveforms of the class E inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7  |

| 2.4  | Class E inverter, alternative configuration with resonant input in-<br>ductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8  |

| 2.5  | ${\rm Class}\; {\rm EF}_2 \; {\rm inverter}. \; \ldots \; $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8  |

| 2.6  | Typical waveforms of the class $\mathrm{EF}_2$ inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8  |

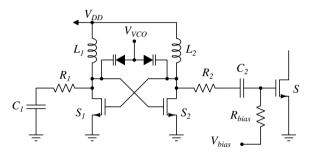

| 2.7  | Class DE inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9  |

| 2.8  | LLC inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9  |

| 2.9  | Typical waveforms of a half-bridge resonant inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9  |

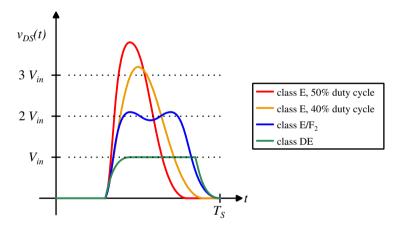

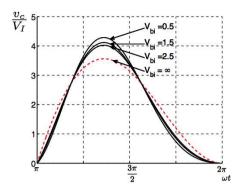

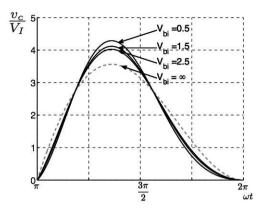

| 2.10 | Peak MOSFET voltage stress comparison for class E, $EF_2$ , and DE inverter topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 |

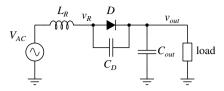

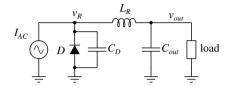

| 2.11 | Class E low $dv/dt$ rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 |

| 2.12 | Class E low $di/dt$ rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 |

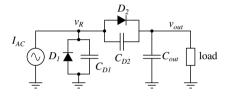

| 2.13 | Class DE half-wave rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11 |

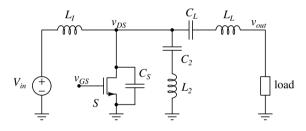

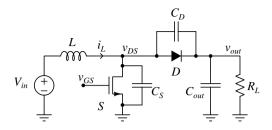

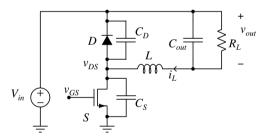

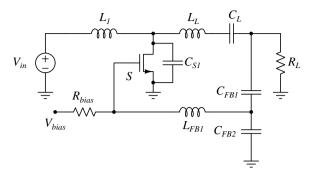

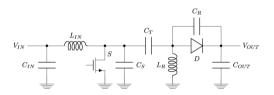

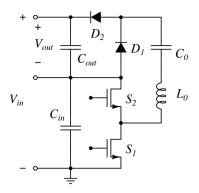

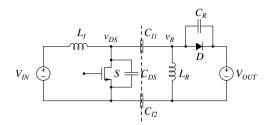

| 2.14 | Quasi-resonant boost dc-dc converter. $\hfill \ldots \hfill \ldots$ | 12 |

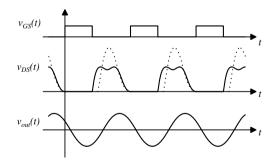

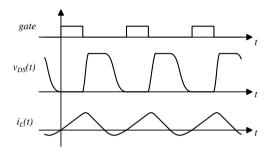

| 2.15 | Quasi-resonant converter waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12 |

| 2.16 | Quasi-resonant buck dc-dc converter with a low-side switch and non-<br>grounded load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12 |

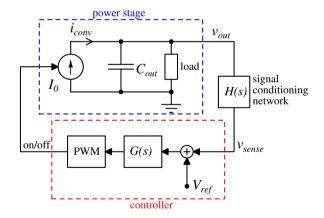

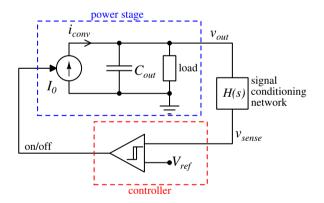

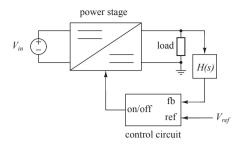

| 2.17 | Low frequency model of a VHF converter with PWM control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13 |

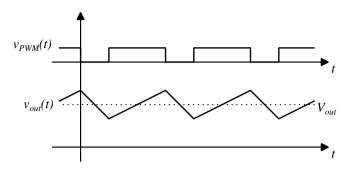

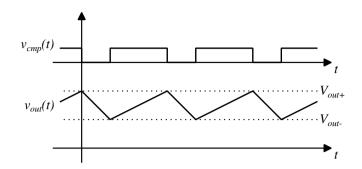

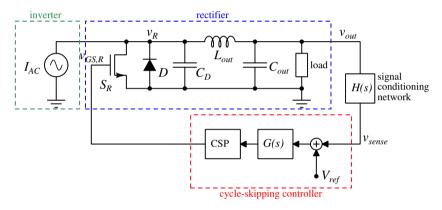

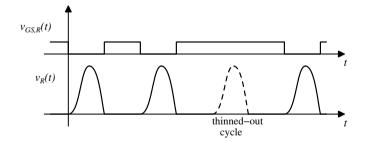

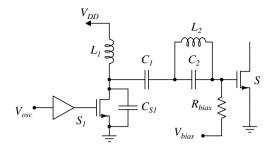

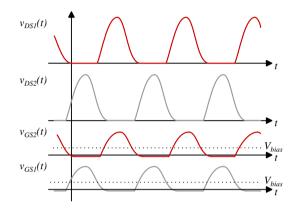

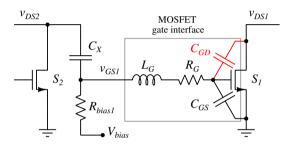

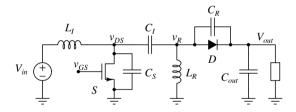

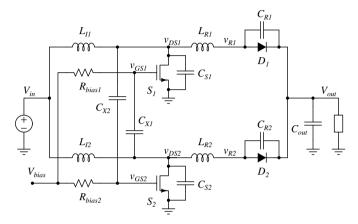

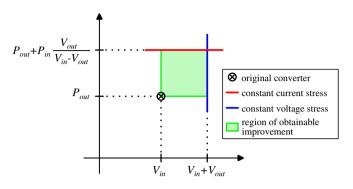

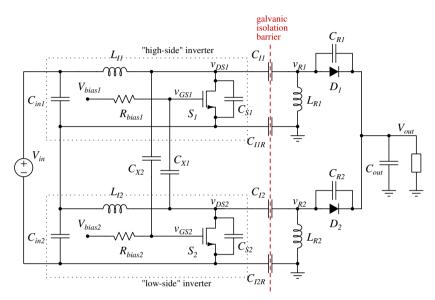

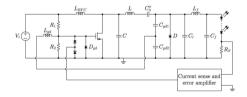

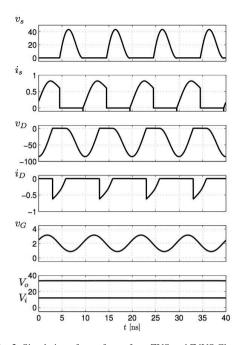

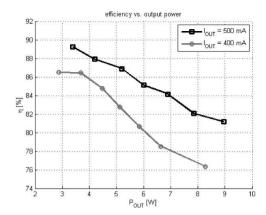

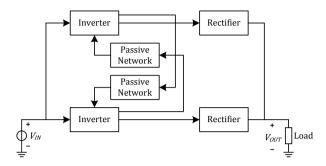

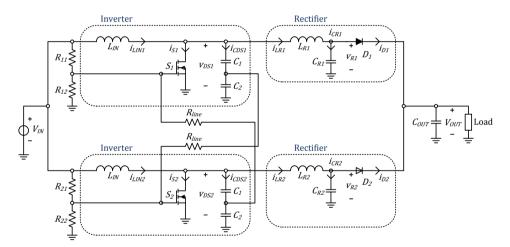

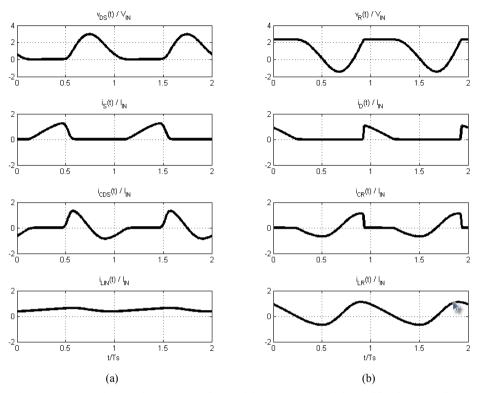

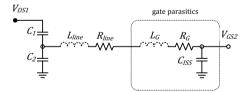

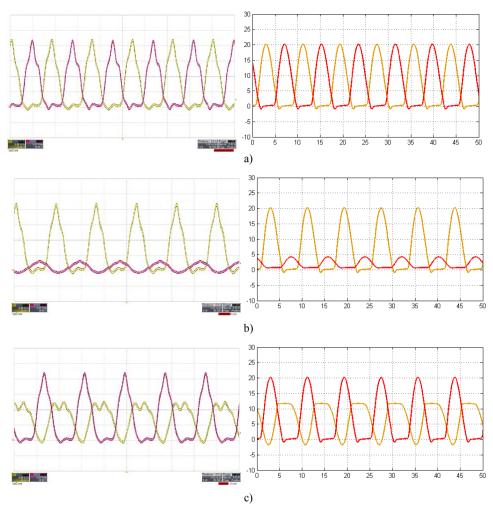

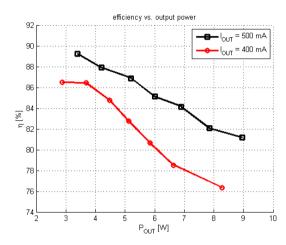

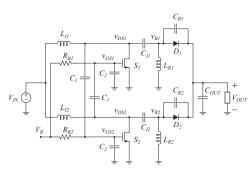

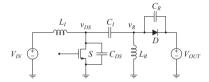

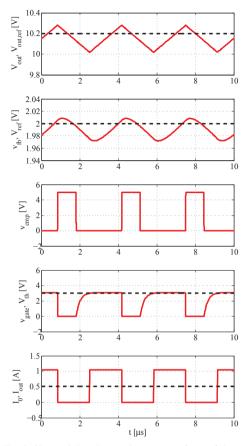

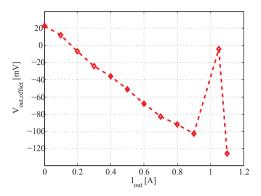

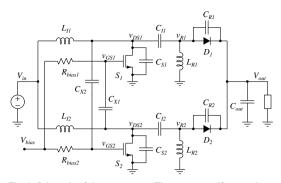

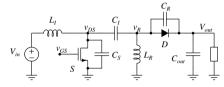

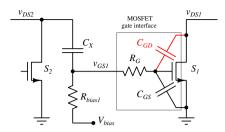

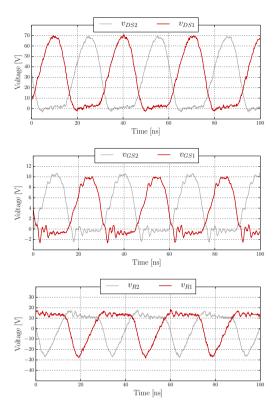

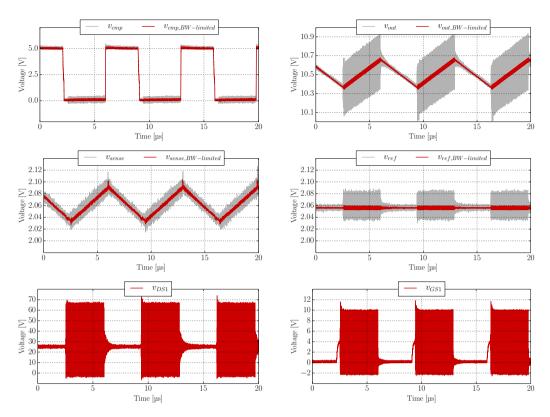

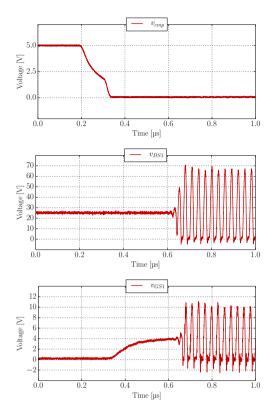

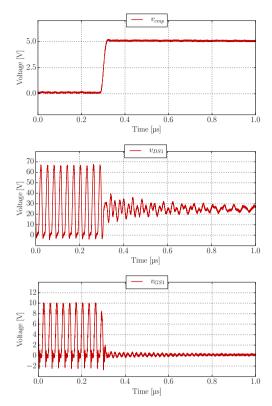

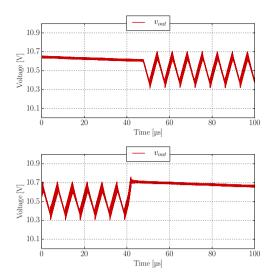

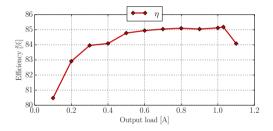

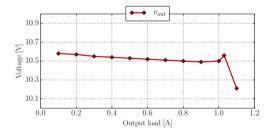

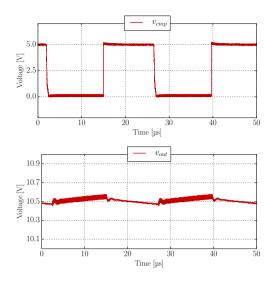

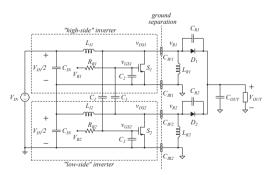

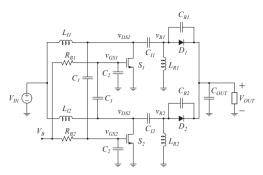

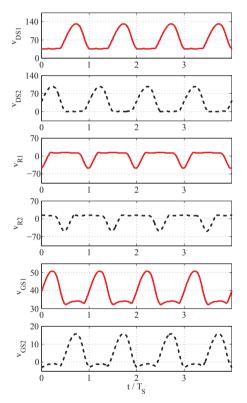

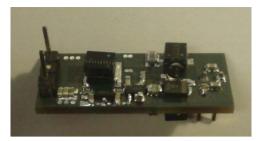

| 2.18 | Typical waveforms of a VHF converter with PWM control. $\hdots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14 |