Downloaded from orbit.dtu.dk on: Apr 20, 2024

**DTU Library**

#### **Advances in PV Inverters**

Anthon, Alexander

Publication date: 2015

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Anthon, A. (2015). *Advances in PV Inverters*. Technical University of Denmark, Department of Electrical Engineering.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Technical University of Denmark

Jeremy Alexander Anthon

## **Advances in PV Inverters**

PhD thesis, October 2015

Jeremy Alexander Anthon

## **Advances in PV Inverters**

PhD thesis, October 2015

Advances in PV Inverters,

#### This report was prepared by

Jeremy Alexander Anthon

#### **Supervisors**

Michael A. E. Andersen Zhe Zhang

Release date: October 2015 Category: 1 (public)

Edition: Final

Comments: This report is part of the requirements to achieve the Doctor of

Philosophy in Electrical Engineering at the Technical University

of Denmark.

Rights: ©Jeremy Alexander Anthon, 2015

Department of Electrical Engineering Electronics Group (ELE) Technical University of Denmark Elektrovej, Building 325 DK-2800 Kgs. Lyngby Denmark

http://www.ele.elektro.dtu.dk Tel: (+45) 45 25 25 25

### **Abstract**

Renewable energies have experienced a significant growth and importance in the last two decades, of which energy from photovoltaic plants are a major contributor. Since solar cells have low efficiencies themselves, however, the necessity of high efficiency power converters at low cost and preferably low complexity leads to new research demands. This is especially true in the field of low cost residential PV inverters where efficiencies are used as major selling arguments. Traditional converter topologies equipped with conventional Silicon based semiconductors to date reach their limitations and new approaches are necessary. Therefore, research areas typically focus on both new topologies and utilizing more advanced semiconductor devices.

To this end, semiconductor devices made of Silicon Carbide have been gaining increasing interest in the last two decades after the successful commercialization of high voltage power diodes. By now, the performance potential of switching devices made of Silicon Carbide is commonly accepted, though they have not found commonplace usage within commercial converter systems for several reasons, among others reliability, availability/cost and gate driver complexity. Therefore, more complex Silicon based converters can be used instead to achieve lower semiconductor losses.

While there is no absolute solution in which direction to go to achieve the aforementioned design goals, this dissertation will thoroughly investigate two potential approaches and discuss their trade-offs.

#### The contributions are:

- Comprehensive loss analysis and identification of major loss contributors within T-Type converter topology operating in inverter and rectifier context.

- Evaluation of the use and loss benefits of Silicon Carbide switching devices in the T-Type structure.

- Thorough investigation of the Hybrid-Neutral-Point-Clamped (Hybrid-NPC) topology as an alternative for the Silicon Carbide based T-Type converter.

- Alternative methodology of semiconductor loss model validation by experimental means.

As to the advanced three-level T-Type converter topology, its unusual operation

mode is thoroughly described identifying its limitations for high efficiency operation. With these results, the first approach utilizes low loss switching devices and their influence on the semiconductor loss behavior is analyzed. The results show that, for near unity power factor operation, a replacement of only two switching devices per phase leg can greatly reduce the semiconductor losses.

The Hybrid-NPC converter can be seen as an attractive and cost competitive alternative to the Silicon Carbide based converter, also allowing to overcome the major drawbacks with the conventional Silicon IGBT based T-Type structure.

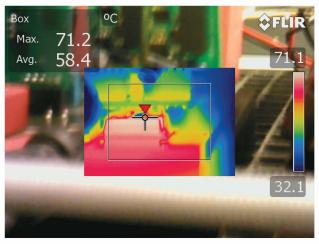

Both alternatives are based on a semiconductor/topological level and thus this is where the loss reduction occurs. The difficulty in experimentally evaluating only the semiconductor losses within a converter operating context is addressed in this work by presenting an alternative measurement approach. Using known heat loads, and a careful calibration procedure on the device heat sink, analytically obtained semiconductor loss models based on datasheet information and in-circuit switching transitions measurements can be experimentally verified and thus a fair performance comparison between two approaches is enabled.

### Resumé

Vedvarende energi har oplevet en markant vækst og betydning i de sidste to årtier, hvoraf energi fra solcelleanlæg er en stor bidragyder. Idet solcellerne har lav effektivitet og efterspørgslen af højeffektive konverter med lave omkostninger og fortrinsvis lav kompleksitet er stigende, medfører dette nye forskningskrav. Dette er især tilfældet inden for billige solcellekonvertere til boliger, hvor effektiviteten anvendes som et større salgsargument. Traditionelle konverter-topologier har til dato nået deres begrænsninger og nye løsninger er nødvendige. Derfor har forskningsområderne typisk fokus på både nye topologier og anvendelse af mere avancerede halvledere.

Til dette formål har halvlederkomponenter lavet af siliciumkarbid (SiC) vundet stigende interesse i de sidste to årtier efter den vellykkede kommercialisering af SiC-højspændingsdioder. På nuværende tidspunkt, er halvledere fremstillet af SiC almindeligt accepteret, selv om SiC halvledere af flere grunde ikke er almindelige i kommercielle konverter systemer. Dette begrundes i deres upålidelighed, tilgængelighed / omkostninger og gate driver kompleksitet. Derfor kan mere komplekse konvertere være et attraktivt alternative til opnå et mindre tab.

Der er ingen absolut løsning for i hvilken retning man skal gå for at opnå de førnævnte designmål. Denne afhandling indeholder en grundig undersøgelse af to potentielle muligheder og diskutere deres fordele og ulemper. De forskningsmæssige bidrag er:

- Omfattende tabsanalyse og identifikation af de store tabsbidrag indenfor T-Type inverter og ensretter-drift konteksten

- Evaluering af brugen af og tabsfordelene ved SiC-halvledere i T-Type konverter

- Grundig undersøgelse af Hybrid-Neutral-Point-Clamped (NPC) som et alternativ til SiC-baserede T-Type konverter

- Præsentation af en alternativ metode til at måle halvlederes tab

T-Type konverterens usædvanlige driftstilstand vil blive beskrevet, hvormed begrænsningerne for høj effektivitet er identificeret. Disse resultater bruges til at undersøge anvendelse af halvledere lavet af SiC og deres tab i T-Type konverteren.

Resultaterne viser, at når effektfaktoren er tæt på én, er det kun nødvendigt at udskifte to halvledere til SiC. Hybrid-NPC konverteren kan ses som et attraktiv og effektivt konkurrencedygtigt alternativ til SiC T-Type konverteren. Hybrid-NPC konverteren gør det også muligt at overvinde de store ulemper med den konventionelle silicium (Si) IGBT-baserede T-Type konverter. Begge alternativer er baseret på et halvleder / topologisk grundlag, og det er her at tabet reduceres. Vanskeligheden i at måle tab i halvlederne i de forskellige T-Typer konvertere bliver diskuteret og et alternativt måleprincip er præsenteret. Ved brug af kendte varmebelastninger og en præcis kalibreringsprocedure på halvlederens køleplade, bliver det muligt at validere halvledernes tabsmodeller med målinger. Dermed er en fair sammenligning imellem de to løsninger mulig.

### **Preface**

This PhD project Advances in PV Inverters is part of the Intelligent Efficient Power Electronics (IEPE) research program, in which Danish universities and companies collaborate to achieve more sophisticated power electronic systems. It gave me the chance to explore and extend my knowledge within power electronics in photovoltaic inverters and to participate in interesting and challenging dialogues with experts in this field.

My deepest gratitude is to my supervisors Michael A. E. Andersen and Zhe Zhang at the Department of Electrical Engineering, Technical University of Denmark, who gave me the opportunity to conduct the PhD project at the Electronics Group of DTU. I further appreciate their support and their consistent encouragement that helped me finish this project.

I am very thankful to be part of this excellent work environment and I would like to gratefully and sincerely thank all my friends and colleagues in the Electronics Group at DTU. I would like to give my special appreciation to Pere, Juan and Maria, Gabriel and Kristian for the enjoyable time in the department as well as during conferences. Last but not least, I would like to thank our group secretary Henriette, our former engineer assistant Bertil and our current engineer assistant Hans-Christian.

I am thankful to Professor Grahame Holmes and Associate Professor Brendan Mc-Grath for accepting me as a visiting student at their Power and Energy Research Group at RMIT University in Melbourne, Australia, and deep gratitude goes to Dr. Carlos Teixeira for the very supportive help during the laboratory work.

Finally, I would like to thank my family and friends for their support and encouragement, and their love, which helped me go through this kind of work.

## **Contents**

| A            | bstra | act                                                 | ii           |

|--------------|-------|-----------------------------------------------------|--------------|

| $\mathbf{R}$ | esum  | né                                                  | iv           |

| P            | refac | $\mathbf{e}$                                        | $\mathbf{v}$ |

| $\mathbf{C}$ | onter | nts                                                 | vii          |

| A            | crony | yms                                                 | хi           |

| Li           | st of | Figures                                             | iii          |

| Li           | st of | Tables x                                            | vii          |

| 1            | Intr  | $\operatorname{roduction}$                          | 1            |

|              | 1.1   | Scope                                               | 1            |

|              | 1.2   | Motivation                                          | 1            |

|              | 1.3   | Project objectives                                  | 2            |

|              | 1.4   | Structure                                           | 3            |

| 2            | Ove   | erview and state-of-the-art                         | 5            |

|              | 2.1   | Photovoltaic systems and DC/AC converter topologies | 5            |

|              | 2.2   | Wide bandgap devices                                | 9            |

|              | 2.3   | Summary                                             | 11           |

| 3            | Top   | pological Comparison of Three-Level Converters      | 13           |

|              | 3.1   | NPC converter                                       | 16           |

|              | 3.2   | T-Type converter                                    | 16           |

|    | 3.3    | Efficiency comparison                                                | 16 |

|----|--------|----------------------------------------------------------------------|----|

|    | 3.4    | Summary                                                              | 17 |

| 4  | Effi   | ciency Improvements in the T-Type Structure                          | 19 |

|    | 4.1    | Using SiC switching devices                                          | 19 |

|    |        | 4.1.1 Advantages and Challenges with SiC Switching Devices $$        | 20 |

|    |        | 4.1.2 Conduction losses                                              | 22 |

|    |        | 4.1.3 Switching losses                                               | 23 |

|    |        | 4.1.4 Loss breakdown analysis                                        | 25 |

|    |        | 4.1.5 Use of SiC in T-Type Inverter                                  | 29 |

|    | 4.2    | Using 600 V Si Switching Devices / Hybrid-NPC                        | 32 |

|    | 4.3    | Experimental results - Loss Model Validation by Thermal Measurements | 35 |

|    | 4.4    | Comparative Study on these two Alternatives                          | 38 |

|    |        | 4.4.1 Loss comparison                                                | 38 |

|    |        | 4.4.2 Cost comparison                                                | 44 |

|    |        | 4.4.3 Price discussion on SiC based converter                        | 46 |

|    | 4.5    | Summary                                                              | 48 |

| 5  | Des    | ign Alternatives                                                     | 49 |

|    | 5.1    | Efficiency Improvements and Reliability                              |    |

|    | 5.2    | Increased Output Power Rating                                        |    |

|    | 5.3    | Heat Sink Size Reduction                                             |    |

|    | 5.4    | Filter Size Reduction                                                |    |

|    | 5.5    | Summary                                                              |    |

| 6  | Cor    | nclusion                                                             | 55 |

| 7  | Fut    | ure work                                                             | 57 |

|    | 7.1    | Optimization of Hybrid-NPC Converter                                 | 57 |

|    | 7.2    | Inductor redesign                                                    | 58 |

|    | 7.3    | EMC                                                                  | 58 |

|    | 7.4    | High switching frequency operation                                   | 58 |

| P: | iblios | ranhy.                                                               | 61 |

|    |        |                                                                      |    |

| Aı           | ppendix                                                                                                                                      | 71         |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|

| $\mathbf{A}$ | Calibration Procedure of Thermal Measurements                                                                                                | 71         |

| В            | Comparison of $600\mathrm{V}$ devices                                                                                                        | <b>7</b> 5 |

| $\mathbf{C}$ | Equations for semiconductor average and RMS current calculations                                                                             | 77         |

|              | C.1 Average and RMS currents for boost converter                                                                                             | 77         |

|              | C.2 Average and RMS currents for T-Type converter                                                                                            | 78         |

|              | C.3 Average and RMS currents for Hybrid-NPC converter                                                                                        | 78         |

| D            | Efficiency Investigations of a $3\mathrm{kW}$ T-Type Inverter for Switching Frequencies up to $100\mathrm{kHz}$                              | 81         |

| ${f E}$      | Switching Investigations on a SiC MOSFET in a TO-247 Package                                                                                 | 89         |

| ${f F}$      | Comprehensive Loss Evaluation of Neutral-Point-Clamped (NPC) and T-Type Three-Level Inverters based on a Circuit Level Decoupling Modulation |            |

| G            | Efficiency Evaluation on a CoolMos Switching and IGBT Conducting Multilevel Inverter                                                         | 105        |

| Н            | Comparison of a State of the Art Si IGBT and Next Generation<br>Fast Switching Devices in a 4kW Boost Converter                              | 111        |

| Ι            | The Benefits of SiC MOSFETs in a T-Type Inverter for Grid-Tie Applications                                                                   | 121        |

| J            | Analysis and Comparison of Si and SiC Power Devices on a Grid-<br>Tie Fuel Cell Energy Storage System                                        | 133        |

| K            | Comparative Evaluation of the Loss and Thermal Performance of<br>Advanced Three Level Inverter Topologies                                    | 141        |

## **Acronyms**

AC Alternating Current

ANPC Active Neutral-Point-Clamped

BSNPC Bipolar-Switched-Neutral-Point-Clamped

**CM** Common Mode

**DC** Direct Current

**DPT** Double Pulse Test

**DPWM** Discontinuous Pulse Width Modulation

EMC Electromagnetic Compability

EMI Electromagnetic Interference

**EV** Electric Vehicle

FC Flying Capacitor

**FEM** Finite Element Method

FIT Feed-in Tariff

GaN Gallium Nitride

IGBT Insulated-Gate-Bipolar-Transistor

NPC Neutral-Point-Clamped

**PD** Phase Disposition

PV Photovoltaic

**RMS** Root Mean Square

Si Silicon

SiC Silicon Carbide

**SPWM** Sine Pulse Width Modulation

**SVM** Space Vector Modulation

$\mathbf{VSC}$  Voltage Source Converter

$\mathbf{VSD}$  Variable Speed Drive

## **List of Figures**

| 1.1 | Global PV capacity                                                                                                                                                                                                                 | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Thesis outline                                                                                                                                                                                                                     | 4  |

| 2.1 | PV systems for different power levels                                                                                                                                                                                              | 5  |

| 2.2 | Block diagram of a transformer-less PV system                                                                                                                                                                                      | 6  |

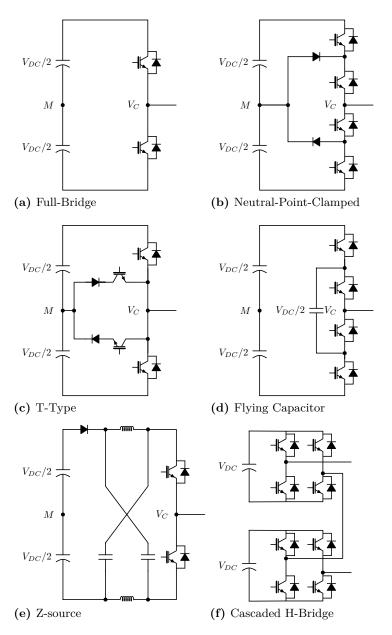

| 2.3 | One phase leg of each suitable topology. In (a) the Full-Bridge inverter, in (b) the NPC inverter, in (c) the T-Type inverter, in (d) the Flying Capacitor inverter, in (e) the Z-source inverter and in (f) the cascaded H-Bridge | 7  |

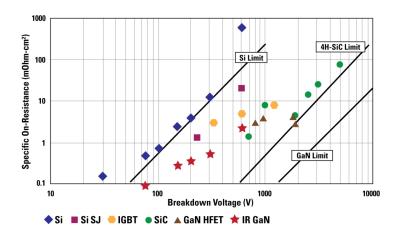

| 2.4 | Specific on-state resistance comparison of Si, SiC and GaN $\ \ldots \ \ldots$                                                                                                                                                     | 10 |

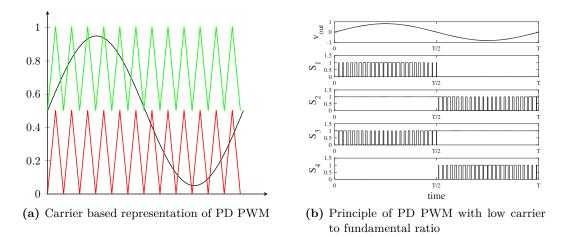

| 3.1 | Phase Disposition (PD) PWM as the chosen modulation principle .                                                                                                                                                                    | 13 |

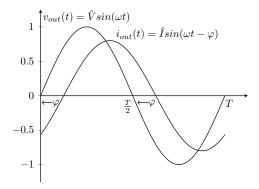

| 3.2 | Output voltage and output current                                                                                                                                                                                                  | 14 |

| 3.3 | Switching states for T-Type inverter (left-hand side) and NPC inverter (right-hand side) operating at unity power factor                                                                                                           | 15 |

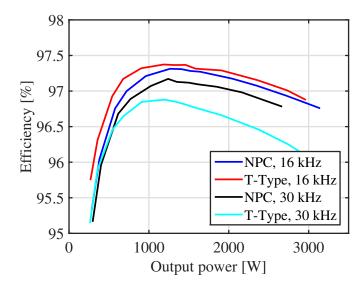

| 3.4 | Measured efficiencies of NPC and T-Type for different switching frequencies and output power                                                                                                                                       | 17 |

| 4.1 | Schematic of the gate driver circuits                                                                                                                                                                                              | 21 |

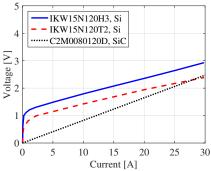

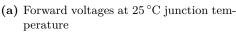

| 4.2 | Forward voltages at different current levels and junction temperatures                                                                                                                                                             | 23 |

| 4.3 | On-state resistances versus junction temperature                                                                                                                                                                                   | 23 |

| 4.4 | Double pulse test circuit for switching energy measurements                                                                                                                                                                        | 24 |

| 4.5 | SiC MOSFET turn on commutation in (a) and associated losses in (b)                                                                                                                                                                 | 24 |

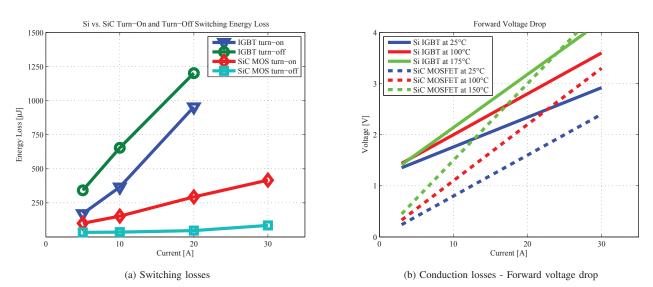

| 4.6 | Measured switching energies for different current levels and a junction temperature of $25^{\circ}\mathrm{C}$                                                                                                                      | 24 |

| 4.7 | Schematic of a conventional boost converter                                                                                                                                                                                        | 25 |

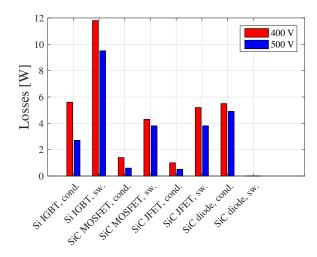

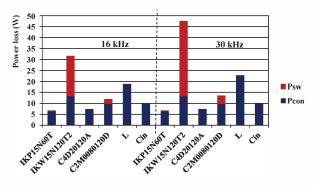

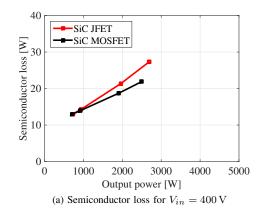

| 4.8  | Semiconductor loss breakdown analysis in the boost converter operating at $20\mathrm{kHz}$ switching frequency and an output power of $2.5\mathrm{kW}$ .       | 27 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

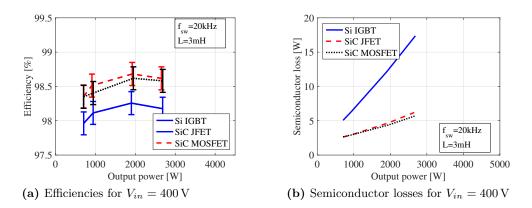

| 4.9  | Measured efficiencies and calculated semiconductor losses for $400\mathrm{V}$ input voltage and $700\mathrm{V}$ output voltage $\ldots\ldots\ldots\ldots$      | 27 |

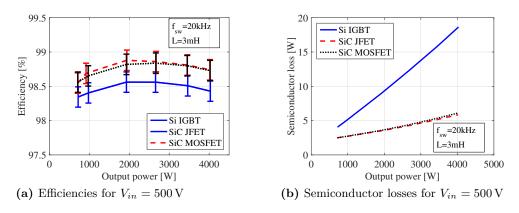

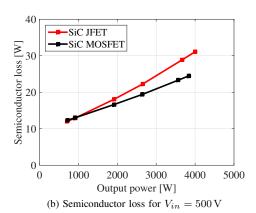

| 4.10 | Measured efficiencies and calculated semiconductor losses for $500\mathrm{V}$ input voltage and $700\mathrm{V}$ output voltage $\ldots\ldots\ldots$            | 27 |

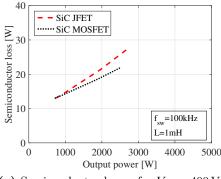

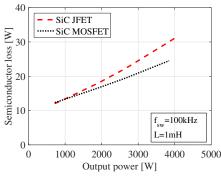

| 4.11 | Semiconductor losses for different output power levels, input voltages and a switching frequency of $100\mathrm{kHz}$                                          | 28 |

| 4.12 | Forward voltage comparison of two $1200\mathrm{V}$ Si IGBTs and a $1200\mathrm{V}$ SiC MOSFET at different current levels and junction temperatures .          | 29 |

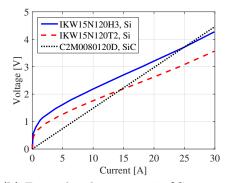

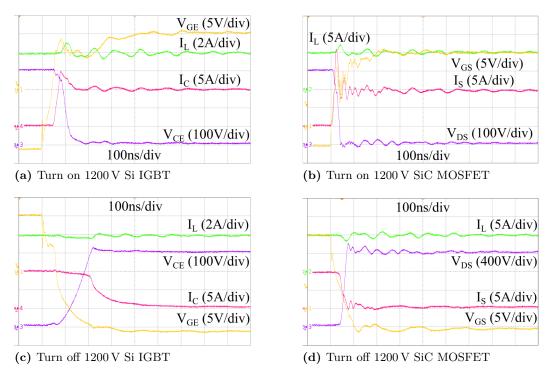

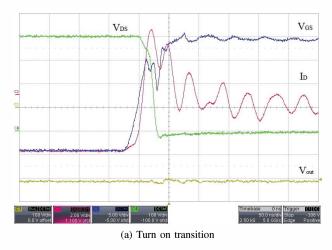

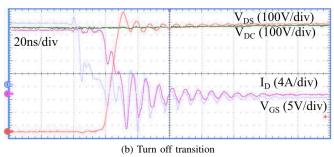

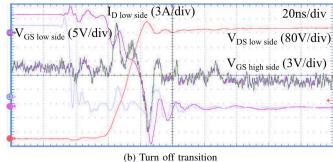

| 4.13 | Turn on and turn off transitions in the T-Type inverter context                                                                                                | 30 |

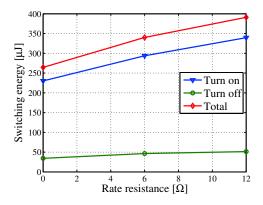

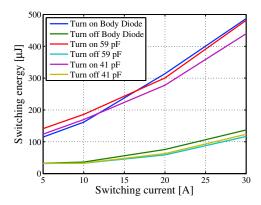

| 4.14 | Measured switching energies of utilized 1200 V devices at a commutation voltage of 400 V $\dots \dots \dots \dots \dots \dots$ .                               | 31 |

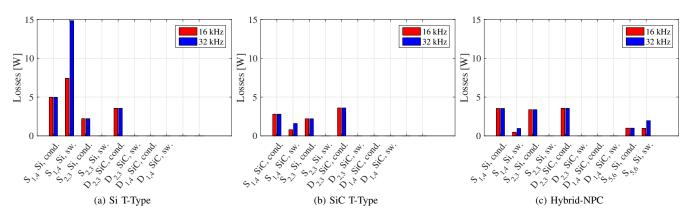

| 4.15 | Loss breakdown analysis comparison for Si IGBT and SiC MOSFET based inverter                                                                                   | 32 |

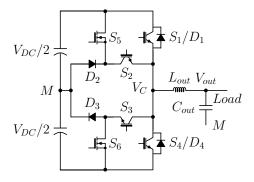

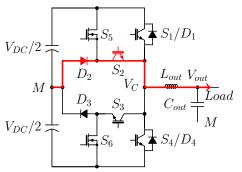

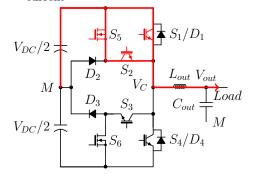

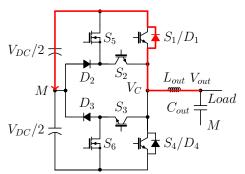

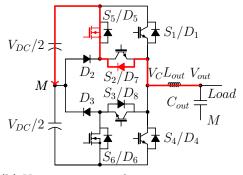

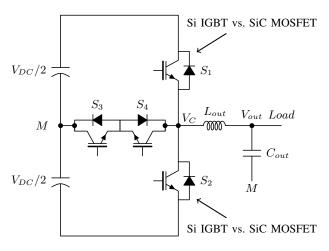

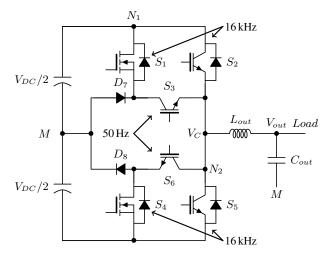

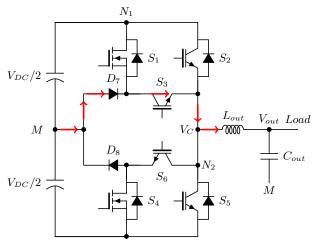

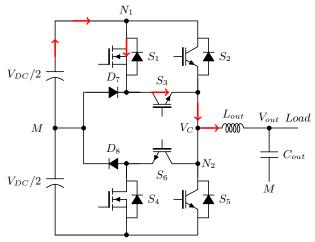

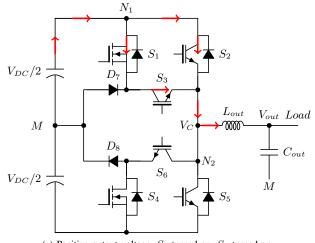

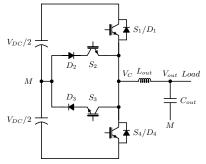

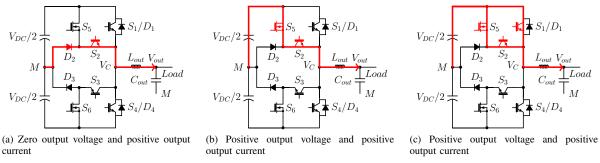

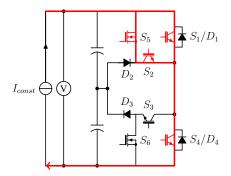

| 4.16 | Hybrid-NPC topology                                                                                                                                            | 32 |

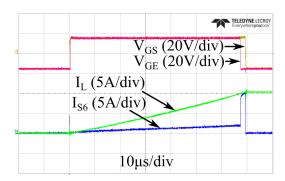

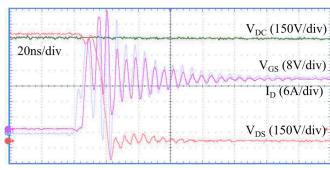

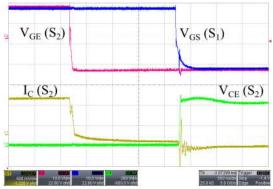

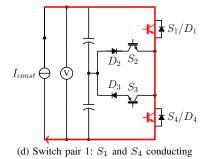

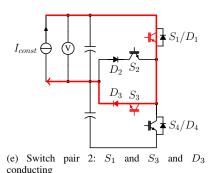

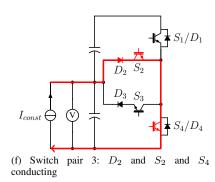

| 4.17 | Switching transition from zero to positive output voltage in Hybrid-NPC inverter                                                                               | 33 |

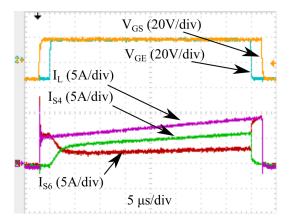

| 4.18 | Inductor current and current through $S_6$ when both $S_6$ and $S_4$ are turned on                                                                             | 34 |

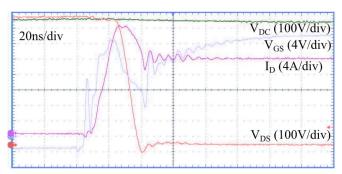

| 4.19 | Induced current in $S_4$ in (a) and its associated switching energies in (b)                                                                                   | 34 |

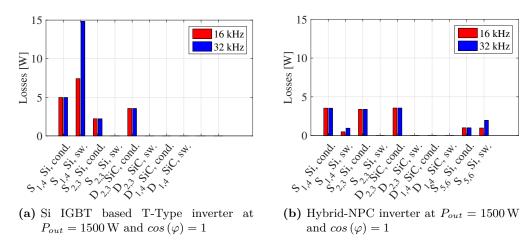

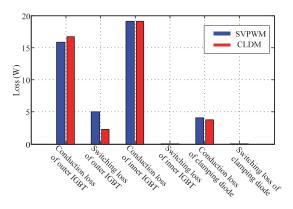

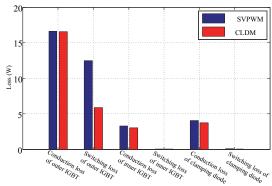

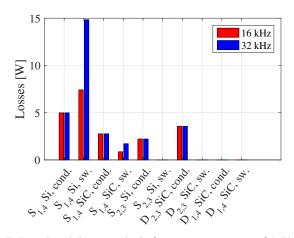

| 4.20 | Semiconductor loss breakdown analysis of conventional T-Type inverter in (a) and Hybrid-NPC inverter in (b)                                                    | 35 |

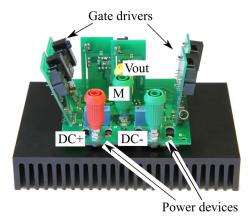

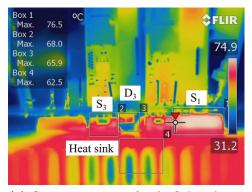

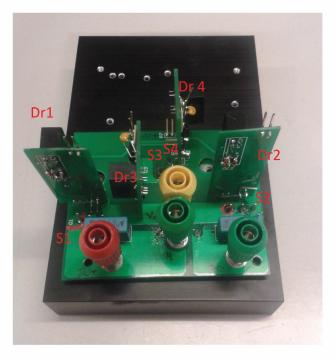

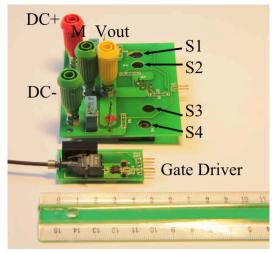

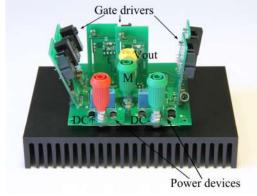

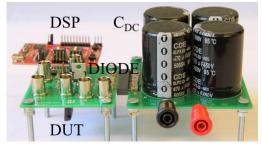

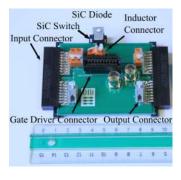

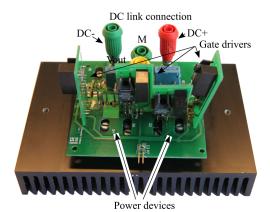

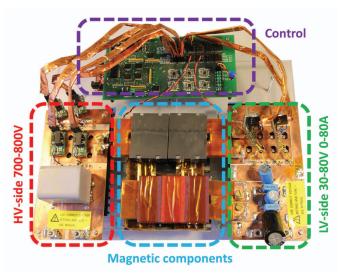

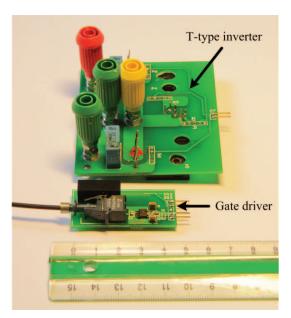

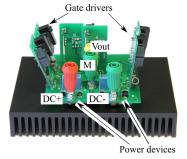

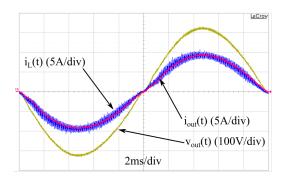

| 4.21 | Photograph of the final laboratory protytpe                                                                                                                    | 36 |

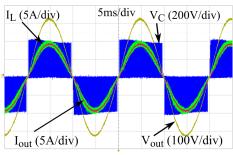

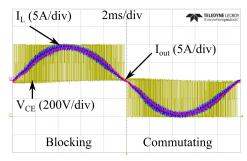

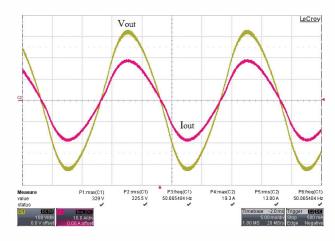

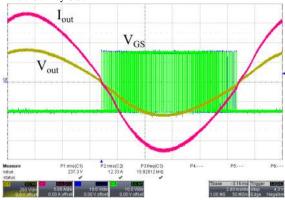

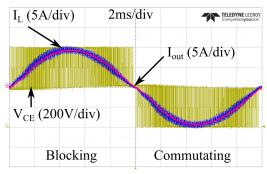

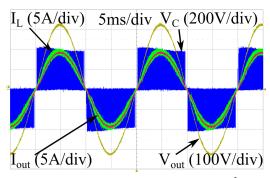

| 4.22 | Experimental waveforms of the converter operating at full load                                                                                                 | 37 |

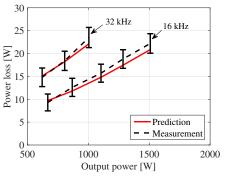

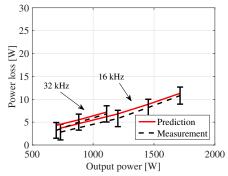

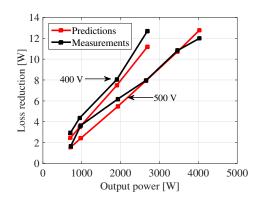

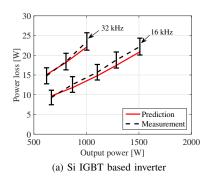

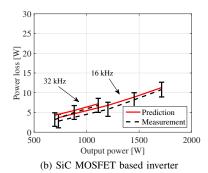

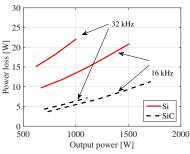

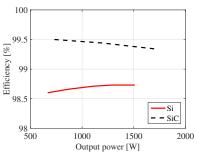

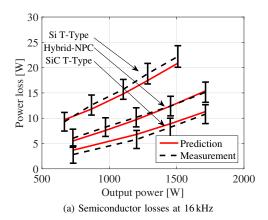

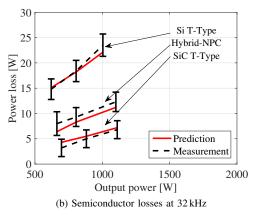

| 4.23 | Predicted and measured semiconductor losses for different converter alternatives                                                                               | 37 |

| 4.24 | Current flow for non-unity power factors                                                                                                                       | 39 |

| 4.25 | Switching states for T-Type inverter operating at unity power factor                                                                                           | 39 |

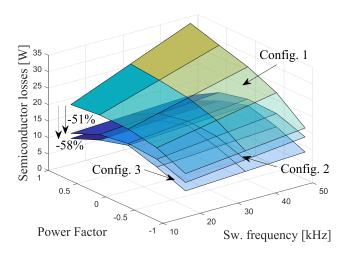

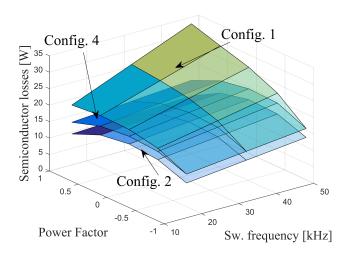

| 4.26 | Si based T-Type in configuration 1 compared to $1200\mathrm{V}$ SiC MOSFET T-Type in configuration 2 and a full SiC based T-Type inverter in configuration $3$ | 40 |

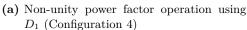

| 4.27 | Possible current flows for non-unity power factors in the Hybrid-NPC structure                                                                                 | 41 |

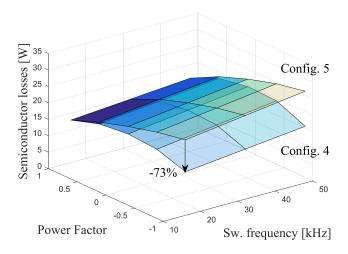

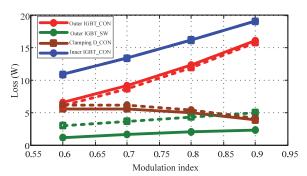

| 4.28 | Loss comparison of configuration 4 and configuration 5 using two different current paths from Fig. 4.27                                                        | 42 |

| 4.29 | Loss comparison of the Si and SiC based T-Type converters and the Hybrid-NPC converter                                                                                                                       | 42 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

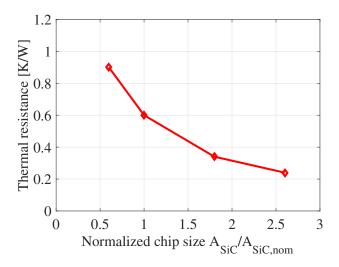

| 4.30 | Thermal resistance against different chip sizes                                                                                                                                                              | 47 |

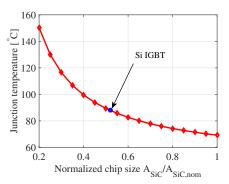

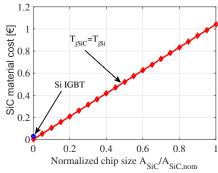

| 4.31 | Junction temperature against chip size in (a) and material cost against chip size in (b) $\dots \dots \dots$ | 47 |

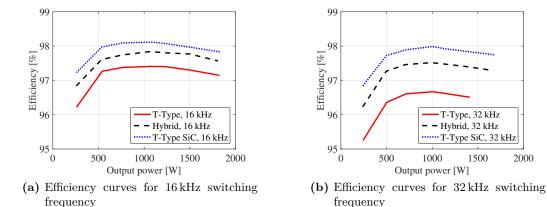

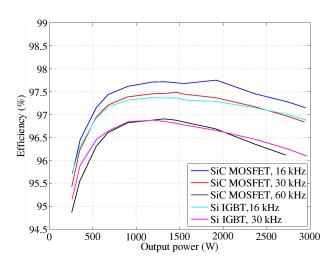

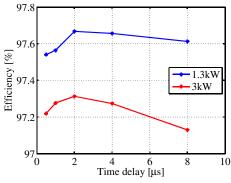

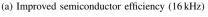

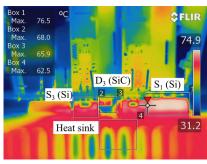

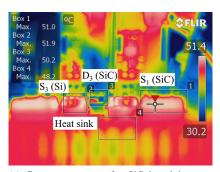

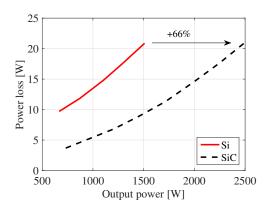

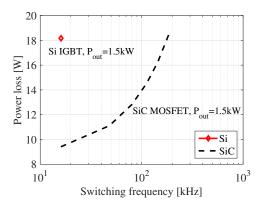

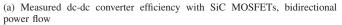

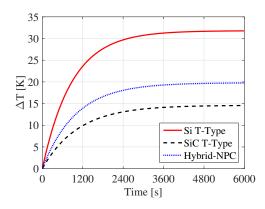

| 5.1  | Measured overall converter efficiencies for different switching frequencies                                                                                                                                  | 49 |

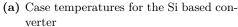

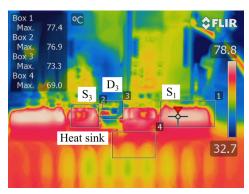

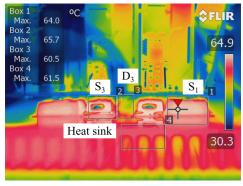

| 5.2  | Case temperature measurements for the Si and SiC alternative $$                                                                                                                                              | 50 |

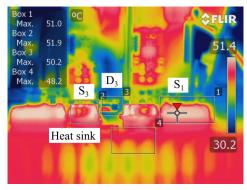

| 5.3  | Possible increase in output power in (a) and resulting case temperature measurements in (b)                                                                                                                  | 51 |

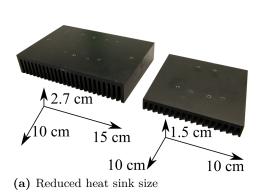

| 5.4  | Reduced heat sink size in (a) and resulting case temperature measurements in (b) $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                               | 51 |

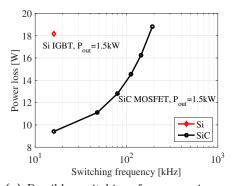

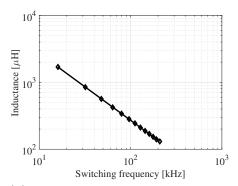

| 5.5  | Semiconductor losses versus switching frequency in (a) and resulting grid side inductance reduction in (b)                                                                                                   | 52 |

| 7.1  | Inductor current and current through $S_6+100\mathrm{m}\Omega$ when both $S_6$ and $S_4$ are turned on                                                                                                       | 58 |

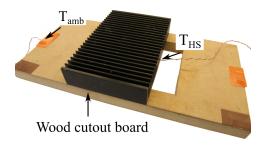

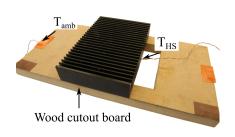

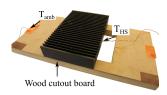

| A.1  | Backside of the converter. Thermal measurements are performed directly on the heat sink $T_{HS}$ and below the heat sink $T_{amb}$                                                                           | 71 |

| A.2  | Front view of converter in open ended chimney in (a) and thermal measurements performed inside in (b) $\dots$                                                                                                | 72 |

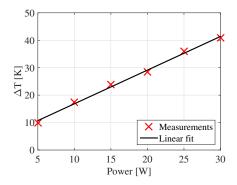

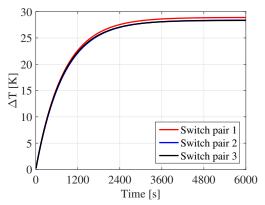

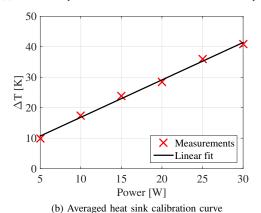

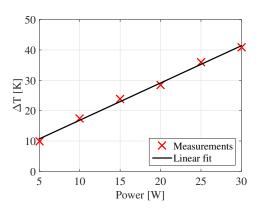

| A.3  | Calibration procedure for heat sink                                                                                                                                                                          | 73 |

| A.4  | Calibration fit                                                                                                                                                                                              | 73 |

| В.1  | Forward voltages for a $600\mathrm{V}$ Si IGBT and a $650\mathrm{V}$ SiC MOSFET at different current levels and junction temperatures                                                                        | 75 |

| B.2  | Switching energies of the utilized $600\mathrm{V}$ Si IGBT and $650\mathrm{V}$ SiC MOSFET for two different junction temperatures                                                                            | 76 |

## **List of Tables**

| 2.1 | Properties of wide-bandgap materials                                                                            | 9  |

|-----|-----------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Switching states for NPC and T-Type converters                                                                  | 14 |

| 4.1 | Semiconductors used                                                                                             | 20 |

| 4.2 | Specifications for boost converter                                                                              | 26 |

| 4.3 | Semiconductor comparison                                                                                        | 28 |

| 4.4 | Specifications inverter                                                                                         | 31 |

| 4.5 | Semiconductor utilization for configurations 1, 2 and 3 according to Fig. 4.24 and Fig. 4.25                    | 40 |

| 4.6 | Semiconductor utilization for configurations 1, 4 and 5 $\dots$                                                 | 41 |

| 4.7 | Loss comparison and loss reduction for different configurations. $P_{out}=1.5\mathrm{kW},f_{sw}=16\mathrm{kHz}$ | 44 |

| 4.8 | Price configuration for the entire power factor range $\cos\left(\varphi\right)=\left[-11\right]$               | 44 |

| 4.9 | Price configuration for unity power factor only, $cos(\varphi) \approx 1 \dots$                                 | 45 |

## Chapter 1

## Introduction

### 1.1 Scope

This thesis presents the results achieved throughout the PhD project entitled Advances in PV Inverters which has been carried out by the author from November 2012 until October 2015. The research outcome has been presented or submitted in form of peer reviewed conference and journal papers. These papers build the basic structure of this thesis and are therefore included in the appendix. This dissertation gives more elaborated insights on the already published information, and thereby presents a more coherent and complete analysis of the research topics in this work. Furthermore, this thesis including its appendix contains a large amount of advanced knowledge on the analysis, design and performance evaluation associated with advanced multilevel inverters and their semiconductor loss profiles.

#### 1.2 Motivation

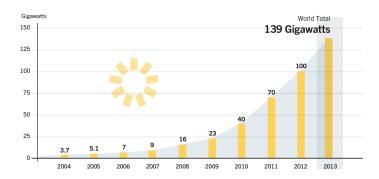

The integration of renewable energy generation in our society has undergone a tremendous development in the last two decades and is still ongoing. In 2012, a contribution of 19% from renewable energies was estimated [1]. Looking at the growth rate, energy coming from Photovoltaic (PV) experiences a significant importance within renewable energies with a record year in 2013 [1]. With 39 GW added in 2013, PV energy reached a total global capacity of 139 GW. The growth of installed PV generation is demonstrated in Fig. 1.1 [1].

The installation of PV in the residential sector has several advantages over other renewable energy resources such as smaller size compared to wind farms, and consequently cost. The high Feed-in Tariff (FIT) in some countries (Germany for instance) further strengthened the attractiveness of PV. Related to the high amount of PV installations (as well as other distributed renewable energy sources), an ongoing development from conventional standalone systems towards systems including energy storage units [2] which can be used for self consumption or grid support becomes more and more attractive. Nevertheless, all solutions have in common

Figure 1.1: Global PV capacity

to have major demand for proper and high efficient grid-connection because solar cells are reported to have low efficiencies themselves (typically in the range of up to 20% [3]). Therefore, loss reduction and thus high efficiencies of the power converters become major design goals for low cost PV systems. To this end, commercial power converters for residential PV systems can show high efficiencies in the range of 98% [4]. Since efficiency is a major selling argument (keeping in mind that the customer receives money for feeding energy to the grid), a competition of very high efficiencies is still ongoing.

Using next generation semiconductor devices made of Silicon Carbide (SiC), efficiencies for PV inverters of over 99% are reported [4]. Such advanced switching devices, however, are still in an ongoing development stage and thus cost expensive, so that they have not found commonplace usage within commercial systems. The majority of publications on the utilization of SiC shows the benefits of reduced losses, but are rarely covering the topic cost, which are a major design constraint as well. This PhD project will therefore investigate possible alternatives to achieve high efficiency power converters and discusses them against the converter design constraints complexity and cost.

### 1.3 Project objectives

Based on the aforementioned demand for high efficient power converters, the aim of this project is to identify current limitations within high efficiency power conversion in PV inverters, and to thoroughly investigate possibilities to overcome these. This thesis focuses on the investigation on a semiconductor and a topological level as this is where a major loss contribution within electrical power conversion is typically found. The benefits of achieving high efficiency in two possible ways will be discussed against their design trade-offs such as increased complexity and cost. This thesis will not intend to follow an optimization routine that results in the highest possible efficiency as this topic is well established and typically includes an overall converter design covering input filters, topologies, semiconductors, output filters, modulation strategies and control, and cannot be covered in a single PhD project alone.

The main objectives in this project are therefore:

- to accurately identify major loss contributors and limitations for high efficiencies in a commonly used PV inverter topology for given operating points,

- to investigate the utilization of new semiconductor power devices within PV inverter operation context,

- to investigate the approach of a more complex but promising topology as an alternative to SiC based converters.

This thesis, however, does not cover:

- EMC filtering

- AC filtering

- Magnetic design

- Control and modulation related issues

### 1.4 Structure

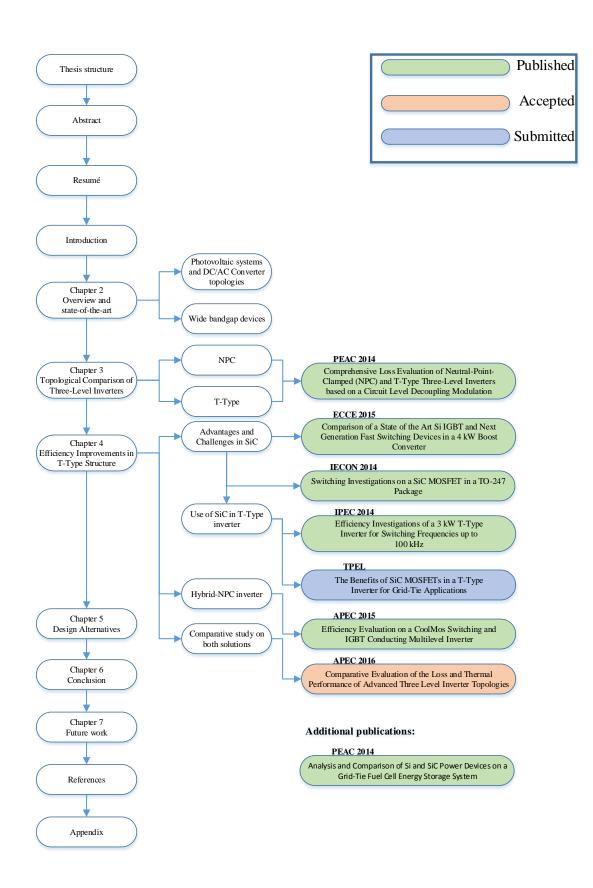

Fig. 1.2 demonstrates the outline of this dissertation and how each publication relates to the key parts of the project. More elaborated, Chap. 2 gives an overview of current practices within PV systems based on previous work that has been carried out on both a topological point of view and on a semiconductor level. From this point, a tendency is drawn to which this dissertation can give an update and hence contribute.

A thorough elaboration on the state-of-the-art work on a topological level is given in Chap. 3, in which the advantages and drawbacks of two commonly used topologies are compared against each other. The conclusion from this chapter will lead to the starting point of Chap. 4 which represents the main work carried out in this PhD, i.e. thoroughly demonstrating design considerations on how efficiency improvements can be achieved and to accurately validate the proposed approaches through measurements. This chapter ends with a discussion on both solutions including the cost factor. The consequences of loss reduction will be introduced in Chap. 5 in terms of possible design alternatives, which directly leads to the conclusions and recommendations for future work, presented in Chap. 7.

Figure 1.2: Thesis outline

## Chapter 2

## Overview and state-of-the-art

# 2.1 Photovoltaic systems and DC/AC converter topologies

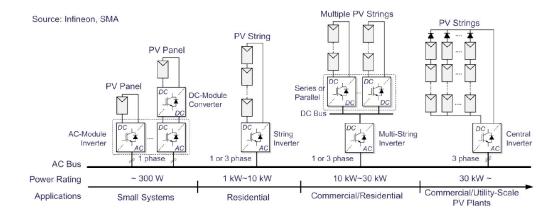

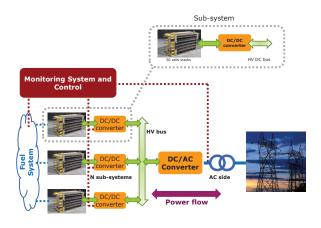

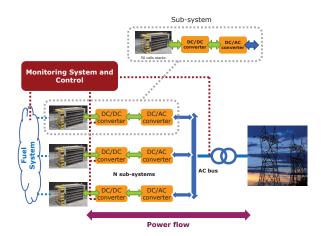

Based on the increased interest in PV systems explained in Sec. 1.2, strong research is conducted in several fields within PV, starting from increasing efficiencies in PV modules towards the full integration of complete systems. The integration of a PV system depends on its power rating, as demonstrated in Fig. 2.1 [5].

Figure 2.1: PV systems for different power levels

All configurations in Fig. 2.1 have in common to convert the electrical Direct Current (DC) power from the PV modules into Alternating Current (AC) power to comply with the grid specifications, e.g.  $230\,\mathrm{V}/400\,\mathrm{V}$ ,  $50\,\mathrm{Hz}$  in most European countries. That conversion stage has been under intensive research within the last decades and can be grouped into two parts, i.e. transformer based and transformer-less systems [6]. Where transformer based systems have the particular advantage in their safety structures due to the galvanic isolation between the grid and the PV side, transformer-less systems can achieve higher efficiencies and higher power

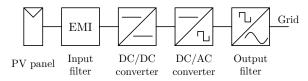

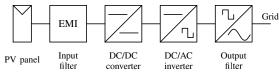

densities at lower cost due to the absence of the transformer. However, a boost stage placed between the PV panels and the DC/AC converter is then necessary to ensure a DC link voltage large enough to achieve the required grid specifications. A block diagram of a typical transformer-less PV system is shown in Fig. 2.2.

Figure 2.2: Block diagram of a transformer-less PV system

In recent years, safety regulations for grid-connected residential systems have been lowered such that a clear tendency is observed favoring transformer-less systems and thus accepting the additional DC/DC converter stage [7]. To this end, various studies have compared topologies against each other to further improve the integration of PV. Despite the various topological alternatives available to obtain the desired AC output, this work lists the most commonly used configurations within the prospect of PV application found in the literature.

The most mature configuration is the three-phase Full-Bridge topology. It is a two-level alternative meaning that the switched converter output terminals can achieve two defined voltage potentials. In contrast to the two-level inverter, multilevel inverter topologies can achieve staircase voltages on their output terminals. This kind of topology has been introduced in [8] in 1975 and has gained increasing interest ever since [9,10], of which the minimum voltage levels are categorized as three-level topologies [9], which can then go up to n-level inverters. With an infinite number of levels, i.e.  $n \to \infty$ , the voltage at the output terminals will be a pure sinusoid and no filtering will be necessary [9,11], clearly at the expense of an infinite number of semiconductor devices.

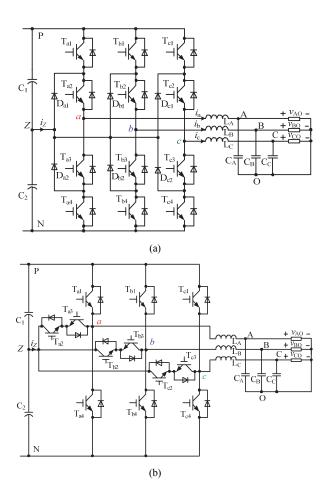

Therefore, extensive research has been carried out in the past comparing two- and multilevel topologies against each other and it is found out that the choice of topology strongly depends on the given application. For PV systems, the following topologies have found major interest in the literature, of which one phase leg for each topology is shown in Fig. 2.3:

- The three-phase Full-Bridge structure [12], Fig. 2.3a

- The Neutral-Point-Clamped (NPC) structure [13, 14], Fig. 2.3b

- The T-Type structure [15] (known as Bipolar-Switched-Neutral-Point-Clamped (BSNPC) [16] or Conergy [17]), Fig. 2.3c

- The Flying Capacitor (FC) [18,19], Fig. 2.3d

- The Z-source converter [20], Fig. 2.3e

- The cascaded H-Bridge [8], Fig. 2.3f

The last configuration in this list needs an individual DC source for each H-Bridge and is therefore only an interesting choice for medium and large scale PV systems [21, 22] rather than residential low cost PV systems. Hence it is not further

**Figure 2.3:** One phase leg of each suitable topology. In (a) the Full-Bridge inverter, in (b) the NPC inverter, in (c) the T-Type inverter, in (d) the Flying Capacitor inverter, in (e) the Z-source inverter and in (f) the cascaded H-Bridge

included in this overview. A major advantage of multilevel inverters is that the semiconductor devices are commutating with only part of the DC link voltage. For instance, in a three-level inverter, each switching device switches only half the DC link voltage whereas in a conventional two-level inverter, each switching device switches the full DC link voltage. This directly leads to reduced switching losses for the three-level inverter at any given switching frequency. Nevertheless, total semi-conductor losses in a two-level inverter can still be lower compared to a three-level inverter if the switching frequency is low enough. Hence, the operating condition becomes a crucial aspect when comparing topologies.

For instance, in [23], the two-level and the three-level NPC converter have been

compared against each other in terms of semiconductor losses, filter aspects, reliability and cost. It is found out that the staircase voltage at the NPC converter output terminals and hence the reduced harmonic content directly lead to a smaller AC filter size for a given operating condition. The size reduction in the AC filter and the lower heat sink requirements for a three-level inverter (due to the reduced switching losses) can lead to an equally expensive or an even cheaper PV inverter despite the fact that the semiconductor count is higher.

A similar comparison has been carried out in [24], in which a two-level inverter has been evaluated against the three-level NPC and the three-level T-Type inverters. The T-Type structure is a derivation of the NPC achieving the same output performance at reduced semiconductor count [10,17]. Instead of cost as a comparison parameter, [24] uses the area chip size as a cost indicator. With similar results as in [23], three-level inverters can outperform the two-level inverter at increased switching frequencies, not only in losses but also in price. For residential PV systems, the switching frequency is usually set between 16 kHz and 48 kHz [4] with around 20 kHz as a good compromise between switching losses and filter size.

In [12], two-level and three-level inverter constellations have been evaluated based on their leakage currents, which is a major concern in transformer-less PV systems, and have found out that the Common Mode (CM) voltage is larger for the Full-Bridge structure compared to the NPC. This consequently results in larger leakage currents.

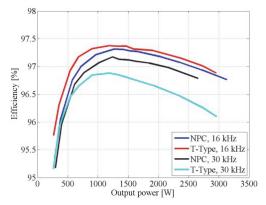

Within the three-level converter topologies, as pointed out in [24], the three-level T-Type structure achieves lower semiconductor losses compared to its NPC alternative at low to medium switching frequencies (approx.  $20\,\mathrm{kHz}$ ). That is because the NPC converter has relatively large conduction losses as always two semiconductor devices conduct the load current [25] (an elaboration on that is given in Chap. 3). This leads to an uneven loss distribution and consequently to an uneven thermal stress among the semiconductor devices [26]. While this can be overcome in an Active Neutral-Point-Clamped (ANPC) [27], in which the clamping diodes are replaced by switching elements, such solution clearly adds complexity to the circuitry and control. Above a certain switching frequency, the T-Type inverter shows higher total semiconductor losses compared to the NPC due to the relatively large switching losses in the outer DC bus connecting switches ( $S_1$  and  $S_4$  in Fig. 3.3a).

The topological comparison has been extended in [20,28,29] evaluating transformerless inverter topologies including the Z-source structure from Fig. 2.3e, which has the particular benefit of having a boost stage without any additional switching elements. However, this solution has been commonly found to achieve lower efficiencies than the NPC including a separate boost state. The Flying Capacitor from Fig. 2.3d requires a more complex startup routine, extra capacitors and a proper voltage balancing scheme [23,30,31] and is therefore not commonly used for low-cost PV systems.

### 2.2 Wide bandgap devices

Apart from the topological investigation to achieve high efficiency power conversion, power losses in a converter can be reduced using low loss semiconductor devices. To this end, research interest not only tends to improve currently available Insulated-Gate-Bipolar-Transistors (IGBTs) made of Silicon (Si) to optimize their trade-offs between the saturation voltage and switching energies [32,33], but also to introduce wide-bandgap semiconductor devices. Especially devices made of SiC and Gallium Nitride (GaN) have been in the focus of high efficient power converters in grid-connected applications. Such devices were first commercially available with the introduction of SiC diodes in 2001. Their particular benefit is the absence of the reverse recovery current which not only lowers the switching losses in the diode itself, but also greatly reduces the turn-on switching losses of the commutating switching device [34–36]. The important properties of wide-bandgap material are listed in Table 2.1 [37].

| Properties                                       | Si              | GaN            | 4H-SiC         |

|--------------------------------------------------|-----------------|----------------|----------------|

| Bandgap, Eg<br>(eV at 300 K)                     | 1.12            | 3.4            | 3.2            |

| Critical electric field $Ec (V/cm)$              | $2.5\cdot 10^5$ | $3 \cdot 10^6$ | $2.2\cdot10^6$ |

| Thermal conductivity, $\lambda$ (W/cmK at 300 K) | 1.5             | 1.3            | 3 - 4          |

| Electron mobility, $\mu_n$ (cm <sup>2</sup> /Vs) | 1350            | 1000           | 950            |

| Dielectric constant, $\varepsilon$               | 11.9            | 9.5            | 10             |

Table 2.1: Properties of wide-bandgap materials

The higher bandgap Eg is a very beneficial property since that directly relates to the on-resistance of the device, which is commonly used as a figure of merit within the comparison against Si. The specific on-resistance of a MOSFET can be calculated as [37]

$$R_{on,sp} = \frac{4V_B^2}{\varepsilon \mu_n E_c^3} \qquad , \tag{2.1}$$

where  $V_B$  is the breakdown voltage,  $\varepsilon$  the dielectric constant,  $\mu_n$  the electron mobility and  $E_c$  the critical field strength. Eq. (2.1) illustrates the non-linear relationship between specific on-resistance and electric breakdown field which immediately demonstrates the superior performance of semiconductors made of wide-bandgap material. A comparison of Si, SiC and GaN is shown in Fig. 2.4 [38].

Thus, the use of SiC devices can be very attractive in order to keep conduction losses low. Not only are the new kind of devices attractive because of their possible lower conduction losses, also their high switching speeds are beneficial to reduce low switching losses. A common way to compare one device over another is by using simple Double Pulse Test (DPT) measurements, from which it is concluded that SiC switching devices offer performance benefits in terms of switching speed and hence switching losses can be greatly reduced compared to a state of the art Si IGBT [3,39]. Such comparisons are extended to compare SiC switching devices in

Figure 2.4: Specific on-state resistance comparison of Si, SiC and GaN

various applications. For instance, [40] demonstrates the potentials and challenges of SiC MOSFETs against Si IGBTs in a Variable Speed Drive (VSD), such as same overall converter losses at 50 kHz switching frequency for the SiC based system compared to the Si based system operating at 15 kHz. In [41], the utilization of SiC JFETs in Electric Vehicle (EV) is investigated and the energy consumption savings due to the higher efficiency are predicted.

The potential of SiC performance improvements within PV inverter context is explored in [3], in which the utilization of a SiC JFET in a two-level inverter is investigated and compared against a more complex three-level NPC inverter using conventional Si IGBTs, and has concluded that similar overall converter efficiencies can be achieved with the use of SiC. The analysis of the utilization of SiC in three-level inverters for PV systems is furthermore in some detail presented in [4,42], in which efficiency curves of a commercially available PV inverter are shown.

The utilization of 650 V SiC MOSFETs and 1200 V SiC MOSFETs in a T-Type structure for PV inverters is demonstrated in [43], in which the feasibility of the intrinsic body-diode of such switching devices is investigated and concluded to be reliable. However, no detailed loss breakdown is shown to what extend the utilization of SiC switching devices in either the bi-directional or the vertical path of the T-Type structure can result in loss performance improvements.

While the majority of applications investigate the benefits of SiC such as reduced losses and high switching frequency operation, fewer publications are available that address the higher prices, which, to date, might be a strong argument for not utilizing such devices in commercial products. In the early introduction of SiC switching devices, [44] discussed the potential cost savings of PV inverters due to the reduction of inductive components (AC filter) for increased switching frequencies and cost reduction of the heat sink due to the higher operating temperature capabilities of SiC material paired with an increased annual benefit because of the loss reduction in the semiconductor devices. However, such gain is not compared against the increased initial cost due to the expensive SiC switching devices themselves. In [45], a time span of 15 years is predicted for a 2.5 kW DC/DC converter until the cost even point is reached with the SiC based system. A more recent approach in evaluating the cost benefits of SiC in power converters is presented in [46], in

which a 25 kHz Si boost converter is theoretically compared against a 100 kHz SiC based boost converter showing cost reductions due to the downsize of the inductor at increased switching frequencies, although no detailed analysis on the inductor itself is given (in particular if the same core material is used for 25 kHz and 100 kHz) and the comparison is based on an assumption that the SiC MOSFET is capable of operating reliable at high ambient temperatures, which then assumes a greatly reduced heat sink requirement. Another cost analysis is given in [47] predicting a relatively short payback time of around 2 years for the SiC based system. This is, however, under the assumption that a 5 kW converter operates 24 h a day at full load, which is obviously not applicable in the case of PV inverters.

### 2.3 Summary

Based on the literature review given in this section, three-level topologies have found place in grid-connected applications due to their lower loss profile and the smaller AC filter size because of the lower harmonic content at the converter output terminals. The NPC inverter still seems to be an attractive choice for low cost PV systems even though it has been introduced over 30 years ago. That is mainly due to the high level of maturity and thus availability within semiconductor modules. However, it comes with the particular drawback that current must always flow through two semiconductor devices, which causes large conduction losses resulting in an uneven thermal stress among the semiconductor devices. At typical switching frequencies for residential PV systems, i.e. in the range of 20 kHz, the T-Type structure can achieve lower total semiconductor losses due to the reduced conduction losses. However, as the switching frequency increases, the T-Type structure will significantly increase the semiconductor losses and thus lower the efficiency compared to the NPC alternative.

To date, various publications on SiC can be found, including static and dynamic performance comparisons both standalone and demonstrating efficiency improvements in actual applications, while almost none of them address the cost factor. Instead, it seems that the higher price for SiC is simply accepted arguing that cost will automatically go down with mass production in the future. This leads to the generalized conclusion that SiC can greatly reduce losses compared to Si, although detailed loss breakdown analyses verified experimentally are often left out such that some applications may or may not inherently benefit from such new materials. Also, even several years after the introduction of SiC switching devices, no mass production is achieved yet and the factor cost may still be a design constraint when it comes to SiC based converter design.

# Chapter 3

# Topological Comparison of Three-Level Converters

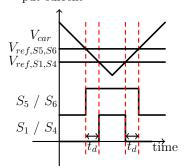

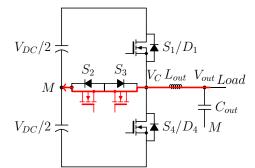

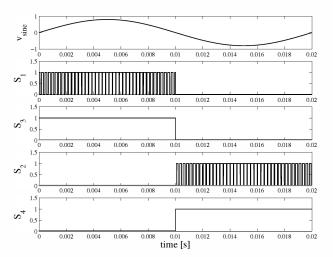

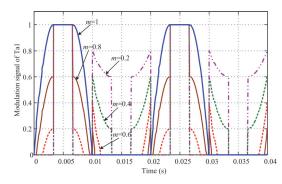

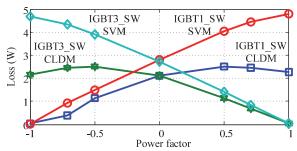

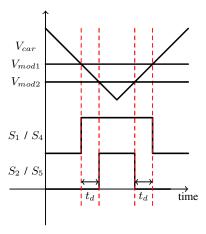

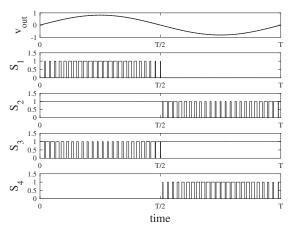

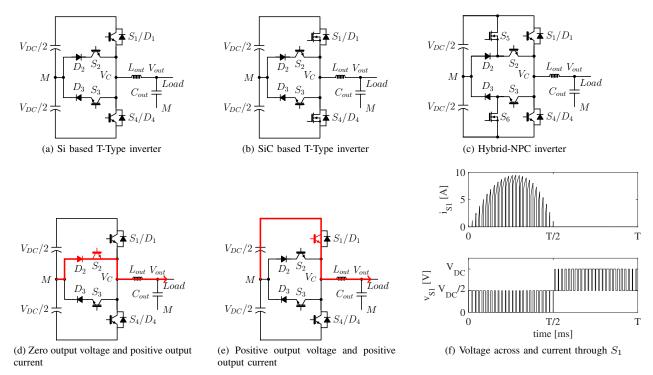

This chapter gives a more detailed comparison between two commonly used three-level inverter alternatives, namely the NPC and the T-Type inverter. Both topologies have in common to have a direct connection to the midpoint of the DC link and hence enable a three-level switched output voltage. One phase leg of each topology is depicted in Fig. 2.3b for the NPC and Fig. 2.3c for the T-Type alternative. Their main difference is the placement of the outer switches ( $S_{1,4}$  in Fig. 3.3) which gives advantages on one side and disadvantages on the other. Before the analysis of both topologies is carried out, a brief introduction to the modulation principle is given. With several possible modulation strategies available for three-level inverters such as Space Vector Modulation (SVM) or Sine Pulse Width Modulation (SPWM), Phase Disposition (PD) PWM is applied which is found to be the optimum modulation strategy for these topologies [48, 49]. The basic principle for PD PWM is illustrated in Fig. 3.1a and can be applied to either the NPC or T-Type topology. The switching states from Fig. 3.1b are detailed in Table 3.1.

Figure 3.1: Phase Disposition (PD) PWM as the chosen modulation principle

**Table 3.1:** Switching states for NPC and T-Type converters

| Output voltage | $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|----------------|-------|-------|-------|-------|

| $V_{DC}/2$     | 1     | 1     | 0     | 0     |

| 0              | 0     | 1     | 1     | 0     |

| $-V_{DC}/2$    | 0     | 0     | 1     | 1     |

The modulation strategy will be explained on both the T-Type and the NPC structures and unity power factor is assumed for simplicity reasons, i.e.  $cos(\varphi) = 1$ . For clarification, the phase displacement  $\varphi$  describes to what degree the output voltage  $v_{out}(t)$  and output current  $i_{out}(t)$  are out of phase, illustrated in Fig. 3.2, and thus defines the amount of active and reactive power exchange according to

$$P_{out} = V_{out}I_{out}cos\left(\varphi\right) \qquad , \tag{3.1}$$

where  $V_{out}$  and  $I_{out}$  are the Root Mean Square (RMS) values of  $v_{out}(t)$  and  $i_{out}(t)$ . Pure active power exchange is defined if voltage and current are in phase, i.e.  $\varphi = 0^{\circ}$ , and the power factor  $cos(\varphi)$  thus becomes  $cos(0^{\circ}) = 1$ . Pure reactive power exchange occurs at  $\varphi = 90^{\circ}$  with a power factor of  $cos(90^{\circ}) = 0$ .

Figure 3.2: Output voltage and output current

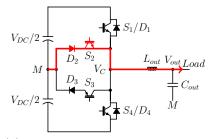

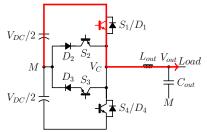

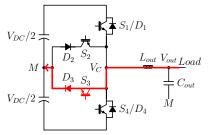

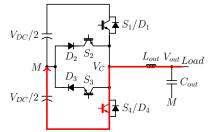

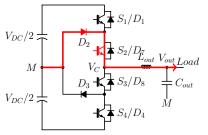

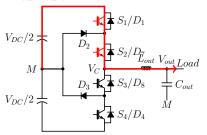

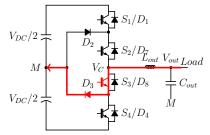

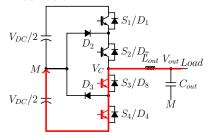

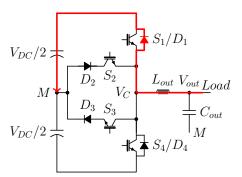

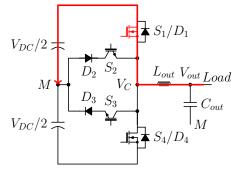

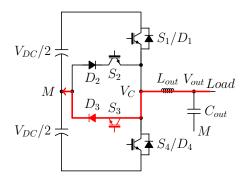

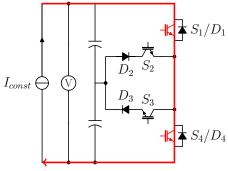

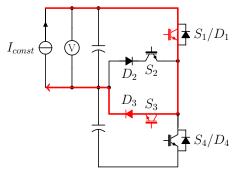

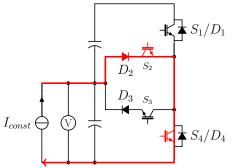

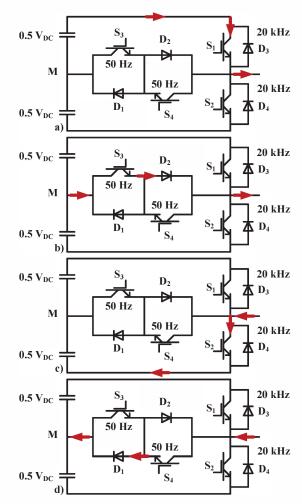

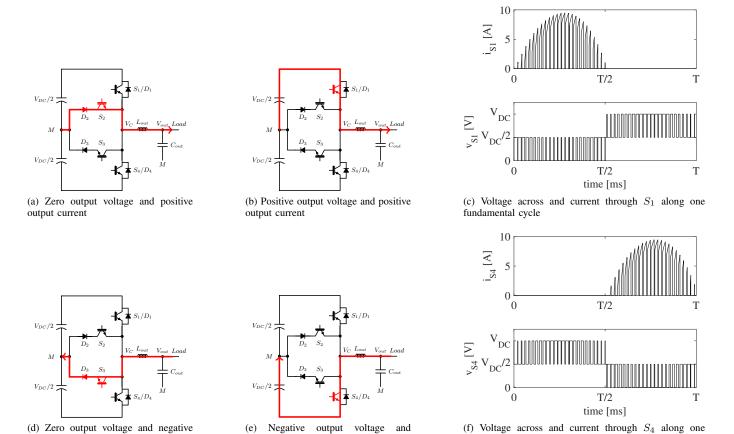

The commutation states for both topologies are illustrated in Fig. 3.3. As an initial state, the load current is positive (representing the time interval from t = [0..T/2] in Fig. 3.1b) and the converter output voltage  $V_c$  is zero, also called as zero output voltage. The current for both topologies flows through diode  $D_2$  and  $S_2$  towards the load. To achieve a positive output voltage, switch  $S_1$  turns on and current commutates from  $D_2$  to  $S_1$  causing switching losses in  $S_1$ . Note that this statement is true for both the T-Type and the NPC converters.

For a positive output voltage, current will flow through  $S_1$  only in the T-Type constellation (Fig. 3.3c) whilst flowing through both  $S_1$  and  $S_2$  in the NPC alternative (Fig. 3.3d). When the load current is negative (during t = [T/2..T]) and the converter output voltage is zero, current flows from the load to the midpoint of the DC link through  $S_3$  and  $S_4$ . To achieve a negative output voltage, switch  $S_4$  turns on as depicted in Fig. 3.3g and Fig. 3.3h. The current paths for the T-Type and the NPC alternatives follow the same principle as for a positive output voltage, now only through  $S_4$  in the T-Type structure against  $S_3$  and  $S_4$  in the NPC constellation. This clearly shows that current will always flow through two semiconductor

(a) Zero output voltage and positive output current.  $S_1$  turned off,  $S_2$  turned on

(c) Positive output voltage and positive output current.  $S_1$  turned on

(e) Zero output voltage and negative output current.  $S_4$  turned off,  $S_3$  turned on

(g) Negative output voltage and negative output current.  $S_4$  turned on

(b) Zero output voltage and positive output current.  $S_1$  turned off,  $S_2$  turned on

(d) Positive output voltage and positive output current.  $S_1$  turned on

(f) Zero output voltage and negative output current.  $S_4$  turned off,  $S_3$  turned on

(h) Negative output voltage and negative output current.  $S_4$  turned on

**Figure 3.3:** Switching states for T-Type inverter (left-hand side) and NPC inverter (right-hand side) operating at unity power factor

devices for the commonly used NPC in each switch constellation whereas current will only flow through two semiconductor devices when the T-Type topology is in its zero output voltage. This fundamental difference can achieve a reduction in conduction losses for the T-Type alternative.

#### 3.1 NPC converter

The NPC topology is depicted in Fig. 2.3b and comprises of a DC link bus with split bulk capacitors, four switching devices and six diodes. The particular benefit of the NPC topology is that it can be realized with semiconductor devices that need to block half the DC link voltage only. This means that for the NPC topology, semiconductor devices can be chosen with a breakdown voltage half of the semiconductor devices that are utilized in a two-level topology, which can hence greatly reduce the switching losses for the NPC structure [23]. Its drawback, however, is that current will always flow through two semiconductor devices with associated conduction losses.

## 3.2 T-Type converter

The T-Type inverter is a derivation of the NPC inverter that aims to reduce its relatively large conduction losses. This is done by rearranging the outer switches  $S_{1,4}$  as shown in Fig. 3.3. The result is that switches  $S_{2,3}$  only conduct current at a zero output voltage on the converter output terminal. The conduction intervals for  $S_{1,4}$  remain the same. This rearrangement of the outer switching devices can also reduce the semiconductor device count, now four switching devices and four diodes per phase leg only, which is two diodes less compared to the NPC alternative. The rearrangement, however, has the particular disadvantage that the outer switches in the T-Type alternative ( $S_{1,4}$ ) now need to be able to block the full DC link voltage, despite the fact that the commutating voltage is only at half the DC link. This unusual operation mode of the T-Type structure indicates that the DC bus connecting devices need to be chosen to have breakdown voltages at the full DC link voltage, which then leads to increased switching losses compared to the NPC converter.

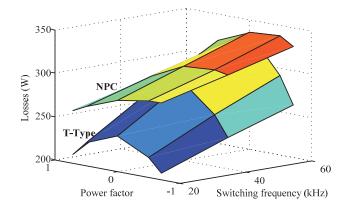

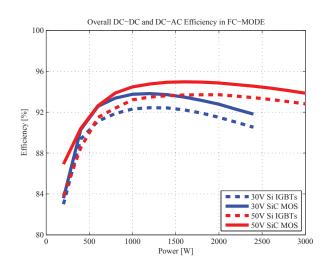

# 3.3 Efficiency comparison

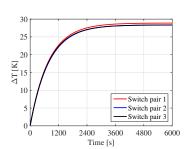

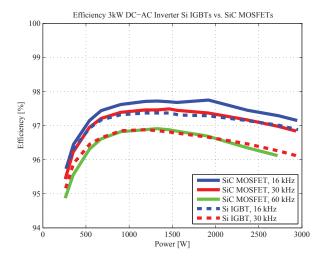

As pointed out in [23], semiconductor devices with higher breakdown voltages suffer from larger conduction and switching losses compared to devices rated at lower breakdown voltages. It is then investigated in [24,50], that the switching frequency becomes a critical parameter when comparing the NPC and T-Type structures and have found that the T-Type alternative has superior loss performance particularly at lower operating frequencies. As the switching frequency increases, however, switching losses in the DC bus connecting switches in the T-Type structure become dominant, hence decreasing the overall converter efficiency. While switching losses can generally be reduced using loss optimized PWM strategies such as Discontinuous Pulse Width Modulation (DPWM) [15, 50, 51], a trade-off is usually made against other criteria (e.g. increased harmonic content for DPWM [11, 52]). Another alternative is to replace the Si diodes in the inner bi-directional path with SiC diodes to reduce reverse recovery losses [53]. An All-SiC T-Type inverter is demonstrated in [43].

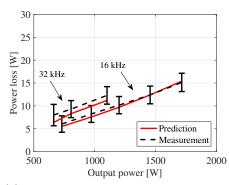

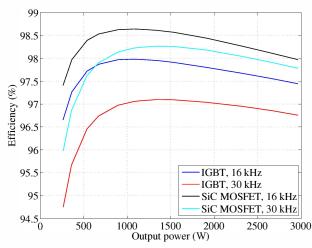

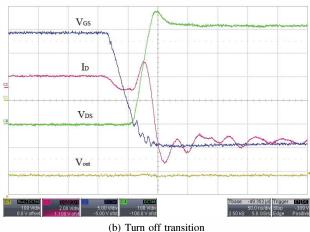

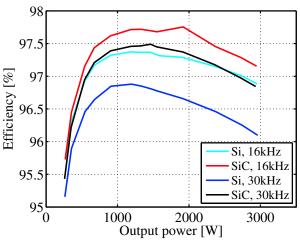

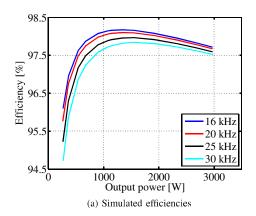

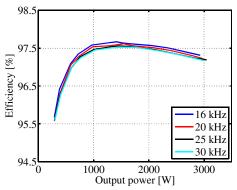

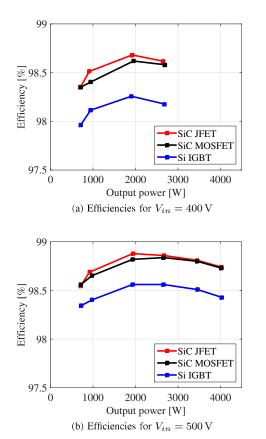

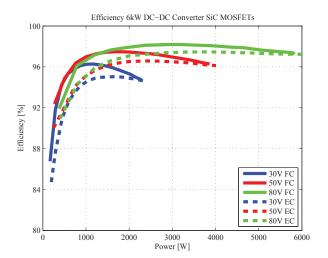

**Figure 3.4:** Measured efficiencies of NPC and T-Type for different switching frequencies and output power

The aforementioned analysis on the switching frequency influence on the converter losses is verified experimentally. Efficiency measurements are conducted with an N4L PPA5500 power analyzer based on the specifications from Table 4.4. Results for both topologies using conventional PD PWM and Si IGBT devices paired with SiC diodes are given for two different switching frequencies, i.e. 16 kHz and 30 kHz. The results are shown in Fig. 3.4 illustrating a large efficiency drop for the T-Type alternative as the switching frequency is increased. In particular, Fig. 3.4 shows that efficiencies for the T-Type inverter are highest as the switching frequency is set low. This is especially true for light load conditions where the T-Type converter can achieve lower conduction losses because only one device conducts current at positive or negative output voltage state. However, as the switching frequency increases, a major drop in efficiency for the T-Type converter is observed while the drop in efficiency for the NPC is less severe. Clearly, these curves can look different depending on the chosen semiconductor devices, modulation strategies and operating conditions such as DC link voltage, modulation index etc. However, Fig. 3.4 verifies the general statement in alignment to [24] that the efficiency in the T-Type structure is more dependent on the switching frequency than the NPC alternative, which, in turn, leads to the conclusion that the T-Type structure to date is not a suitable topology for high efficiency high switching frequency operation.

# 3.4 Summary

This chapter dealt with a direct comparison of two commonly used three-level inverter structures, i.e. the NPC and the T-Type topology. Using conventional PD PWM, the T-Type inverter can achieve high efficiencies at low switching frequencies. That is because its conduction losses are lower compared to the NPC due to the reduced current stress in the inner switching devices  $S_{2,3}$ . However, as the switching frequency increases, the switching losses in the outer switching devices

$S_{1,4}$  become large because they need to be able to block the whole DC link voltage even though the commutation voltage is only  $V_{DC}/2$ . This significantly reduces the overall efficiency in the T-Type inverter compared to the NPC structure because the latter alternative can be realized with semiconductor devices that need to block only half the DC link voltage.

# Chapter 4

# Efficiency Improvements in the T-Type Structure

Based on the previous chapter, the T-Type topology has its advantages in the low conduction losses but suffers from large switching losses due to the utilization of  $1200\,\mathrm{V}$  switching devices in its outer path compared to the NPC alternative despite the fact that only half the DC link voltage applies during a switching commutation. This chapter represents the major part of this PhD project, i.e. to accurately quantify the inverter losses for a given application/specification and to investigate possible methods to overcome the fundamental issue linked to the T-Type structure. Two approaches are investigated in detail and compared to each other. The first approach is investigated in Sec. 4.1 and directly utilizes low loss switching devices made of SiC whereas the second approach, presented in Sec. 4.2, strategically adds lower breakdown voltage rated semiconductor devices in addition to the conventional T-Type inverter, resulting in a more complex topology. This approach is referred to Hybrid-NPC in further reading.

# 4.1 Using SiC switching devices

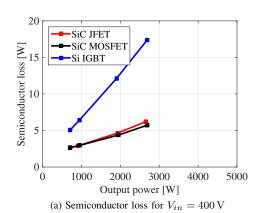

Semiconductor devices made of SiC are of great interest in power electronics applications because of their superior performance compared to regular Si based devices. An introduction to these semiconductor devices was given in Sec. 2.2 showing the potentials within the field of power electronics. This chapter compares two promising SiC switching devices against each other and a high-speed Si based IGBT. Based on the outcome of this analysis, the most promising candidate is utilized in the three-level T-Type inverter to investigate possible loss reduction on a topological level.

#### 4.1.1 Advantages and Challenges with SiC Switching Devices

Despite their introduction and implementation in various prototypes, SiC switching devices have not found commonplace usage in commercial products. First of all, the commercial availability of SiC switching devices through distribution channels is mainly dominated by SiC MOSFETS [54] as these devices are closest to well known Si devices [37, 55]. Furthermore, there is no direct replacement meaning that for each SiC device implemented, modifications on their gate driver circuits must be done while the device itself often comes in the same package (TO-220 or TO-247 when discrete device are considered).

Another major aspect postponing the replacement of Si devices comes with the term reliability. SiC switching devices have their own characteristics, each with particular advantages and drawbacks. For instance, the SiC MOSFET is claimed to have reliability issues in its gate-oxide [55, 56]. Not only is the gate threshold voltage highly instable as the temperature in the gate-oxide increases, the gate can also degrade after a short-circuit operation [57–59]. While these issues are related to long-term reliability, which the SiC JFET does not have because of its missing gate-oxide, its depletion mode (normally-on) characteristic is the main drawback. Normally-on means that it is fully turned on when the gate-source voltage is 0 V and a negative voltage is required to turn the device off. This immediate reliability issue is important in Voltage Source Converters (VSCs) comprising of large DC link capacitor banks (for instance in each topology in Fig. 2.3). While this issue can be addressed with an in series placed low voltage Si MOSFET, known as a cascode configuration [60,61], it increases the complexity of the converter system because an additional semiconductor device is necessary for each SiC JFET. Where only one gate driver is necessary for the conventional cascode [60,61], only the low voltage MOSFET is directly controlled and no direct control of the JFET is possible. The other approach is the *Direct driven cascode* [62], which achieves direct control for both the JFET and the MOSFET, but comes at the expense of a clearly more sophisticated requirement to the gate driver. A detailed explanation of the Direct driven approach can be found in [62]. Since the Direct driven approach allows controllability of the JFET and the low voltage MOSFET only acts for normallyoff behavior, the analysis and comparison are done on the JFET only since no switching losses in the cascode MOSFET are expected. The semiconductors used for this comparison are listed in Table 4.1.

Table 4.1: Semiconductors used

| Device     | Name         | $I_C$ or $I_D$ at          | $V_{GE}$ or $V_{GS}$ | $C_{oss}$ |

|------------|--------------|----------------------------|----------------------|-----------|

|            |              | $25^{\circ}\mathrm{C}$ [A] | [V]                  | [pF]      |

| Si IGBT    | IKW15N120H3  | 30                         | ±20                  | 75        |

| SiC MOSFET | C2M0080120D  | 36                         | -10/+25              | 80        |

| SiC JFET   | IJW120R070T1 | 35                         | -19.5/+2             | 102       |

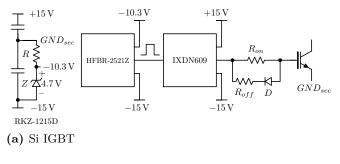

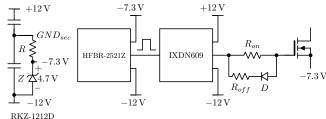

The basis in this comparison is chosen to be a similar current rating at  $25\,^{\circ}$ C. Table 4.1 also details the particular gate-source or gate-emitter requirements given as absolute maximum ratings. Although the gate driver circuits for the use of SiC switching devices are well discovered by now, a direct comparison on the design alterations compared to a conventional gate driver for Si IGBTs are only partially

#### (b) SiC MOSFET

(c) SiC JFET

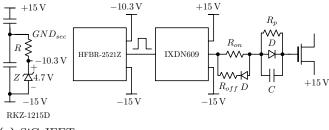

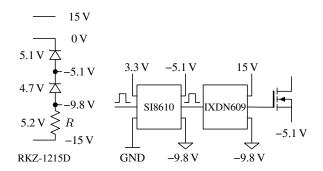

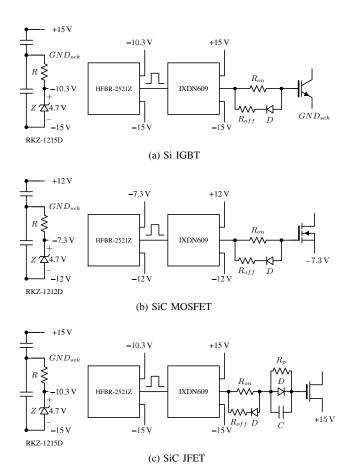

Figure 4.1: Schematic of the gate driver circuits

covered in literature, e.g. in [63]. The JFET driver circuit is taken from [64] which has found good acceptance for the use of normally-on JFETs. All three possible gate driver constellations are shown in Fig. 4.1.

The IGBT gate driver circuit with its most basic components uses the commercially available DC/DC converter RKZ-1215D to provide not only galvanic isolation (usually necessary in multilevel converters) but also the required voltage levels for the IGBT gate. The HFBR-2521Z receives the control signal from the evaluation board  $C2000\ Piccolo\ Launchpad$ , and IXDN609 is the gate driver IC. The voltage supply for the receiver is obtained using a simple zener diode.

The SiC MOSFET requires different gate voltages. This work uses the approach to obtain such voltage levels with a minimum adjustment with respect to the IGBT driver. First of all, the commercially available DC/DC converter RKZ-1215D is replaced with the RKZ-1212D providing  $\pm 12\,\mathrm{V}$ . The source of the SiC MOSFET is connected to the anode of the zener diode, i.e.  $-7.3\,\mathrm{V}$ . The driving voltage for turn on is then according to Kirchoff's voltage law (KVL)

$$V_{GS,on} = +12 \text{ V} - (-7.3 \text{ V}) = 19.3 \text{ V}$$

(4.1)

and the turn off voltage, respectively

$$V_{GS,off} = -12 \,\text{V} - (-7.3 \,\text{V}) = -4.7 \,\text{V}$$

(4.2)

With respect to the IGBT gate driver, only two minor modifications are thus necessary:

- 1. Replace the DC/DC converter RKZ-1215D with the DC/DC converter RKZ-1212D which provides galvanic isolation and two output voltages  $\pm 12 \,\mathrm{V}$ .

- 2. Reference the source of the SiC MOSFET to the voltage of the zener diode, i.e.  $-7.3\,\mathrm{V}$ .

The gate driver circuit for the SiC JFET is most different from the Si IGBT driver circuit. The reason for that lies in the internal structure of a normally-on SiC JFET, which is thoroughly described in [56,62,64]. It is turned on with 0 V and a negative voltage needs to be applied to turn the device off. This pinch-off voltage is given to be around -16 V and a thus a voltage of around -20 V is recommended to fully turn the device off. At around -23 V, the gate-source junction enters reverse breakdown causing a large current flowing through the gate. The gate driver shown in Fig. 4.1c is designed to allow reverse breakdown because the current is limited by the high ohmic resistor  $R_p$  [64]. The modifications for the JFET gate driver with respect to the IGBT gate driver are as follows:

- 1. Place an RCD network between the gate resistance and the gate of the JFET.

- 2. Reference the source of the JFET to the positive supply voltage of the DC/DC converter output, i.e. +15 V.

Based on the gate driver circuit, neither the JFET standalone nor the MOSFET seem to show significant differences compared to the IGBT, although the JFET needs three more components (RCD network) and the statement holds only true if no low voltage cascode MOSFET is used. In case of a direct driven cascode configuration, two separate gate drivers and a proper undervoltage lockdown capability are necessary, which makes the SiC MOSFET then advantageous over the SiC JFET.

The second comparison basis uses the devices losses, based on datasheet information, switching transition measurements and converter loss measurements using a N4L PPA5500 power analyzer.

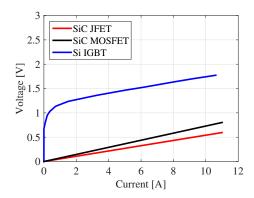

#### 4.1.2 Conduction losses

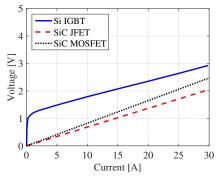

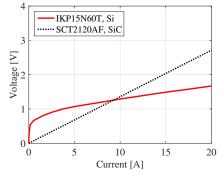

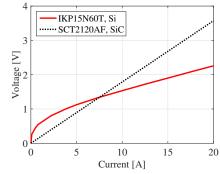

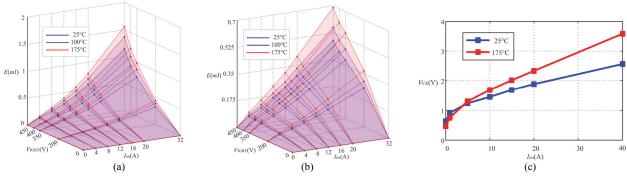

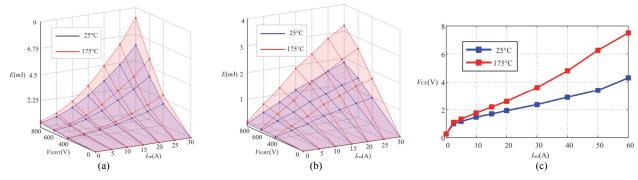

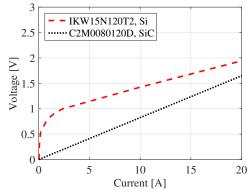

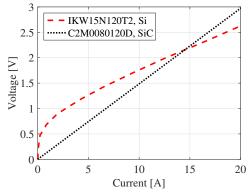

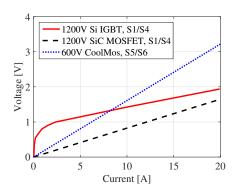

Forward voltages of all three devices for two different junction temperatures  $T_j$ , i.e.  $T_j = 25\,^{\circ}\mathrm{C}$  and  $T_j = 175\,^{\circ}\mathrm{C}$ , are shown in Fig. 4.2. The SiC devices have a lower voltage drop over the entire current range at a low junction temperature of 25 °C and superior forward voltage behavior up to around 20 A at a junction temperature of 175 °C. This indicates that the SiC devices will have lower conduction losses compared to the Si IGBT over various operating points. Within the prospect of the SiC switching devices, both devices have a resistive output behavior and the SiC JFET has a lower on-state resistance than the SiC MOSFET alternative at 25 °C junction temperature. At maximum junction temperature of 175 °C, the SiC JFET has a higher forward voltage compared to the SiC MOSFET. It is therefore of interest to show the on-state resistance as a function of junction temperature, shown

- (a) Forward voltage drop of a Si IGBT and two SiC switching devices at a junction temperature of  $25\,^{\circ}\mathrm{C}$

- (b) Forward voltage drop of a Si IGBT and two SiC switching devices at a junction temperature of 175 °C

Figure 4.2: Forward voltages at different current levels and junction temperatures

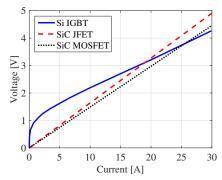

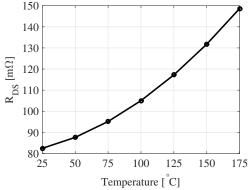

Figure 4.3: On-state resistances versus junction temperature

in Fig. 4.3. From a conduction loss point of view, the SiC JFET is beneficial at a junction temperature of up to  $100\,^{\circ}$ C. Above that temperature, the SiC MOSFET shows superior conduction loss behavior.

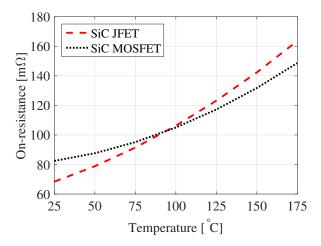

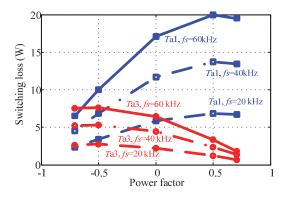

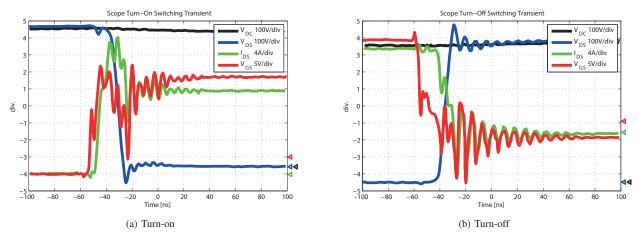

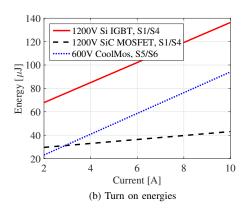

#### 4.1.3 Switching losses

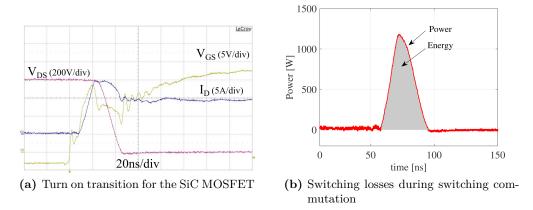

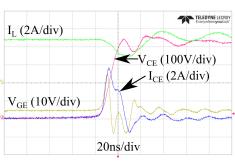

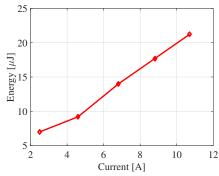

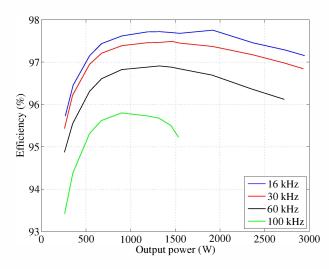

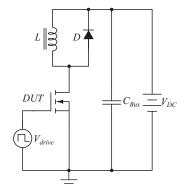

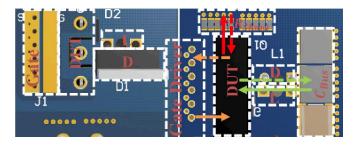

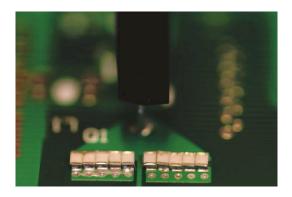

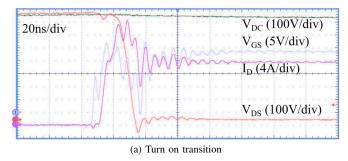

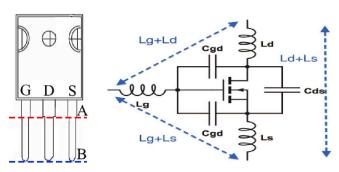

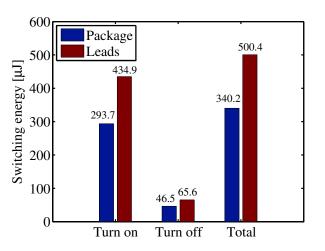

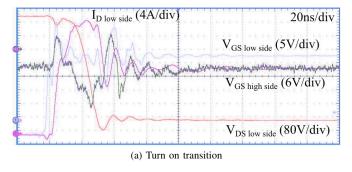

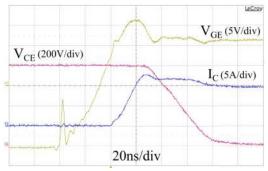

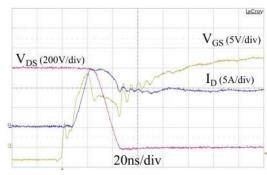

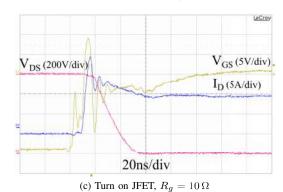

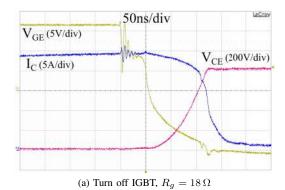

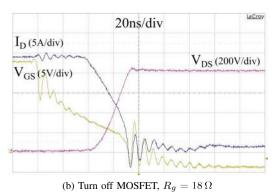

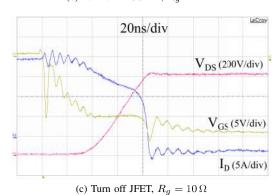

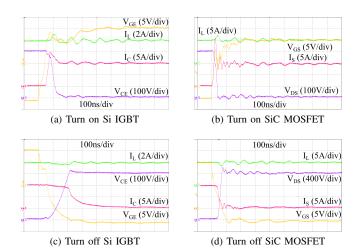

Switching losses are another major loss contributor in a power electronics converter, caused during a commutation event where voltage across and current through the device are overlapping with significant large values for a short amount of time. A common way of measuring this overlap of current and voltage is done via a DPT circuit, which has been designed in a Master's thesis throughout this PhD project [65]. The schematic and the laboratory prototype are shown in Fig. 4.4. Measuring voltage and current over a wide range of operating points, and integrating the product of these two values, gives the energy dissipation during each particular switching transition. This is exemplary shown in Fig. 4.5 for the SiC MOSFET, and a turn on commutation of 800 V and 10 A. Note that a complete comparison including the other devices is presented in App. H. This principle is then used to

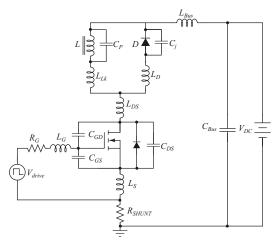

Figure 4.4: Double pulse test circuit for switching energy measurements

Figure 4.5: SiC MOSFET turn on commutation in (a) and associated losses in (b)

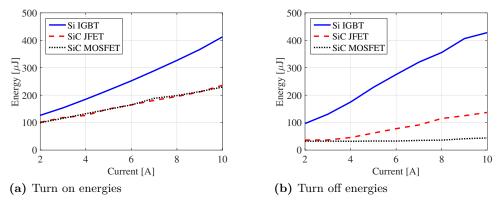

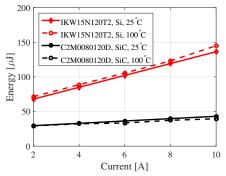

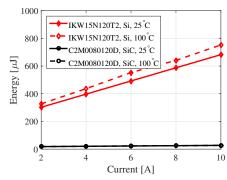

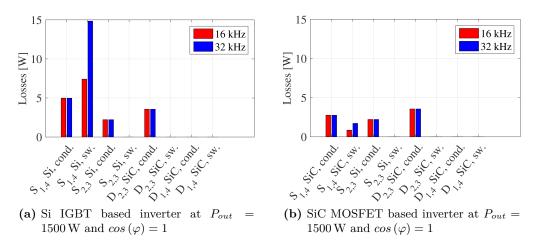

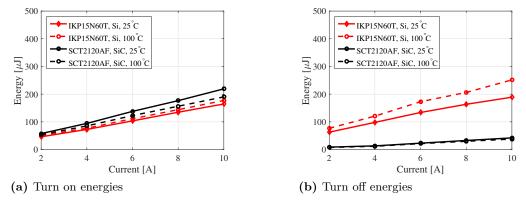

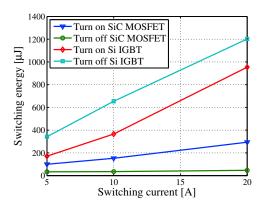

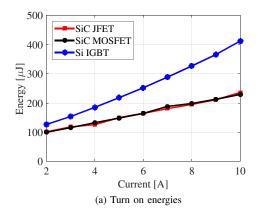

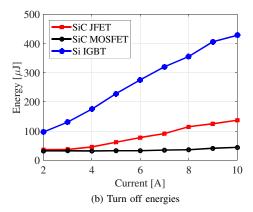

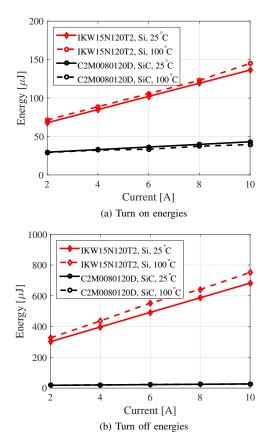

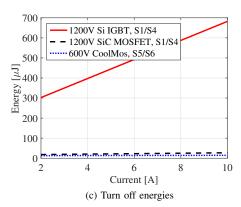

**Figure 4.6:** Measured switching energies for different current levels and a junction temperature of  $25\,^{\circ}\mathrm{C}$

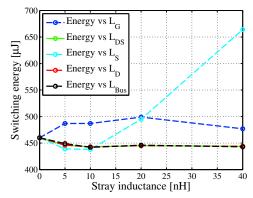

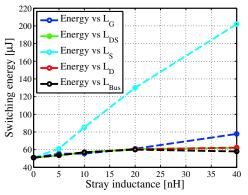

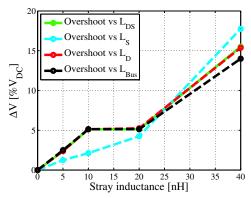

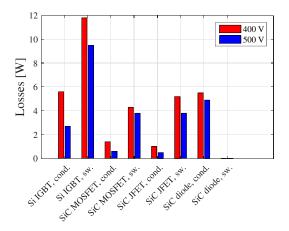

obtain the switching energies plotted in Fig. 4.6. It is commonly known that SiC switching devices have significantly lower switching energies compared to their Si IGBT alternatives. It is therefore only worthy of comment that the SiC JFET and SiC MOSFET have very similar turn on energies throughout the current range. However, the SiC MOSFET shows turn off energies almost constant throughout

the measured current range, which are much lower than the turn off energies of the SiC JFET, that are increasing with the switched current.

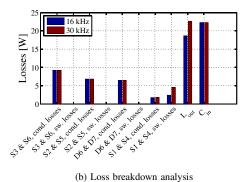

#### 4.1.4 Loss breakdown analysis

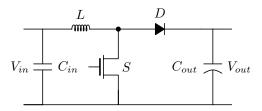

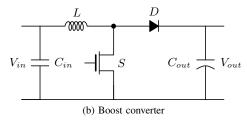

Based on the previous analysis on the static and dynamic characteristics of the semiconductor devices, loss models can be developed and used for a loss breakdown analysis. The performance analysis is carried out on a simple boost converter. This topology has been chosen not only due to its low complexity (only one switching element, one diode and one boost inductor are necessary as depicted in Fig. 4.7), but also because it is generally necessary in a transformer-less PV inverter system to obtain a constant DC link voltage and the boost converter then acts as a pre-regulator [35, 66].

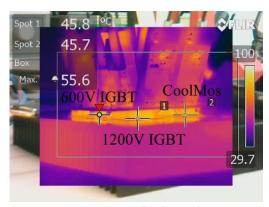

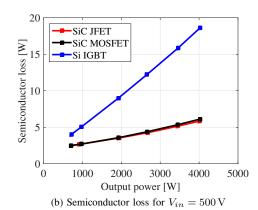

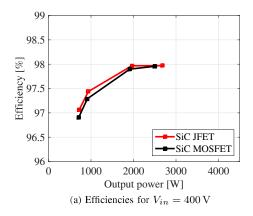

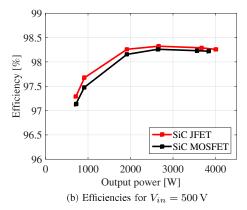

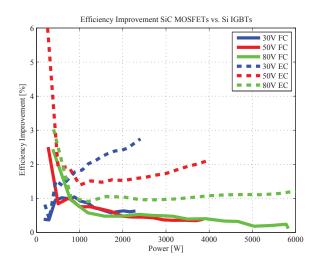

Figure 4.7: Schematic of a conventional boost converter