## **Custom Integrated Circuit Design for Portable Ultrasound Scanners**

Llimos Muntal, Pere

Publication date: 2016

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Llimos Muntal, P. (2016). Custom Integrated Circuit Design for Portable Ultrasound Scanners. Technical University of Denmark.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Pere Llimós Muntal

# **Custom Integrated Circuit Design for Portable Ultrasound Scanners**

Ph.D. Thesis, November 2016

Pere Llimós Muntal

# **Custom Integrated Circuit Design for Portable Ultrasound Scanners**

Ph.D. Thesis, November 2016

#### **Custom Integrated Circuit Design for Portable Ultrasound Scanners**

#### Author:

Pere Llimós Muntal

#### **Supervisors:**

Ivan H.H. Jørgensen — DTU Elektro, Electronics Group Erik Bruun — DTU Elektro, Electronics Group

Department of Electrical Engineering Electronics Group Technical University of Denmark Elektrovej building 325 DK-2800 Kgs. Lyngby Denmark

www.ele.elektro.dtu.dk

Tel: (+45) 45 25 38 00 Fax: (+45) 45 88 01 17 E-mail: hw@elektro.dtu.dk

Release date: 30<sup>th</sup> November 2016

Category: 1 (public)

Edition: First

Comments: This thesis is submitted in partial fulfillment of the requirements for

obtaining the Ph.D. degree at the Technical University of Denmark.

Rights: © Pere Llimós Muntal, 2016

## Preface and Acknowledgment

This thesis is submitted in partial fulfillment of the requirements for obtaining the Ph.D. degree from the Technical University of Denmark (DTU). This project is part of the Advanced Technology Foundation (Innovationsfonden) platform number 82-2012-4, "A new platform and business model for on-demand diagnostic ultrasound imaging", also known as Futuresonic. This project has been done in collaboration with BK Ultrasound, DTU Nanotech and Center of Fast Ultrasound Imaging (CFU) at DTU. The project has been supervised by Professor Erik Bruun and Associate Professor Ivan Harald Holger Jørgensen.

Even though a Ph.D. project is as much technical work as it is self-management, this project would have not been completed without the support of several people. I would like to take this chance to thank you all.

- A very special thank you to Ivan Harald Holger Jørgensen for all the support, supervision, discussions and much more. You have always been available even in a short-notice time for both technical and non-technical discussions. Focused approach, out of the box ideas, hard work, realistic thinking, and availability. An awesome combination for more than a supervisor.

- A very special thank you to Erik Bruun. First of all, because I would not be here

at all if it was not for you. Also, for always believing in me and supporting in

whatever was needed. You have been a true inspiration. That also includes wine

advice.

- A thank you to the Advanced Technology Foundation (Innovationsfonden) for giving me the opportunity to be part of this research platform.

- A thank you to Trond Ytterdal for the external stay. It was a great period both in a technical and personal way and you received me with open arms.

- A thank you to Henriette D. Wolff for your day-to-day hard work in the department. You are the "mother" of ELE and I have no idea what we would do without you.

- A thank you to Allan Jørgensen for technical assistance with the development tools and keeping the servers fully functional so that everybody can work efficiently.

- A thank you to all the people I have been working with from BK Ultrasound, it has been a pleasure to collaborate with you.

- A thank you to all the Ph.D. students and personal in the ELE group that has been a part of these last three years. This is more than a group, it is a great family to be part of, and I will never forget this period.

- A great thank you Dennis Øland Larsen and Niels Marker-Villumsen for all the long hours spent discussing all sorts of related (and VERY unrelated) topics, for always being available and very willing to help and BILF-ing. You have been coworkers, mentors, friends... and I can not thank you enough for that.

- A great thanks to all my friends living in Copenhagen. Living abroad is not always easy, but I have been lucky enough to find all of you.

- Finally, an incredibly special thanks to my father Jaume, my mother Montse, my brother Albert and Pat. Even though you are not here in Denmark, you have no idea how much your continuous support means to me. This would have definitely not been possible without you.

## Abstract

This work concerns the integrated circuitry contained inside a portable ultrasound scanner. These scanners are size and power limited, therefore, the main challenge is to achieve an acceptable picture quality within those restrictions. The structure of portable ultrasound scanners is different from traditional static ultrasound scanners since the data acquired is pre-beamformed, and thereby reduced, in the handheld probe. As a result, the circuitry inside the handheld probe is complex and is required to be small and efficient. Furthermore, it needs to reach enough performance to generate a usable picture quality, within the area and power budget limitations.

A handheld probe for portable ultrasound scanners contains several transducers, transmitting channels and receiving channels. In order to pre-beamform, the transmitting channels individually excite the transducers in a sequence filling the imaging plane and the signals received from each transmit burst area summed. Each receiving channel is required to individually amplify and delay its signal in order to correctly pre-beamform. The handheld probe delivers the data to a processing unit digitally, hence, analog to digital converters (ADCs) are contained in the probe.

Due to the nature of ultrasonic transducers, the transmitting circuitry needs to generate high-voltage pulses to drive them. Furthermore, the low-voltage receiving circuitry has to provide high enough signal to noise ratio (SNR) in order to generate usable imaging. For the purpose of evaluating the feasibility of the transmitting and receiving circuitry of a handheld probe for portable ultrasound scanners, three integrated circuit prototypes have been fabricated. Measurements have been performed on all of them with satisfactory results.

The first part of this project is focused on the high-voltage transmitting channels circuitry. This circuitry is required to generate pulses in the range of  $100\,\mathrm{V}$  with frequencies around  $5\,\mathrm{MHz}$ . The first prototype contains a full reconfigurable single-ended transmitting channel occupying a die area of  $0.938\,\mathrm{mm}^2$  and a power consumption of  $1.41\,\mathrm{mW}$ . The second prototype contains a full differential transmitting channel, which has improvements on performance, smaller die area of  $0.18\,\mathrm{mm}^2$  and lower power consumption of  $0.936\,\mathrm{mW}$ .

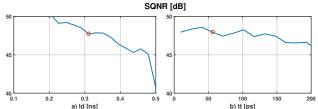

The second part of the project aims at the receiving channel circuitry. The third prototype includes a continuous-time delta-sigma analog-to-digital converter (CTDS ADC) operating at a sampling frequency of 320 MHz, a SNR of 45 dB, occupying an area of 0.0175 mm<sup>2</sup> and a power consumption of 0.594 mW. The CTDS ADC digitizes the signal before the pre-beamform summing is applied. The SNR of the ADC is directly linked to the picture quality of the imaging. However, the SNR is also related to the power consumption, creating a tradeoff between power and picture quality. The design approach will be to achieve the minimum SNR that generates an acceptable picture quality while using the minimum power possible. The ADC is implemented as an oversampled data converter with 1-bit output in order to simplify the accurate digital delay needed in each receiving channel to pre-beamform. Using this approach, the digital delay can be very efficiently implemented as an inverter based digital delay line with switches, achieving accurate precise delay that scales with technology.

## Resumé

Dette arbejde vedrører de integrerede kredsløb, der indgår som en del af en bærbar ultralydsskanner. Denne type scanner er begrænset af krav til størrelse og effektforbrug. De primære udfordringer er derfor at opnå en acceptabel billedkvalitet indenfor de fastsatte krav. Bærbare ultralydsskannere er opbygget forskelligt fra statiske ultralydsskannere, da dataopsamlingen i den håndholdte probe er pre-beamformed, hvilket medfører en reduceret datamængde. Det komplekse databehandlingskredsløb i den håndholdte probe skal både være areal- og effekt-effektivt, kredsløbet skal samtidig opnå en høj ydelse indenfor de fastsatte budgetter for areal og effektforbrug.

En håndholdt probe der anvendes til bærbare ultralydsskannere indeholder adskillige transducere, der hver især er tilknyttet en dedikeret sender og modtager. Prebeamformningen foregår ved at hver enkel sendekanal exciterer transduceren i en sekvens, samtidig med at modtager-kanalernes data summeres for hver excitation. Det er påkrævet at hver modtager-kanal både forstærker og forsinker dens signal for at opnå korrekt prebeamformning. Den håndholdte probe indeholder analog-til-digital-konvertere (ADC), der opsamler analog data og sender disse videre i digital form til en databehandlingsenhed.

Den fysiske opbygning af ultralydstransducere gør, at det er nødvendigt at drive transducerne med firkantpulser med høj spænding. Lavspændingsmodtagerne skal opnå et stort signal-til-støjforhold (SNR) for at kunne generere brugbare billeder. Tre integrerede kredsløbsprototyper er blevet fabrikeret for at sandsynliggøre anvendelsen af sende- og modtagekredsløbenes til brug i bærbare ultralydsskannere. De tre prototyper er blevet verificeret eksperimentelt med tilfredsstillende resultater.

Den første del af projektet er fokuseret på højspændingssendekanalerne. Disse kredsløb skal generere spændingspulser op til  $100\,\mathrm{V}$  med frekvenser omkring  $5\,\mathrm{MHz}$ . Den første prototype chip, indeholder en fuld rekonfigurerbar single-ended sendekanal, der optager et chipareal på  $0.938\,\mathrm{mm}^2$  og har et effektforbrug på  $1.41\,\mathrm{mW}$ . Den anden prototype chip, indeholder en fulddifferentiel sendekanal, som har forbedret ydelse, optager mindre chipareal på  $0.18\,\mathrm{mm}^2$  og har et lavere effektforbrug på  $0.936\,\mathrm{mW}$  sammenlignet med den første prototype.

Den anden del af projektet er fokuseret på modtagerkredsløbet. Den tredje prototype chip, indeholder en kontinuerttids delta-sigma analog-til-digital-konverter (CTDS ADC), der opererer med en samplingfrekvens på 320 MHz, SNR på 45 dB, optager et chipareal på 0.0175 mm², og har effektforbrug på 0.594 mW. Formålet med denne er at digitalisere modtagesignalet før pre-beamformning. SNR for ADC'en er direkte forbundet til billedkvaliteten. Forbedring af SNR er samtidig forbundet med et højere effektforbrug, hvilket skaber en afvejning mellem effektforbrug og billedkvalitet. Designfremgangsmåden er at opnå det mindst mulige SNR, som fører til en acceptabel billedkvalitet med det mindst mulige effektforbrug. ADC'en er implementeret som en oversamplet konverter med 1-bit for at simplificere den præcise digitale forsinkelse, der er nødvendig i hver modtagekanal. Ved brug af denne fremgangsmåde kan den digitale forsinkelse implementeres meget effektivt som en digital inverter-baseret delay line, hvorved der kan opnås en præcis forsinkelse, der er skalerbar med procesteknologi.

## Contents

| $\mathbf{P}_{1}$ | refac  | e and Acknowledgement                        | i    |

|------------------|--------|----------------------------------------------|------|

| A                | bstra  | act                                          | ii   |

| $\mathbf{R}$     | esum   | né                                           | iii  |

| Li               | ist of | Abbreviations                                | x    |

| Li               | ist of | Figures                                      | xiii |

| 1                | Inti   | roduction                                    | 1    |

|                  | 1.1    | Thesis Outline                               | 2    |

| 2                | Cur    | rrent Ultrasound Scanning Systems            | 5    |

|                  | 2.1    | Traditional Static Ultrasound Scanners       | 5    |

|                  | 2.2    | Portable Ultrasound Scanners                 | 6    |

| 3                | Ult    | rasonic Transducers                          | 9    |

|                  | 3.1    | Introduction                                 | 9    |

|                  | 3.2    | Ultrasonic Transducer Types                  | 10   |

|                  | 3.3    | Transducer selection                         | 12   |

| 4                | Dig    | ital Probe Portable Ultrasound System        | 13   |

|                  | 4.1    | System Characteristics                       | 13   |

|                  | 4.2    | Block Structure                              | 14   |

|                  | 4.3    | Specifications                               | 16   |

|                  | 4.4    | Ultrasound Scanner Circuits State of the Art | 19   |

| 5                | Circ   | cuit Design                                  | 23   |

|                  | 5.1    | Single-ended Transmitting Circuit - ASIC0    | 23   |

|                  |        | 5.1.1 Overview                               | 23   |

|                  |        | 5.1.2 Design                                 | 24   |

|                  |        | 5.1.3 Measurements                           | 28   |

|                  | 5.2    | Differential Transmitting Circuit - ASIC1    | 31   |

|               |                        | 5.2.1                | Overview                                                                          |                        | 31         |

|---------------|------------------------|----------------------|-----------------------------------------------------------------------------------|------------------------|------------|

|               |                        | 5.2.2                | Design                                                                            |                        | 31         |

|               |                        | 5.2.3                | Measurements                                                                      |                        | 36         |

|               | 5.3                    | Tx cir               | cuit comparison and evaluation                                                    |                        | 38         |

|               | 5.4                    | Low N                | Joise Amplifier - ASIC2                                                           |                        | 43         |

|               | 5.5                    | Contin               | nuous-Time Delta-Sigma ADC - ASIC2                                                |                        | 43         |

|               |                        | 5.5.1                | System Level Design                                                               |                        | 44         |

|               |                        | 5.5.2                | Implementation                                                                    |                        | 44         |

|               |                        | 5.5.3                | Simulation Results                                                                |                        | 52         |

|               |                        | 5.5.4                | Measurements                                                                      | •                      | 54         |

| 6             | Sys                    | tem as               | sessment                                                                          |                        | 57         |

|               | 6.1                    | Power                | consumption assessment                                                            |                        | 57         |

|               | 6.2                    | Area a               | assessment                                                                        |                        | 60         |

| 7             | Cor                    | nclusio              | ns                                                                                |                        | 63         |

|               | 7.1                    | Future               | e Work                                                                            |                        | 64         |

| 8             | Oth                    | er Res               | search Topics                                                                     |                        | 67         |

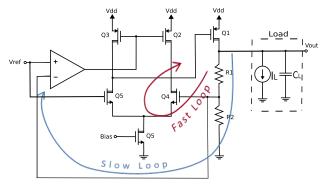

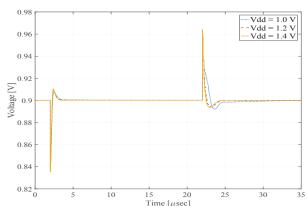

|               | 8.1                    | Capac                | itor-Free Low Drop-Out Linear Regulator                                           |                        | 67         |

| Bi            | bliog                  | graphy               |                                                                                   |                        | 70         |

| ${f A}_{f J}$ | open                   | $\operatorname{dix}$ |                                                                                   |                        | <b>7</b> 6 |

| $\mathbf{A}$  | $\mathbf{Int}\epsilon$ | egrated              | l Reconfigurable High-Voltage Transmitting Circuit for CM                         | ИU                     | Ts 77      |

| В             |                        | h-volta<br>tions     | age Pulse-triggered SR Latch Level-Shifter Design Consi                           |                        | 83         |

| $\mathbf{C}$  | Inte                   | egrated              | l reconfigurable high-voltage transmitting circuit for CMU                        | $\mathbf{T}\mathbf{s}$ | 91         |

| D             |                        | egrated<br>CMUT      | l Differential Three-Level High-Voltage Pulser Output Sta<br>Ts                   |                        | 03         |

| ${f E}$       | Inte                   | egrated              | l Differential High-Voltage Transmitting Circuit for CMUT                         | Γs1                    | 09         |

| $\mathbf{F}$  | -                      |                      | vel design of a continuous-time $\Delta$ $\Sigma$ modulator for portable scanners |                        | 15         |

| G       | A Capacitor-Free, Fast Transient Response Linear Voltage Regulator<br>In a 180 nm CMOS  | r<br>121 |

|---------|-----------------------------------------------------------------------------------------|----------|

| н       | ${\bf Integrated\ reconfigurable\ high-voltage\ transmitting\ circuit\ for\ CMUT}$      | `s127    |

| Ι       | System-level Design of an Integrated Receiver Front-end for a Wireless Ultrasound Probe | -<br>139 |

| ${f J}$ | A 10MHz Bandwidth Continuous-Time Delta-Sigma Modulator for                             | r        |

${\bf K}$  Capacitor-Free, Low Drop-Out Linear Regulator in a 180 nm CMOS

**153**

161

Portable Ultrasound Scanners

for Hearing Aids

## List of Abbreviations

ADC Analog to Digital Converter

ASIC Application Specific Integrated Circuit

A - TGC Adaptive Time-Gain Control

BW Bandwidth

CFU Center for Fast Ultrasound imaging

CIFB Cascade of Integrators with Feedback

CMFB Common Mode Feedback

CMOS Complementary Metal-Oxide-Semiconductor

CMUT Capacitive Micromachined Ultrasonic Transducer

CS Common Source

CTDS Continuous-Time Delta-Sigma

CTDSADC Continuous-Time Delta-Sigma Analog to Digital Converter

DAC Digital to Analog Converter

DD Digital Delay

DTDS Discrete-Time Delta-Sigma

DTU Denmark Technical University

DTR Data Transfer Rate

FFT Fast Fourier Transform

FoM Figure of Merit

GBW Gain-Bandwidth Product

IC Integrated Circuit

LNA Low Noise Amplifier

LDO Low-Drop Out

MEMS Micro-Electro-Mechanical Systems

MOS Metal-Oxide-Semiconductor

MSA Maximum Stable Amplitude

NOCG Non-Overlapping Clock Generator

NRZ Non-Return-to-Zero

OSR Oversampling Ratio

OTA Operational Transconductance Amplifier

PCB Printed Circuit Board

PEX Parasitic Extracted

Rx Receiving circuit

SAR Successive Approximation Register

SASB Synthetic Aperture Sequential Beamforming

SCH Schematic

SDNR Signal to Noise and Distortion Ratio

SNR Signal to Noise Ratio

SQNR Signal to Quantization Noise Ratio

SR Slew Rate

Tx Transmitting circuit

USB Universal Serial Bus

# List of Figures

| 1.1 | Overview of the thesis chapters and related published work. *The author of this work is not the main designer. **Suggested for submission                                                                                                                                                                                              | 4       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 2.1 | Traditional static ultrasound scanner structure                                                                                                                                                                                                                                                                                        | (       |

| 2.2 | Portable ultrasound scanner structure                                                                                                                                                                                                                                                                                                  | 7       |

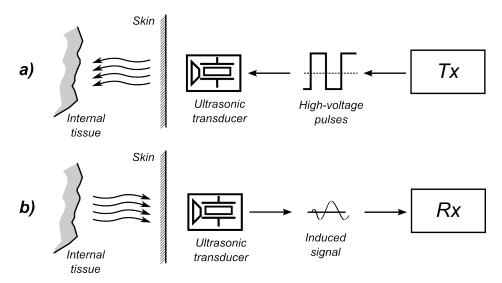

| 3.1 | Ultrasonic transducer operation: a) Transmission. b) Reception                                                                                                                                                                                                                                                                         | 10      |

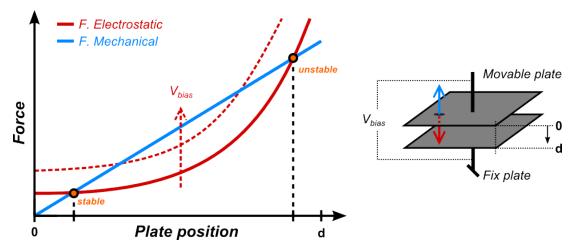

| 3.2 | CMUT operation principle. Electrostatic force, mechanical force and stable/unstable equilibrium points                                                                                                                                                                                                                                 | 11      |

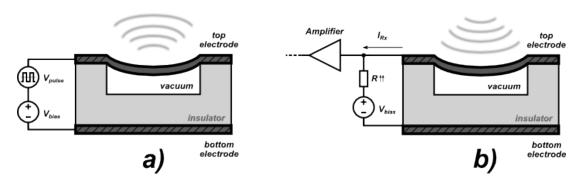

| 3.3 | CMUT connection: a) Transmitting. b) Receiving                                                                                                                                                                                                                                                                                         | 12      |

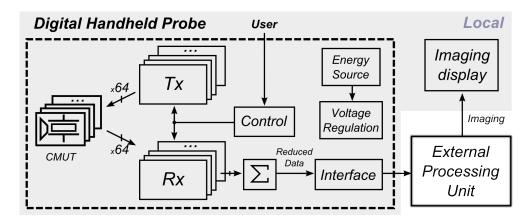

| 4.1 | Digital probe portable ultrasound system structure                                                                                                                                                                                                                                                                                     | 14      |

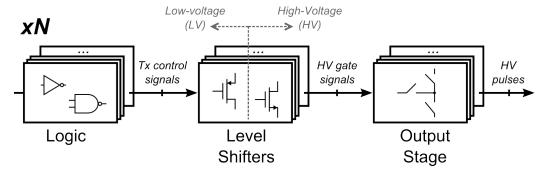

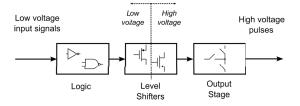

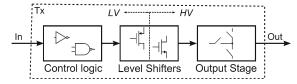

| 4.2 | Structure of the transmitting circuitry (Tx). Low-voltage logic block, level shifters and output stage                                                                                                                                                                                                                                 | 1!      |

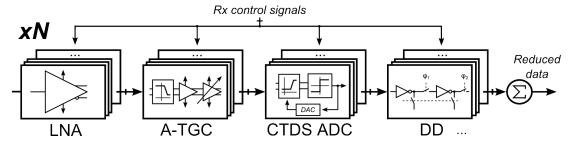

| 4.3 | Structure of the receiving circuitry (Rx). Low noise amplifier (LNA), adaptive time gain control (A-TGC), continuous-time delta-sigma analog-to-digital converter (CTDS ADC), clocked digital delay (DD) and summing block                                                                                                             | 15      |

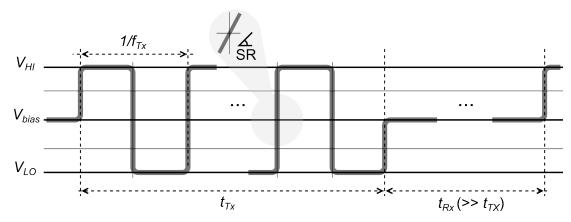

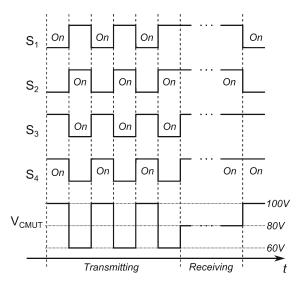

| 4.4 | Typical high-voltage pulsing shape required for CMUT operation. Transmitting frequency $f_{Tx}$ , slew rate SR, transmitting time $t_{Tx}$ , receiving time $t_{Rx}$ and voltage levels $V_{LO}$ , $V_{bias}$ and $V_{HI}$                                                                                                             | 19      |

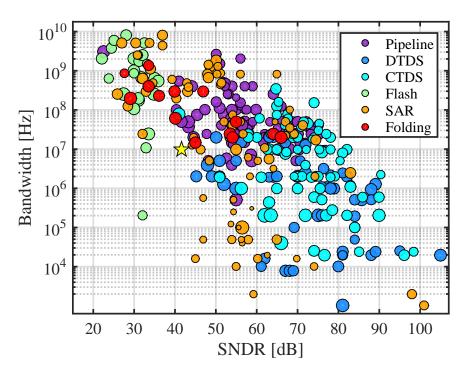

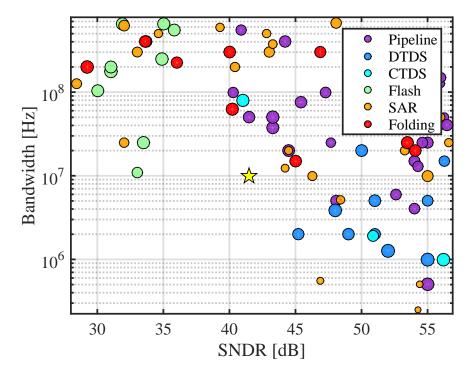

| 4.5 | ADC performance survey plot in function of the SDNR and the BW. The size of the circles is proportional to the FoM of each ADC. The ADC of this project is marked with a star.                                                                                                                                                         | 2       |

| 4.6 | Closer look at the ADC performance survey plot in function of the SDNR and the BW. The size of the circles is proportional to the FoM of each ADC. The ADC of this project is marked with a star                                                                                                                                       | 2       |

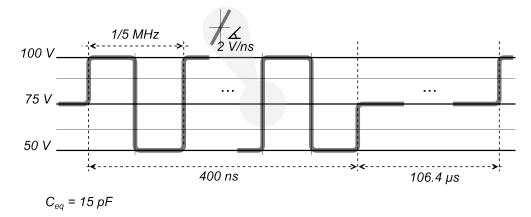

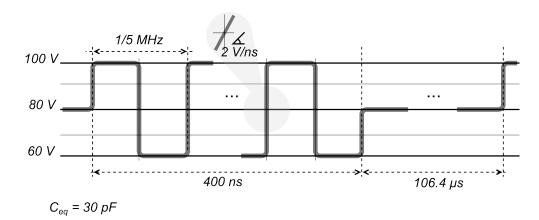

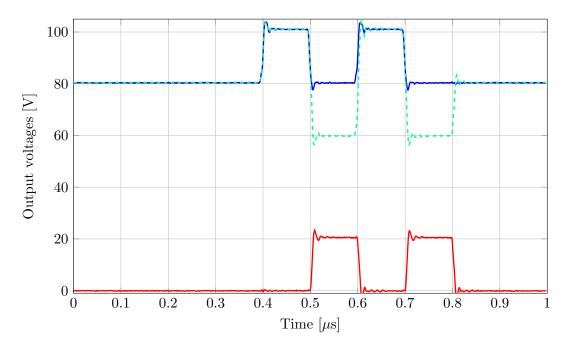

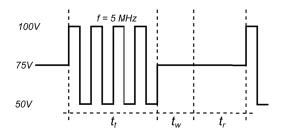

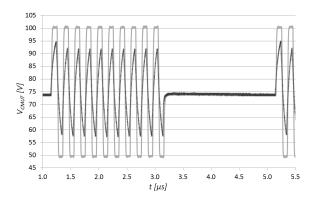

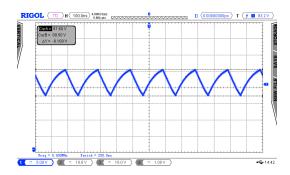

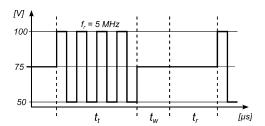

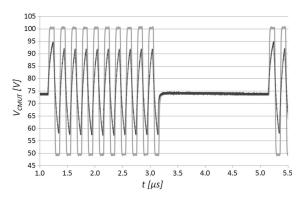

| 5.1 | Tx output in the most demanding driving operation. Tx frequency $f_{Tx} = 5 \text{MHz}$ , slew rate SR = $2 \text{V/ns}$ , transmitting time $t_{Tx} = 400 \text{ns}$ , receiving time = $106.4 \mu\text{s}$ , $V_{LO} = 50 \text{V}$ , $V_{bias} = 75 \text{V}$ , $V_{HI} = 100 \text{V}$ and load equivalent $C_{eq} = 15 \text{pF}$ | $2^{2}$ |

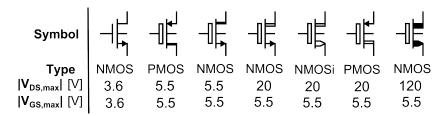

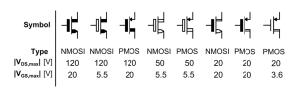

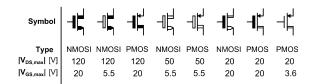

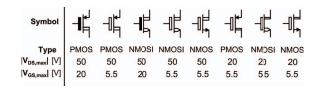

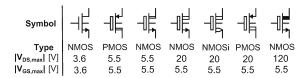

| 5.2 | High-voltage MOS devices                                                                                                                                                                                                                                                                                                               | 24      |

| 5.3 | Structure of the single-ended transmitting circuit                                                                                                                                                                                                                                                                                     | 25      |

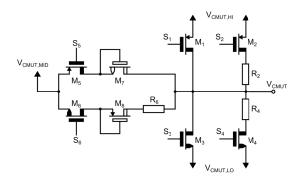

| 5.4 | Schematic of the single-ended output stage                                                                                                                                                                                                                                                                                             | 25      |

| 5.5 | Schematic of the pulse-triggered level shifter topology                                                                                                                                                                                                                                                                                | 2       |

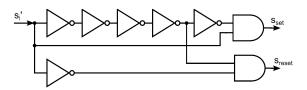

| 5.6 | Low-voltage logic block structure                                                                                                                                                                                                                                                                                                      | 28      |

| 5.7  | Schematic of the low-voltage pulser                                                                                                                                                                                                                                                                                                                                   | 28 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

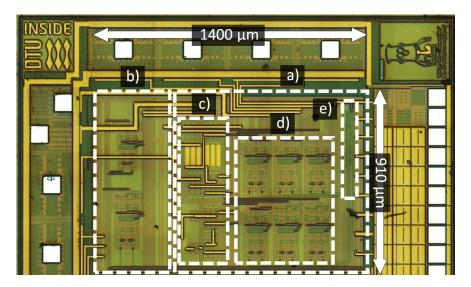

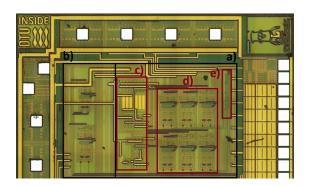

| 5.8  | Picture of the fabricated integrated circuit. a) Tx circuit. b) Isolated level shifters. c) Output stage. d) Level shifters. e) Logic block                                                                                                                                                                                                                           | 29 |

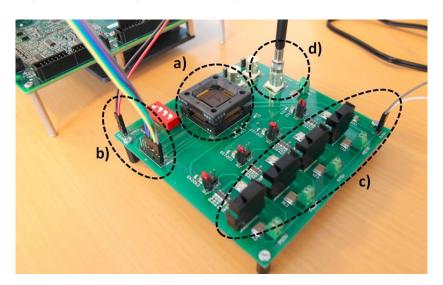

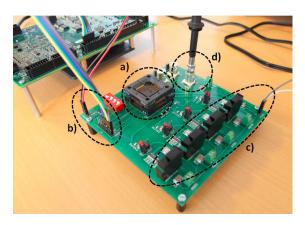

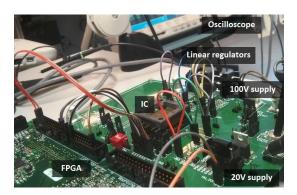

| 5.9  | Setup for ASIC0 measurements. a) ASIC0. b) Xilinx Spartan-6 LX45 FPGA low-voltage signals and low-voltage supply. c) High-voltage supply from a SM 400-AR-8 Delta Elektronika and linear regulators. d) Probe connected to the WaveSurfer 104MXs-B Lecroy oscilloscope                                                                                                | 29 |

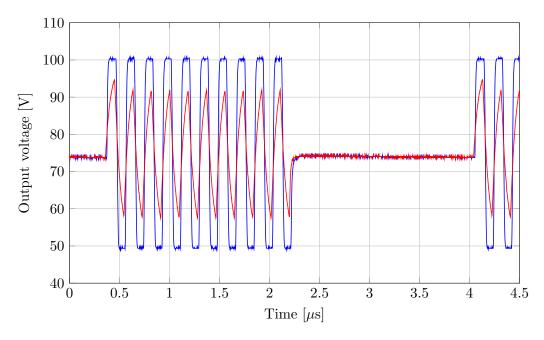

| 5.10 | Measured transmitting circuit output voltage, $V_{CMUT}$ . Fast transitions in blue. Slow transitions in red                                                                                                                                                                                                                                                          | 30 |

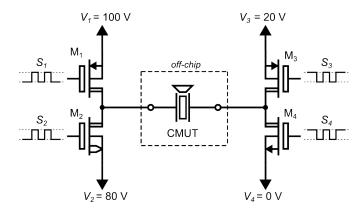

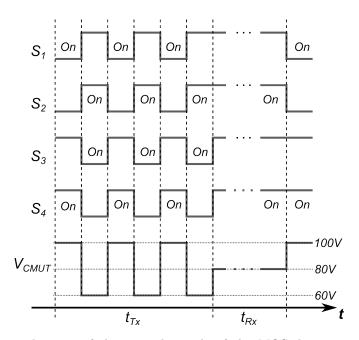

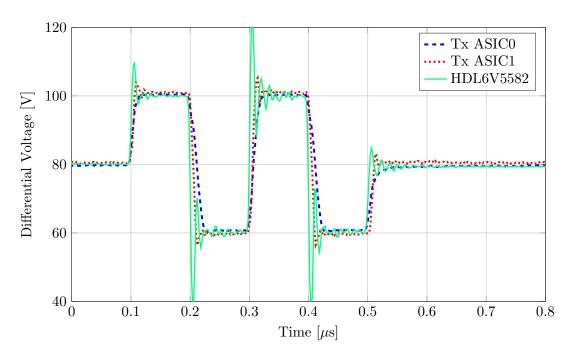

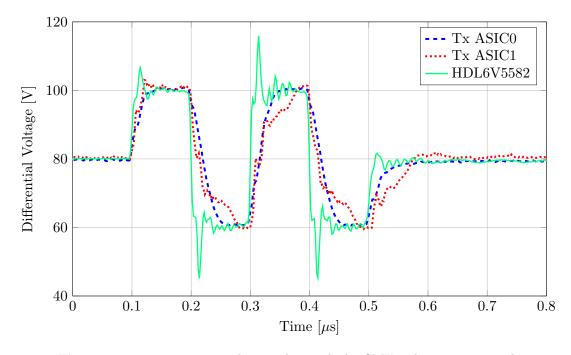

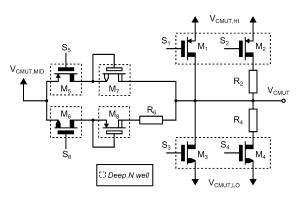

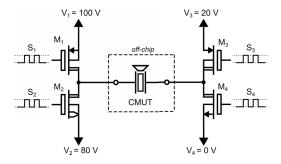

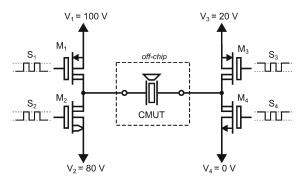

| 5.11 | Voltage difference across the CMUT load specified for the differential Tx. Transmitting frequency $f_{Tx}=5\mathrm{MHz}$ , slew rate SR = $2\mathrm{V/ns}$ , transmitting time $t_{Tx}=400\mathrm{ns}$ , receiving time = $106.4\mathrm{\mu s}$ , $V_{LO}=60\mathrm{V}$ , $V_{bias}=80\mathrm{V}$ , $V_{HI}=100\mathrm{V}$ and load equivalent $C_{eq}=30\mathrm{pF}$ | 31 |

| 5.12 | Structure of the differential transmitting circuit                                                                                                                                                                                                                                                                                                                    | 32 |

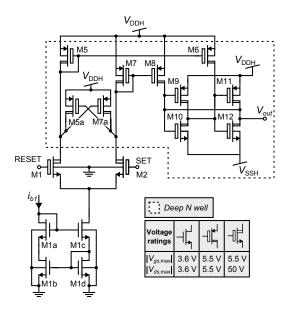

| 5.13 | High-voltage MOS devices                                                                                                                                                                                                                                                                                                                                              | 32 |

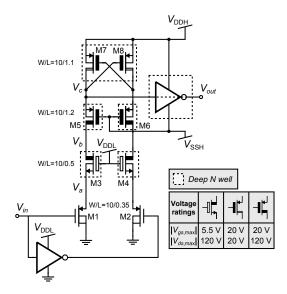

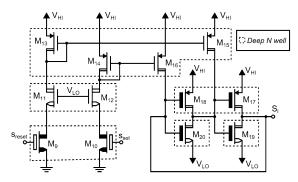

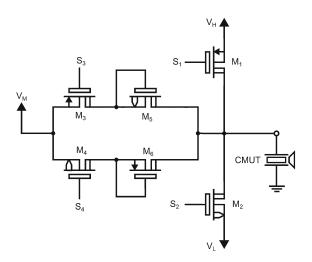

| 5.14 | Schematic of the differential output stage topology                                                                                                                                                                                                                                                                                                                   | 32 |

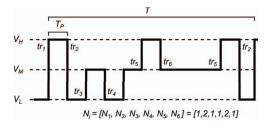

| 5.15 | Time diagram of the control signals of the MOS devices and the equivalent differential voltage across the CMUT                                                                                                                                                                                                                                                        | 33 |

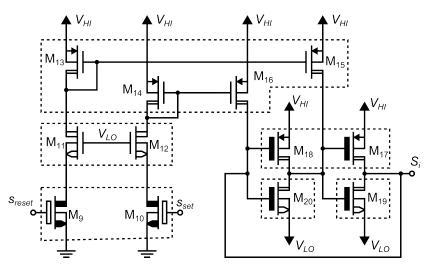

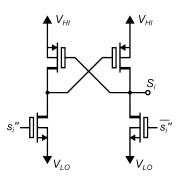

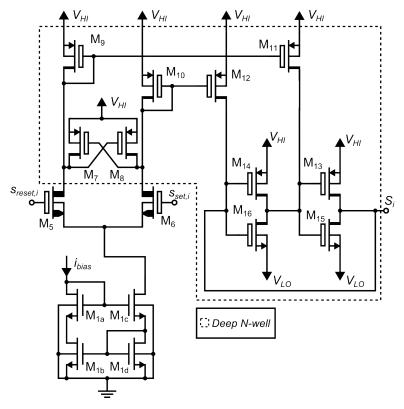

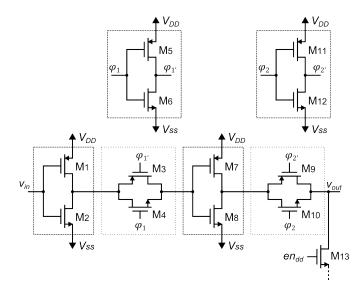

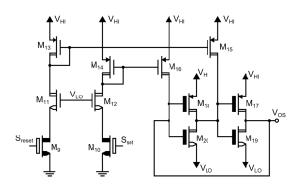

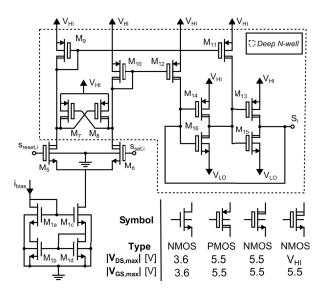

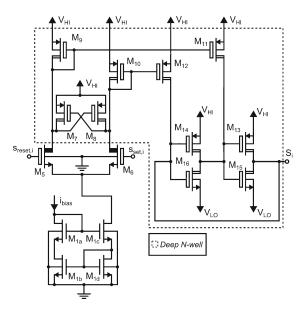

| 5.16 | Schematic of the low-voltage cross coupled simple topology used for level shifter number four. All width/length ratios are $0.4\mu\text{m}/0.5\mu\text{m}.$                                                                                                                                                                                                           | 34 |

| 5.17 | Schematic of the improved pulse-triggered level shifter. $V_{LO} = V_{HI}$ - 5 V.                                                                                                                                                                                                                                                                                     | 35 |

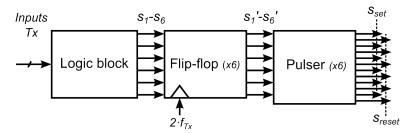

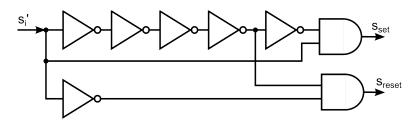

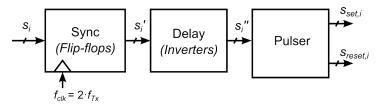

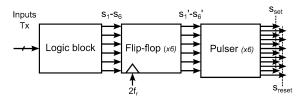

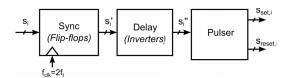

| 5.18 | Block structure of the low-voltage control logic                                                                                                                                                                                                                                                                                                                      | 36 |

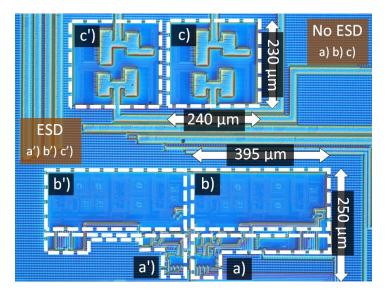

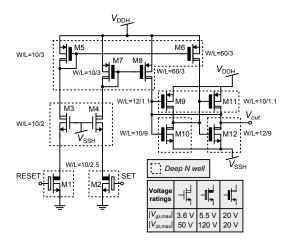

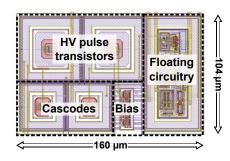

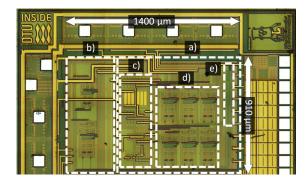

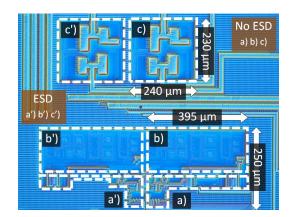

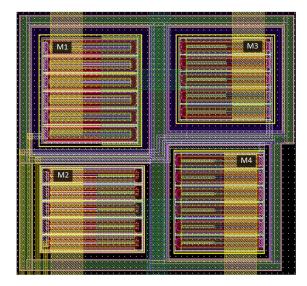

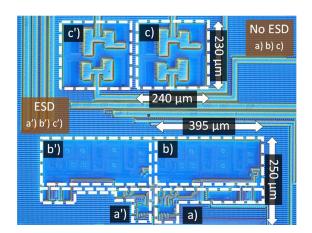

| 5.19 | Picture of the taped-out differential transmitting circuit. a) a') Low-voltage logic, b) b') Level shifters, c) c') Output stage                                                                                                                                                                                                                                      | 37 |

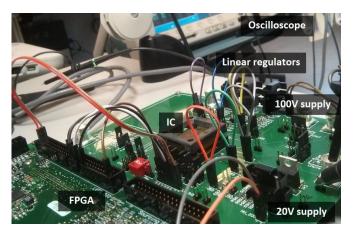

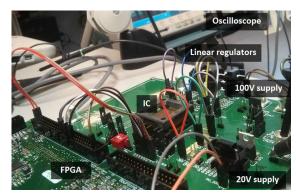

| 5.20 | Measurement setup for the differential transmitting circuit                                                                                                                                                                                                                                                                                                           | 37 |

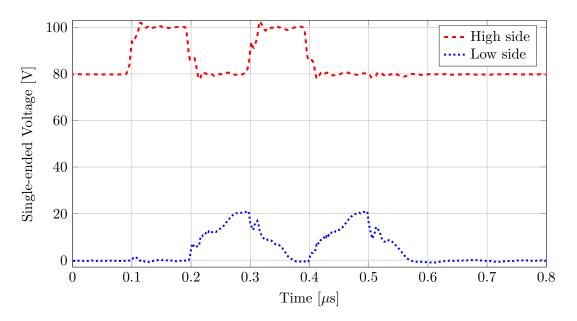

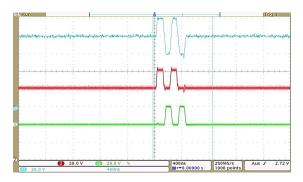

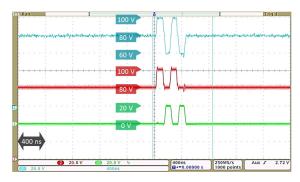

| 5.21 | Measurements of the output terminals of the differential Tx. The blue and red trace are the voltages measured at the high-voltage and low-voltage terminals of the Tx respectively. The green dotted trace is the differential voltage                                                                                                                                | 38 |

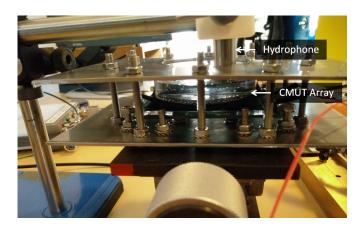

| 5.22 | Transmitting measurement setup. a) CMUT array submerged in water. b) Hydrophone                                                                                                                                                                                                                                                                                       | 39 |

| 5.23 | Transmitting voltage pulses without load                                                                                                                                                                                                                                                                                                                              | 40 |

| 5.24 | Transmitting voltage pulses with the CMUT element connected                                                                                                                                                                                                                                                                                                           | 40 |

| 5.25 | Single-ended pulses from the $\mathrm{Tx}_1,\ldots,\ldots$                                                                                                                                                                                                                                                                                                            | 41 |

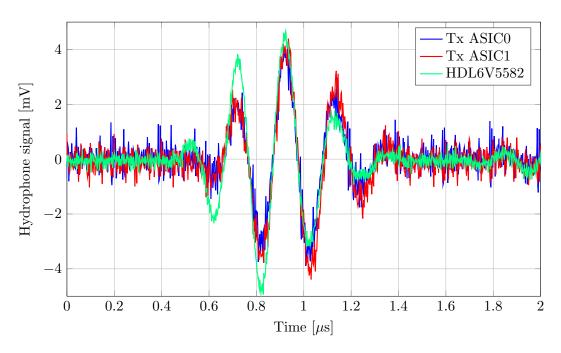

| 5.26 | Signal received with the hydrophone by pulsing the CMUT element                                                                                                                                                                                                                                                                                                       | 42 |

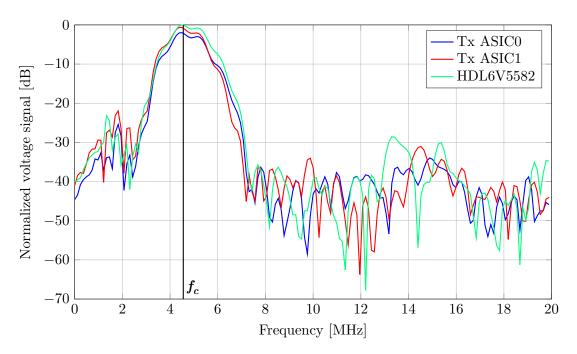

| 5.27 | FFT of the signal received with the hydrophone by pulsing the CMUT element                                                                                                                                                                                                                                                                                            | 42 |

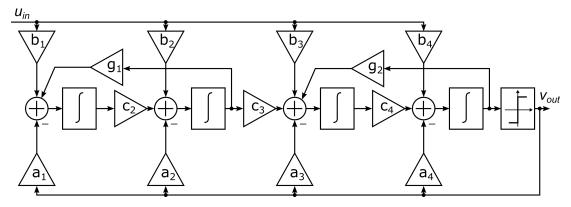

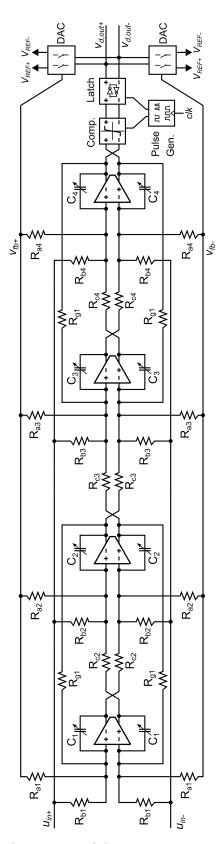

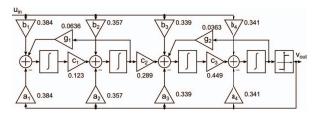

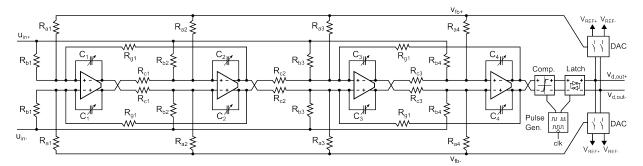

| 5.28 | Structure of the fourth order continuous-time delta-sigma ADC                                                                                                                                                                                                                                                                                                         | 44 |

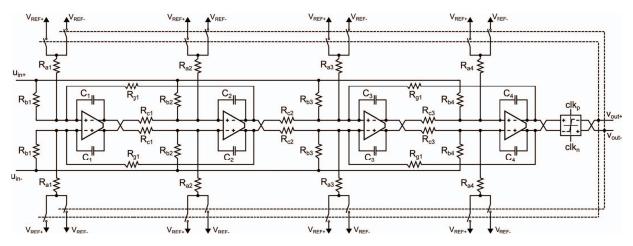

| 5.29 | Implementation of the continuous-time delta-sigma ADC                                                                                                                                                                  | 46 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

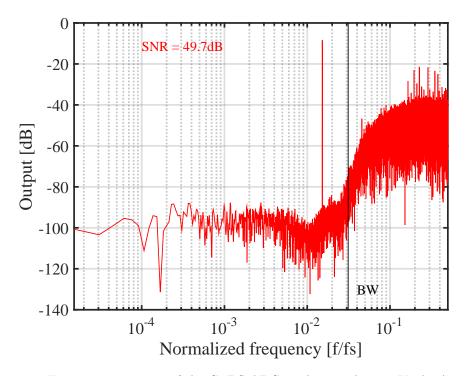

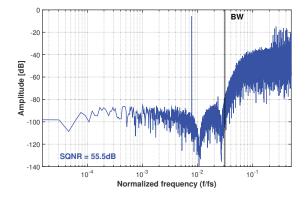

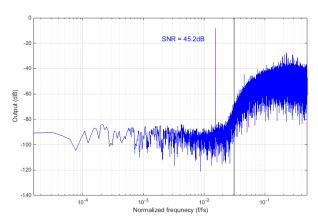

| 5.30 | Frequency spectrum of the CTDS ADC implemented using VerilogA models of the blocks. Input amplitude $u_{in}=0.6\mathrm{V.}$                                                                                            | 47 |

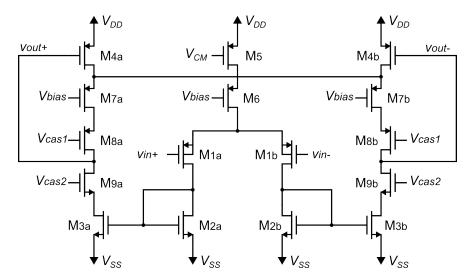

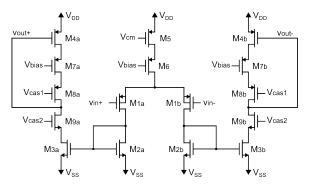

| 5.31 | Schematic of the symmetrical OTA, with cascodes and common-mode feedback                                                                                                                                               | 48 |

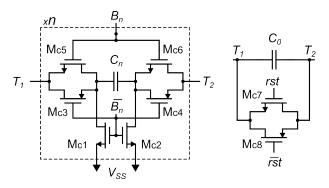

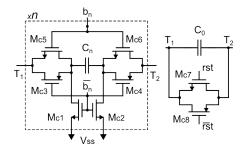

| 5.32 | Schematic of the integrating capacitor array, which is adjusted with the bits $B_n$ , $n=3$ . Reset functionality implemented with the signal $rst$                                                                    | 49 |

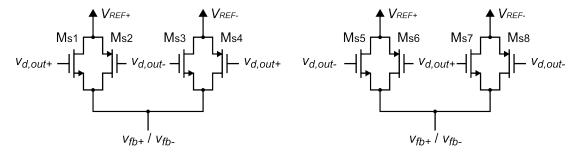

| 5.33 | Schematic of the voltage feedback DACs                                                                                                                                                                                 | 50 |

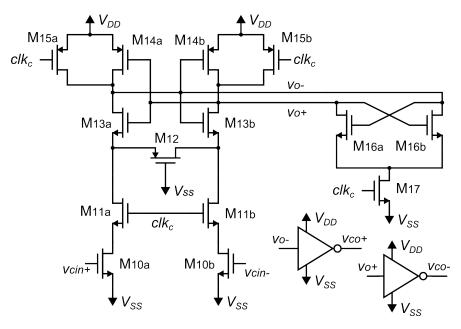

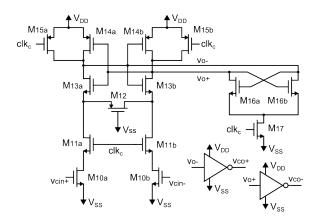

| 5.34 | Schematic of the high-speed clocked comparator                                                                                                                                                                         | 51 |

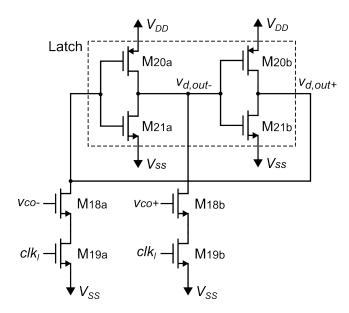

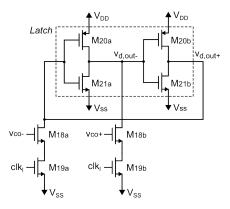

| 5.35 | Schematic of the pull-down clocked latch                                                                                                                                                                               | 51 |

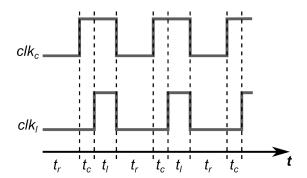

| 5.36 | Comparator and latch timing diagram                                                                                                                                                                                    | 52 |

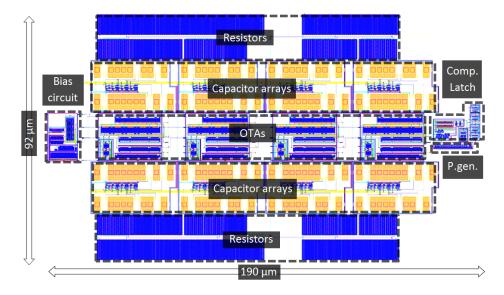

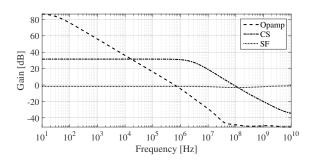

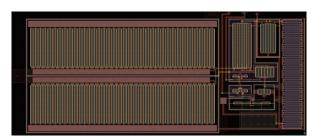

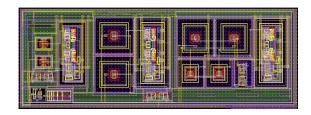

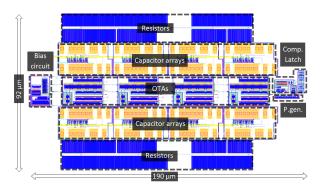

| 5.37 | Layout of the full CTDS ADC designed                                                                                                                                                                                   | 52 |

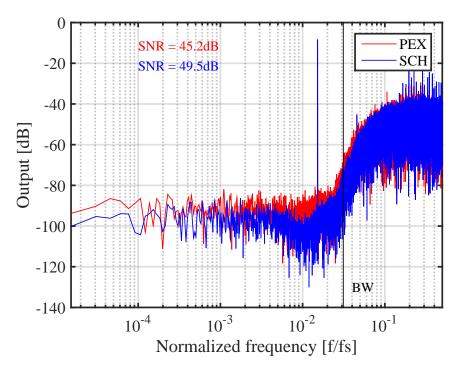

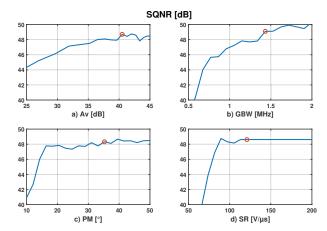

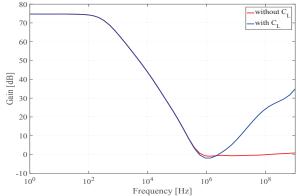

| 5.38 | Frequency response of the CTDSM in the nominal corner. Input amplitude $u_{in} = 0.6 \text{V}$ . Simulations on schematic (SCH) and with parasitic extraction (PEX)                                                    | 53 |

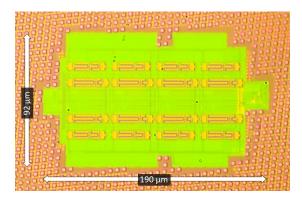

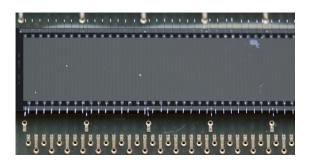

| 5.39 | Picture of the fabricated integrated circuit ASIC2                                                                                                                                                                     | 54 |

| 5.40 | Continuous-time delta-sigma ADC measurements setup                                                                                                                                                                     | 54 |

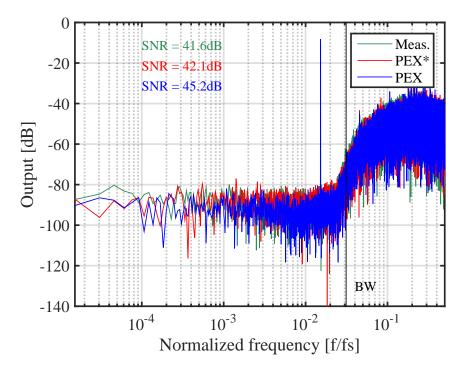

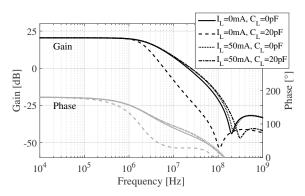

| 5.41 | Frequency response of the CTDS ADC with $u_{in}=0.6\mathrm{V}$ . Measurements (Meas.), simulated results with parasitic extraction and measurement setup modeled (PEX*) and simulated with parasitic extraction (PEX). | 56 |

| 6.1  | Digital probe portable ultrasound system structure overview                                                                                                                                                            | 58 |

| 6.2  | Schematic of a single digital delay unit of the DD line                                                                                                                                                                | 59 |

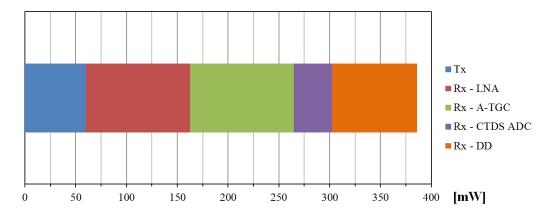

| 6.3  | Power budget distribution of the 64 Tx and 64 Rx channels                                                                                                                                                              | 59 |

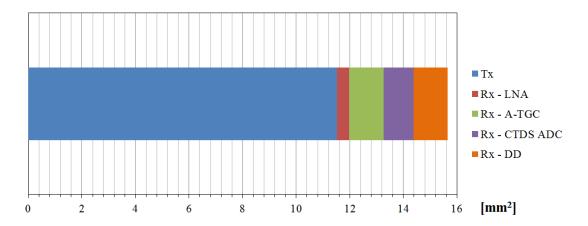

| 6.4  | Die area distribution of the 64 Tx and 64 Rx channels                                                                                                                                                                  | 60 |

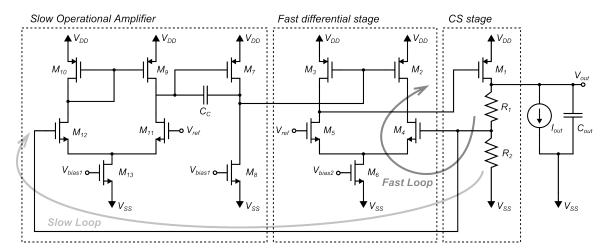

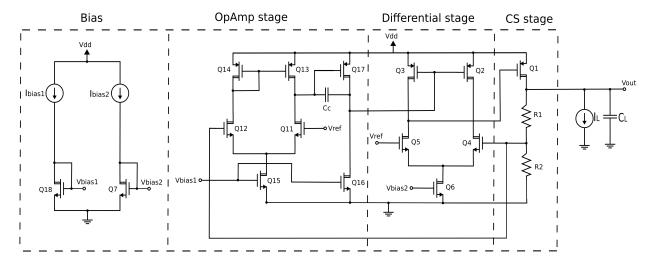

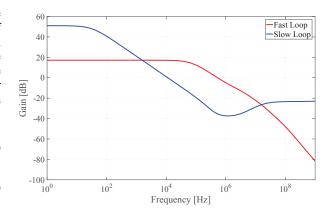

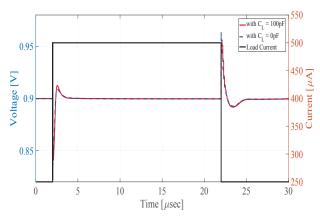

| 8.1  | Schematic of the most recent linear regulator design                                                                                                                                                                   | 68 |

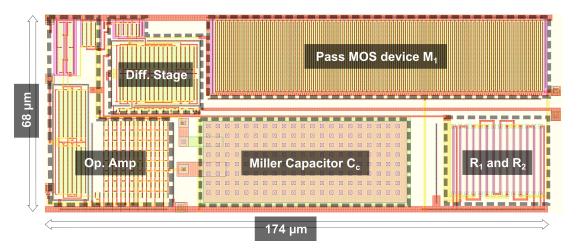

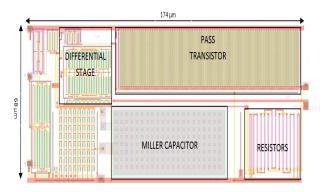

| 8.2  | Layout of the capacitor-free low drop-out linear regulator                                                                                                                                                             | 69 |

## Introduction

This chapter provides an overview of the Ph.D. project documented in this thesis. The motivation and main challenges of this project are described and an outline of the chapters and contributions is given.

Ultrasound imaging is widely used in medical applications. This technique is cost efficient, ionizing radiation free, noninvasive and it allows real time imaging. Throughout the last years, the tendency of ultrasound scanners has been to increase their complexity in order to improve the picture quality. This is possible due to the fact that traditional ultrasound scanners are plugged into the AC mains which effectively supply unlimited power to the scanner. Therefore, the picture quality is limited by the data acquisition and processing, since the electronic circuitry of the scanner is not size or power consumption limited. The resulting system is a high-performance static large ultrasound system with a wide variety of scanning features. However, these ultrasound scanner systems have some inconvenients. Firstly, due to their large size, the transportability is limited. Secondly, the amount of scanners per hospital is low because of the high production cost, which is reflected in the price of the scanner. As a result, the flexibility of ultrasound scanning procedures in hospitals is severely reduced.

In the last decade, high-integration tendencies and technology improvements have enabled the possibility of portable ultrasound scanners [1]. The concept behind these scanners is to reduce the size in order to overcome the lack of flexibility of traditional static ultrasound scanners. Nonetheless, a portable system is supplied with limited power which sets a restriction on the complexity, size and power consumption of the electronics. Furthermore, due to the reduced size of the scanner, the area and power dissipation capabilities of the scanner set another constrain on the design of the electronics. For this reason, the image quality limiting factor of portable ultrasound scanners is not the complexity and precision of the data acquisition and processing, but the complexity and precision of the electronics achievable within the available area and power budget. Designing the electronics for a portable ultrasound scanner is a challenge, since they are required to be small and have low power consumption in order to utilize effectively the area and power budget. Moreover, the circuitry that drives the ultrasonic transducers needs to provide high-voltage levels, which increases the complexity of the design even further.

Generic discrete components are used in traditional static ultrasound scanners for implementing the electronics. These components, even though they are cheap, are typi-

2 Introduction

cally over-designed in terms of area and power consumption to accommodate for a wide variety of applications. As a result, generic discrete components are not efficient for a specific application. This is not a problem for static ultrasound scanners because there are no area or power limitations. Nonetheless, for the handheld-size and power limited portable ultrasound scanners, application specific integrated circuit (ASIC) solutions are needed to fully utilize the area and power budget and achieve the best possible picture quality.

The aim of this Ph.D. project is to assess the feasibility of the integrated electronics of portable ultrasound scanners. This project is part of the Advanced Technology Foundation (Innovationsfonden) platform number 82-2012-4, "A new platform and business model for on-demand diagnostic ultrasound imaging", also known as Futuresonic. This research project is conducted by the Danish companies BK Ultrasound, Meggitt and the Alexandria Institute together with four research groups, Center of Fast Ultrasound Imaging (CFU) at the Denmark Technical University (DTU), DTU Elektro, DTU Nanotech and Radiology at Rigshospitalet. This platform covers complete research on ultrasound systems from the transducer to the imaging. Each company and research group is responsible for a specific part of the platform.

### 1.1 Thesis Outline

This thesis consists of eight chapters:

Chapter 2 presents the current state of ultrasound scanning. Firstly, the traditional static ultrasound scanners are briefly explained and the main advantages and disadvantages are examined. Secondly, portable ultrasound scanners are proposed as an alternative that covers the main disadvantages of traditional systems. Finally, the main implementation challenges of these portable scanners are thoroughly discussed.

Chapter 3 provides an overview of ultrasonic transducers including both piezoelectric transducers and the alternative more recent capacitive micromachined ultrasonic transducers. The main functioning principles and strengths and weaknesses are explained. Furthermore, the transducers used in this project are described.

Chapter 4 describes the digital probe portable ultrasound system that this Ph.D. project is targeting. The integrated circuits designed in this work are costume made to fit in the described portable ultrasound system in order to assess its feasibility. The characteristics, advantages, block structure and specifications are presented. Additionally, an overview of the state of the art of electronic circuitry for ultrasound scanners is provided.

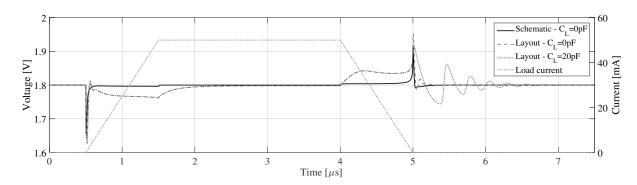

Chapter 5 presents the integrated circuitry designed in this project. Three prototypes were made throughout the three years of this project and they contain circuitry for both the transmitting and receiving parts of the scanner. The first integrated circuit (IC), ASIC0, contains a single-ended transmitting circuit designed in a high-voltage 0.35 µm process. The second IC, ASIC1, contains a differential transmitting circuit also designed in a high-voltage 0.35 µm process. The third IC, ASIC2, contains a continuous-time delta-sigma analog-to-digital converter (ADC) and a low noise amplifier (LNA) for the receiving signal path designed in a 65 nm process. The design process, the topology selection, schematic, layout and measurements of the integrated circuits are presented.

1.1 Thesis Outline 3

Chapter 6 discusses the feasibility of the integrated electronics of the digital probe portable ultrasound system according to the results obtained with the three prototypes. The area and power consumption of the designed blocks together with area and power consumption estimations of the remaining blocks are used for the feasibility analysis.

Chapter 7 presents the Ph.D. project conclusions including the main success points, challenges and future work.

Chapter 8 provides an overview of other research topics that have been addressed throughout this Ph.D. project which are not directly related but still relevant to this work.

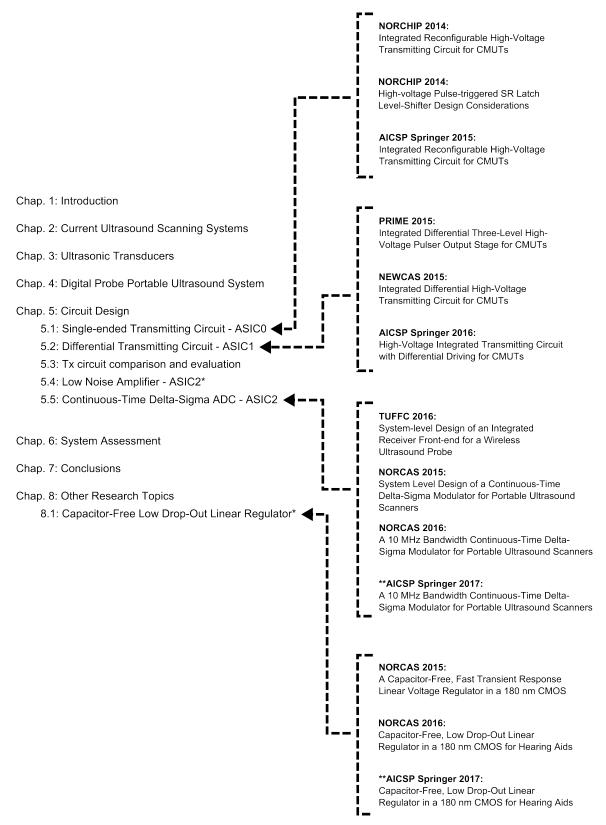

A visual overview of this thesis and its related publications is shown in Fig. 1.1.

4 Introduction

Figure 1.1: Overview of the thesis chapters and related published work.

\*The author of this work is not the main designer.

<sup>\*\*</sup>Suggested for submission.

## Current Ultrasound Scanning Systems

In this chapter, an overview of the current state of ultrasound scanning is given. Traditional static ultrasound scanners are presented and their strengths and weaknesses are discussed. The emerging portable ultrasound scanners are introduced as a flexible alternative, while exposing their main implementation challenges.

#### 2.1 Traditional Static Ultrasound Scanners

Medical ultrasound imaging diagnostic techniques have been used since 1950s in hospitals and they have become a standard procedure with wide variety of applications. It is a low-cost, non-invasive, easily usable technique that does not require any type of radiation or radioactive contrast substance to be injected in the patient [2]. A trained professional is able to visually diagnose various conditions through the ultrasound scanned image due to its high spacial and temporal resolution. Nonetheless, the utility of an ultrasound scanner is directly linked to its picture quality, since the higher resolution, the more precise and accurate diagnosis can be performed. For this reason, the main objective of ultrasound scanner design is to obtain the highest possible picture quality.

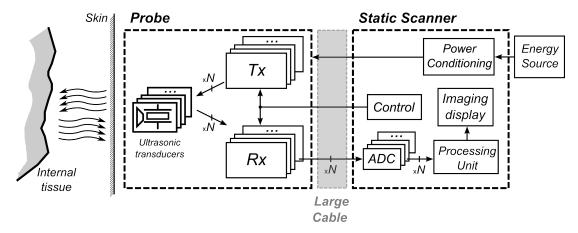

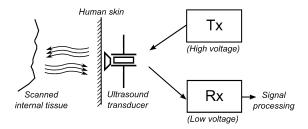

The structure of a traditional static ultrasound scanner, including its probe, is shown in Fig. 2.1. The probe consists of N channels each of them composed of an ultrasonic transducer, a transmitting circuit (Tx) and a receiving circuit (Rx). The high-voltage Tx excites the transducer in order to generate the ultrasound waves, which will be reflected off of the scanned internal tissue and travel back to the transducer inducing a signal that is amplified by the Rx. In order to transfer the N analog amplified signals from the probe to the scanner, a large, heavy and expensive cable containing N shielded coaxial cables is needed. The signals are digitized in the scanner using N ADCs leading to a data transfer rate (DTR) in the order of 150 Gb/s. Once the data has reached the processing unit, the real time imaging from the data acquired is generated and the imaging is finally visualized in a display. The transmitting and receiving timings of each channel are dictated by a control unit and the energy needed for the static scanner and probe are supplied externally, since the scanner is plugged into the AC mains.

Figure 2.1: Traditional static ultrasound scanner structure.

The maximum achievable image quality has several limiting factors. Firstly, the transmitting and receiving capabilities of the ultrasonic transducer, which are discussed in Chapter 3. Secondly, the quality of the Tx, Rx and ADCs which dictate the signal-to-noise ratio (SNR) of the signals delivered to the processing unit. Finally, the algorithm implemented in the processing unit which generates imaging from the acquired data.

In traditional static ultrasound scanners, the second limitation is not relevant since these scanners are plugged into the AC mains that effectively supply as much power as required to the system. Moreover, the size of the scanner is not a restriction, therefore, there is no limitation on the size or power consumption of electronic circuitry of the scanner. The electronics can be as complex as desired and do not need to be area or power efficient, hence generic discrete components are typically used. Even though they are over-designed to accommodate for a wide range of applications and thereby, they occupy more area and consume more power than needed, the cost of all the components is low compared to the total cost of the scanner.

Despite having a very high-performance and cover a wide range of ultrasound imaging applications, static scanners have several disadvantages. Firstly, a large, heavy and expensive cable containing N shielded coaxial cables is needed to transfer the analog data to the processing unit. As a result, the processing unit is local and physical part of the scanner. Secondly, these scanners are large and require AC mains supply, therefore, their transportability is limited. Thirdly, the price of static ultrasound scanners is high, hence the amount of devices per hospital is also restraint. Overall, static ultrasound scanners provide the best possible imaging results, however, they are expensive and have low scanning flexibility.

### 2.2 Portable Ultrasound Scanners

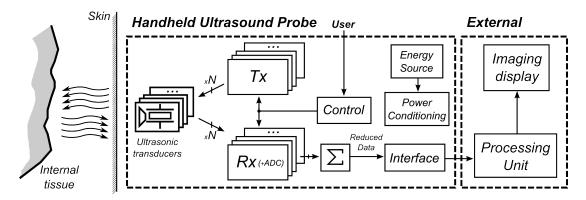

In order to overcome the flexibility challenges of traditional static ultrasound scanners, the concept of portable scanners has started to emerge. The idea is to develop a small hand-held device able to perform on-spot scanning, increasing the flexibility of ultrasound scanning procedures. The structure of an N channel portable ultrasound scanner is shown in Fig. 2.2. The main difference between the structure of a static and a portable ultrasound scanner relies on the data reception. In static scanners, a large

Figure 2.2: Portable ultrasound scanner structure.

amount of analog signals need to be transferred from the probe to the scanner. As a result, the signal transfer has to be done using a large, heavy and expensive cable containing N shielded coaxial cables, which typically ranges from 32 to 192. For this reason, the data processing unit is a local and physical part of the scanner.

Contrarily, portable ultrasound scanners digitize and reduce the data in the handheld probe. There is a lot of research done regarding ultrasound data reduction algorithms, however, this goes beyond the scope of this project. Only synthetic aperture sequential beamforming (SASB), which is the main imaging techique researched in the Futuresonic project is considered [3–6]. From this point on, beamforming is used instead of SASB techniques for simplicity. The probe contains ADCs in the Rx and has transmitting and receiving pre-beamforming capabilities to achieve the data reduction. The pre-beamforming is performed by exciting each transducer individually in a sequence filling all the imaging plane and summing the received signals from each transmit burst [3]. Each Rx needs to individually amplify and delay the signal to correctly pre-beamform the data, hence, a separate delay and amplification block per channel is needed. All channels are digitized and summed, reducing the data to be transferred to the data processing unit. The control of the Tx and Rx pre-beamformings is done with the control block.

Pre-beamforming the data reduces the DTR requirements down to 240 Mb/s, enhancing the use of standard data transfer methods such as universal serial bus (USB) or Wi-Fi interface. As a result, an AC mains supply independent low-power hand-held ultrasound probe can be used for the scanning without the need of a local processing unit. However, the hand-held probe becomes power limited by the required local energy source, i.e. battery. The processing unit can be specialized and located externally in a space with easy AC mains supply access, hence, similarly to static scanners, very high-performance data processing can be achieved due to no power consumption limitations. Additionally, the current state of the art transducers are already suitable for portable ultrasound requirements, hence, no specific transducers need to be investigated and developed for them. For these reasons, the main picture quality limiting factor is not the transducer quality or the imaging algorithms that generate the picture anymore. The power budget limited electronics of the hand-held probe dictate the maximum picture quality of portable ultrasound scanners. From this point on, the data processing and imaging will be considered external and effectively non picture quality limiting.

There are several challenges in the design and implementation of those electronics. Firstly, as it was aforementioned, the hand-held probe is no longer AC-mains powered,

therefore its maximum allowable power consumption is determined by the battery or energy source. Furthermore, the size of the probe is constrained since it needs to be hand-held operated. That sets a limitation on the area available for the electronics and the maximum power dissipation in the probe. Another challenge is the required high-voltage capabilities in order to drive the ultrasound transducers. As a result, the probe has to contain high-voltage transmitting circuitry and low-voltage accurate receiving circuitry while being small and efficient.

All these challenges need to be overcome to deliver data from the hand-held probe with the highest feasible SNR to obtain the best picture quality possible. In order to achieve this, the area and power budget need to be fully utilized, hence, over-designed generic discrete components are not suitable for this application. Custom designed Application Specific Integrated Circuit (ASIC) solutions are required for obtaining the best SNR achievable for a specific area and power budget.

This project is aimed at assessing the feasibility of the custom designed integrated electronics inside the hand-held probe of a portable ultrasound scanner. The portable ultrasound system targeted, including the hand-held probe, is described in Chapter 4.

## Ultrasonic Transducers

In this chapter, an overview of ultrasonic transducers is given.

The commonly used piezoelectric transducers are briefly explained and the emerging capacitive micromachined ultrasonic transducers are presented as an alternative. Their main advantages and disadvantages are discussed and the transducers used in this project are described.

### 3.1 Introduction

The most essential and characteristic part of ultrasound scanners are the ultrasonic transducers. These devices are responsible for the generation of the ultrasonic waves and the reception of the reflected waves, hence they can be operated bidirectionally. Electrical energy can be fed into the devices generating ultrasonic pressure (transmission), or ultrasonic pressure can be applied to the transducer generating an electrical signal (reception).

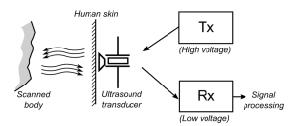

The two operating modes of an ultrasonic transducer, transmission and reception, are shown in Fig. 3.1. During the transmission, the Tx excites the transducer with high-voltage pulses generating ultrasonic waves, Fig. 3.1 a). The shape of the transmitting pulses is part of the transducers research field and it is out of the scope of this work. Square pulses are used here as part of the research done in the Futuresonic project. These waves travel through the skin and get reflected off of the internal tissue back to the transducer. During reception, the reflected waves are received by the transducer inducing a signal that is amplified by the Rx, Fig. 3.1 b).

The geometry and structure of the transducer determine the characteristics of the optimal driving pulses and induced signal, and thereby, the specifications for the Tx and Rx. For this reason, in order to custom design the electronics efficiently, the specific transducer to drive has to be determined. The circuitry can always be re-designed for a new transducer, but a generic design will never be optimal for different transducers.

In the next section, an overview of the two main types of ultrasonic transducers is given. Firstly, the commonly used piezoelectric transducers and the capaticive micromachined ultrasonic transducers (CMUTs), which are used in this project, are discussed. Secondly, the operation principles of CMUTs are explained and the main advantages are evaluated. Finally, the specific CMUTs used in this project are described in order to derive the specifications for the Tx and Rx.

Figure 3.1: Ultrasonic transducer operation: a) Transmission. b) Reception.

## 3.2 Ultrasonic Transducer Types

Piezoelectric transducers are the most used transducers in ultrasound applications. Most commercial ultrasound scanners are piezoelectric based [7] since they are well known, well characterized and have a suitable performance for most ultrasound scanning demands. These transducers consist of two thin conductive layers with a piezoelectric material based on crystals or ceramics in between. By applying a voltage difference between the plates, the piezoelectric material deforms. Therefore, by applying a variating voltage, ultrasonic waves can be created. For receiving, the ultrasonic waves create a vibration in the piezoelectric material which generates a voltage signal between the two conductive layers that can be amplified for imaging.

Even though piezoelectric transducers are the mainly used transducers, extensive research in the last two decades has proved that capacitive micromachined ultrasonic transducers (CMUTs) are a very suitable alternative [8] and have advantages both in terms of performance and fabrication process [9]. Due to the low mechanical impedance, CMUTs have less ringing that results in a shorter temporal pulse. Therefore, they achieve better temporal and axial resolution, which leads to a wider operating bandwidth (BW). Furthermore, they also have better thermic and transduction efficiency [10]. CMUTs are fabricated using standard silicon micromachining techniques, hence, they benefit from all the typical advantages such as low cost and high design flexibility [8]. Additionally, piezoelectric elements are diced using a mechanical saw that limits the distance between elements to 30-50 µm. CMUT elements are defined using photolitography, which allow much smaller distance between elements, 1-5 µm. For this reason, the number of elements per area unit is higher for CMUTs and the fabrication of complex transducer element arrays is simpler. As a result, it is much easier to flip-chip an IC to a CMUT array obtaining very compact structures with minimal interconnection parasitics, which highly benefits portable ultrasound scanner systems [11]. Additionally, due to process similarities, there is a high integration compatibility with CMOS integrated circuits. There has been several research done integrating CMUT and CMOS technologies by either wafer co-processing or wafer post-processing using monolithic CMUT-on-CMOS integration [12–18].

**Figure 3.2:** CMUT operation principle. Electrostatic force, mechanical force and stable/unstable equilibrium points.

CMUTs are micro-electro-mechanical systems (MEMS)-based devices that were invented in the mid-1990s and have improved immensely throughout the last two decades [8]. CMUT elements are mainly capacitive units that consist of a thin movable plate that forms the top electrode, which is suspended on top of a vacuum gap, and a fixed substrate, which forms the bottom electrode. In Fig. 3.2, a simplified approximation of the operation principle of CMUTs is shown. Whenever a voltage difference  $V_{bias}$  is applied between the two electrodes, the movable plate deflects due to the electrostatic force. The equilibrium is reached when this electrostatic force is equal to the opposing force generated by the mechanical stiffness of the plate. There are two equilibrium points, a stable and an unstable one. The CMUT operates around the stable point without surpassing the unstable point, since otherwise the plates would snap together. Increasing  $V_{bias}$  enhances the electromechanical coupling of the transducer but reduces the distance between the stable and unstable point, which makes the CMUT plates snap easier. Consequently, there is an optimal bias voltage  $V_{bias}$  for each CMUT, where the electromechanical coupling is the highest while avoiding the snapping of the plates.

For transmitting, high-voltage pulses are applied on top of  $V_{bias}$  creating a plate vibration that generates ultrasonic waves, Fig. 3.3 a). For the purpose of achieving symmetrical transmitting waves, the high-voltage pulses are symmetrical with respect to  $V_{bias}$  obtaining a vibration around the stable deflection position. The transmitting sound pressure of the CMUT will be maximum at a pulsing frequency matching the resonant or center frequency of the CMUT  $(f_c)$ . The optimal  $V_{bias}$  and  $f_c$  are both determined by the structure and geometry of the transducer. For receiving,  $V_{bias}$  is constantly applied between the two electrodes 3.3 b). The reflected ultrasonic waves create a vibration on the movable plate that varies the transducer capacitance. This capacitance variation combined with a fixed voltage across the plates induces a current  $(I_{Rx})$  proportional to that variation according to (3.1).

$$I_{Rx} = dQ/dt = d(C \cdot V_{bias})/dt = dC/dt \cdot V_{bias}$$

(3.1)

Figure 3.3: CMUT connection: a) Transmitting. b) Receiving.

## 3.3 Transducer selection

In this project, the integrated electronics are designed for CMUTs because of their potential advantages and also because these transducers are part of the research done in the Futuresonic project. DTU Nanotech is in charge of the design and fabrication of the CMUTs used in this project. The Tx and Rx need to be designed for a specific CMUT, therefore their specifications and requirements are determined by the characteristics of that transducer. Two different CMUTs have been used in this project, CMUT<sub>A</sub> and CMUT<sub>B</sub>. The specifications of each of them can be seen in Table 3.1. CMUT<sub>B</sub> is an newer version of CMUT<sub>A</sub> with a better fabrication process that achieves higher yield. Both transducers have the same  $f_c$ , receiving BW and driving slew rate (SR) requirements, however, they have different equivalent capacitance,  $C_{eq}$ , optimal  $V_{bias}$  and transmitting pulse amplitude  $V_{pulse}$ . CMUT<sub>A</sub> is used in the single-ended Tx presented in Section 5.1 and CMUT<sub>B</sub> is used in the differential Tx shown in Section 5.2. Since both CMUTs have the same  $f_c$  and BW, for receiving purposes they are effectively equivalent, hence they can both be used for the Rx channels.

**Table 3.1:** CMUTs used in this project

|                     | $C_{eq} \; [\mathrm{pF}]$ | $f_c  [\mathrm{MHz}]$ | BW [MHz] | $\mathbf{SR}$ [2 V/ns] | $V_{bias} [ m V]$ | $oldsymbol{V_{pulse}} [	ext{V}]$ |

|---------------------|---------------------------|-----------------------|----------|------------------------|-------------------|----------------------------------|

| $CMUT_A$            | 15                        | 5                     | 10       | 2                      | 75                | +/-25                            |

| $\mathrm{CMUT_{B}}$ | 30                        | 5                     | 10       | 2                      | 80                | +/-20                            |

# Digital Probe Portable Ultrasound System

This chapter describes the digital probe portable ultrasound system that will contain the integrated electronics designed in this project. The system level tradeoffs are discussed and the system block structure is presented. The specifications for each block are defined and the state of the art of integrated circuitry for ultrasound scanners is reviewed.

## 4.1 System Characteristics

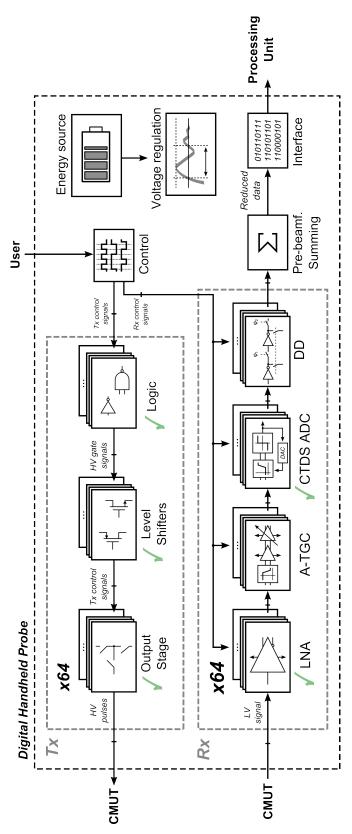

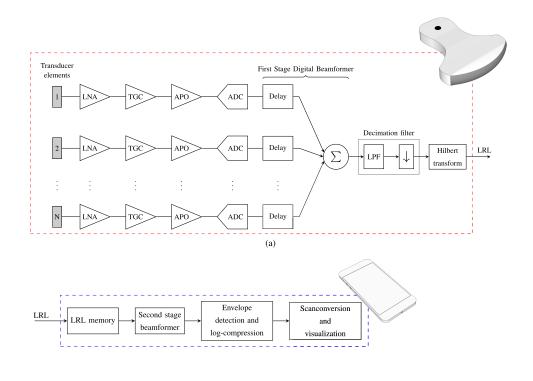

The target of this project is to assess the feasibility of the electronics for portable ultrasound scanners. Previous to the integrated electronic design, the system has to be defined. In this project, the digital probe portable ultrasound system shown in Fig. 4.1 is targeted. Similarly to the structure of portable systems discussed in Chapter 3, it contains in-probe pre-beamforming to reduce the data transfer to the processing unit.

The digital handheld probe contains 64 CMUTs, 64 transmitting channels, 64 receiving channels, a pre-beamforming summing block, an interface, a control block, a voltage regulation block and an energy source. The internal energy source, i.e. battery, feeds the voltage regulation block that supplies all the other circuitry. The Tx channels excite the CMUTs with a specific delay profile, and the 64 Rx channels are used for receiving. The combined data from the Rx channels is pre-beamformed by separately delaying and amplifying each channel and adding the signals with the summing block. The timings and configuration for the pre-beamforming transmission and reception are controlled by the control block. The pre-beamformed reduced data is sent to an interface such as a universal serial bus (USB), Wi-Fi or similar protocols, enabling the data transfer to an external system. The complex digital signal processing can now be performed in an external data processing unit (i.e. servers, cloud-based computing...) which have no processing or power consumption limitations. The real time imaging generated by the external processing unit is sent to a local imaging display so that the probe user can visually perform the diagnostic.

This project is focused on the integrated electronics in the handheld probe, therefore its general characteristics have to be defined. The power budget of handheld probe is limited to 3 W due to thermal dissipation capabilities. Moreover, the dimensions of

Figure 4.1: Digital probe portable ultrasound system structure.

the probe can not exceed the typical values of a portable device. The length of the probe is set to  $100\,\mathrm{mm}$  so that it can be easily handheld. The width and height of the probe are determined by the size of the CMUT array, which in this case is  $41\,\mathrm{mm}$  x  $7.8\,\mathrm{mm}$ . Accounting for the battery, plastic encapsulation and extra margin, the total dimensions of the handheld probe of the system are set to  $100\,\mathrm{mm}$  x  $55\,\mathrm{mm}$  x  $15\,\mathrm{mm}$ . The probe contains a CMUT array connected directly to two printed circuit boards (PCBs), which are sized  $90\,\mathrm{mm}$  x  $50\,\mathrm{mm} = 4500\,\mathrm{mm}^2$ . By allocating  $500\,\mathrm{mm}^2$  in each PCB for the contacts to the CMUT array, the effective area for the electronics in both PCBs is a total of  $8000\,\mathrm{mm}^2$ .

#### 4.2 Block Structure

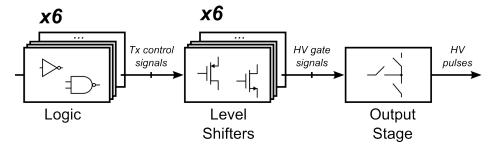

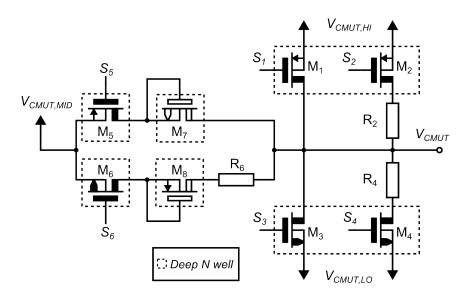

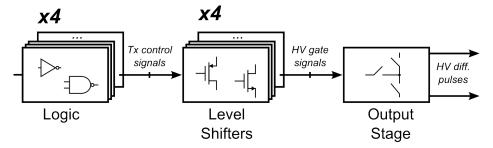

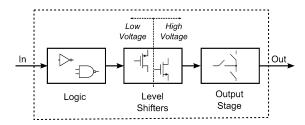

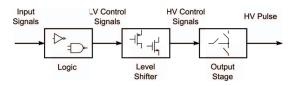

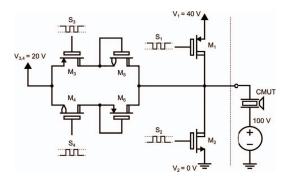

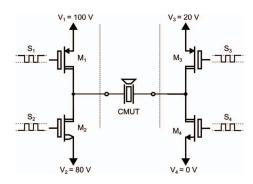

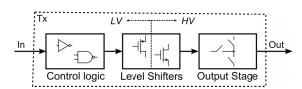

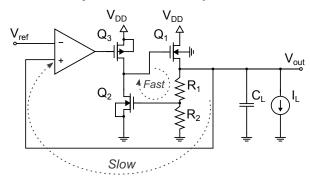

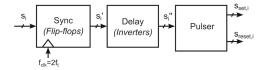

Once the system has been established, the block structure of the Tx and Rx need to be defined. The Tx is responsible for the generation of the high-voltage pulses that drives the CMUT and the bias voltage needed for receiving. The structure used for the Tx is shown in Fig. 4.2. First, a low-voltage logic circuit conditions the signals received from the control block. The logic block functionality includes buffering, internal signal synchronization and gate-based logic operations. The level-shifters are responsible for translating the low-voltage control signals to the high-voltage gate signals needed to drive the output stage. The output stage, which consists in several high-voltage MOS switches driven by the level-shifted signals, connects the output terminal to different voltage levels. The Tx is implemented in a high-voltage 0.35 µm process that can tolerate up to 120 V.

The structure of the Rx is not as straight-forward as the Tx. Each Rx channel needs an individual gain and accurate delay profile in order to correctly pre-beamform, hence these two operations have to be performed before the summing block. The main tradeoff of the Rx channel structure is the placement of the analog-to-digital converter (ADC).

The first option is to place the ADC after the delay line, therefore an analog implementation of the delay is required. The ADC would be implemented as a Nyquist rate converter, hence an interpolation filter is needed afterwards in order to achieve the high delay accuracy needed for the pre-beamforming. These type of filters are complex, process dependent and highly area and power demanding, which is not ideal in this system.

4.2 Block Structure 15

**Figure 4.2:** Structure of the transmitting circuitry (Tx). Low-voltage logic block, level shifters and output stage.

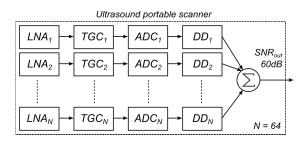

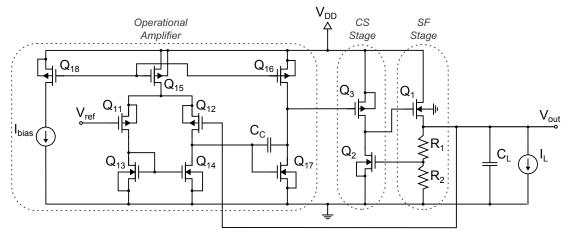

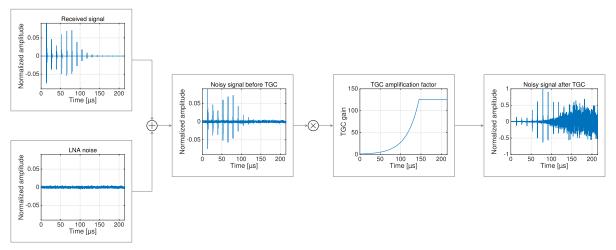

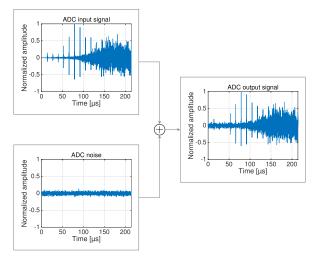

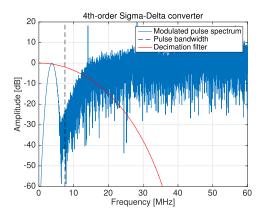

The second option is the proposed one, Fig. 4.3, where the ADC is placed before the delay, leading to a digital delay. Firstly, the single-ended signal induced in the CMUT is sent to a low noise amplifier (LNA), which applies the first gain and converts the signal to differential. This LNA requires a high-voltage switch or protection, since it is directly connected to the transducer. Secondly, the adaptive time-gain control (A-TGC) filters and adjusts the gain of the signal depending on the receiving time. This is needed since the magnitude of the received signal decreases over time due to the deeper ultrasound reflections, therefore the gain of the received signal needs to be increased progressively. Thirdly, the signal is digitized into a 1-bit stream by a continuous-time delta-sigma analog-to-digital converter (CTDS ADC). The channel delay is applied using a digital delay block (DD) and finally, all the channels are summed obtaining the reduced data. In this case, the ADC is implemented as an oversampled data converter obtaining a 1-bit digital stream with the necessary time accuracy inherently embedded. For this purpose, the output frequency of the ADC has to fit the minimum delay needed in the delay line. Furthermore, a 1-bit output simplifies the digital delay structure the most. Using this option, the clocked digital delay can be easily implemented with an inverter based clocked digital delay line with switches. The inverters and switches can be built out of minimum size devices and operate at the lowest supply possible achieving a small, efficient and precise delay implementation. This second implementation option was chosen from the Futuresonic project since it seemed more promising and also because of its research value. The Rx circuitry is implemented in a 65 nm process (instead of the 0.35 µm process previously used) in order to take advantage of the lower node technology, making the clocked digital delay more efficient and even less power consuming.

Figure 4.3: Structure of the receiving circuitry (Rx). Low noise amplifier (LNA), adaptive time gain control (A-TGC), continuous-time delta-sigma analog-to-digital converter (CTDS ADC), clocked digital delay (DD) and summing block.

The most critical blocks in order to achieve a low area and low power implementation are the Tx, LNA and ADC. Due to the need of high-voltage devices, the Tx is one of the most area limiting parts of the system, therefore, a small efficient design is necessary. Moreover, its current consumption can also be an issue, because of the high-voltage pulses at a frequency in the order of MHz. The LNA, since it is the first gain stage of the Rx, has to apply the first gain of the signal path while introducing the least amount of noise possible. Consequently, a significant part of the power budget has to be spent on the LNA to achieve the high requirements. Finally, similarly to the LNA, the ADC has to convert the analog signal to digital with the highest possible SNR to obtain the best picture quality. The area and power consumption feasibility study of the integrated electronics of the digital portable ultrasound system depends mainly on the Tx, LNA and ADC, hence, these are the main focus of this project.

## 4.3 Specifications

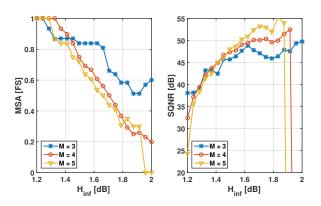

In this section, the specifications of the system are described. As it was stated before, the top-level limitations of the handheld probe are a maximum total power consumption of 3 W and an effective PCB area of  $8000\,\mathrm{mm}^2$ . Furthermore, the work [19], part of the Futuresonic project, showed that a minimum SNR after summing of 60 dB is needed to produce acceptable ultrasound imaging with the processing unit. For the purpose of allocating the optimal SNR specifications in every part of the Rx channel, the system is studied.

The SNR of a single channel (SNR<sub>ch</sub>) can be calculated as shown in (4.1), where  $v_{rms}$  is voltage root mean square value (rms) of the received signal and  $\sigma_n$  is the standard deviation of the noise. The total SNR obtained by summing  $N=2^M$  signals with the same  $v_{rms}$  and  $\sigma_n$  is shown in (4.2). The total summed SNR<sub>M</sub> improves by  $M \cdot 3 \, \text{dB}$  compared to the original SNR<sub>ch</sub>. Consequently, for a system with 64 channels (M=6) and an expected SNR<sub>M</sub> of 60 dB after summing, the SNR<sub>ch</sub> requirements at the end of each channel is 42 dB.

$$SNR_{ch} = 10 \cdot \log_{10} \left( \frac{P_{signal,ch}}{P_{noise,ch}} \right) = 10 \cdot \log_{10} \left( \frac{v_{rms}^2}{\sigma_n^2} \right)$$

(4.1)

$$SNR_{M} = 10 \cdot \log_{10} \left( \frac{P_{signal,M}}{P_{noise,M}} \right) = 10 \cdot \log_{10} \left( \frac{(2^{M} \cdot v_{rms})^{2}}{2^{M} \cdot (\sigma_{n})^{2}} \right)$$

$$= 10 \cdot \log_{10} \left( \frac{v_{rms}^{2}}{\sigma_{n}^{2}} \right) + 10 \cdot \log_{10} \left( 2^{M} \right) dB \approx SNR_{ch} + M \cdot 3 dB$$

$$(4.2)$$

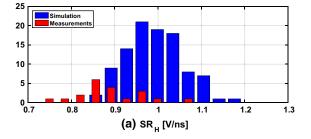

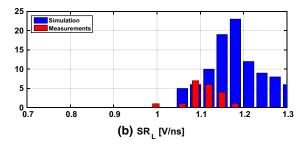

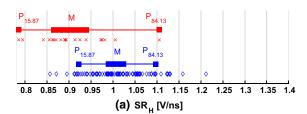

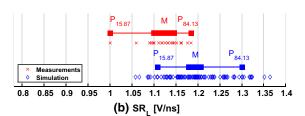

Assuming that each Rx channel is thermal noise dominated and with a fixed signal power, the SNR<sub>ch</sub> is determined by its noise power. The voltage squared input related thermal noise  $v_{in,n}^2$  of a single transistor across a frequency bandwidth of  $f_{BW}$  is shown in (4.3), where  $k = 1.38 \cdot 10^{-23}$  JK<sup>-1</sup> is the Boltzmann constant, T is the temperature in Kelvins, q is the electron charge, and  $g_m$  is the transconductance of the transistor. Note that flicker noise is omitted in (4.3) due to the high frequency operation of the system. The  $g_m$  of a transistor in saturation can be expressed as