**DTU Library**

### **Capacitive Micromachined Ultrasonic Transducers for Gas Sensing**

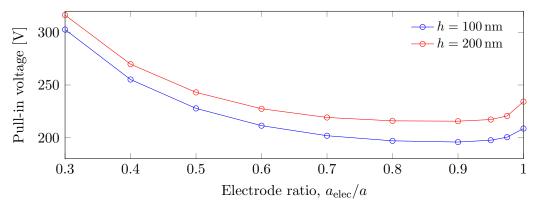

Mølgaard, Mathias J.G.

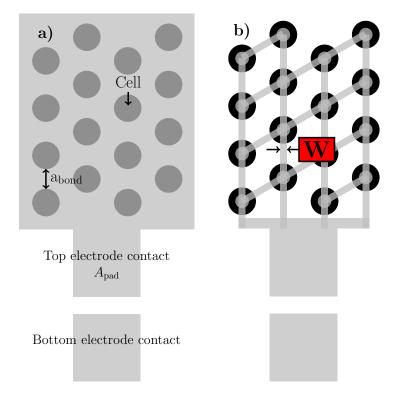

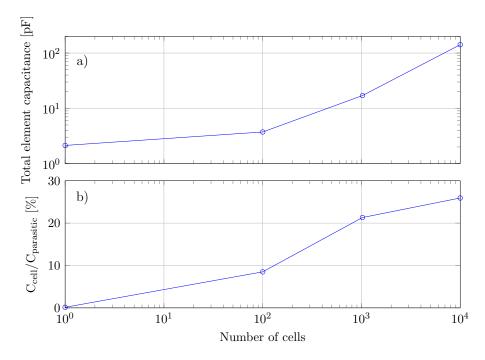

Publication date: 2018

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

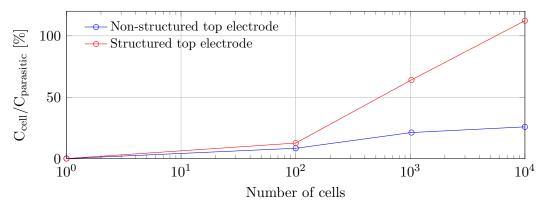

Citation (APA):

Mølgaard, M. J. G. (2018). Capacitive Micromachined Ultrasonic Transducers for Gas Sensing. DTU Nanotech.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Capacitive Micromachined Ultrasonic Transducers for Gas Sensing

Mathias J. G. Mølgaard PhD Thesis June 2018

# TECHNICAL UNIVERSITY OF DENMARK

## Ph.D. Thesis

# Capacitive Micromachined Ultrasonic Transducers for Gas Sensing

Author: Mathias J. G. Mølgaard Supervisors:

Prof. Erik V. Thomsen

Assoc. Prof. Mogens H. Jakobsen

$21^{\rm st}$  June 2018

Kgs. Lyngby, Denmark

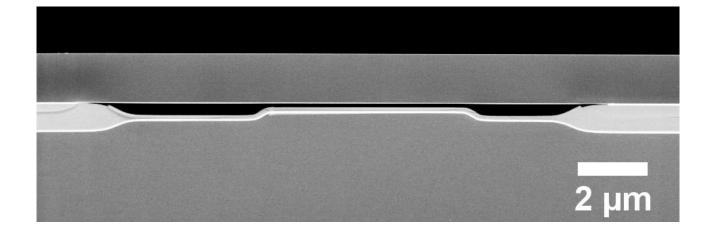

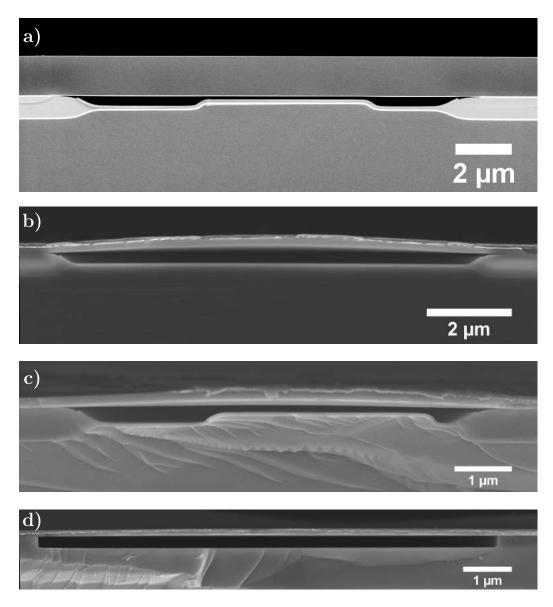

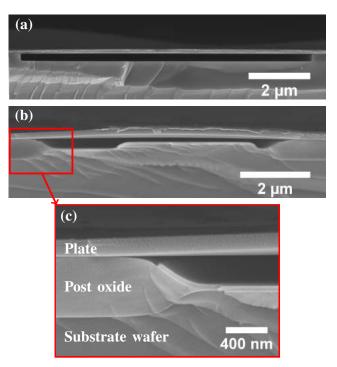

Cover image: Scanning electron microscope image of the cross-section of a G1 CMUT cell before the plate has been thinned down.

### Technical University of Denmark Department of Micro- and Nanotechnology

Ørsteds Plads 345C 2800 Kgs. Lyngby DENMARK

Tel: (+45) 4525 5700 Fax: (+45) 4588 7762

Web: www.nanotech.dtu.dk E-mail: info@nanotech.dtu.dk

Author e-mail: migmol@nanotech.dtu.dk

### Preface

This PhD thesis has been submitted to the Technical University of Denmark, in partial fulfillment of the requirements for the degree of Doctor of Philosophy. The work has been supervised by Professor Erik Vilain Thomsen and Associate professor Mogens Havsteen Jakobsen. This thesis consists of a recapitulation of the research work carried out from May 2015 to June 2018 at DTU Nanotech, Technical University of Denmark.

Capacitive Micromachined Ultrasonic Transducers (CMUTs) are currently one of the topics being researched in the group of Erik V. Thomsen but with a focus on the use of CMUTs as transducers for medical ultrasound imaging. Therefore, both practical knowledge of CMUT fabrication and characterization as well as a theoretical understanding of the CMUTs had already been established when my project began. This experience was the foundation and starting point of my project.

Mathias J. G. Mølgaard Kgs. Lyngby, June 2018

Math Malgood

### Summary

Gas sensors are used in many fields for a wide range of applications from monitoring the indoor air quality control to detecting tiny amounts of illegal drugs. Different sensing methods exist, but in this thesis the focus is on gravimetric detection, that is measuring a perturbation (typically a resonance frequency shift) due to the addition of a mass on the sensor. Gravimetric sensors have a number of advantages over the other sensor types: small device footprint, low power consumption, and low cost. Capacitive micromachined ultrasonic transducer (CMUT) gas sensors are a subcategory of gravimetric gas sensors that offer a high sensitivity, low limit of detection per area, simple fabrication process, and an electrostatic actuation and detection scheme. Consequently, CMUTs are good candidates for being used as gas sensors. The aim of this thesis is to develop, fabricate, and apply state of the art CMUT gas sensors.

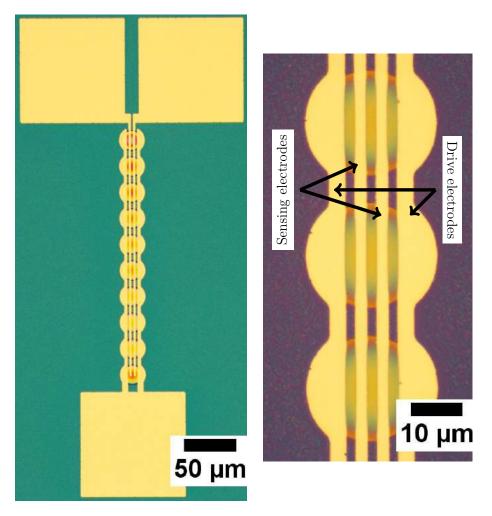

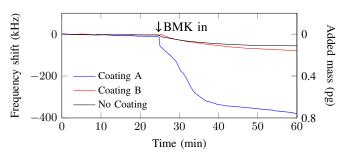

The theoretical background of CMUTs is given by presenting both a static and a dynamic model of the CMUT. Furthermore, design rules are developed for optimizing the mass sensitivity and limit of detection. Four generations of CMUT chips are designed, fabricated and characterized. The design space was investigated which resulted in an optimal choice of materials and geometry for CMUTs with small radii (radii  $< 5 \,\mu m$ ). The best CMUTs showed a record high distributed mass sensitivity of 0.83 Hz/ag and a record low limit of detection of 1.16 ag, which in part is due to an optimized design and fabrication process. The CMUTs were used for detection of a precursor molecule for the synthesis of (meth)amphetamine called Benzyl Methyl Ketone (BMK). This was done in conjunction with a colorimetric chip which showed a high selectivity towards BMK. Finally, an alternative method of reading out the resonance frequency from the CMUT was presented. The top electrode of the CMUT is split in three: one for actuating the CMUT and two for detecting the capacitance change caused by the plate deflection.

vi SUMMARY

Hence, the actuating and detection electrode and signals are decoupled and common mode noise can be suppressed by making a differential measurement of the signals from the two sensing electrodes.

#### Resumé

Gassensorer er udbredte indenfor mange felter, hvor de bliver brugt til forskellige formål, fra at overvåge den indendørs luftkvalitet til at detektere små mængder ulovlige stoffer. Der eksisterer forskellige måder til at måle gas, men i denne afhandling har fokus været på den gravimetriske målemetode, hvor man detekterer en perturbation af sin sensor (typisk et resonansfrekvens skift) efter masse er blevet tilføjet sensoren. Gravimetriske sensorer har en række fordele i forhold til andre gassensor-typer: lille sensor størrelse, lavt energiforbrug og lav enhedspris. Kapacitive Mikrofremstillede Ultraslydstransducere (CMUTs) er en underkategori af gravimetriske sensorer og tilbyder en høj følsomhed, god opløsning pr. areal, en simpel fremstillingsproces og en elektrostatisk aktuerings-mekanisme. Af disse grunde er CMUTs gode kandidater til at blive brugt som gas sensorer. Målet for denne afhandling er at udvikle, fabrikere og anvende state of the art CMUTs til brug som gas sensorer.

Den teoretiske baggrund for CMUTs er givet ved en præsentation af både en statisk og en dynamisk CMUT model. Ydermere er der udviklet designregler for at optimere masse-følsomheden og opløsningen. Fire generationer af CMUT chips er blevet udviklet, fabrikeret og karakteriseret. Grænserne for designet er undersøgt, og der blev fundet et optimalt valg af materialer og geometri for CMUTs med små dimensioner (radier  $< 5\,\mu\text{m}$ ). Disse CMUTs udviste en rekord høj distribueret masse-følsomhed: 0.83 Hz/ag og en rekord lav detektionsgrænseværdi: 1.16 ag, grundet et optimeret design og fabrikationsmetode. Sensorerne blev anvendt til at detektere et molekyle som bliver brugt til at syntetisere (met)amfetamin kaldet Benzyl Methyl Ketone (BMK). Dette blev målt sammen med en kolorimetrisk chip, som udviste en god selektivitet overfor BMK. Til sidst blev en ny metode til at udlæse resonansfrekvensen præsenteret. Topelektroden splittes i tre: en bliver brugt til at aktuere, og de to andre bliver brugt til at udlæse en kapacitans-ændring,

som er proportional med pladeudbøjningen. Herved afkobles aktuerings- og udlæsnings-signalet, og eventuel støj kan blive undertrykt ved at foretage en differentiel måling.

### Acknowledgements

First of all I would like to thank my main supervisor Professor Erik V. Thomsen for his great support and enthusiasm throughout the project on both a professional and personal level. Furthermore, I would like to thank Associate Professor Mogens Havsteen Jakobsen and his group for providing me with the know-how and infrastructure for the functionalization of my devices. Especially, thank you to Milan Laustsen who have helped me both fabricate colorimetric chips and functionalize my CMUTs.

Moreover, thanks to my colleagues for our valuable academic discussions, as well as our not so academic discussions. I have enjoyed the informal work environment you have helped create. A special thanks goes out to Jan Bagge for his tireless effort of teaching us about electrical engineering. Furthermore, thanks to Ole Hansen for always being willing to help with everything from fabrication problems to theoretical calculations. I would like to thank the master and bachelor students I have supervised, for their hard work in the cleanroom fabricating CMUTs. On the same note, a thanks goes out to the staff at DTU Danchip for sharing their practical fabrication knowledge, as well as keeping the cleanroom running. Finally, thanks to my aunt for proofreading the manuscript.

# Contents

| <b>P</b> :                | refac | e        |                                  | iii          |

|---------------------------|-------|----------|----------------------------------|--------------|

| $\mathbf{S}_{\mathbf{I}}$ | umm   | ary      |                                  | $\mathbf{v}$ |

| $\mathbf{R}$              | esum  | ıé       |                                  | vii          |

| A                         | ckno  | wledge   | ments                            | ix           |

| 1                         | Inti  | oduction | on                               | 1            |

|                           | 1.1   | Gas se   | ensor specifications             | <br>2        |

|                           | 1.2   | Gas se   | ensor types                      | <br>2        |

|                           | 1.3   | Resona   | ant gravimetric sensing          | <br>3        |

|                           |       | 1.3.1    | Mass sensitivity                 | <br>6        |

|                           |       | 1.3.2    | Limit of detection               | <br>7        |

|                           |       | 1.3.3    | Selectivity                      | <br>8        |

|                           |       | 1.3.4    | Choice of sensor type            | <br>9        |

|                           | 1.4   | The Cl   | MUT                              | <br>10       |

|                           |       | 1.4.1    | Working principle                | <br>11       |

|                           |       | 1.4.2    | Brief historical account         | <br>12       |

|                           |       | 1.4.3    | State of the art of CMUT sensing | <br>13       |

|                           | 1.5   | Thesis   | aim                              | <br>18       |

|                           | 1.6   | Acader   | mic contributions                | <br>18       |

|                           | 1.7   | Thesis   | outline                          | <br>18       |

| 2                         | The   | eory     |                                  | 21           |

|                           | 2.1   | Linear   | harmonic oscillator              | 21           |

xii CONTENTS

|   | 2.2 | Static CMUT model                                   |

|---|-----|-----------------------------------------------------|

|   |     | 2.2.1 Plate deflection profile                      |

|   |     | 2.2.2 Eigenfrequency                                |

|   |     | 2.2.3 Capacitance                                   |

|   | 2.3 | Dynamic CMUT model                                  |

|   |     | 2.3.1 Electrostatic analysis                        |

|   |     | 2.3.2 Dynamic equivalent circuit model              |

|   |     | 2.3.3 Impedance analysis                            |

|   | 2.4 | Mass sensitivity                                    |

|   |     | 2.4.1 Mass sensitivity - stressed plates            |

|   | 2.5 | Limit of detection                                  |

|   |     | 2.5.1 Quality factor                                |

|   | 2.6 | Gravimetric gas detection                           |

|   | 2.7 | Sensitivity versus limit of detection               |

|   | 2.8 | Chapter conclusion                                  |

| 3 | Des | ign 69                                              |

| • | 3.1 | CMUT generations                                    |

|   | 3.1 | 3.1.1 Cavity structure discussion                   |

|   |     | 3.1.2 Fabrication process flow                      |

|   |     | 3.1.3 Plate material                                |

|   | 3.2 | Design of LOCOS cavities                            |

|   | J   | 3.2.1 Introduction and motivation                   |

|   |     | 3.2.2 Process simulation model validation           |

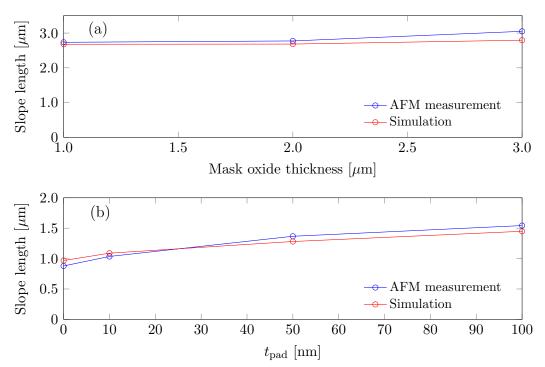

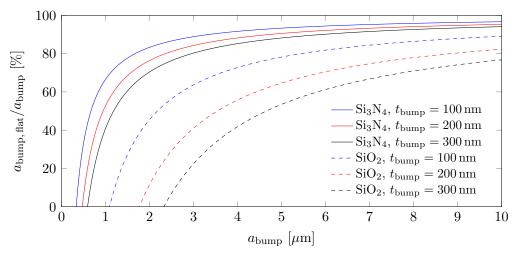

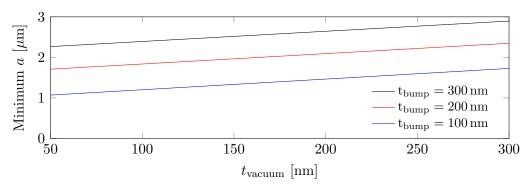

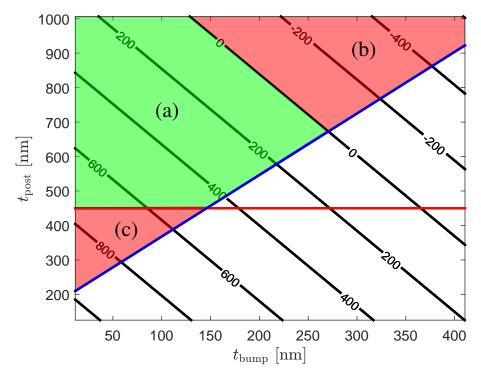

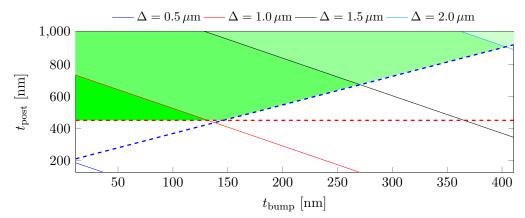

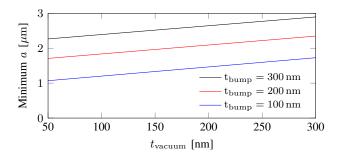

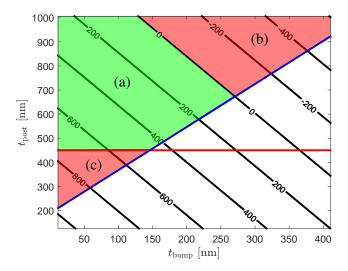

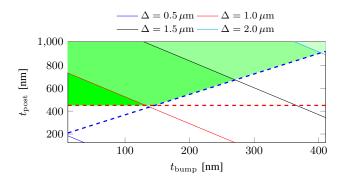

|   |     | 3.2.3 LOCOS cavity optimization and design space 82 |

|   |     | 3.2.4 Partial conclusion                            |

|   |     | 3.2.5 Vertical LOCOS cavity design                  |

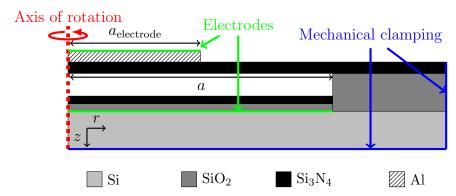

|   | 3.3 | Finite element modeling                             |

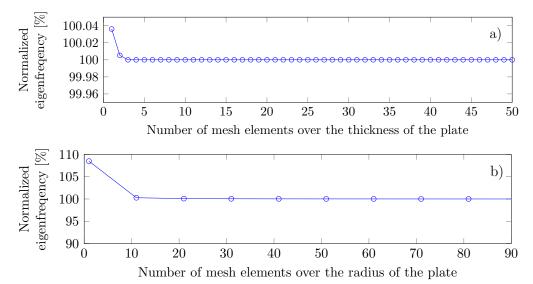

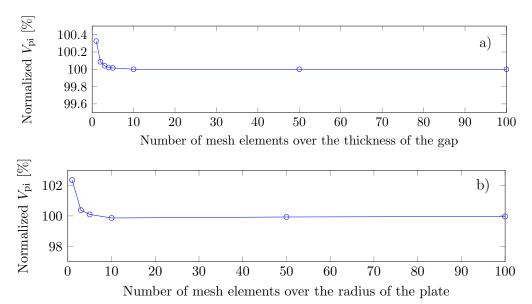

|   |     | 3.3.1 Mesh convergence study                        |

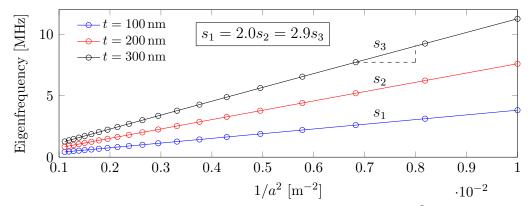

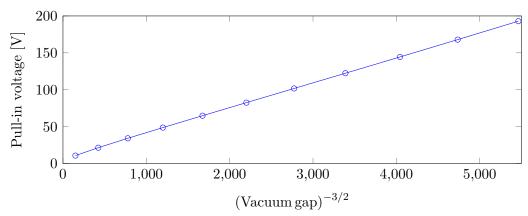

|   |     | 3.3.2 Model validation                              |

|   | 3.4 | Cell designs                                        |

|   |     | 3.4.1 Capacitance                                   |

|   |     | 3.4.2 Top electrode design                          |

|   |     | 3.4.3 Dielectric breakdown                          |

|   | 3.5 | Chapter conclusion                                  |

| 4 | Dev | ice fabrication 107                                 |

| • | 4.1 | General fabrication aspects                         |

|   | 4.1 | 4.1.1 Wafers                                        |

|   |     | 4.1.2 Lithography                                   |

|   |     | 4.1.3 Film thickness measurement                    |

|   |     |                                                     |

| CONTENTS | xiii |

|----------|------|

|          |      |

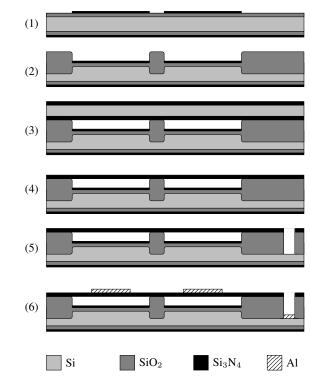

|   | 4.2 | Process flow - G1                           |

|---|-----|---------------------------------------------|

|   | 4.3 | Process flow - G2                           |

|   | 4.4 | Process flow - G3                           |

|   | 4.5 | Process flow - G4                           |

|   | 4.6 | Process optimization                        |

|   |     | 4.6.1 Wafer bonding                         |

|   |     | 4.6.2 Dry etching of $Si_3N_4$              |

|   |     | 4.6.3 Wire bonding                          |

|   | 4.7 | Chapter conclusion                          |

| 5 | Cha | racterization and results 125               |

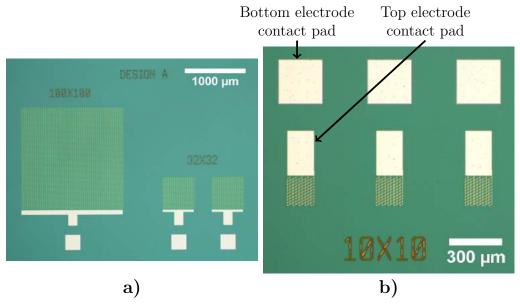

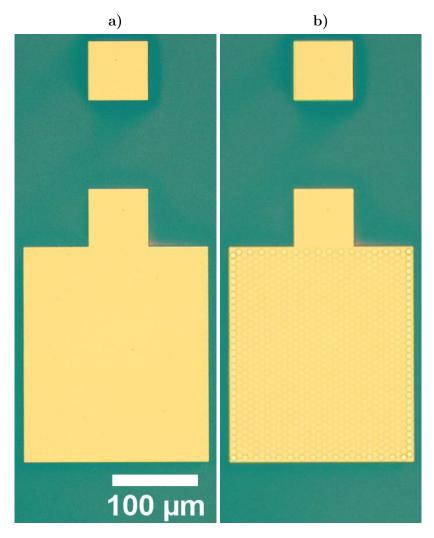

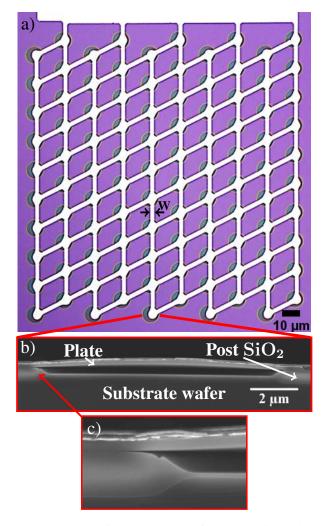

| 0 | 5.1 | Chip designs                                |

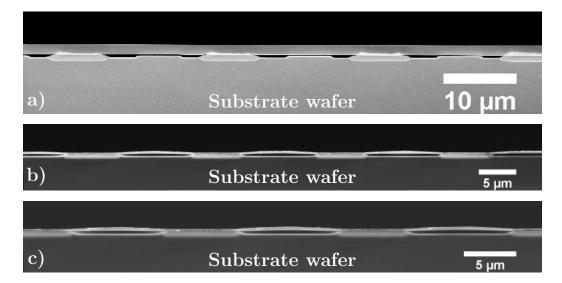

|   | 0.1 | 5.1.1 Optical microscopy                    |

|   |     | 5.1.2 Scanning electron microscopy          |

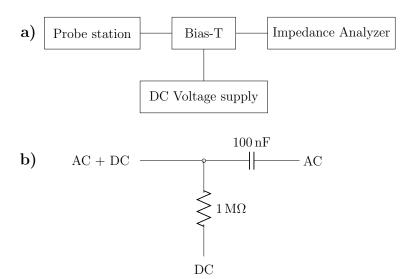

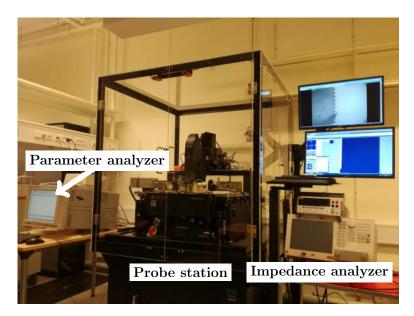

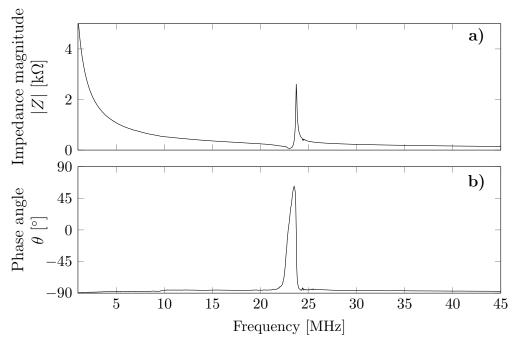

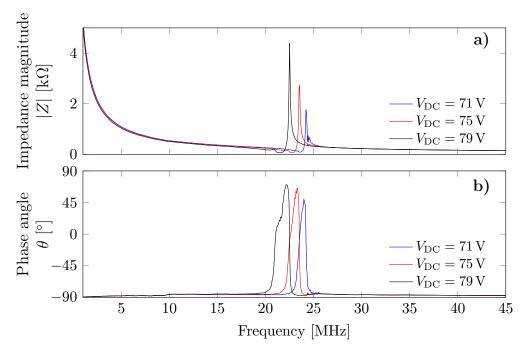

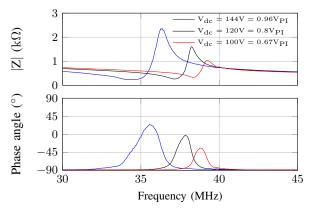

|   | 5.2 | Impedance analysis                          |

|   | 0.2 | 5.2.1 Measurement setup                     |

|   |     | 5.2.2 Impedance spectra                     |

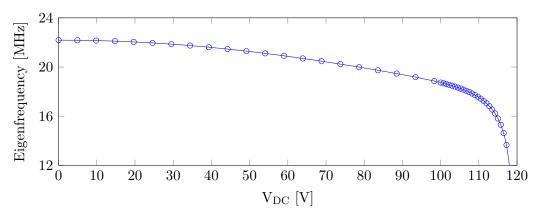

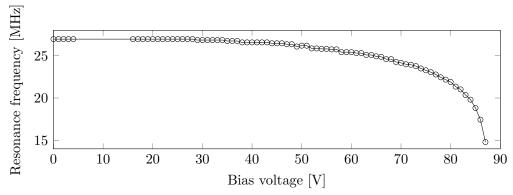

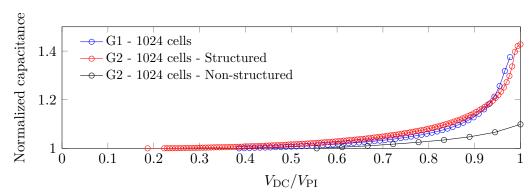

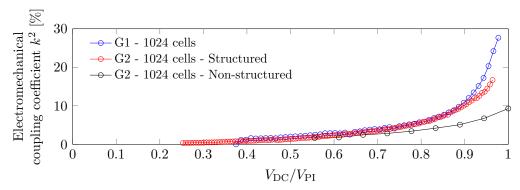

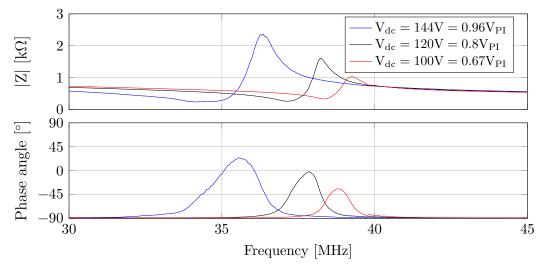

|   |     | 5.2.3 Effect of the bias voltage            |

|   |     | 5.2.4 Partial conclusion                    |

|   | 5.3 | Dielectric charging                         |

|   | 0.0 | 5.3.1 Experimental                          |

|   | 5.4 | Mass limit of detection                     |

|   | 0.4 | 5.4.1 Experimental setup                    |

|   |     | 5.4.2 Allan Deviation                       |

|   |     | 5.4.3 Mass limit of detection               |

|   | 5.5 | Mass sensitivity                            |

|   | 5.5 | 5.5.1 Sensitivity non-linearity             |

|   |     | 5.5.2 Sensitivity and operating conditions  |

|   |     | 5.5.3 Experimentally determined sensitivity |

|   |     | 5.5.4 Sensitivity comparison                |

|   | 5.6 | Chapter conclusion                          |

|   | 5.0 | Chapter Conclusion                          |

| 6 |     | sensing experiments - BMK 163               |

|   | 6.1 | Selectivity                                 |

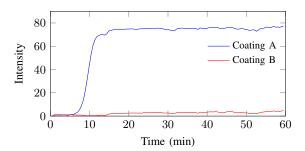

|   | 6.2 | Colorimetry                                 |

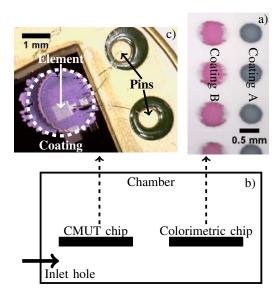

|   | 6.3 | Experimental setup and method               |

|   |     | 6.3.1 CMUT chips                            |

|   |     | 6.3.2 Colorimetric chips                    |

|   |     | 6.3.3 Experimental setup                    |

|   | 6.4 | Results and discussion                      |

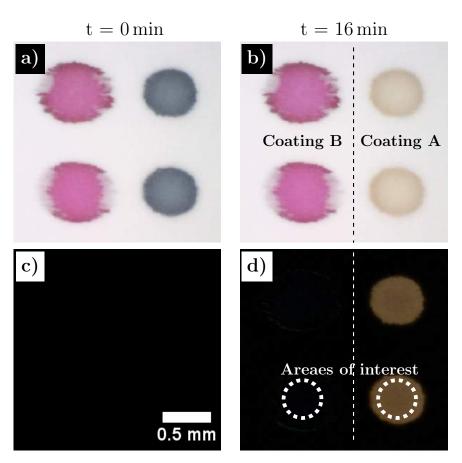

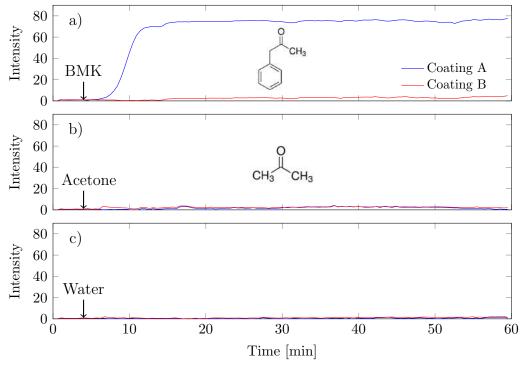

|   |     | 6.4.1 Colorimetry                           |

|   |     |                                             |

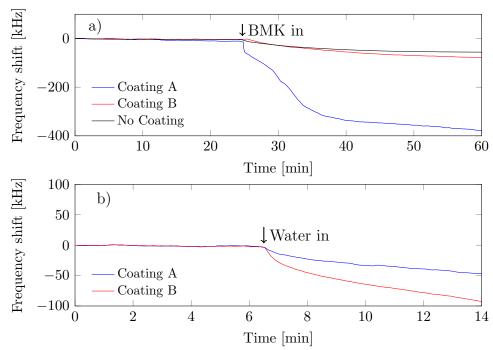

|              | 6.5               | 6.4.2<br>6.4.3<br>Chapte                    | CMUT                                                                              |                      | . 173                                                             |

|--------------|-------------------|---------------------------------------------|-----------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------|

| 7            | 7.1<br>7.2<br>7.3 | Workin<br>7.1.1<br>7.1.2<br>7.1.3<br>Experi | re read-out method  In principle                                                  | <br><br>             | <ul><li>. 179</li><li>. 181</li><li>. 181</li><li>. 182</li></ul> |

| 8            | Con               | clusion                                     | and Outlook                                                                       |                      | 187                                                               |

| Bi           | bliog             | raphy                                       |                                                                                   |                      | 203                                                               |

| Aı           | ppen              | dices                                       |                                                                                   |                      | 205                                                               |

| A            |                   | er - Se<br>UT sei                           | nsitivity optimization of wafer bonded gravim                                     | $\operatorname{etr}$ | ic<br>207                                                         |

| В            | _                 |                                             | ombined Colorimetric and Gravimetric CMUT<br>tection of Benzyl Methyl Ketone      | $\mathbf{Se}$        | n-<br>217                                                         |

| $\mathbf{C}$ |                   |                                             | e paper - Combined Colorimetric and Gravim<br>nsor for Detection of Phenylacetone | $\operatorname{etr}$ | ic<br>225                                                         |

| D            | Pro               | cess flo                                    | ow - G1                                                                           |                      | 231                                                               |

| $\mathbf{E}$ | Pro               | cess flo                                    | ow - G2                                                                           |                      | 239                                                               |

| $\mathbf{F}$ | Pro               | cess flo                                    | ow - G3                                                                           |                      | 245                                                               |

| $\mathbf{G}$ | Pro               | cess flo                                    | ow - G4                                                                           |                      | 253                                                               |

## CHAPTER 1

### Introduction

Gas sensing is the act of detecting and possibly determining the concentration of a specific gas using a sensor. These sensors have an active element which is perturbed by the gas and an output signal is generated. The final output signal is typically electrical and can be logged by a computer.

The value of the global market for gas sensors is estimated to reach  $\sim 2.5$  billion USD by the year 2020 [1,2]. Table 1.1 shows a list of well established fields in which gas sensors are used and examples of corresponding gases of interest. Commercial gas sensors are available for these use cases but one could imagine new markets such as: gas sensors embedded in consumer electronics such as smartphones [3], tablets or wearable devices and as replacements for the current mass spectrometers in high vacuum systems [4,5]. Clearly, these vastly different application areas result in different requirements for the gas sensors in each specific case. For example, a gas sensor replacing a mass spectrometer in a vacuum system will require an extremely low limit of detection while the unit cost may not be important, whereas the opposite would be true for a sensor in a consumer product such as a smartphone.

In the following chapter different sensor types are compared. This comparison forms the basis for the choice of technology of the gas sensor to be made.

| Field                   | Gas examples                                                          |

|-------------------------|-----------------------------------------------------------------------|

| Indoor air quality      | CO <sub>2</sub> , CO and humidity                                     |

| Safety in industry      | Volatile Organic Compounds (VOCs), NH <sub>3</sub> and O <sub>2</sub> |

| Automotive              | Emissions: CO <sub>2</sub> and NO <sub>X</sub>                        |

| Defence                 | Explosives, nerve gas and biological weapons                          |

| Law enforcement         | Alcohol and potentially drugs                                         |

| Environmental studies   | Greenhouse gases                                                      |

| Food quality and safety | Complex mixture                                                       |

**Table 1.1:** Examples of fields in which gas sensors are utilized [6–10].

## 1.1 Gas sensor specifications

As previously mentioned: the application area of the sensor determines the sensor specifications. The most important specifications are defined in Table 1.2. For real non-ideal sensors there will be a trade-off between some of the specifications. Therefore, a good sensor will be one where as many of the specifications can be optimal at the same time.

Apart from the specifications listed in Table 1.2 it may be desirable to have a gas sensor capable of detecting multiple gases at the same time. The inherent ability to do this varies among the different sensor types. Furthermore, remote distributed sensors may become important in the future for creating sensor networks. This requires remote connectivity, low power consumption, and a small footprint of the sensor.

In this thesis the focus will mainly be on the first three specifications from Table 1.2, namely: sensitivity, limit of detection, and selectivity.

### 1.2 Gas sensor types

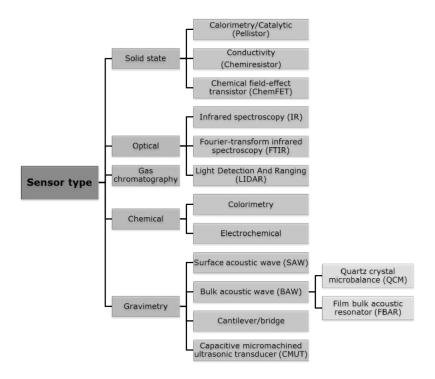

A wide range of gas sensor types exists, some being commercially available, whereas others still are at the research stage. The common aspect shared by all gas sensors is that a perturbation of the sensing element occurs due to the surrounding gas. The actuation and detection scheme may be coupled or decoupled influencing the complexity of the sensor. Figure 1.1 gives an overview of detection techniques and examples of specific sensor types. In the following the focus is on gravimetric sensors as the devices treated in this thesis fall within this category. Table 1.2 showed a list of specifications which now will be discussed in the context of gravimetric sensors. Although some gravimetric gas sensors have reached the commercial market [11, 14], gravimetric sensors are primarily found in research projects in

| Specification name | e Definition                               | Ideal sensor |

|--------------------|--------------------------------------------|--------------|

| Sensitivity        | Slope of the output vs. input curve        | High         |

| Limit of detection | Minimum detectable input                   | Low          |

| Selectivity        | Ability to distinguish between gases       | High         |

| Size               | Physical dimensions                        | Small        |

| Power consumption  | Energy consumed per time unit              | Low          |

| Price              | Unit cost                                  | Low          |

| Response time      | Time before a stable output is reached     | Short        |

| Range              | The interval of measurable input values    | Wide         |

| Linear range       | The range in which the output is linear    | Wide         |

| Reversibility      | Is the initial state reached again?        | Yes          |

| Stability          | Does the characteristics change over time? | No           |

**Table 1.2:** Qualitative definitions of gas sensor specifications. Based on [11–13].

academia at the research and development stage. Gravimetric gas sensors have a number of inherent favorable traits: a small device size, low power consumption, low cost (batch cleanroom fabrication), possibly Complementary Metal—Oxide—Semiconductor (CMOS) compatible fabrication process which means that the sensor and the driving electronics can be integrated into a small and low power unit [3]. Furthermore, excellent volume sensitivities have been demonstrated, e.g. for dimethyl methylphosphonate (DMMP) of 34.5 pptv/Hz with a limit of detection of 50 pptv [3]. This combination of traits is unique among the sensor types listed in Figure 1.1 which makes gravimetric sensors an interesting choice as gas sensors.

A drawback of the gravimetric method is that, without modification of the surface, the sensors cannot distinguish between gasses, i.e. they have no selectivity. Therefore, gravimetric gas sensors commonly have a functionalization layer applied to the sensing element which selectively binds, adsorbs or absorbs the specific analyte gas molecules. However, these layers increase the mass of the sensor itself, hereby decreasing the sensitivity and affects the reversibility and response time of the sensor.

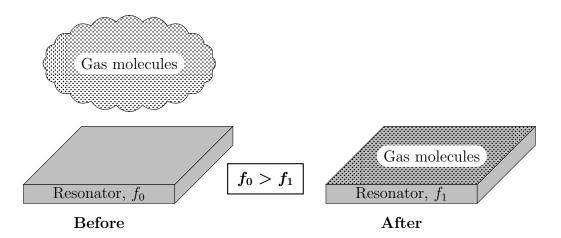

# 1.3 Resonant gravimetric sensing

A resonant gravimetric sensor is a mechanical resonator with a resonance frequency,  $f_0$ , that is determined by the geometry and materials of the device. When the resonator is loaded with a mass, the resonance frequency will decrease. For a resonant gravimetric gas sensor it is the gas molecules which adds the mass to the resonator, as shown in Figure 1.2. To the left in

**Figure 1.1:** Tree diagram of different gas sensor types. The sensor types are grouped according to their detection technique. Based on [6–8, 11, 15].

the figure the gas is not in contact with the resonator but when the gas is introduced, in the figure to the right, some of the molecules will load the resonating element, thus decreasing the resonance frequency to  $f_1$ , such that  $f_0 > f_1$ . This shift in resonance frequency can be recorded and correlated with the concentration of the gas and consequently the sensor can give a quantitative value for the gas concentration.

The gravimetric sensors in Table 1.1 are all either MicroElectroMechanical Systems (MEMS) or NanoElectroMechanical Systems (NEMS) devices. Generally, as the dimensions of a device shrink the surface-area-to-volume ratio increases as it is proportional to the inverse of the characteristic device dimension. As will be evident later this relationship favors miniaturization of the devices in order to increase e.g. the sensitivity.

Various actuation and read-out principles have been used in gravimetric devices. However, common for almost all sensors is that the readout signal in the end is converted to an electric signal. A lot of exotic transduction techniques have been published (see [16] p.115) which not will be mentioned here. The most widely used actuation and detection schemes used in gravimetric sensors are [16] p.115-143:

**Figure 1.2:** Sketch illustrating the principle behind gravimetric gas sensing. Left: resonator before exposure to a gas and right: resonator after exposure to a gas with the gas adsorbed on the surface. The resonance frequency of the resonator is seen to decrease after exposure to the gas.

Actuation: Electrostatic, Electrodynamic, Piezoelectric and Thermoelastic.

Detection: Electrostatic, Electrodynamic, Piezoelectric, Piezoresistive and Optic.

The electrostatic technique relies on having quasistatic charges on two electrodes typically separated by a small gap, where one of the electrodes is free to move. When a potential is applied between the two electrodes the charges experience an attractive electrostatic force. The electrostatic technique is widespread among MEMS transducers due to a low power consumption and since only simple external circuitry is needed for the actuation and detection. However, for NEMS devices the electrode areas are typically very small resulting in small signals which are difficult to measure.

The electrodynamic technique relies on the Lorentz force and thus requires *moving* charges in a magnetic field for the charges and hereby device to experience a force. The magnetic field may come from permanent magnets or electromagnets and the moving charges are typically supplied by running a current through a conductor in the device. Due to this current the power consumption is typically higher than for the electrostatic technique.

The piezoelectric technique relies on the fact that for piezoelectric materials the strain and electric field are coupled. Consequently, these materials can be used for both actuation and detection. The quality of the piezoelectric material determines the coupling between the mechanical and electrical domain and one of the challenges can be ensuring a high material quality.

In the gravimetric sensor literature much attention is given to three of the

specifications from Table 1.2, namely: sensitivity, limit of detection (LOD) and selectivity. In the following the gravimetric sensor types will be compared based on these three specifications.

#### 1.3.1 Mass sensitivity

In Table 1.2 the distributed mass sensitivity was defined as: the slope of the output vs. input curve of the sensor. The sensitivity can be calculated for resonators modeled as single degree of freedom (1D) linear harmonic oscillators [11]:

$$S = \frac{\partial f}{\partial m} = \frac{\partial}{\partial m} \sqrt{\frac{k_{\text{eff}}}{m_{\text{eff}}}} = -\frac{1}{2} \frac{f_0}{m_{\text{eff}}},$$

(1.1)

where  $k_{\rm eff}$  is the effective spring constant,  $f_0$  is the resonance frequency and  $m_{\rm eff}$  is the effective mass of the resonator. Equation 1.1 is valid under the assumption that the mass added to the resonator is much smaller than the mass of the resonator:  $\partial m \ll m_{\rm eff}$ . The equation shows that in order to increase the sensitivity a high resonance frequency and a low resonator mass is wanted. Which shows why MEMS and NEMS devices are often used.

To be able to better compare the sensitivities of the different sensor types a normalized sensitivity is used [17]:

$$S_{\text{norm}} = \lim_{\partial m \to 0} \frac{1}{f_0} \frac{\partial f}{\partial m/A} = \frac{\partial f}{\partial m} \frac{A}{f_0} = S \frac{A}{f_0}, \tag{1.2}$$

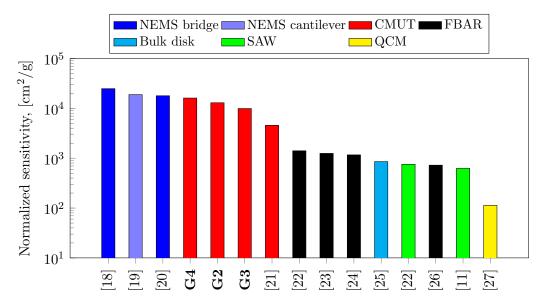

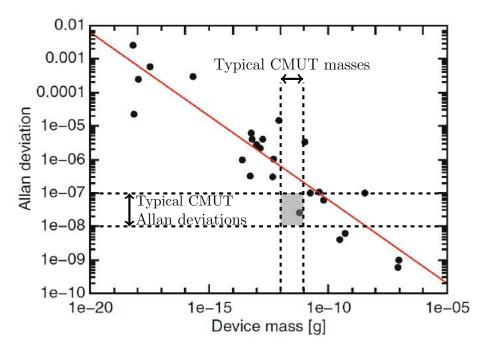

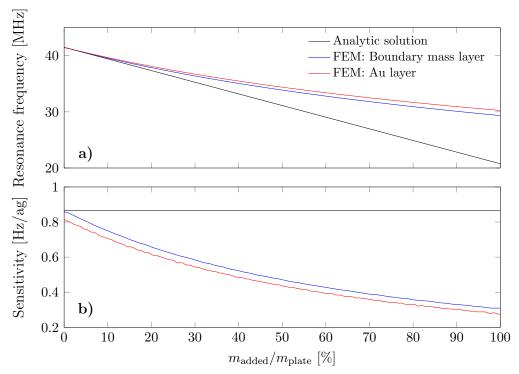

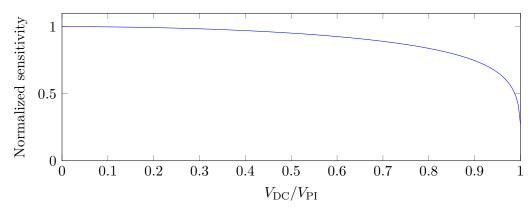

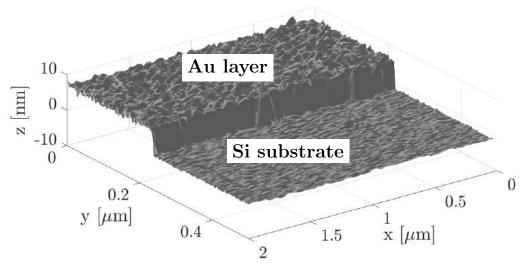

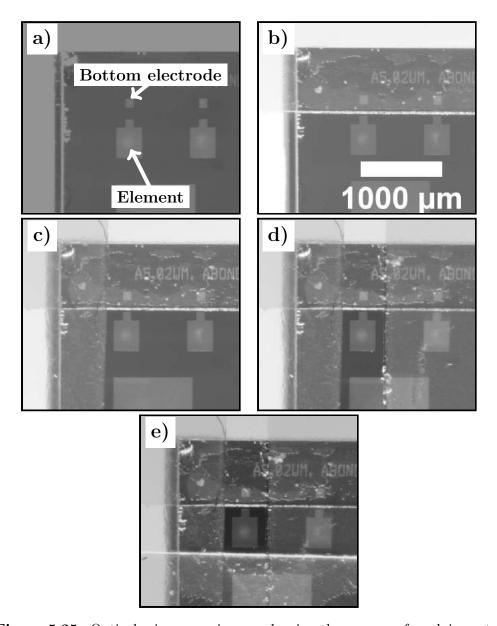

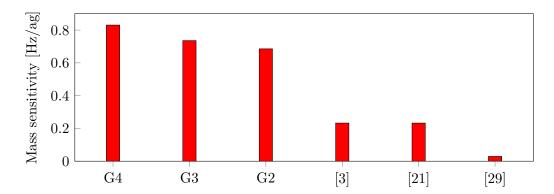

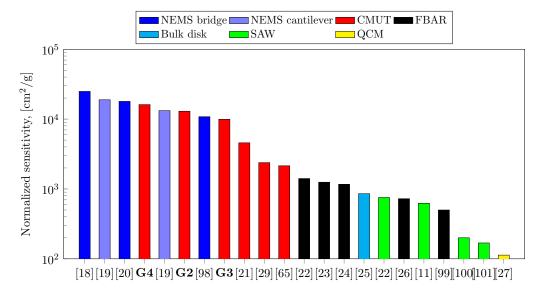

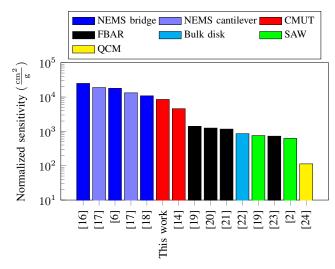

where A is the area of the resonator. The sensitivity is here normalized with the area and resonance frequency of the resonator. Since the operating principles differ between the gravimetric sensor types, the normalized sensitivity will have different dependencies on the geometrical parameters. Hence, the normalized sensitivities are expected to also differ between the sensor types. Figure 1.3 shows the highest normalized sensitivities I have found in the literature for each sensor type. A general trend is observed where the NEMS bridges and cantilever have the highest normalized sensitivities due to their small dimensions. The second highest values are found for the CMUTs where G2-G4 are the CMUT generations designed and fabricated during this project. Finally, the FBAR, SAW and QCM devices have the lowest normalized sensitivities. The reason for this is elaborated more upon later.

**Figure 1.3:** Normalized distributed mass sensitivities for different types of state of the art sensors. The CMUTs made in this project are labeled G2-G4 and for these the normalized sensitivity has been calculated using the measured (as opposed to the designed) geometrical values.

#### 1.3.2 Limit of detection

The mass limit of detection was in Table 1.2 defined as: the minimum detectable input. The mass LOD can be defined more precisely as the minimum mass change which gives a detectable frequency shift distinguishable from the frequency noise in the system. Mathematically this minimum LOD can be written as [11]:

$$LOD = 2m_{\text{eff}}\sigma_{\min}, \tag{1.3}$$

where  $\sigma_{\min}$  is the minimum Allan deviation, which is a measure for the frequency noise in a system. In order to achieve the lowest LOD a small resonator mass should be designed with a minimum of frequency noise which will reduce the Allan deviation, since a high frequency stability results in a low Allan deviation.

It can be shown that the *gas concentration* limit of detection is given by [11]:

$$\partial C \propto \frac{\text{LOD}}{A} = \frac{2m_{\text{eff}}\sigma}{A},$$

(1.4)

where A is the surface area of the resonator. Equation 1.4 shows that the ratio  $\frac{\text{LOD}}{A}$  should be minimized for the best sensor performance and that this is accomplished by decreasing the LOD and increasing the surface area of the

| <b>Table 1.3:</b> Resonance frequency, | , Allan deviation, surface area, an | d LOD/A for   |

|----------------------------------------|-------------------------------------|---------------|

| different sensor types. All devices    | are under atmospheric pressure.     | The values in |

| the table are taken from [11].         |                                     |               |

| Sensor type | $f_{ m r} \ [{ m MHz}]$ | Allan deviation, $\sigma_{\min}$ | $\begin{array}{c} \text{Active surface area, } A \\ [\text{mm}^2] \end{array}$ | $rac{\mathrm{LOD}/A}{[\mathrm{ng/cm^2}]}$ |

|-------------|-------------------------|----------------------------------|--------------------------------------------------------------------------------|--------------------------------------------|

| BAW         | 1100                    | $10^{-7}$                        | 0.25                                                                           | 1                                          |

| SAW         | 500                     | $10^{-8}$                        | 4                                                                              | 0.03                                       |

| CMUT        | 8                       | $10^{-8}$                        | 0.25                                                                           | 0.01                                       |

| CMUT        | 47.7                    | $3 \times 10^{-8}$               | 0.09                                                                           | 0.003                                      |

| MEMS        | 3                       | $10^{-7}$                        | $7.3 \times 10^{-6}$                                                           | 0.1                                        |

| NEMS        | 127                     | $10^{-6}$                        | $8 \times 10^{-8}$                                                             | 0.1                                        |

device. Table 1.3 shows an overview of typical values of the resonance frequency, Allan deviation, surface area and  $\frac{\text{LOD}}{A}$  for different gravimetric sensor types. The values in the table are obtained at atmospheric pressure, which is important to note since many NEMS devices are operated in a vacuum which influences the Allan deviation. The devices with the smallest dimensions display the highest Allan deviations and are thus the least frequency stable. This can be seen by comparing the NEMS and MEMS devices with the other sensor types.

The lowest  $\frac{\text{LOĎ}}{A}$  ratio is found for the CMUT due to a low LOD and relatively large surface area. The LOD is itself low due to a low Allan deviation and relatively low mass compared with the other sensors. The CMUT device has a combination of parameters which places it in the middle ground between the BAW and SAW on one side and MEMS and NEMS devices on the other, thus bringing together the best of both worlds. The CMUT maintains a surface area roughly as big as the BAW and SAW devices while having a much lower effective mass than these devices. This is due to the inherent parallelism of the CMUT structure which will be discussed more later. Equation 1.4 shows that the mass per area should be minimized by decreasing the amount of mass used per surface area. As will be shown later this is exactly what the CMUT structure allows for.

The lowest mass LOD is found for the NEMS devices due to the small size and hereby low mass, see Equation 1.3, but the surface area is for the same reason very small compared with the other devices. Also, the Allan deviation is approximately a factor 100 higher than for the CMUT. Therefore, the  $\frac{\text{LOD}}{A}$  does not ends up being the lowest.

### 1.3.3 Selectivity

Resonant gravimetric sensors measure a response to a change of mass and they do therefore not exhibit any selectivity between gasses. In order to make the sensors selective they are typically coated with a thin layer having an affinity towards the gas one is trying to detect. This thin layer is called the functionalization layer which enables the possibility of selective and label-free sensing.

The functionalization layer can be applied using different techniques. Sometimes the choice of technique is limited due to the geometry of the sensor. For example, it could be important not to coat the underside of a NEMS cantilever or bridge. It is generally easier to coat the sensors with a 'closed' surface such as BAWs, SAWs and CMUTs. Here several coating techniques can be used such as: spin coating, drop coating, dip coating, and spray coating.

### 1.3.4 Choice of sensor type

The choice of sensor technology was first narrowed down from the list of all potential gas sensing techniques shown in Figure 1.1, to only focus on gravmetric gas sensors. Within this subcategory the different types have been compared and a choice of technology can now be made.

**Sensitivity.** The normalized sensitivities for different resonant gravimetric sensors were compared in Section 1.3.1. The highest normalized sensitivities were found for the NEMS sensors followed by the CMUT sensors. The lowest normalized sensitivities were seen among the BAW and SAW sensors.

**Limit of detection.** It was shown in Section 1.3.2 that the important figure of merit (FOM) for the gas concentration LOD is the ratio  $\frac{\text{LOD}}{A}$ , which should be minimized. This ratio was lowest for the CMUT sensor, due to a favorable combination of Allan deviation, plate mass, and surface area compared with the other sensor types.

**Selectivity.** The point regarding selectivity came down to the ease of functionalization which is shared between the sensor types with a closed surface. Furthermore, these structures are also more robust towards the external environment.

Based on these criteria the NEMS and CMUT devices seem most promising but there are other points which should be considered:

**Fabrication**. The fabrication of CMUTs, even for high sensitivity sensors, can be done using standard cleanroom planar processing and UV lithography. The latter is not always possible for the fabrication of NEMS structures where lithography techniques with a higher resolution are needed, which in some cases (e.g. for electron beam lithography) are serial processes.

**Actuation and detection**. The actuation scheme in CMUTs is based on the electrostatic force while the detection is based on a capacitance change.

As stated earlier this allows for a low power consumption with an easy integration to the electronics, which can either be discrete or integrated [28]. Many different actuation and detection schemes have been used for NEMS sensors but many uses a variation of electrodynamic actuation or readout which requires an external magnetic field which in turn increases the complexity and size of the sensor.

The CMUT structure is inherently parallel where a single device is made up of many small resonators which in part explains the excellent noise performance but can also be used to tailor the electrical impedance seen by the external electronics. Furthermore, making several independent CMUT sensors on the same chip is straightforward which e.g. has been exploited for the detection of multiple gasses at the same time [29].

To conclude: for the reasons mentioned above the CMUT is seen as the best choice of technology for gas sensing. Therefore, the devices used in this thesis are CMUTs.

#### 1.4 The CMUT

A capacitive micromachined ultrasonic transducer is an electromechanical resonator. The CMUT device can transform energy from the electrical domain to the mechanical domain to the acoustical domain and vice versa. In this thesis the focus will mainly be on the transduction between the mechanical domain and electrical domain. In this section the basic working principle of the CMUT is described, while Chapter 2 provides a more detailed theoretical description of the CMUT.

The CMUT has been used as a transducer in several areas. Much attention has been given to the use of CMUTs as transducers for medical ultrasound imaging [30–33]. This is a field in which both academia and industry have devoted much time and many resources to further develop the CMUT to suit the transducers currently in use typically utilize piezoelectric crystals as the oscillating part and compared with these the CMUT potentially offers a larger bandwidth, improved pressure sensitivity, increased design flexibility, reduced cost and a CMOS compatible fabrication process.

Airborne applications such as flow metering and range sensors has also been proposed as an area in which CMUTs could be used [34, 35]. CMUTs have been applied as transducers for ultrasonic non-destructive testing (NDT) [36–39]. NDT is e.g. used for thickness measurements in pipes, weld inspection or for detecting fatigue induced cracks.

Finally, CMUTs have, as already mentioned, successfully been used for

1.4. THE CMUT 11

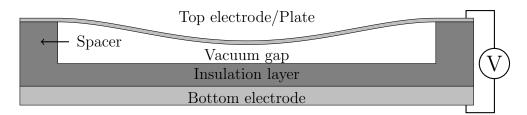

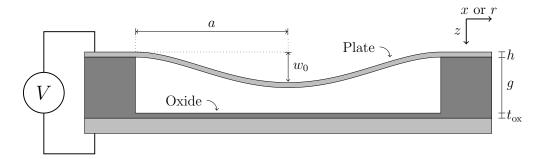

**Figure 1.4:** Cross-sectional sketch of a single CMUT cell. The plate is deflected into the vacuum gap due to an applied bias voltage between the top and bottom electrodes.

both immersion chemical/biological sensing and gas sensing [28, 40, 41]. A more thorough literature review of CMUT gas sensors is given in Section 1.4.3.

### 1.4.1 Working principle

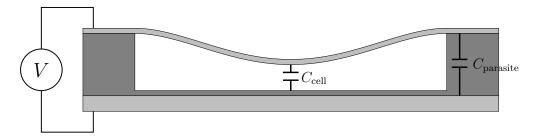

Figure 1.4 shows a sketch of a cross-sectional view of a single CMUT cell, whereas a CMUT element typically consists of many cells electrically connected in parallel. Figure 1.4 highlights the main parts of the CMUT cell. The plate is the oscillating part of the CMUT and deflects due to an applied force. For some designs the plate itself also acts as the top electrode, which requires the plate material to be an electrical conductor. The geometry of the plate, as seen from above, can be chosen arbitrarily but circles [42], squares [43] and hexagons [44] are most commonly used. The spacer material separates the top electrode from the underlying layers and creates the vacuum gap. The insulating layer prevents the plate/top electrode from touching the bottom electrode, hereby creating a short circuit in the capacitor.

The CMUT is actuated by applying an electrical potential between the top electrode and bottom electrode. The difference in potential gives rise to electrical charges of opposite sign on the two electrodes. This separation of charge results in an attractive electrostatic/Coulomb force between the electrodes and consequently, the top electrode/plate is deflected down into the gap. The position at which the plate stops is determined by a equilibrium between the electrostatic force and the mechanical force stemming from the rigidity of the plate. Superimposing an AC voltage on the already applied DC voltage will make the plate oscillate with the frequency of the AC voltage. If the frequency of the AC voltage matches the mechanical resonance frequency of the plate, the deflection amplitude is maximized. The capacitance of the CMUT is affected by these oscillations of the plate since the distance between the two electrodes is varying as a function of time. Consequently,

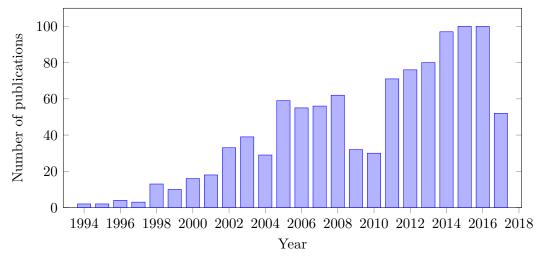

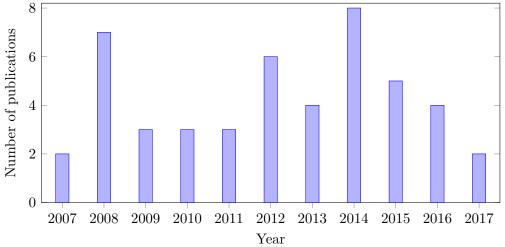

**Figure 1.5:** Number of publications as a function of publishing year for the entire CMUT field. The data for the chart is obtained from the database search site www.webofknowledge.com and includes publications in conference proceedings.

the capacitance change is at a maximum at resonance.

#### 1.4.2 Brief historical account

This section presents an overview of the CMUT literature and the most important milestones, relevant for gravimetric sensing, in the development of the CMUT. The first CMUT was reported in a publication from 1994 by Matthew I. Haller and Butrus T. Khuri-Yakub [45]. Butrus T. Khuri-Yakub heads a research group at Stanford University and is a pioneer within the CMUT field. Since this first publication, the CMUT field has grown which is reflected in the increasing number of articles published each year, see Figure 1.5. This figure shows that the number of CMUT related articles published as a function of time is increasing.

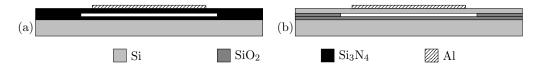

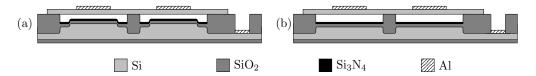

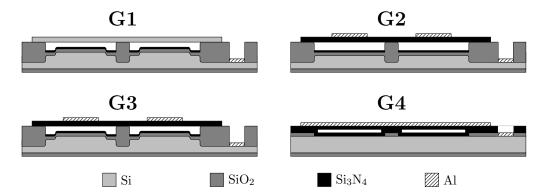

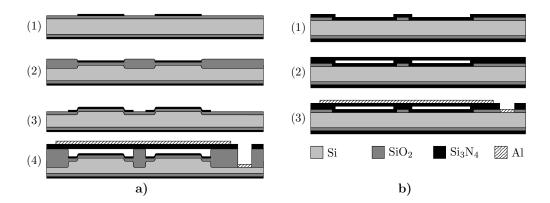

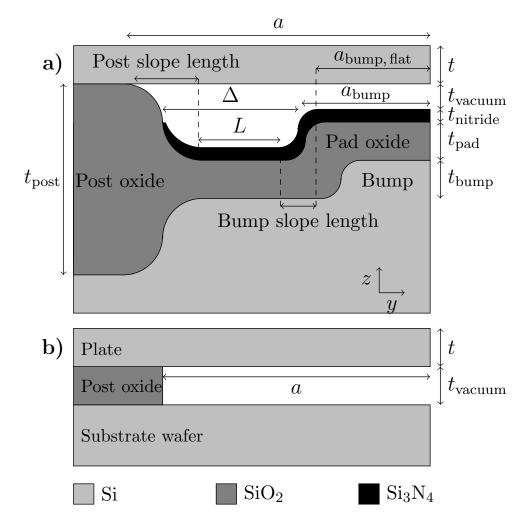

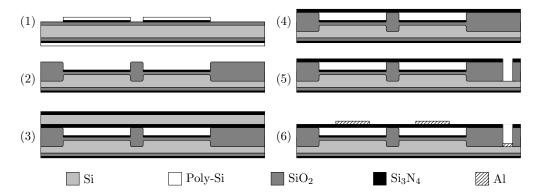

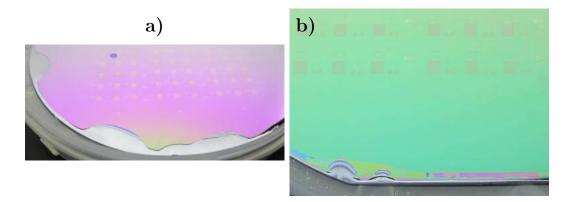

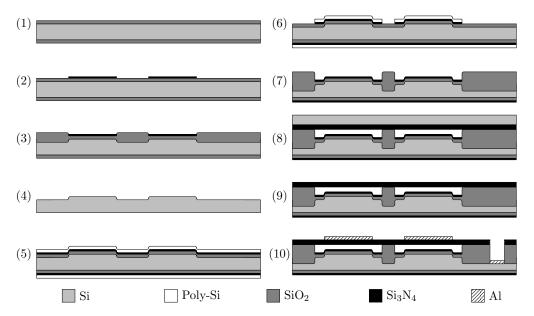

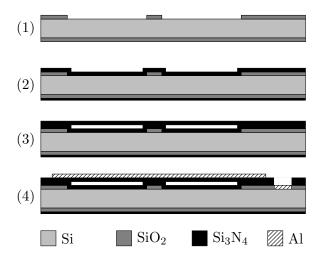

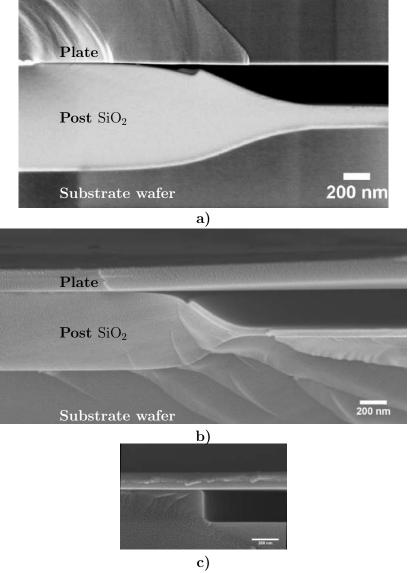

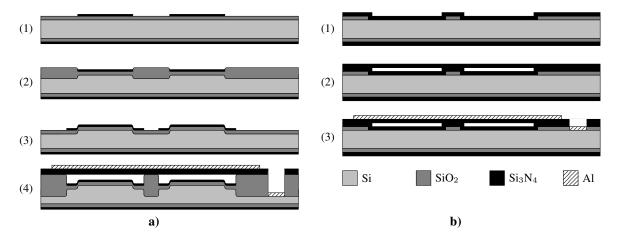

The first CMUTs were fabricated using standard micromachining clean-room processes and a sacrificial release method [46]. In the sacrificial release method the cavity is defined by a sacrificial layer which is selectively etched after a plate layer has been deposited on top. Figure 1.6 a) shows a cross-section of a CMUT cell fabricated using the sacrificial release method. In this example typical materials have been used such as Si for the bottom electrode, a Si<sub>3</sub>N<sub>4</sub> plate and an Al top electrode. A new fabrication method was developed by the Stanford group in 2003 [47], where the cavities are etched out in a dielectric layer (e.g. SiO<sub>2</sub>) and subsequently the plate is wafer bonded to this substrate wafer hereby encapsulating the cavities. The result of this wafer bonding fabrication technique is shown in Figure 1.6 b).

1.4. THE CMUT 13

**Figure 1.6:** Cross-sectional sketches of single CMUT cells fabricated with the a) sacrificial release method and b) wafer bonding fabrication process. The choice of material is chosen to match what is commonly used.

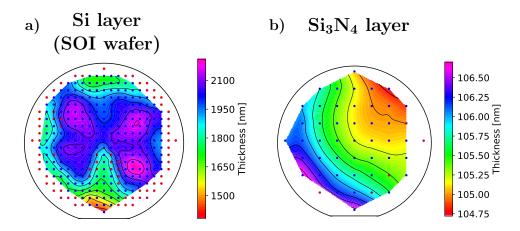

Here the black line between the two SiO<sub>2</sub> layers denotes the bonding interface. Silicon on insulator (SOI) wafers have been used extensively to define the plate [33, 48, 49] due to the possibility of a low thickness variation and well controlled mechanical properties of the device layer [46], which is the layer comprising the plate.

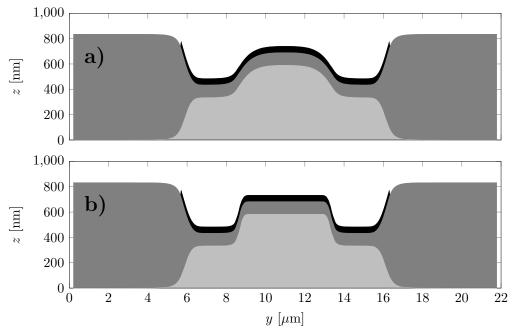

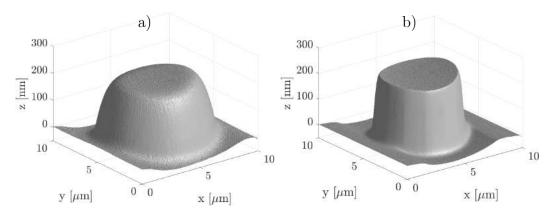

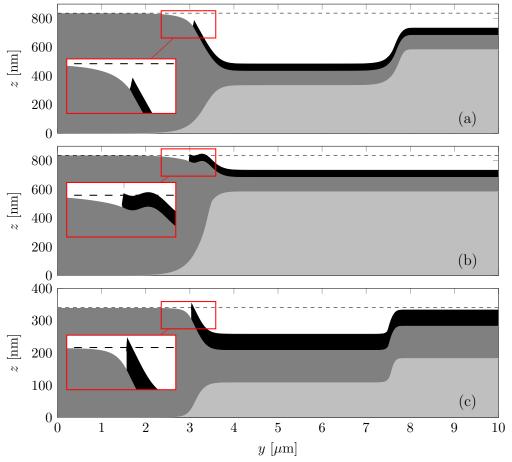

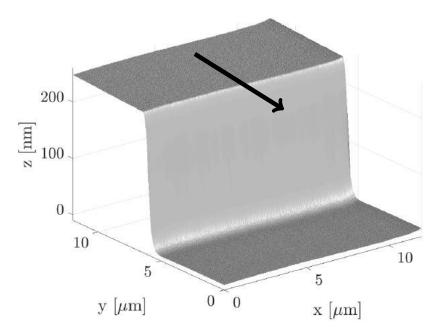

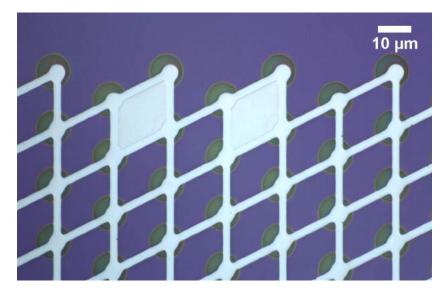

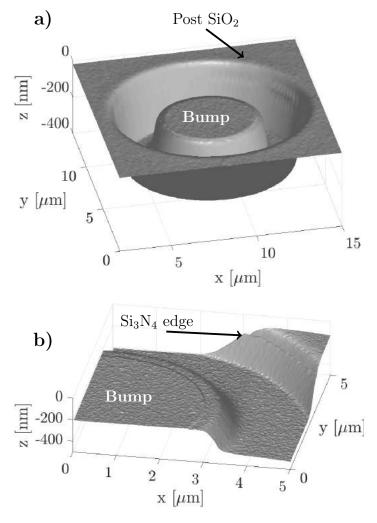

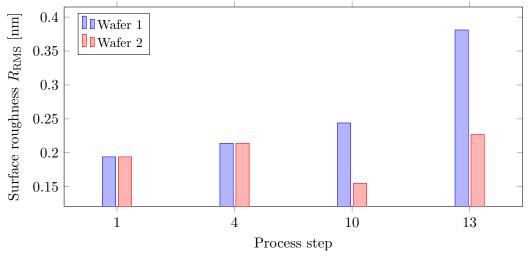

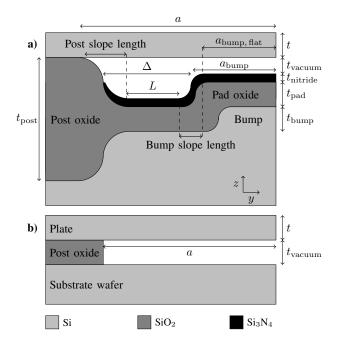

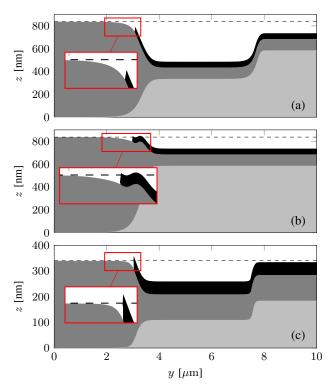

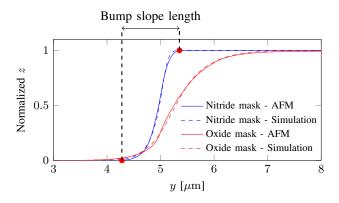

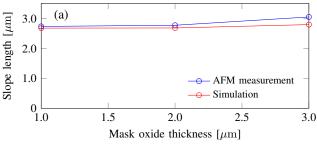

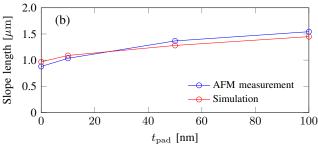

The local oxidation of silicon (LOCOS) fabrication process was first published in [50] also by the Stanford Group. A journal paper was published by the same group in 2011 [42] which goes more into detail with the fabrication process and modeling. Figure 1.7 a) shows a sketch of a cross-section of a finished CMUT cell fabricated by the LOCOS process. The spacer between the top and bottom electrodes is called the post oxide which can be made thicker than the spacers in the processes shown in Figure 1.6 for the same gap height. This decreases the parasitic capacitance which improves the device performance [42]. Furthermore, the control and uniformity over a wafer of the vacuum gap thickness is approximately a couple of nanometer which enables the fabrication of small (< 50 nm) vacuum gaps. In the LO-COS process the silicon substrate wafer is selectively oxidized to first form the Si bumps in the center of the cavities and then the oxide posts forming the cavities. The structure in Figure 1.7 b) is a CMUT fabricated by only using a single LOCOS process step forming cavities but not the Si bumps. Hence, the structure in 1.7 a) will here be called a double LOCOS structure, while the structure in 1.7 b) will here be called a single LOCOS structure. Both structures have been fabricated in this project along with the structure in Figure 1.6 b). The fabrication processes of these structures all rely on wafer bonding. It should be noted that the plate material for the wafer bonded structures also can be other materials such as Si<sub>3</sub>N<sub>4</sub> as demonstrated in [51-54].

### 1.4.3 State of the art of CMUT sensing

In this section the state of the art for CMUT sensing is presented. The emphasis will be on CMUTs used for gas sensing but a short overview of CMUTs used as bio-sensors is presented in the end.

**Figure 1.7:** Cross-sectional sketches of single CMUT cells fabricated with the a) double LOCOS process b) single LOCOS fabrication process. Notice the central Si protrusions, called bumps, in the cavities in a) and the lack hereof in b).

**Figure 1.8:** Number of publications as a function of time for CMUTs used as gas sensors and biological sensors, including papers in conference proceedings.

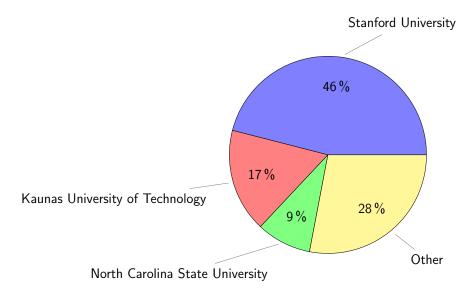

Figure 1.8 shows the number of publications as a function of time for CMUTs used as gas sensors or biological sensors. Compared with the plot for the entire CMUT field (Figure 1.5), the number of publications is rather constant with much fewer publications each year. The first articles were published in 2007 by the Stanford group [40,55]. The same group has published almost half of the articles regarding bio-sensing and gas sensing, see Figure 1.9. Most of these articles are about gas sensing, whereas the publications from Kaunas University of Technology are mainly about biological sensing using CMUTs.

#### Gas sensing

The first articles concerning the use of CMUTs for gas sensing were published by the Stanford group. In 2007 Park et al. [40] described the use of a 6 MHz CMUT array, originally designed for medical ultrasonic imaging, for gas sensing. Specifically, four analytes were detected: water, isopropanol, acetone and methanol. The CMUT elements in the array were drop coated

1.4. THE CMUT 15

**Figure 1.9:** Publication distribution by institution. Note that almost half of the publications are published by an author in the Stanford group.

with three different polymers showing different sensitivities towards each of the analytes. This technique has in subsequent publications been employed in order to be able to distinguish between analytes.

Drop coating has been used to a great extent for the functionalization of CMUTs, e.g. [56] [29]. Drop coating consists of dissolving the functionalization layer material in a solvent. Droplets of this liquid solution is hereafter dispensed unto the CMUT element and when the solvent evaporates the functionalization layer remains on the surface. This technique is an inherently serial process but the deposition can be performed by a dedicated machine which can be programmed to functionalize entire wafers at a time at a fast pace. Li et al. [57,58] demonstrated a novel 2-step coating technique where first a layer of nanoparticles is deposited to form a uniform substrate layer for the second chemical sensitive layer. The nanoparticle layer serves multiple purposes. First, it localizes the second layer to the spot where it is deposited. This is useful in the case where several different layers are to be deposited close to each other. Secondly, it ensures a more uniform layer which minimizes the decrease of the quality factor. Finally, the effective surface area is increased due to the spherical shape of the nanoparticles, at the expense of an increased mass of the plate, due to the weight of the particles.

Several articles have been published by the Stanford group regarding the detection of dimethyl methylphosphonate (DMMP) which is a common simulant for sarin gas. Such a gas sensor should have a gas concentration LOD

of in the order of parts per billion (ppb) or better [3]. In 2008 Lee et al. and Park et al. [59,60] functionalized CMUTs with a resonance frequency of 18MHz with a polyisobutylene (PIB) layer for the detection of DMMP. The mass sensitivity per area was found to be  $130 \frac{\text{zg}}{\text{Hz} \cdot \mu \text{m}^2}$ . The DMMP volume concentration sensitivity and limit of detection was found to be 37 ppbv/Hz and 21 ppbv, respectively. These already impressive values were further improved upon with a CMUT device with a resonance frequency of 47.7 MHz and a new functionalization layer [3,61]. The layer was a polymer abbreviated DKAP, which is a poly(dimethylsiloxane) derivative. The mass sensitivity of the CMUT was  $48.8 \frac{zg}{Hz \cdot \mu m^2}$ , which is an improvement by a factor 2.7 compared with the previous device. The DMMP volume sensitivity was measured to be 34.5 pptv/Hz [3] which is about an order of magnitude better than the volume sensitivity reported previously in [59,60]. The same order of improvement is seen for the volume concentration LOD which was 50.5 pptv with gas flow [3] and 16.8 pptv without gas flow [61]. Both the volume sensitivity and gas concentration LOD were, at the time of publication, the best reported for a gravimetric DMMP gas sensor.

The detection of CO<sub>2</sub> using CMUTs has also been studied. Lee et al. [62] used mesoporous silica layers on top of CMUT plates in order to increase the volume sensitivity towards CO<sub>2</sub>. The mesoporous layer increases the surface area of the sensor, thus more molecules can load the plate per area and a larger response/better sensitivity is expected. By using such a mesoporous layer with a (3-Aminopropyl)triethoxysilane (APTES) functionalization layer on top a volume sensitivity of 1.6 ppm/Hz and a volume LOD of 1.82 ppm was obtained. The volume sensitivity was 38 times higher than that of a mesoporous CMUT device with no APTES functionalization. In an article from the same year by the same first author [63] different functionalization layers were compared. The polymer guanidine showed the best volume sensitivity towards  $CO_2$ : 1.06 ppm/Hz. In 2015 and 2016 a conference and a journal paper were published by Barauskas et al. concerning the detection of greenhouse gasses, including CO<sub>2</sub> [41,64]. A volume sensitivity of 0.25 ppm/Hz is obtained with a polymer functionalization layer made of polyethylenimine (PEI). This is the best volume sensitivity for CO<sub>2</sub> reported for CMUTs. However, the volume LOD was 330 ppm which is much higher compared with the volume LOD of 1.82 ppm reported by Lee et al.

One of the main challenges of any gravimetric sensor is how to obtain selectivity. Functionalization layers with a chemistry specific tailored to a target analyte can for gas mixtures with few confounding gasses be enough to detect the target analyte gas. However, when more complex gas mixtures, which can be encountered during operation outside of a laboratory, 1.4. THE CMUT 17

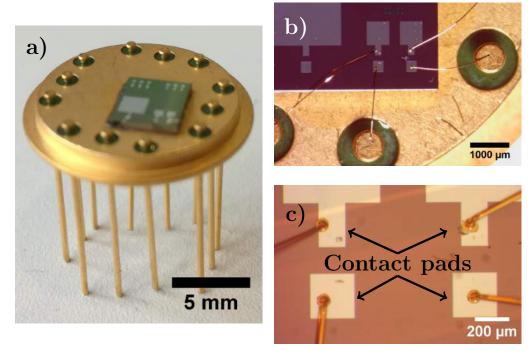

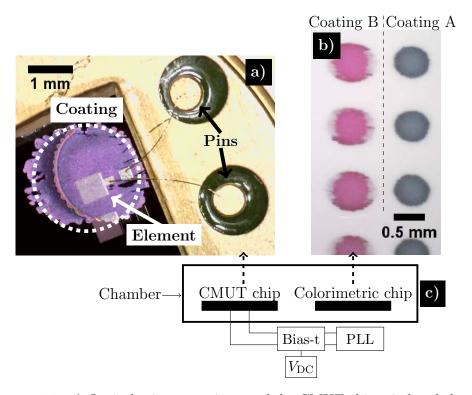

are faced, other solutions to the selectivity challenge must be employed. One solution has been to use CMUT arrays with multiple separate elements that each can have a different functionalization layer [21, 29, 49, 65, 66]. The responses of the elements can then be analyzed e.g. using principal component analysis (PCA) [29]. Another approach to increasing the selectivity has been to combine the CMUT with another sensor type with a better selectivity. This approach was investigated by Mølgaard et al. [53, 56], where a colorimetric sensor was combined with a CMUT for detection of benzyl methyl ketone (BMK) which is a precursor molecule for the synthesis of (meth)amphetamine. The colorimetric sensor showed an good selectivity towards BMK, while the CMUT sensor can give a quantitative value for the concentration when calibrated.

#### **Biosensing**

A short review of the publications regarding the use of CMUTs as biological sensors is given here for completeness. Since CMUTs are flexural resonators with out of plane deflections, the use of them as immersion sensors is not an obvious choice since they will be damped more than sensors using bulk or surface/interface waves such as BAWs and SAWs [28]. However, CMUTs generally exhibit a higher mass sensitivity than e.g. FBARs and SAWs [28], also see Figure 1.3. Moreover, the previously mentioned advantages of the CMUT over the other gravimetric sensors still apply. Particularly, the vacuum filled cavity is a great advantage in immersion since the plate is only exposed and hereby dampened by the medium on one side, unlike the situation for cantilevers or double clamped bridges.

The CMUT has been used as an immunosensor for the detection of various antigens or antibodies (depending on what part is immobilized on the CMUT surface). The immune system of the human body makes antibodies that can react and partake in a very specific/selective bond with an antigen. Clearly, this selectivity is desired as it will translate to a selective immunosensor overcoming one of the major challenges of gravimetric sensors.

The first peer-reviewed paper of a CMUT used as a biosensor was published by Ramanaviciene et al. [67]. In this paper they demonstrate the use of a CMUT as an immunosensor by immobilizing bovine leukemia virus protein gp51 on the CMUT and detecting anti-gp51 in a solution. Both the resonance frequency and real part of the impedance was seen to change as a function of the concentration of anti-gp51. The same antigen antibody pair was used in subsequent publications [28,68,69], where the effect of the added mass and possible stress in the biofunctionalization layer was investigated. It was found that if sufficient stress is present in this layer the resonance

frequency can increase after the layer is deposited.

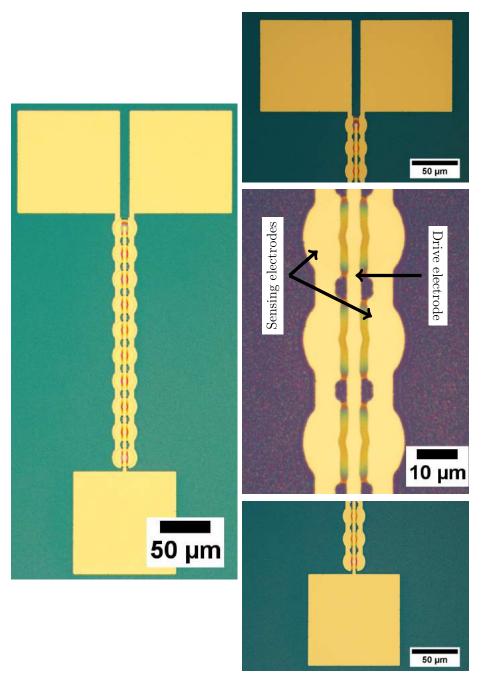

Onen et al. [70] studied the use of a CMUT for detection of ovarian cancer, more specifically, anti-apoptotic protein Bcl-2 was to be detected. The device consisted of two sets of inter-digital CMUT arrays for excitation and detection of Lamb waves. In between these two arrays was a delay line coated with the functionalization layer. The added mass after the antigen antibody reaction then causes a measurable decrease in resonance frequency. The device resembles a SAW sensor utilizing Lamb waves. By relaying on Lamb or surface waves in immersion a lower damping should in general be observed. CMUT sensors for other types of immersion measurements have previously used a similar detection principle [71–73].

#### 1.5 Thesis aim

The overall aim of this thesis is to develop and apply state of the art gas sensors. This is to be achieved by using CMUTs as a technology platform from which different sensor designs can be realized. The CMUTs should be modeled, designed, and fabricated so a high mass sensitivity and low limit of detection is obtained. Furthermore, alternative ways of increasing the selectivity are to be explored. Finally, the use of the CMUTs as gas sensors should be demonstrated by applying them as such.

### 1.6 Academic contributions

The project resulted in two journal papers and one conference proceeding paper, see Appendix A, B, and C, respectively. Furthermore, two talks were given at the conferences International Workshop on Micromachined Ultrasonic Transducers (MUT) 2016 in Rome and MUT 2017 in Glasgow, respectively. In addition, a poster presentation was given at IEEE International Ultrasonics Symposium (IUS) 2017 in Washington D.C.

#### 1.7 Thesis outline

The outline of the thesis is given below to provide the reader with an overview of the thesis.

**Chapter 1 - Introduction**: This chapter qualifies the choice of CMUTs for use as gas sensors by comparing their performance to other gas sensor types. Further, the history and state of the art of CMUTs used for sensing

19

is presented which provides the reader with a background knowledge of prior work in the field.

Chapter 2 - Theory: The theory chapter describes the static and dynamic behavior of the CMUT, leading to an expression of the electrical impedance which can be used to evaluate later impedance measurements. Finally, expressions for the mass sensitivity and mass limit of detection is given.

Chapter 3 - Design: The design of the four CMUT generations, G1-G4, made during this project is presented. The impact of the different fabrication methods on the design of the CMUT cell is shown. Specifically, the design space for the LOCOS CMUTs is investigated, showing how different design choices impact the final cell geometry. In addition, the numerical model that was developed to model the CMUT is presented along with a discussing of the choice of plate material.

Chapter 4 - Device fabrication: This chapter introduces the process flows used for fabricating the CMUTs in the cleanroom. The most critical process steps are highlighted and discussed. Finally, some of the process optimization performed during and before processing is presented.

Chapter 5 - Characterization: In this chapter the fabricated chips are presented through various measurements: optical and electron microscopy, impedance spectroscopy. The limit of detection and mass sensitivity are determined experimentally. These two important figures of merit are compared with the state of the art in the literature.

Chapter 6 - Gas sensing experiments - BMK: In this chapter the CMUT is applied as a gas sensor for the detection of a precursor molecule for the synthesis of (meth)amphetamine. The CMUT is coated with a functionalization layer and combined with a colorimetric chip. The colorimetric method showed a high degree of selectivity while the functionalization layer on the CMUT increased the selectivity towards the precursor molecule.

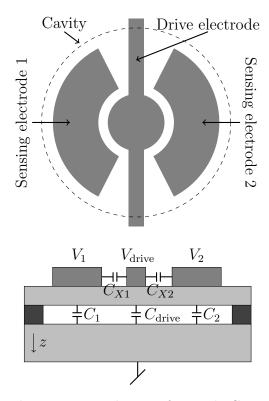

Chapter 7 - Alternative read-out method: In this chapter an alternative method for detecting the resonance frequency is presented. The method involves both a new top electrode design for the CMUT and an external circuit. The design of both is discussed and finally fabricated CMUT chips with this new design are shown.

Chapter 8 - Conclusion and outlook: In this final chapter the conclusions

from the previous chapters are collected. The chapter ends with an outlook where suggestions of improvements to the work already done and future work is given.

# CHAPTER 2

**Theory**

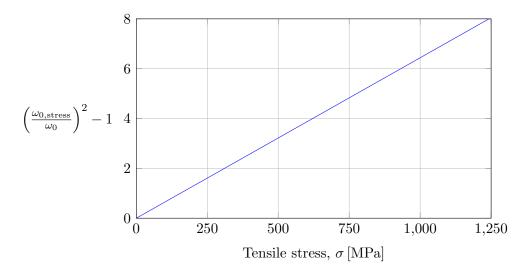

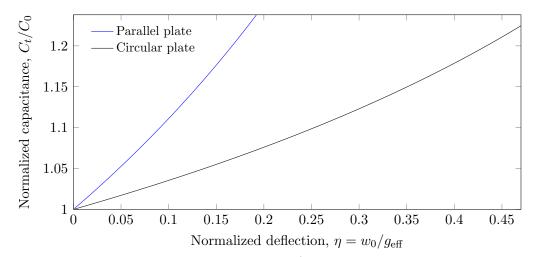

In this chapter the behavior of the CMUT is sought described through mathematical models. First, the linear harmonic oscillator is presented which is the most basic dynamic model for resonators in general. Next, a static CMUT model is presented, from which analytical expressions of the resonance frequency and pull-in voltage are obtained. The dynamic behavior of the CMUT is modeled by an equivalent circuit model spanning the three energy domains: electrical, mechanical, and acoustical. This model provides insight into what affects the electromechanical coupling coefficient and gives an expression for the impedance which is useful for comparison with measurements. Next, the distributed mass sensitivity is calculated for the CMUT both with regular and stressed plates. The normalized sensitivities of different sensor types are compared which shows why the range of values is so large, as seen in Figure 1.3. Finally, an expression for the mass limit of detection is given which is shown to be affected by the noise in the system and thus by the quality factor of the CMUT.

# 2.1 Linear harmonic oscillator

In this section the most simple oscillator model is presented: the linear harmonic oscillator. From this model the concepts of eigenfrequency, resonance, damping and quality factor is derived. The derivation and results are valid for any resonator that oscillates and is therefore the most simple model of a CMUT operated as a resonator. The following section is based on [16]

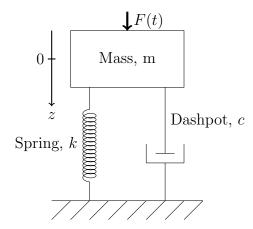

**Figure 2.1:** Mass, spring, dashpot linear single degree of freedom oscillator. The spring and dashpot are fixed at the ground and at the mass which is free to move along the z-axis.

(p.29-40).

Figure 2.1 shows a schematic representation of the single degree of freedom linear harmonic oscillator model. All relevant properties are lumped in to three discrete elements: the mass m, the spring with a spring constant k, and the dashpot with a coefficient of damping c. All mass is located in a single point and is only made up of the mass m, that is the spring and dashpot are massless. The resonator is assumed to be harmonically driven with am external driving force:  $F(t) = F_0 \cos(\omega t)$ . Small amplitudes are assumed resulting in linear behavior of all components.

The equation of motion is found by applying Newton's second law on the system. The left side of Equation 2.1 shows the mass times the acceleration while the right side shows the sum of all the forces acting on the mass.

$$m\frac{d^2z}{dt^2} = F(t) - kz - c\frac{dz}{dt},$$

(2.1)

where the spring represents the restoring force obeying Hook's law  $F_{\text{spring}} = -kz$  and the damping force is proportional to the speed of the mass  $F_{\text{dashpot}} = -c\frac{dz}{dt}$ . The terms and constants in Equation 2.1 can be rearranged to the more convenient form:

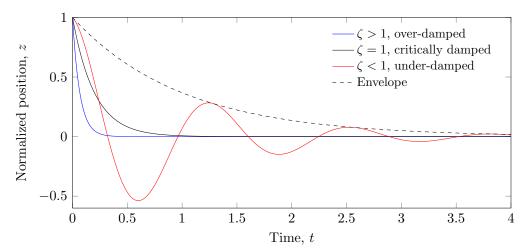

**Table 2.1:** Table showing the three damping regimes defined by the damping ratio  $\zeta$ . The solution characteristic described the behavior of the mass which is exemplified in Figure 2.2.

| Regime name                                      | Damping ratio $\zeta$               | Solution characteristic                                                                                                                                     |  |

|--------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Over-damped<br>Critically damped<br>Under-damped | $\zeta > 1$ $\zeta = 1$ $\zeta < 1$ | No oscillation, amplitude exponentially decreasing<br>No oscillation, amplitude exponentially decreasing<br>Oscillatory, amplitude exponentially decreasing |  |

$$\frac{d^2z}{dt^2} + 2n_c \frac{dz}{dt} + \omega_0^2 z = \frac{F(t)}{m},$$

(2.2)

$$n_c = \frac{c}{2m},\tag{2.3}$$

$$\omega_0 = \sqrt{\frac{k}{m}}, \qquad (2.4)$$

$$\zeta = \frac{n_c}{\omega_0} = \frac{c}{2\sqrt{km}}, \qquad (2.5)$$

$$\zeta = \frac{n_c}{\omega_0} = \frac{c}{2\sqrt{km}},\tag{2.5}$$

where  $n_c$  is called the coefficient of damping,  $\omega_0$  is the eigenfrequency of the resonator and  $\zeta$  is the damping ratio.

#### Undriven oscillator

The simplest case is when there is no external force driving the oscillator: F(t) = 0 and consequently the right hand side of Equation 2.2 is zero and the equation becomes homogeneous. Table 2.1 shows the three damping regimes which can be identified by inserting a trial function in the homogeneous differential equation (for a detailed derivation see [16]). Solutions for these three regimes are plotted in Figure 2.2. The solutions in the figure can be seen as the step responses. The behavior described in Table 2.1 is reproduced in the plot where the over-damped solution decreases the fastest followed by the critically damped solution and finally the under-damped solution which oscillates. Since no external force is acting on the system the amplitude of the oscillations will decrease as the oscillator is being dampened as time passes.

#### Driven oscillator

We now turn the attention to the driven harmonic oscillator, that is when a harmonic external force F(t) is applied to the mass. For the CMUT the driving force is electrostatic and is applied to the plate. The solution is a sum

Figure 2.2: Position as a function of time for three solutions to the undriven linear harmonic oscillator. Parameter values:  $\omega_0 = 5$ ,  $\zeta_{\text{over}} = 3$ ,  $\zeta_{\text{crit}} = 1$  and  $\zeta_{\text{under}} = 0.2$ . Note that the only oscillatory behavior is found for the under-damped oscillator.

of the transient solution found for the homogeneous equation and a steady state solution which is independent of the initial conditions. The steady state solution can take the form:

$$z(t) = z_0 e^{i\omega t}. (2.6)$$

The amplitude  $z_0$  can be written in polar form as the norm and phase:

$$|z_0| = \frac{F_0/m}{\sqrt{(\omega_0^2 - \omega^2)^2 + (2\zeta\omega_0\omega)^2}} = \frac{F_0/m}{\sqrt{(1 - (\frac{\omega}{\omega_0})^2)^2 + (2\zeta\frac{\omega}{\omega_0})^2}}$$

(2.7)

$$\phi = \arctan\left(\frac{2\zeta\omega_0\omega}{\omega^2 - \omega_0^2}\right) = \arctan\left(\frac{2\zeta\frac{\omega}{\omega_0}}{(\frac{\omega}{\omega_0})^2 - 1}\right). \tag{2.8}$$

The gain, G, of the steady state solution can now be extracted from the norm of the amplitude:

$$G = \left(\sqrt{\left(1 - \left(\frac{\omega}{\omega_0}\right)^2\right)^2 + \left(2\zeta\frac{\omega}{\omega_0}\right)^2}\right)^{-1}.$$

(2.9)

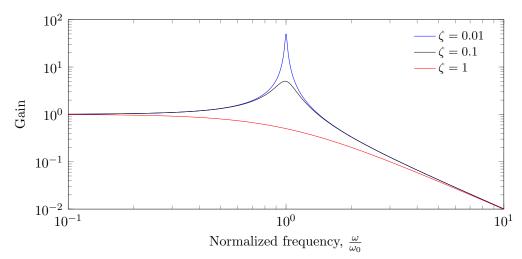

Figure 2.3 shows a plot of G as a function of the normalized frequency  $\frac{\omega}{\omega_0}$  for three damping ratios  $\zeta$ . The lower the damping (lower  $\zeta$ ) the higher the gain

**Figure 2.3:** Gain as a function of normalized frequency for three damping ratios. The lower the damping ratio the more narrow and higher a peak is observed at resonance.

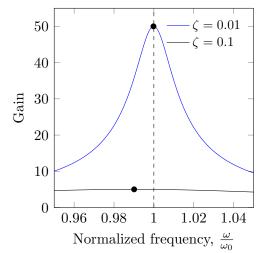

and more narrow peak. Intuitively this makes sense since a lower damping means less power is dissipated. The frequency at which the maximum gain is achieved is called the resonance frequency and is denoted  $\omega_r$ . What is less apparent from the figure is the decrease of  $\omega_r$  for increased damping. Figure 2.4 shows a zoom in on two of the peaks where this decrease of the resonance frequency relative to the eigenfrequency is seen. This phenomenon is described by:

$$\omega_r = \omega_0 \sqrt{1 - 2\zeta^2},\tag{2.10}$$

which is what was observed in Figure 2.4. Equation 2.10 also shows that for oscillators with minor damping the resonance frequency and eigenfrequency will approximately be the same since  $\lim_{\zeta \to 0} \omega_0 \sqrt{1 - 2\zeta^2} = \omega_0$ .

For real physical resonators the concept of quality factor Q is used to describe the damping. The relationship between Q and the various physical damping mechanisms is given in Section 2.5. The quality factor Q is closely related to the damping ratio  $\zeta$ :

$$Q = \frac{\sqrt{1 - 2\zeta^2}}{2\zeta},\tag{2.11}$$

which means that a slightly damped resonator with  $\zeta \ll 1$  will have a high quality factor. For many resonators, and especially for gravimetric mass sensors, a high quality is desired since it results in larger deflection amplitudes (see Figure 2.3), more narrow peaks (lower bandwidth) and a lower noise. For

**Figure 2.4:** Zoom-in on two peaks in Figure 2.3 demonstrating the slight different resonance frequencies cause by the difference in damping.

gravimetric mass sensors a lower noise gives a lower LOD as will be shown in Section 2.5.

The quality factor describes the amount of damping of a resonator. The damping mechanism is solely described by the dashpot in the oscillator model (Figure 2.1) which is the only element capable of dissipating energy. The spring and mass represents the potential and kinetic energy, respectively, of the oscillator doing oscillation. The quality factor can be defined in the energy domain:

$$Q = 2\pi \frac{W}{\Delta W},\tag{2.12}$$

where W is the total energy stored and  $\Delta W$  is the energy which is lost in one oscillation period. This relation shows that a high Q is equivalent to having a resonator that loses energy more slowly which means that it will ring down over a longer period of time. Later it is shown how the quality factor can affect the limit of detection.

In this section a simple dynamic model of a linear resonator was presented. It was shown that three distinct damping regimes exist and how the resonator moves in each of these regimes. Lastly, the resonance frequency was determined and it was shown how the damping can be modeled by a single parameter called the quality factor.

**Figure 2.5:** Cross-section sketch of a single CMUT cell defining the geometrical parameters and coordinate system.

# 2.2 Static CMUT model

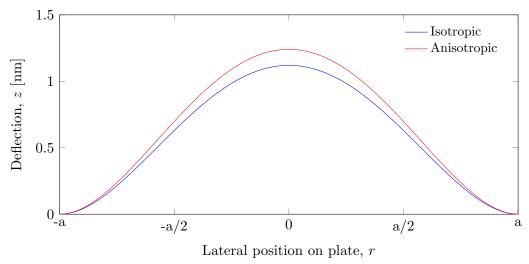

In this section a static model of the CMUT is presented. The starting point is the plate deflection profile, for which the solution for anisotropic plate materials only differs by a numerical prefactor compared with the solution for isotropic plate materials. The deflection profile enables the calculation of the eigenfrequency, pull-in voltage, energies and capacitance of the CMUT, which are presented in the end of the section. Figure 2.5 shows a cross-section of a CMUT cell with various variables defined. In the remainder of the thesis it is assumed that the plate shape is circular, since circular plates exclusively have been used.

# 2.2.1 Plate deflection profile

The deflection profile of a plate can be found by solving the differential plate equation. This equation can in its simplest form be written as [74]:

$$\nabla^4 w = \frac{p}{D},\tag{2.13}$$

where w is a function describing the deflection profile of the plate, p is the pressure difference over the plate and D is the flexural rigidity given by:

$$D = \frac{Eh^3}{12(1-\nu^2)},\tag{2.14}$$

where E is Young's modulus, h is the thickness of the plate (see Figure 2.5) and  $\nu$  is Poisson's ratio. Hence, the flexural rigidity contains all the plate material properties. The flexural rigidity given here is valid for isotropic materials. Later in this section the anisotropic version is presented.

Equation 2.13 is the governing equation determining the deflection profile and it is only valid when certain assumptions are met [75]:

- Small plate deflections relative to the plate thickness:  $\frac{h}{w_{\text{max}}} \gtrsim 5$ . This is to avoid stress stiffening effects.

- Large plate aspect ratio:  $\frac{a}{h} \gtrsim 40$ . This is required so shear deformation can be ignored.

- No built-in material stress:  $\sigma = 0$ .

The pressure on the right side of Equation 2.13 corresponds to a uniform applied force on the plate. The boundary conditions are that of a perfectly clamped plate:

$$w(0) < \infty \tag{2.15}$$

$$w(a) = 0 (2.16)$$

$$\frac{\partial w(0)}{\partial r} = 0 \tag{2.17}$$

$$\frac{\partial w(a)}{\partial r} = 0, (2.18)$$

meaning that the deflection at the center of the plate is finite, the deflection at the edge is zero and that the slope is zero both the center and edge of the plate.

Equation 2.13 can for the isotropic material case be rewritten in cartesian coordinates as:

$$\frac{\partial^4 w}{\partial x^4} + 2 \frac{\partial^4 w}{\partial x^2 \partial y^2} + \frac{\partial^4 w}{\partial y^4} = \frac{p}{D}.$$

(2.19)

Anisotropic materials are commonly used for plates in CMUTs, e.g. when SOI wafers are fusion bonded to the substrate wafer. In this case Si is the anisotropic material. It has been shown that the isotropic plate deflection profile can have an error of up to 10% as compared with finite element modeling while the anisotropic deflection had an error of < 1% [76]. This is the motivation behind using the anisotropic plate equation instead of the isotropic version.

The anisotropic generalized plate equation is given as [75, 76]:

$$\frac{\partial^4 w}{\partial x^4} + k_1 \frac{\partial^4 w}{\partial x^3 \partial y} + k_2 \frac{\partial^4 w}{\partial x^2 \partial y^2} + k_3 \frac{\partial^4 w}{\partial x \partial y^3} + k_4 \frac{\partial^4 w}{\partial y^4} = \frac{p}{D_a}$$

(2.20)

**Table 2.2:** Compliance constants for N-type crystalline silicon at 300 K for a low doping level (150  $\Omega \cdot \text{cm}$ ,  $\approx 2.8 \times 10^{13} \, \text{cm}^{-3}$ ) and high doping level (3.26 m $\Omega \cdot \text{cm}$ ,  $\approx 2.1 \times 10^{19} \, \text{cm}^{-3}$ ). Adapted from [76].

|              | Low doping                                 | High doping                                |

|--------------|--------------------------------------------|--------------------------------------------|

| $s_{11}^c$   | $7.691 \times 10^{-12}  \mathrm{Pa^{-1}}$  | $7.858 \times 10^{-12} \mathrm{Pa^{-1}}$   |

| $s_{12}^{c}$ | $-2.1420 \times 10^{-12} \mathrm{Pa^{-1}}$ | $-2.2254 \times 10^{-12} \mathrm{Pa^{-1}}$ |

| $s^c_{44}$   | $12.577 \times 10^{-12} \mathrm{Pa^{-1}}$  | $12.628 \times 10^{-12} \mathrm{Pa^{-1}}$  |

where  $k_1$ ,  $k_2$ ,  $k_3$ ,  $k_4$  are plate equation coefficients and  $D_a$  is the anisotropic flexural rigidity. These constants are material specific and depends on the orientation of the plate relative to the material crystal structure. In order to find the constants in Equation 2.20 the elastic constants for the plate must first be found. Only part of the derivation is given here, for the full derivation readers are referred to reference [75] and [76].

The classic stress  $\sigma$ , strain  $\epsilon$ , relation is in the crystallographic coordinate system given by:

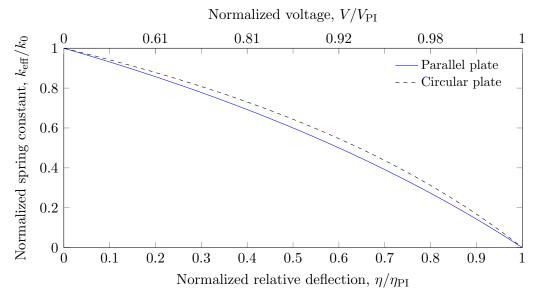

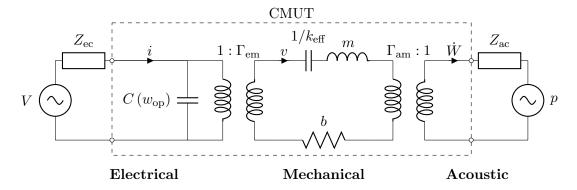

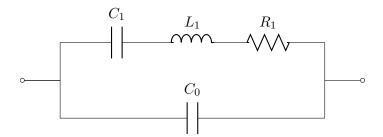

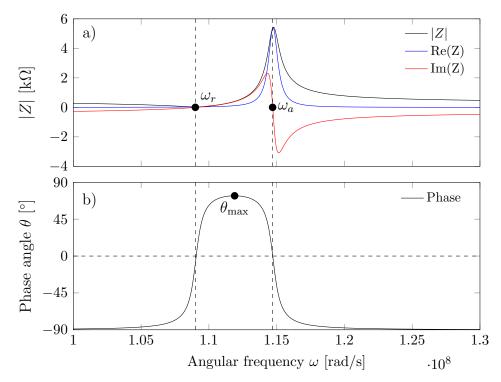

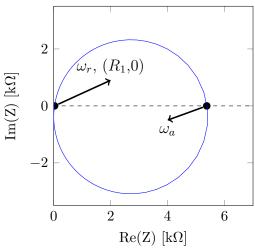

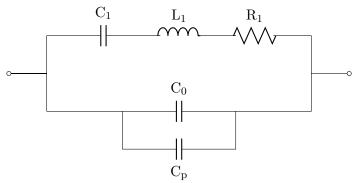

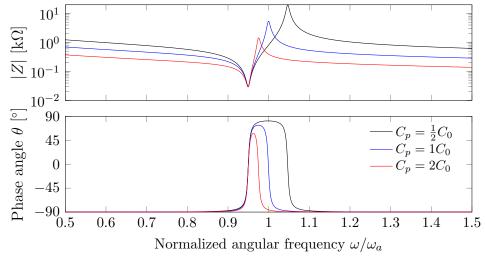

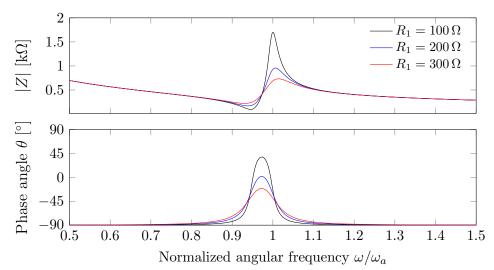

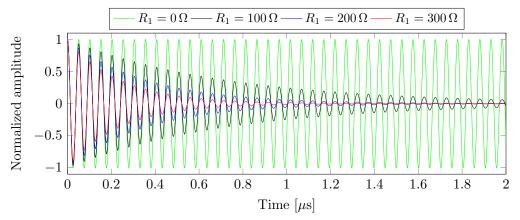

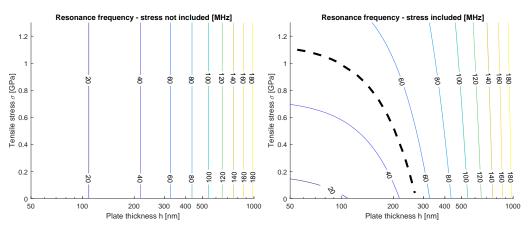

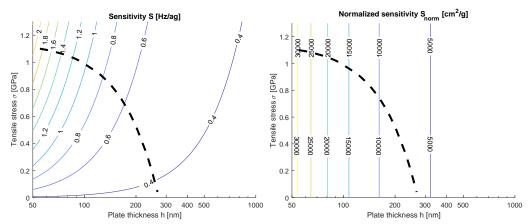

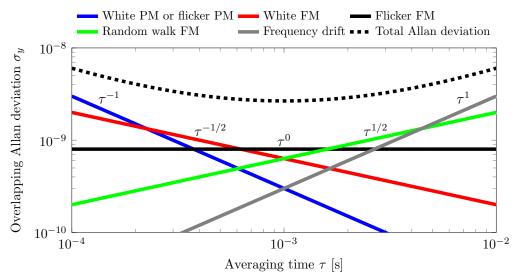

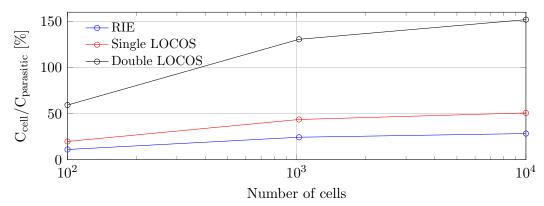

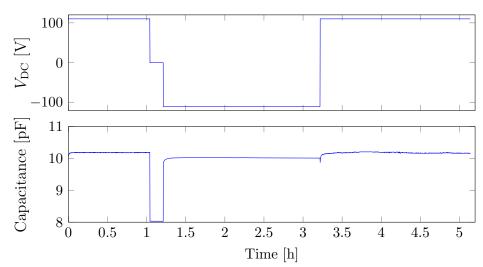

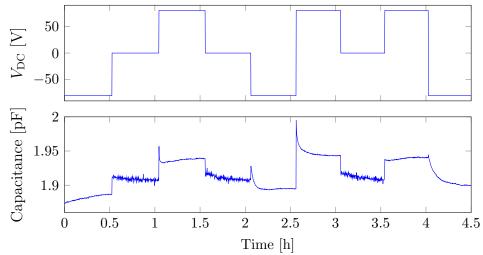

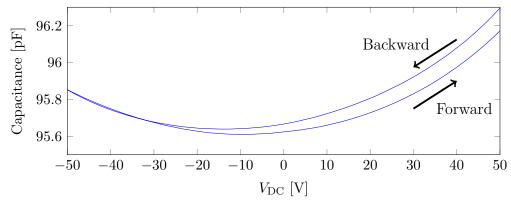

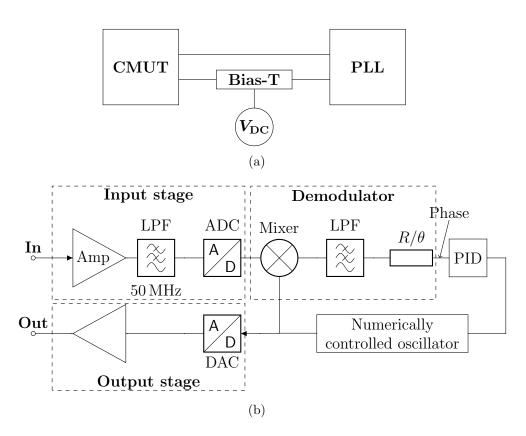

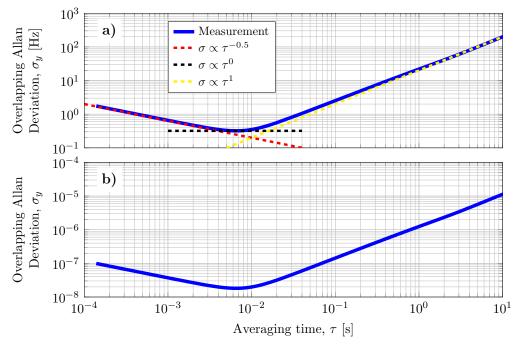

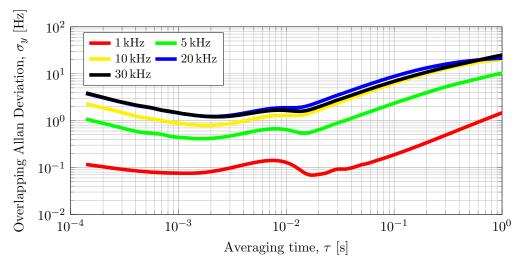

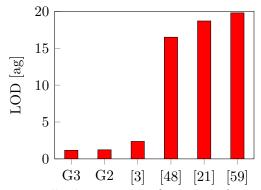

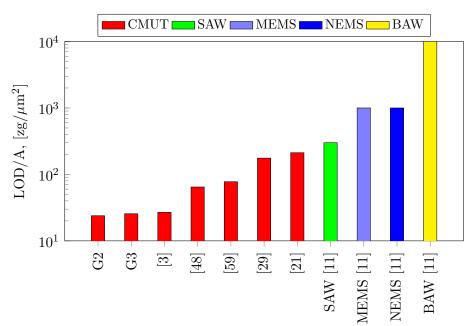

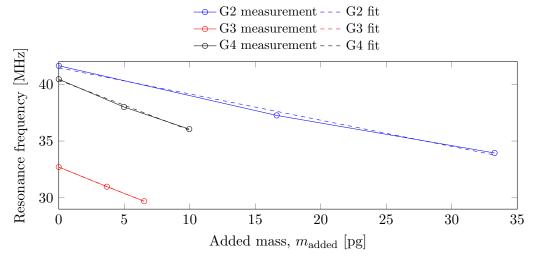

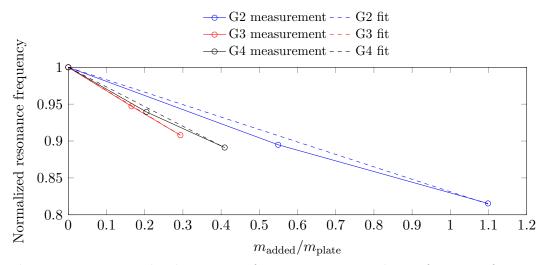

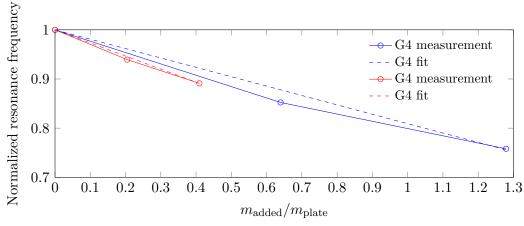

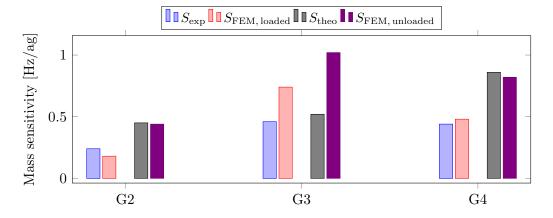

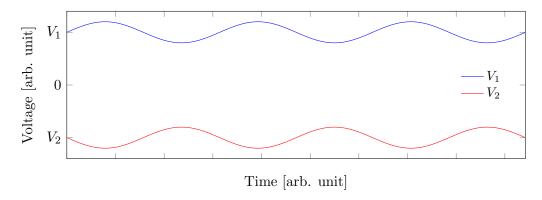

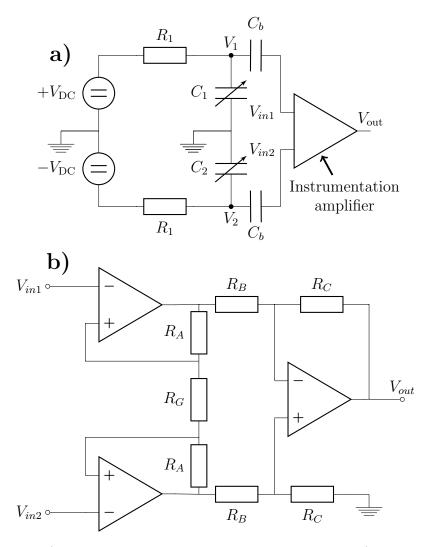

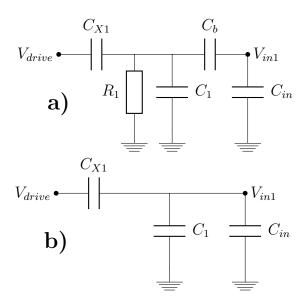

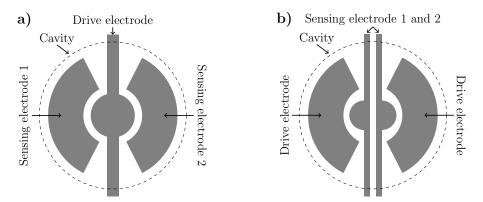

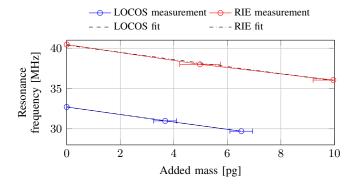

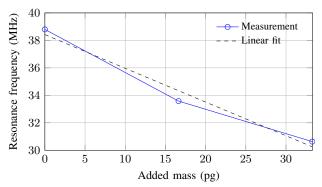

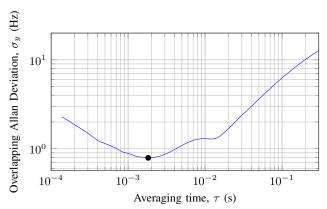

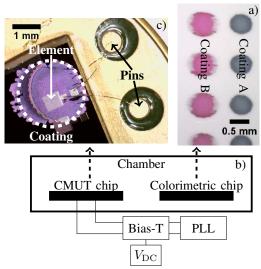

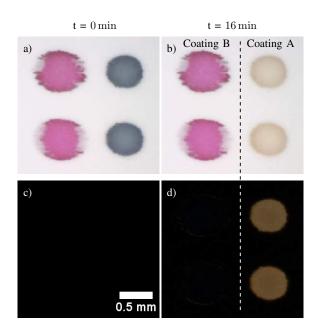

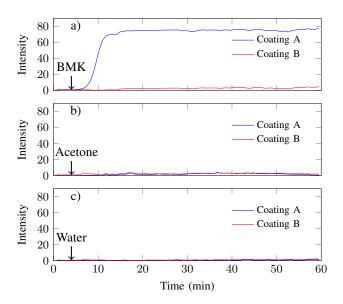

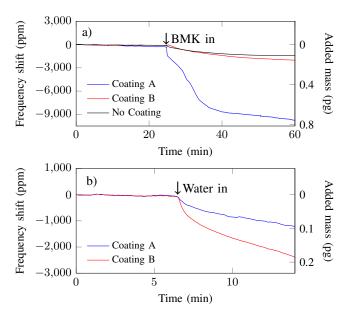

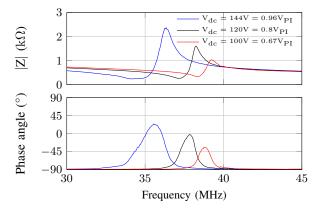

$$\epsilon^c = \mathbf{s}^c \sigma^c, \tag{2.21}$$