**DTU Library**

### **Advances in Bidirectional DC-DC Converters for Future Energy Systems**

**Tomas Manez, Kevin**

Publication date: 2018

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Tomas Manez, K. (2018). Advances in Bidirectional DC-DC Converters for Future Energy Systems. Technical University of Denmark.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Kevin Tomas Manez

# Advances in Bidirectional dc-dc Converters for Future Energy Systems

Ph.D. Dissertation, August 2018

Kevin Tomas Manez

# Advances in Bidirectional dc-dc Converters for Future Energy Systems

Ph.D. Dissertation, August 2018

### Advances in Bidirectional dc-dc Converters for Future Energy Systems

### **Author:**

Kevin Tomas Manez

**Supervisors:**

Zhe Zhang — DTU Elektro, Electronics Group Ziwei Ouyang — DTU Elektro, Electronics Group

Department of Electrical Engineering Electronics Group Technical University of Denmark Elektrovej building 325 DK-2800 Kgs. Lyngby Denmark

www.ele.elektro.dtu.dk

Tel: (+45) 45 25 38 00 Fax: (+45) 45 88 01 17 E-mail: hw@elektro.dtu.dk

Release date:  $31^{\rm th}$  August 2018

Category: 1 (public) Edition: First

Comments: This thesis is submitted in partial fulfillment of the requirements for

obtaining the PhD degree at the Technical University of Denmark.

Rights: © Kevin Tomas Manez, 2018

# Preface and Acknowledgment

This thesis is submitted in partial fulfilment of the requirements for obtaining Ph.D. degree at Technical University of Denmark. The research has been carried out at the Electronics group in the Electronic Department from September 2015 to August 2018 under the supervision of associate prof. Zhe Zhang and associate prof. Ziwei Ouyang.

The Ph.D. project entitled "Advances in Bidirectional dc-dc Converter for Future Energy Systems" is founded by the Danish Energy Technology Development and Demonstration Programme (EUDP).

My special thanks and deep appreciation to:

- My supervisors Zhe Zhang and Ziwei Ouyang, who gave me the opportunity to conduct the Ph.D. project. My deepest gratitude to Zhe Zhang, for his support and consistent encouragement that helped me finish this project and the endless talks and discussions.

- Prof. Michael A.E. Andersen, for being there when I needed support, and for valuable discussions and advise.

- To all who guided me through the elaboration of this thesis and helped reviewing it. To Zhe Zhang, Ziwei Ouyang, Martijn Duraij, Yasser Nour, Christian K. Lumby, Ahmed Ammar and Pere Llimos.

- All my colleagues at DTU Elektro for their help, support and constructive discussions, and of course, for the shared funny moments. My special gratitude to Henriette for making our group something more than a working place and for her endless support in any kind of matter; and to Hans-Christian for continuously improving our labs, his hard work and being always ready to give a hand.

- My deepest gratitude to all who made the difference, shared good and special moments, provide of help and advise without any hesitation and have always been there to support each other when we most needed it. To Yasser, Pere, Maria, Alexander, Ahmed, Gabriel and Yudi.

- To my family in Copenhagen. To the ones that left and the ones that still remain. All this would not have been possible without you. To Sepehr, Julio, Marcos, Jose, Martijn, Sergi, Hugo and Mpizos.

- To Maria. Thank you for your endless support in all my decisions, for your encouragement and for always believing in me.

- To my mother, Sussanna, my father, Jaume, and my sister Judith, for the unconditional love and encouragement. You are the pillars of my life, you made me feel proud of myself, you raised me to be the person I am today. I will never be able to thank you enough.

- And last but not least, a special gratitude to Denmark, that offered me the best

weather ever recorded during the period I was locked in the office writing this

thesis.

The contemporary electricity grid is in the midst of a transformation in which decentralization of energy production is playing a key role. Spurred by the environmental concerns of traditional energy sources and the costs reduction of photovoltaic energy and energy storage systems (ESSs), energy decentralization is disrupting traditional models of energy generation. In addition, vehicle-to-grid technology has been presented as an opportunity to optimize the grid utilization. Considering that photovoltaic energy, energy storage systems and electrical vehicles operate in dc, the electricity network is following a trend of moving towards dc distribution in the form of multiple microgrids. Accordingly, technological advances that allow a simplified and flexible interconnection of microgrids with high energy efficiency are key enablers for the electricity grid transformation. In this regards, high efficiency power electronics interconnecting microgrids and integrating energy storage systems, constitute a main pillar for the development of microgrids and reaching high penetration of renewable energy sources.

The state-of-the-art technologies in electrical power conversion are trending towards the utilization of dc solid-state transformers (SST) as interlinking converters between dc grids. Among the different power converter topologies implemented as SSTs, the series-resonant converter (SRC) has been extensively used, thanks to its load regulation characteristics in open-loop together and its soft-switching conditions for wide power ranges.

This Ph.D. dissertation is divided into two parts. In the first part, the investigation of two-port and three-port SRCs in open-loop operation for dc SST applications is carried out and presented. The study focuses on the design considerations of distributed resonant tanks to improve the load regulations characteristics in open-loop operation at a fixed switching frequency and duty cycle. On this subject, the design criteria to operate multi-port SRCs in soft-switching at input and output ports is overviewed. The resonance frequency matching can pose a challenge in multi-port SRCs with distributed resonant tanks. Therefore, a resonance frequency matching process is proposed to address this issue. This methodology allows to remove the resonant inductors and solely use the stray inductances and leakage inductance of the multi-winding transformer as the inductive component of the resonant tank. As a result, the efficiency and power density of the converter can be highly increased. The SRC tends to have large rootsquare-mean (rms) currents due to the sinusoidal waveform of the resonant currents and the circulating energy required to achieve zero-voltage switching. So the conduction losses are usually high. The minimization of circulating energy by an optimal selection of dead-time and magnetizing inductance is also analysed. In this regard, wide bandgap semiconductors, which are widely known for their benefits in reduced switching loss, have a direct impact on the circulating energies. This introduces additional advantages into the SRC which have also been investigated. Some of these advantages are the reduction of conduction losses and turn-off losses.

In the second part of this PhD dissertation, different power converters configurations to integrate energy storage systems into the dc microgrid are investigated. Each of the converters presented aim to solve different challenges in the integration of ESSs. Firstly, a dual-active-bridge (DAB) derived topology for high voltage gain operation is

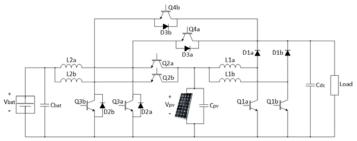

illustrated. The proposed topology features voltage and current stresses reduction as well as an additional degree of freedom to improve the DAB controllability. Secondly, a power conversion system which achieves a large reduction of the power processed by the dc-dc converter is presented. This solution focuses on the rearrangement of the dc-dc converter connection with the dc bus and the ESS. With this configuration, the system efficiency and power density can be largely increased, while the fabrication costs can be potentially reduced. Finally, a three port converter to integrate photovoltaic modules and the ESS into the microgrid is proposed. The converter is derived from conventional buck and boost topologies, hence its implementation is simple. High efficiency can be easily achieved since single energy conversion stages are required to transfer power between different ports.

## Resumé

Det nuværende elforsyningsnet er under forandring, hvori decentralisering af energiproduktion spiller en væsentlig rolle. Ansporet af bekymringer for miljømæssige konsekvenser ved traditionelle energikilder samt den reducerende prisudvikling på markederne for solcelleenergi og energilagring er decentraliseringen ved at omvælte traditionelle modeller for energiproduktion. Ydermere er køretøj-til-hjem/køretøj-til-elnet teknologi blevet præsenteret som en mulighed for at optimere udnyttelsen af elnettet. Med tanke på at solcelleenergi, energilagringssystemer og elektriske køretøjer opererer ved dc, har elnettets udvikling tendens til at bevæges mod dc distribution i form af flere mikronet. Tilsvarende er den teknologiske udvikling, som muliggør en simple og fleksibel forbindelse mellem mikronet med høj nyttevirkning, i centrum af elnettets transformation. Effektelektronik med høj nyttevirkning ved forbindelse mellem mikronet og integration af energilagringssystemer spiller i den forbindelse en central rolle for udviklingen af mikronet og anvendelsen af vedvarende energikilder.

State-of-the-art teknologier indenfor energiomformning bevæger sig mod anvendelse af dc solid-state transformere (SST) som bindeled mellem dc net. Blandt de forskellige topologier for effektomformere implementeret som SST er serie-resonans omformeren (SRO) blevet ekstensivt anvendt grundet dens belastningsregulerings karakteristika ved åben sløjfe operation samt dens soft-switching betingelser for store effektområder.

Denne ph.d.-afhandling er inddelt i to dele. Den første del omhandler en undersøgelse af to-port og tre-port SROer i åben sløjfe til de SST-anvendelser. Studiet fokuserer på overvejelser i forbindelse med design af distribuerede resonanstanke for at opnå høj belastningsregulerings karakteristika ved åben sløjfe operation med fast skiftefrekvens og duty cycle. Herunder gennemgås designkriteriet for at operere multi-port SROer i soft-switching ved indgangs- og udgangs-port. Tilpasning af resonansfrekvensen kan være en udfordring i multi-port SROer med distribuerede resonanstanke. Derfor foreslås en metode for tilpasning af resonansfrekvens til at adressere dette problem. Metoden tillader at resonansspolerne udelades til fordel for blot at benytte parasitisk induktans fra ledningsføring samt læk-induktans fra den flervundne transformer som den induktive komponent af resonanstanken. Som resultat heraf kan omformerens nyttevirkning og effekttæthed forøges betydeligt. SROen har normalvis store root-mean-square (rms) strømme grundet den sinusformede kurve på resonansstrømmene og den cirkulerende energi, som er nødvendig for at opnå zero-voltage switching. Derfor er ledetabene sædvanligvis høje. Muligheder for at minimere den cirkulerende energi undersøges ved at analysere optimale valg af dead-time og magnetiseringsinduktans. Herved konstateres det, at Gallium Nitrid (GaN) komponenter, som er velkendt for deres fordelagtigt lave skiftetab, har direkte indflydelse på de cirkulerende energier. Dette introducerer yderligere fordele ved SROen, hvilket også er blevet undersøgt. Disse fordele er blandt andet reduktion af (1) ledetab, (2) magnetiske viklingstab og (3) ESR tab for resonanskondensatoren.

I anden del af denne ph.d.-afhandling undersøges forskellige effektomformer konfigurationer til integration af energilagringssystemer i dc mikronettet. Hver af de præsenterede omformere forsøger at løse forskellige udfordringer ved integrationen af energilagringssystemer. Først illustreres en dual-active-bridge (DAB) afledt topologi til høj spændingsforstærkning. Den foreslåede topologi har fordel af nedsatte spændings- og strømbelastning foruden en yderligere frihedsgrad til at forbedre DABens kontrollérbarhed. Dernæst præsenteres et system til effektomformning, der opnår stor reduktion af den effekt, som dc-dc omformeren behandler. Denne løsning fokuserer på en omordning af dc-dc omformerens forbindelse med dc-busen og energilagringssystemet. Med denne konfiguration kan systemets nyttevirkning og effekttæthed forøges væsentligt, mens fabrikationsomkostninger potentielt kan reduceres. Endeligt foreslås en tre-port omformer til at integrere solcellemoduler og energilagringssystemer i mikronettet. Omformeren er afledt fra konventionelle buck og boost topologier, hvorfor dens implementering er simpel. Høj nyttevirkning kan nemt opnås, eftersom enkeltstående energiomformningstrin er nødvendige to at flytte effekt mellem de forskellige porte.

# Contents

| Pı            | eface       | e and . | Acknowledgement                                | i    |

|---------------|-------------|---------|------------------------------------------------|------|

| $\mathbf{A}$  | bstra       | ct      |                                                | i    |

| R             | esum        | é       |                                                | iv   |

| $\mathbf{Li}$ | st of       | Figure  | es                                             | x    |

| Li            | ${f st}$ of | Tables  | S                                              | xiii |

| 1             | Intr        | oducti  | ion                                            | 1    |

|               | 1.1         | Backg   | round                                          | 1    |

|               | 1.2         | Projec  | et objectives                                  | 2    |

|               | 1.3         | Disser  | tation scope                                   | 2    |

|               | 1.4         | Thesis  | s structure                                    | 3    |

| 2             | Stat        | e-of-tl | he-art                                         | 5    |

|               | 2.1         | Future  | e energy systems                               | 5    |

|               |             | 2.1.1   | Energy storage systems                         | 7    |

|               | 2.2         | Dc-dc   | power converters for the future energy systems | 9    |

|               |             | 2.2.1   | Power converters for dc SST applications       | 12   |

|               |             | 2.2.2   | Power converters for ESSs                      | 14   |

| 3             | Seri        | es Res  | sonant Converter Dc Transformer                | 17   |

|               | 3.1         | System  | m description                                  | 17   |

|               | 3.2         | Opera   | ting principle of the SRC dc transformer       | 20   |

|               |             | 3.2.1   | SRC operating regions                          | 20   |

|               |             | 3.2.2   | Steady-state operation                         | 22   |

|               | 3.3         | Design  | n considerations of the SRC dc transformer     | 23   |

|               |             | 3.3.1   | Zero-Voltage Switching                         | 23   |

|               |             | 3.3.2   | Inductive operation                            | 24   |

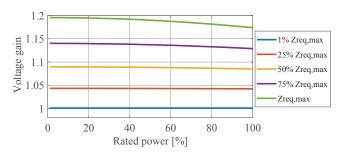

|               |             | 3.3.3   | Inherited load regulation characteristics      | 27   |

|               |             | 3.3.4   | Resonance frequency matching                   | 29   |

|              | 3.4    | Design               | a optimization for high efficiency operation                            | 33         |

|--------------|--------|----------------------|-------------------------------------------------------------------------|------------|

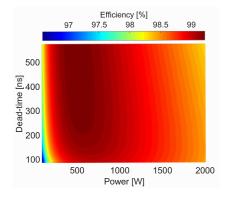

|              |        | 3.4.1                | Dead-time contribution to losses                                        | 34         |

|              |        | 3.4.2                | SRC performance improvements with GaN FETs                              | 36         |

|              |        | 3.4.3                | Transformer design                                                      | 37         |

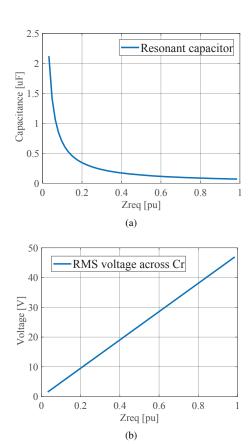

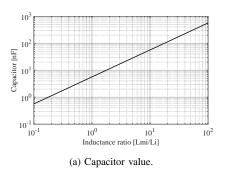

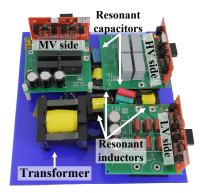

|              |        | 3.4.4                | Resonant capacitors                                                     | 42         |

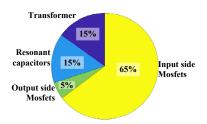

|              |        | 3.4.5                | Efficiency analysis                                                     | 42         |

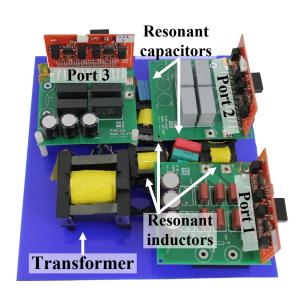

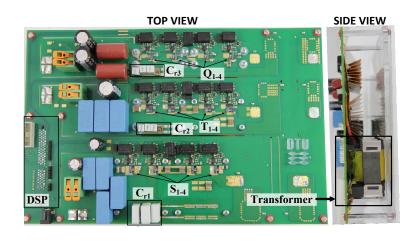

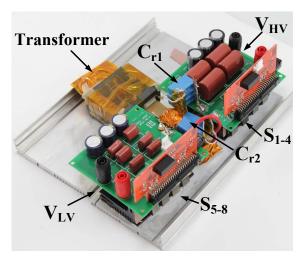

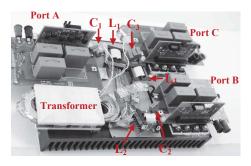

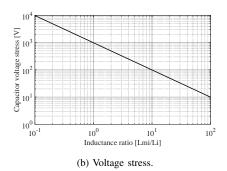

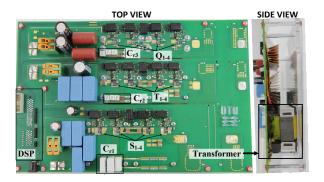

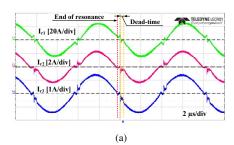

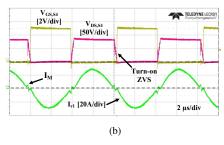

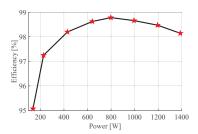

|              | 3.5    | Exper                | imental prototypes                                                      | 43         |

|              |        | 3.5.1                | Prototypes summary                                                      | 44         |

| 4            | Adv    | vances               | in Power Electronics for Energy Storage Systems                         | 49         |

|              | 4.1    |                      | lly Paralleled Dual Active Bridge Converter with Dual Phase-Shift       |            |

|              |        | Contr                |                                                                         | 49         |

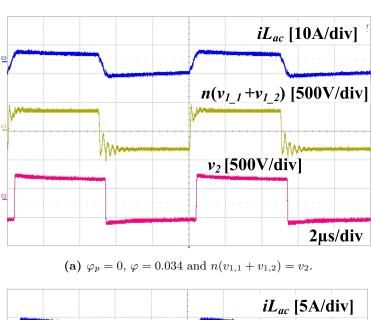

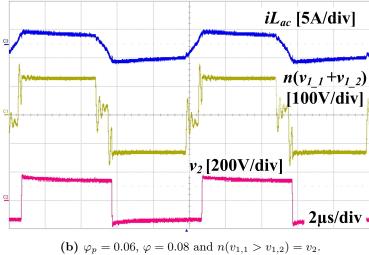

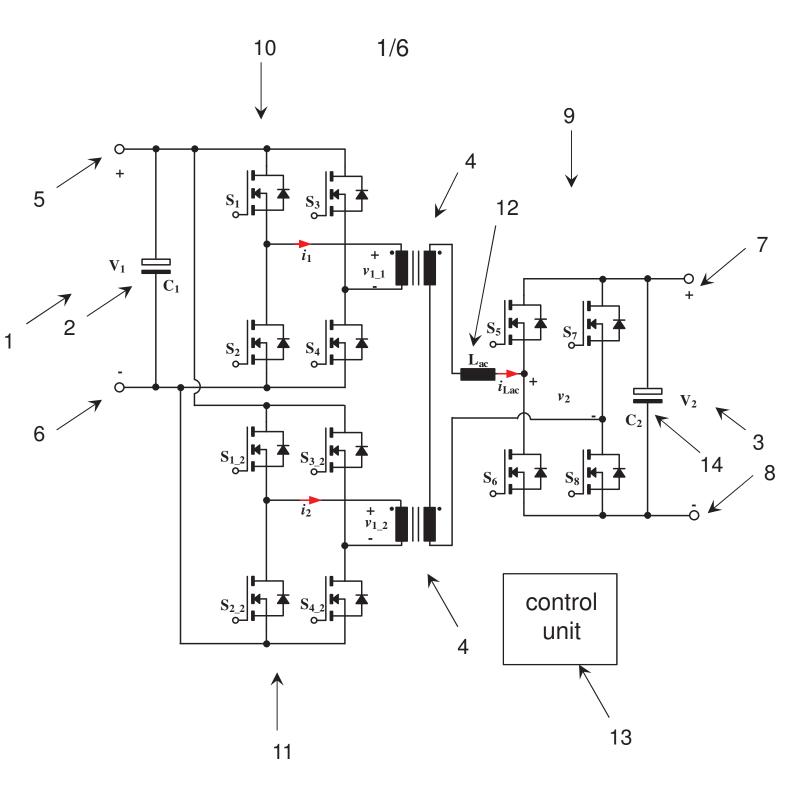

|              |        | 4.1.1                | Topology and operating principle                                        | 50         |

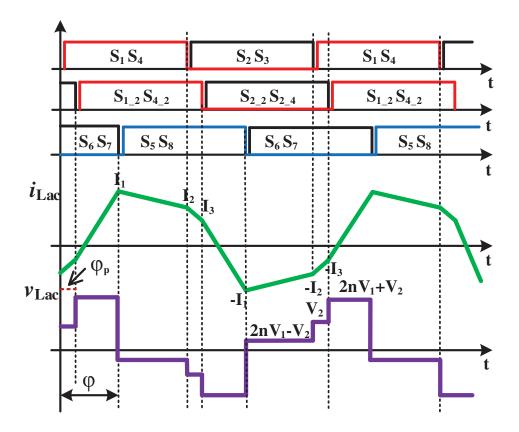

|              |        | 4.1.2                | Design considerations                                                   | 54         |

|              |        | 4.1.3                | Experimental prototype                                                  | 55         |

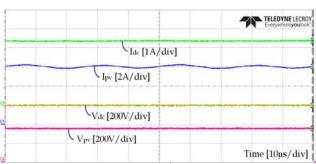

|              | 4.2    | Series               | -connected power conversion system                                      | 56         |

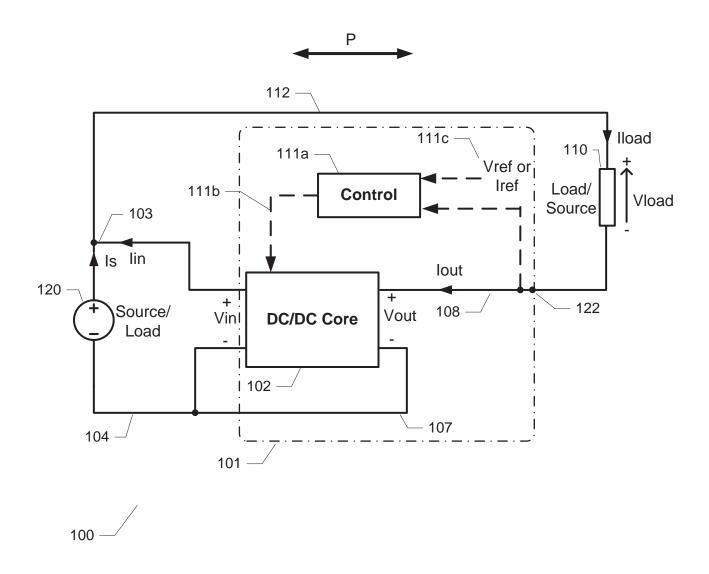

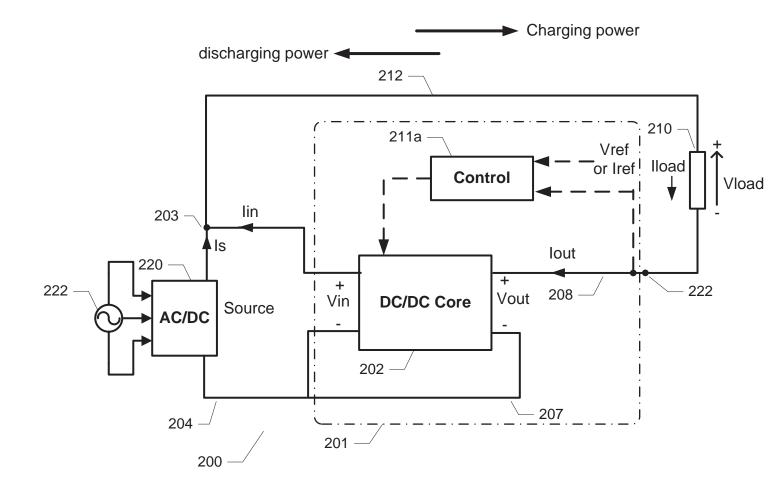

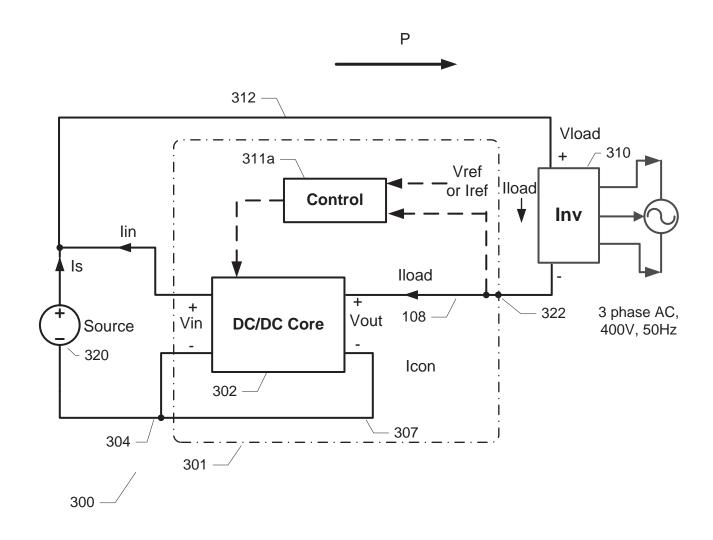

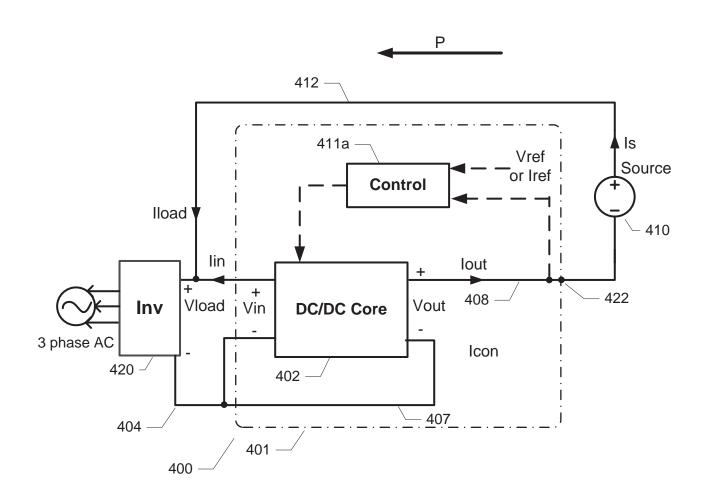

|              |        | 4.2.1                | System analysis                                                         | 56         |

|              |        | 4.2.2                | Design considerations                                                   | 59         |

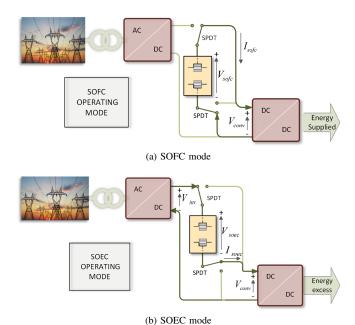

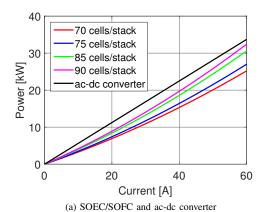

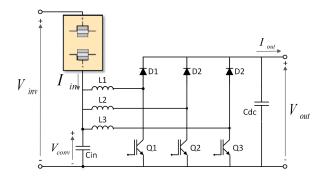

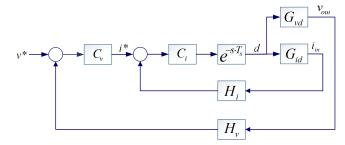

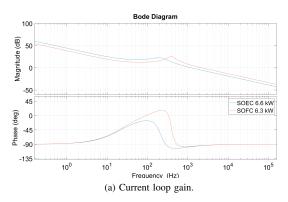

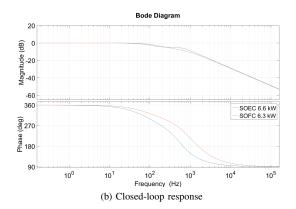

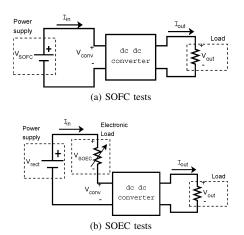

|              |        | 4.2.3                | Dynamic power conversion system for SOEC/SOFC $\ \ldots \ \ldots$ .     | 61         |

|              |        | 4.2.4                | Series connected PCS with DAB converter for high voltage gain           | 61         |

|              |        | 4.2.5                | Series connected PCS with an isolated boost dc-dc converter $$          | 62         |

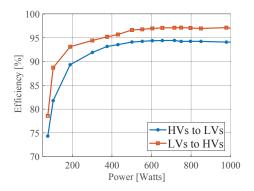

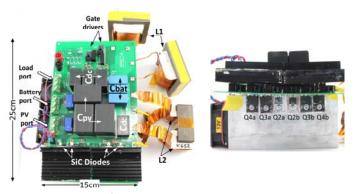

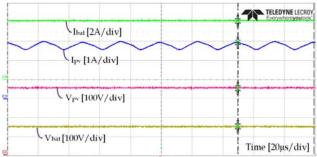

|              | 4.3    |                      | -port dc-dc converter for PV-Battery systems with direct energy section | 64         |

|              |        | 4.3.1                | System analysis                                                         | 64         |

|              |        | 4.3.2                | Topology and operating principle                                        | 65         |

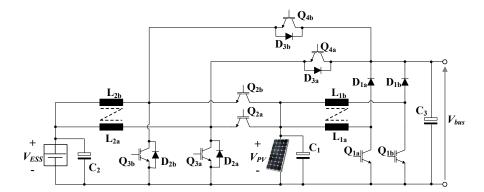

|              |        | 4.3.3                | Modularity by interleaving                                              | 67         |

| 5            | Con    | nclusio              | n                                                                       | 69         |

| 6            | Fut    | ure wo               | ork                                                                     | 73         |

|              | 6.1    | Projec               | et proposals for the SRC dc Transformer                                 | 73         |

|              | 6.2    | Projec               | et proposals for the Partially Paralleled DAB                           | 73         |

| B            | ibliog | graphy               |                                                                         | <b>7</b> 5 |

| $\mathbf{A}$ | ppen   | $\operatorname{dix}$ |                                                                         | 83         |

J High efficiency non-isolated three port DC-DC converter for PV-

229

battery systems

# List of Figures

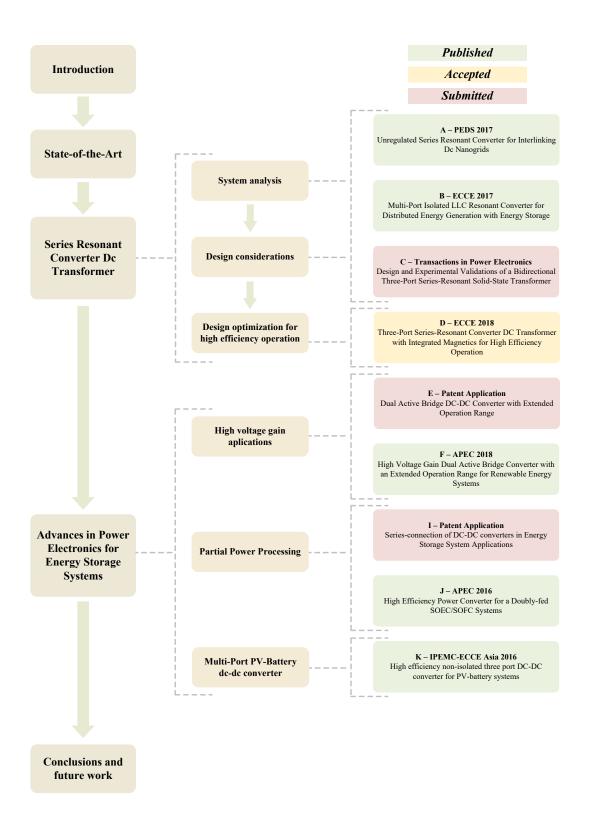

| 1.1  | Thesis outline                                                                                                                                                                                                                                                                                                                                         | 4  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

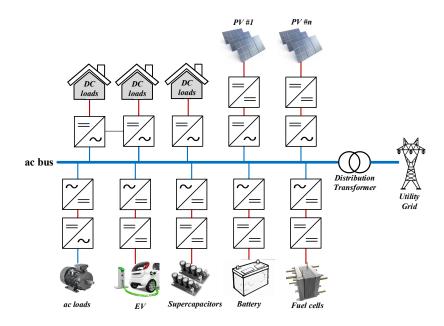

| 2.1  | Building block of ac microgrid system                                                                                                                                                                                                                                                                                                                  | 6  |

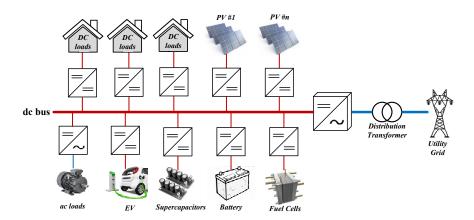

| 2.2  | Building block of dc microgrid system                                                                                                                                                                                                                                                                                                                  | 6  |

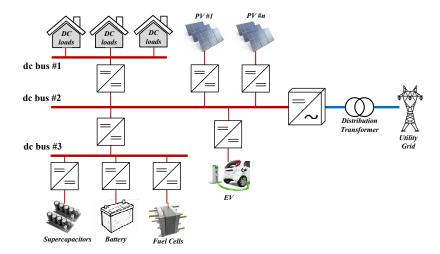

| 2.3  | Building block of multiple dc microgrid system                                                                                                                                                                                                                                                                                                         | 7  |

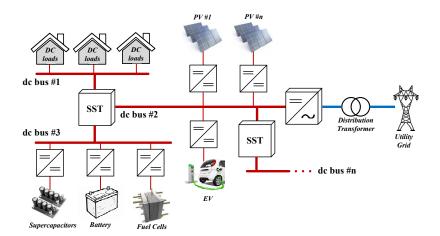

| 2.4  | Building block of dc solid-state transformer enabled dc microgrid                                                                                                                                                                                                                                                                                      | 8  |

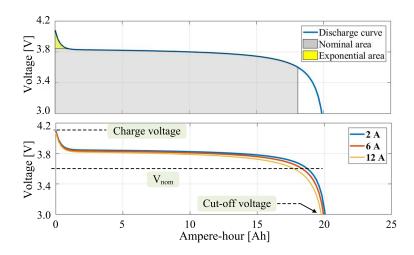

| 2.5  | Discharge curve of a lithium-ion battery. Datsheet: [1]                                                                                                                                                                                                                                                                                                | 9  |

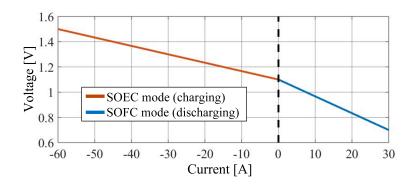

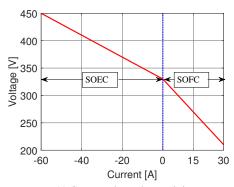

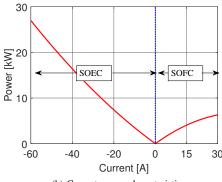

| 2.6  | Typical current-voltage characteristics of a SOEC/SOFC single cell. $$ . $$ .                                                                                                                                                                                                                                                                          | 10 |

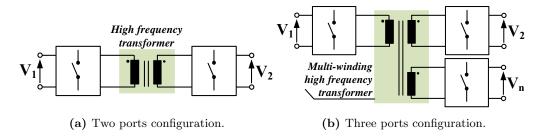

| 2.7  | High voltage gain and multiple ports integration through high frequency transformer                                                                                                                                                                                                                                                                    | 10 |

| 2.8  | Topology of the series resonant converter                                                                                                                                                                                                                                                                                                              | 12 |

| 2.9  | Topology of the dual active bridge                                                                                                                                                                                                                                                                                                                     | 12 |

| 2.10 | Common dc gain characteristics for the DAB and SRC in terms of typical control parameter, i.e. phase angle for the DAB and switching frequency for the SRC, for different output power                                                                                                                                                                 | 13 |

| 3.1  | Structure of Chapter 3                                                                                                                                                                                                                                                                                                                                 | 18 |

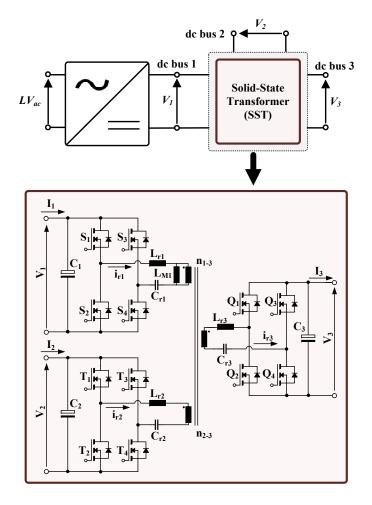

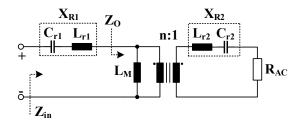

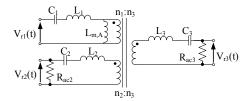

| 3.2  | Series Resonant Converter for dc SST applications                                                                                                                                                                                                                                                                                                      | 19 |

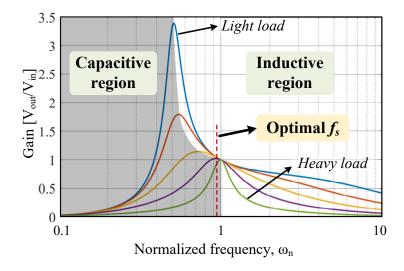

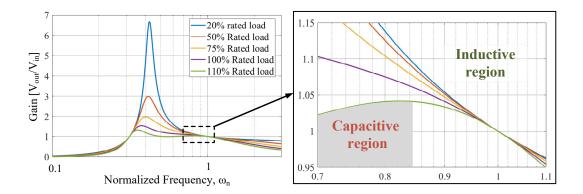

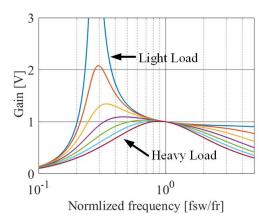

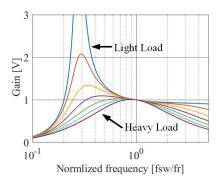

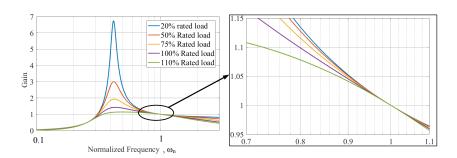

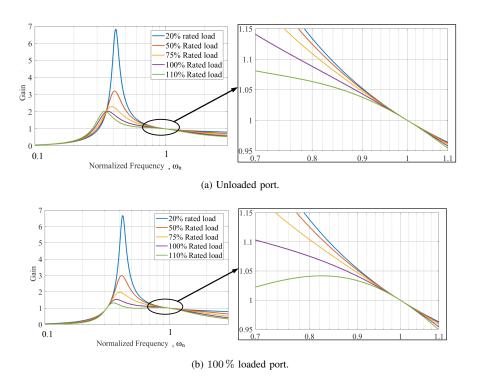

| 3.3  | Dc gain curves of a resonant tank versus normalized frequency $\omega_n$                                                                                                                                                                                                                                                                               | 21 |

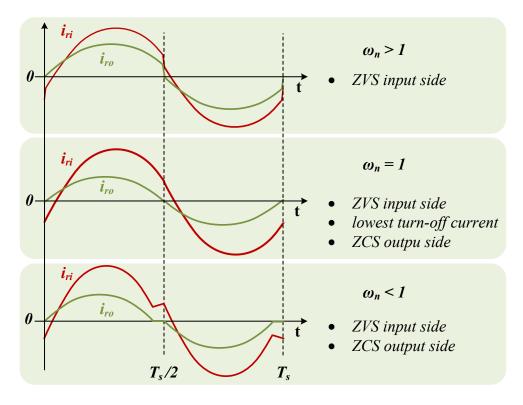

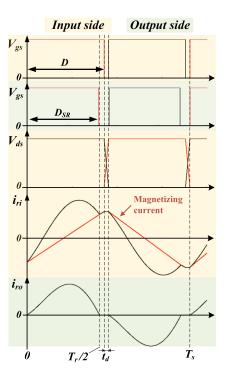

| 3.4  | Typical resonant current waveforms at the input side bridge $i_{ri}$ and output side bridge $i_{ro}$ when operating within the inductive region above the resonance frequency $\omega_n > 1$ , at the resonance frequency $\omega_n = 1$ and below the resonance frequency $\omega_n < 1$                                                              | 21 |

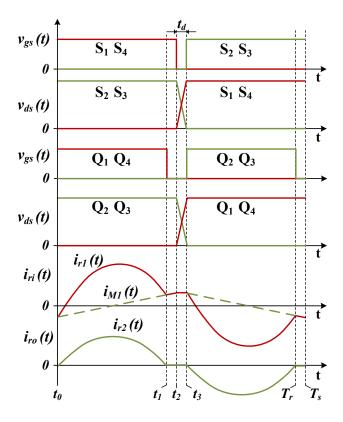

| 3.5  | Steady-state waveforms of the SRC when operating slightly below the resonance frequency                                                                                                                                                                                                                                                                | 23 |

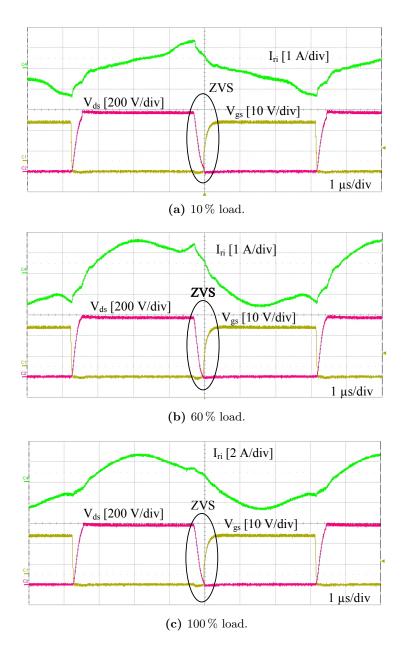

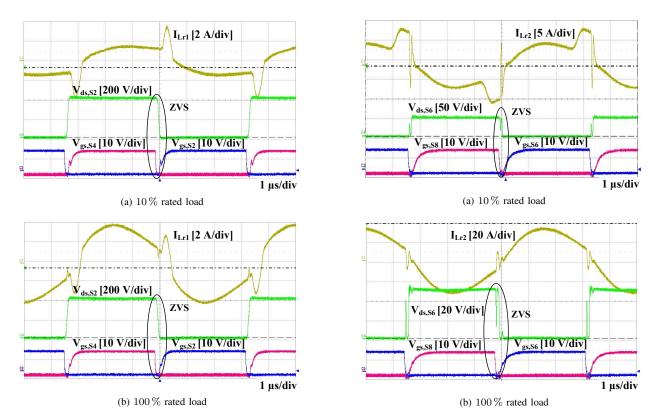

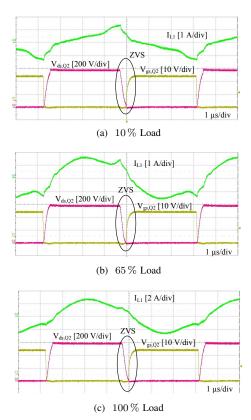

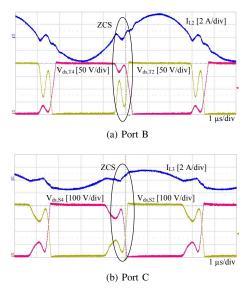

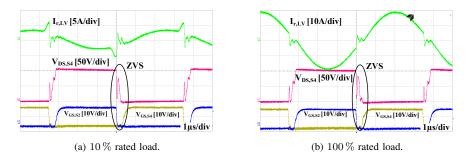

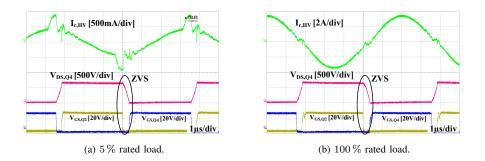

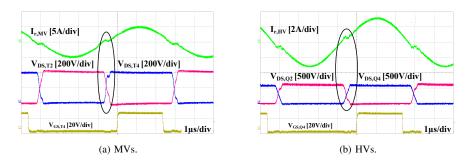

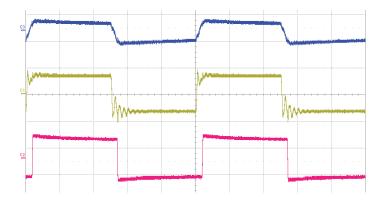

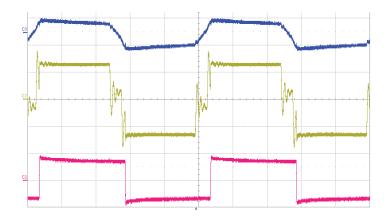

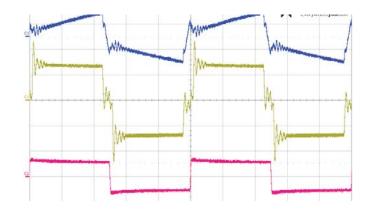

| 3.6  | Experimental results of ZVS operation for different output power                                                                                                                                                                                                                                                                                       | 25 |

| 3.7  | Dc gain characteristics of an arbitrary resonant tank when $m=m_{min}.$ .                                                                                                                                                                                                                                                                              | 26 |

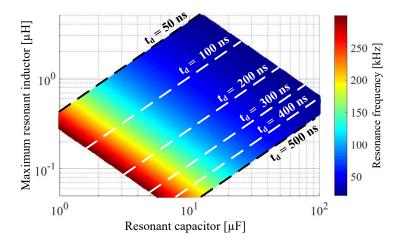

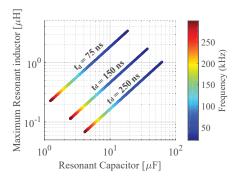

| 3.8  | Resonant tank components size $L_{ri,max}$ and $C_{ri}$ for $m = m_{min}$ versus $t_d$ and $\omega_r$                                                                                                                                                                                                                                                  | 27 |

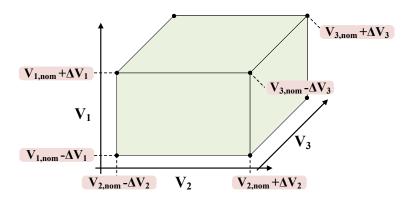

| 3.9  | Voltage limits of a microgrid with three dc buses                                                                                                                                                                                                                                                                                                      | 28 |

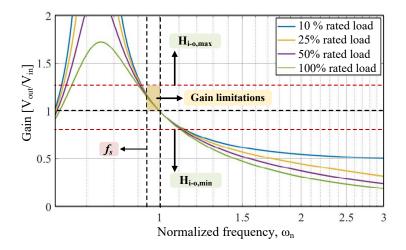

| 3.10 | Gain limitations of the SRC. The figure illustrates the SRC dc gain in terms of $\omega_n$ for different loads. The converter switching frequency is marked with $f_s$ . The gain limitations according to the design specifications are $H_{i-o,min}$ , $H_{i-o,max}$ , $H_{o-i,min}$ and $H_{o-i,max}$ , where $i$ and $o$ refers to the port number | 28 |

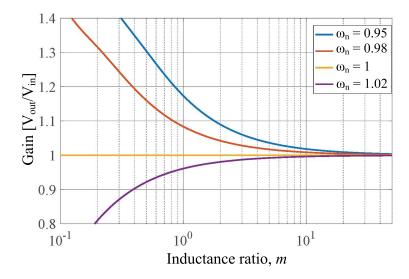

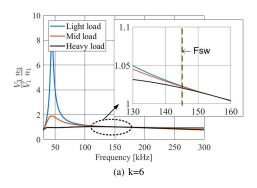

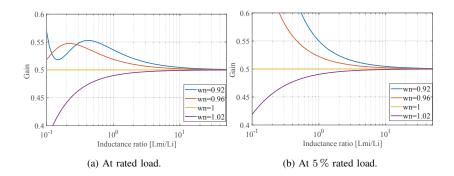

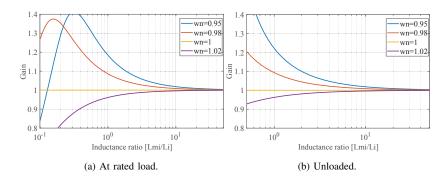

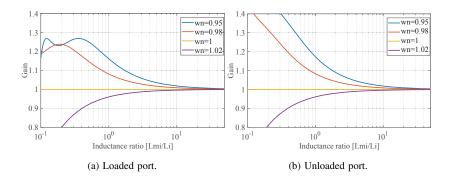

| 3.11 | Dc gain characteristics vs inductance ratio $m$ for different $\omega_n$                                                                                                                                                                                                                                                                                                | 29 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

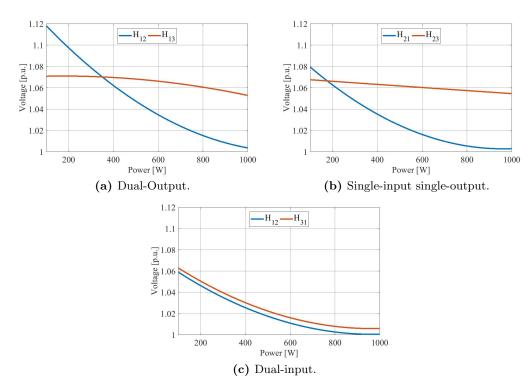

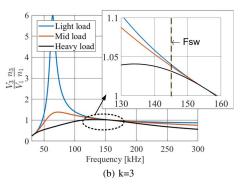

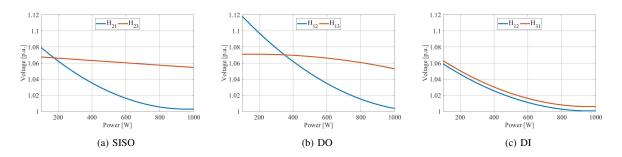

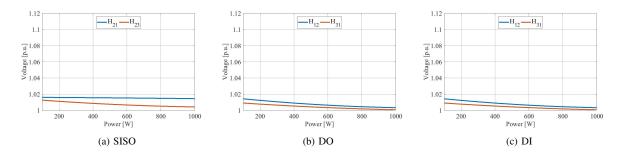

| 3.12 | Experimental results of the steady-state dc gain of a 3P-SRC for a resonant tank with $m=20.$                                                                                                                                                                                                                                                                           | 30 |

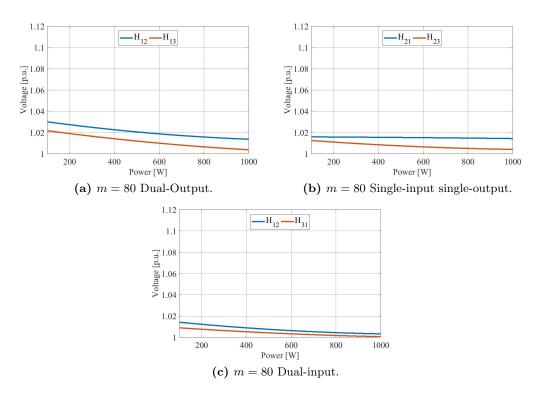

| 3.13 | Experimental results of the steady-state dc gain of a 3P-SRC for a resonant tank with $m=80.$                                                                                                                                                                                                                                                                           | 30 |

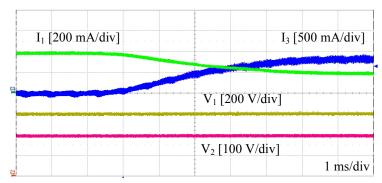

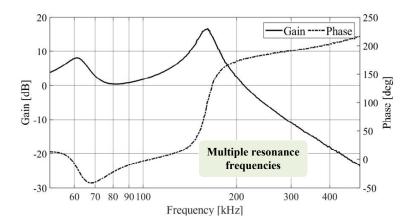

| 3.14 | Voltage regulation with power fluctuations of the 3P-SRC. Port $3(V_3)$ is regulated at 400 V, while ports 1 $(V_1)$ and 2 $(V_2)$ are the unregulated ports. Inputs: Port 1 and 2; Output: Port 3                                                                                                                                                                      | 31 |

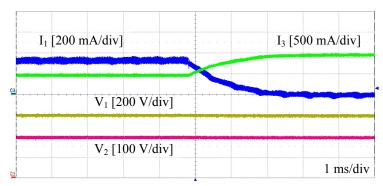

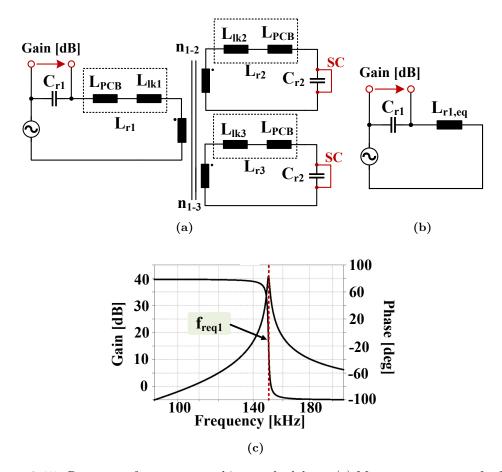

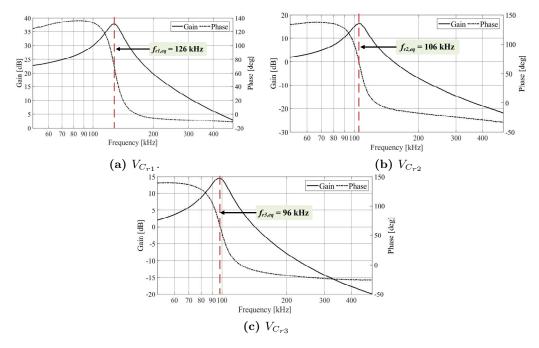

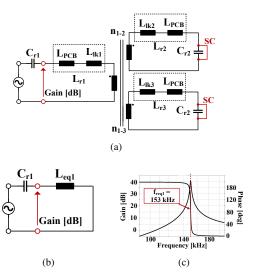

| 3.15 | Resonance frequency matching methodology. (a) Measurement set-up for Port-1: the gain after the resonant capacitor is measured with a Bode analyser. (b) Equivalent circuit of the measurement set-up, where $L_{r1,eq}$ is the overall resonant inductance seen from Port-1. (c) Measured bode plot and equivalent resonance frequency due to $C_{r1}$ and $L_{r,eq1}$ | 32 |

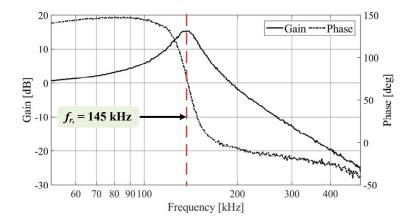

| 3.16 | Voltage gain measurement before compensation with all the resonant tank components                                                                                                                                                                                                                                                                                      | 33 |

| 3.17 | Voltage gain measurement and equivalent resonance frequency from each port                                                                                                                                                                                                                                                                                              | 33 |

| 3.18 | Voltage gain measurement and resonance frequency after compensation with all the resonant tank components                                                                                                                                                                                                                                                               | 34 |

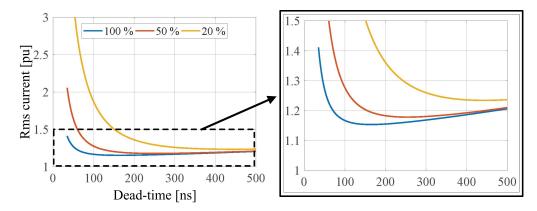

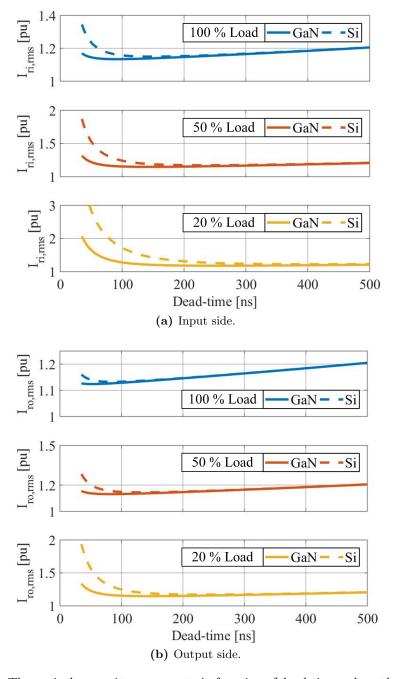

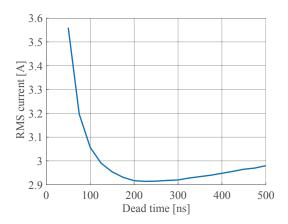

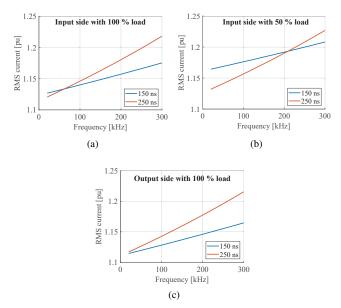

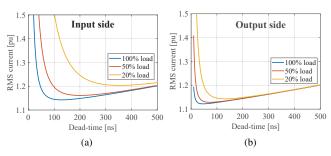

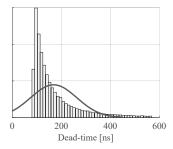

| 3.19 | Theoretical per-unit rms currents versus dead-time under different load conditions, where the rms current base value is the dc port current $I.$                                                                                                                                                                                                                        | 35 |

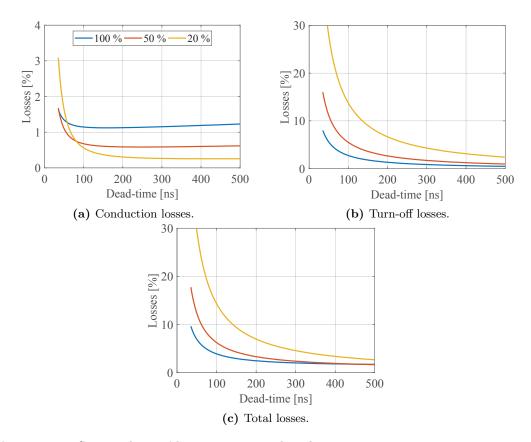

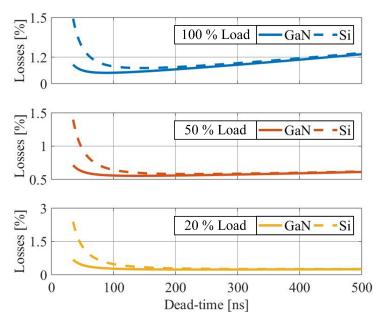

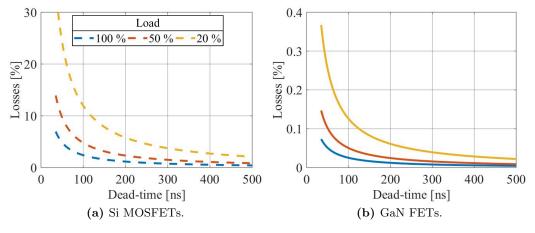

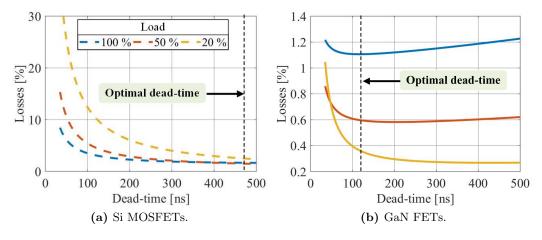

| 3.20 | Semiconductors' losses proportional to the power output in percentage versus $t_d$ for different output power                                                                                                                                                                                                                                                           | 36 |

| 3.21 | Theoretical per-unit rms currents in function of dead-time, where the rms current base value is the dc port current $I.$                                                                                                                                                                                                                                                | 38 |

| 3.22 | Conduction losses in function of dead-time                                                                                                                                                                                                                                                                                                                              | 39 |

| 3.23 | Switching losses in function of dead-time                                                                                                                                                                                                                                                                                                                               | 39 |

| 3.24 | Total semiconductors losses in function of dead-time                                                                                                                                                                                                                                                                                                                    | 39 |

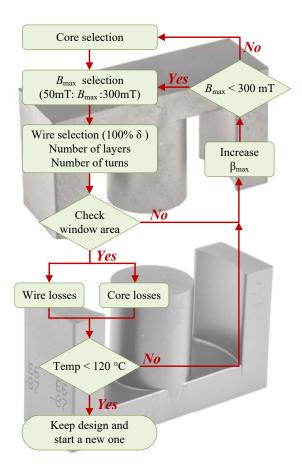

| 3.25 | Simplified flowchart of the algorithm used to design the optimized transformer                                                                                                                                                                                                                                                                                          | 40 |

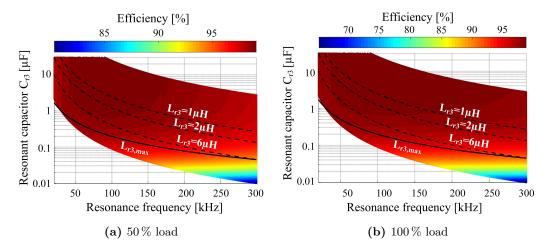

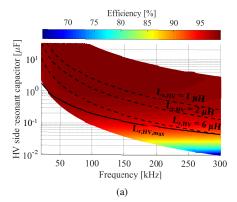

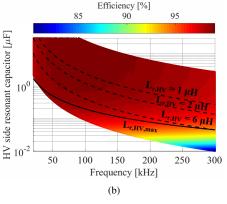

| 3.26 | Theoretical efficiency of 3P-SRC in terms of resonance frequency and resonant components size. Efficiency is calculated for dual-output mode with equal power sharing among ports                                                                                                                                                                                       | 43 |

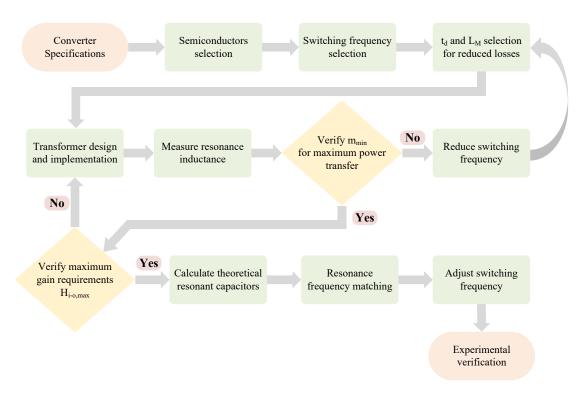

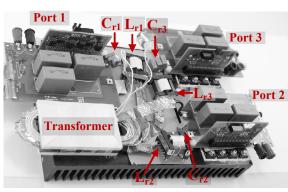

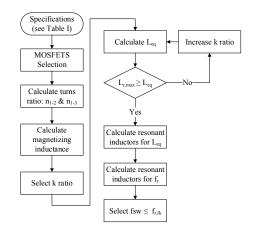

| 3.27 | Design flowchart when using integrated resonant inductors                                                                                                                                                                                                                                                                                                               | 44 |

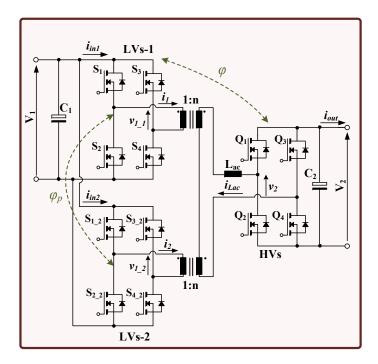

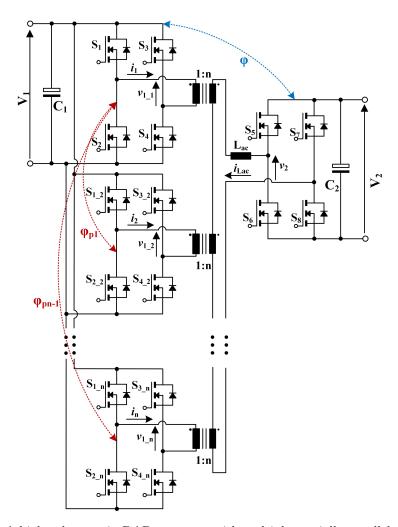

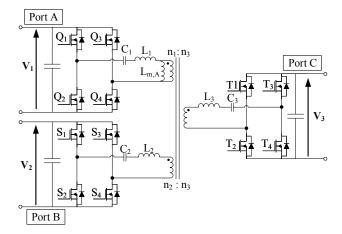

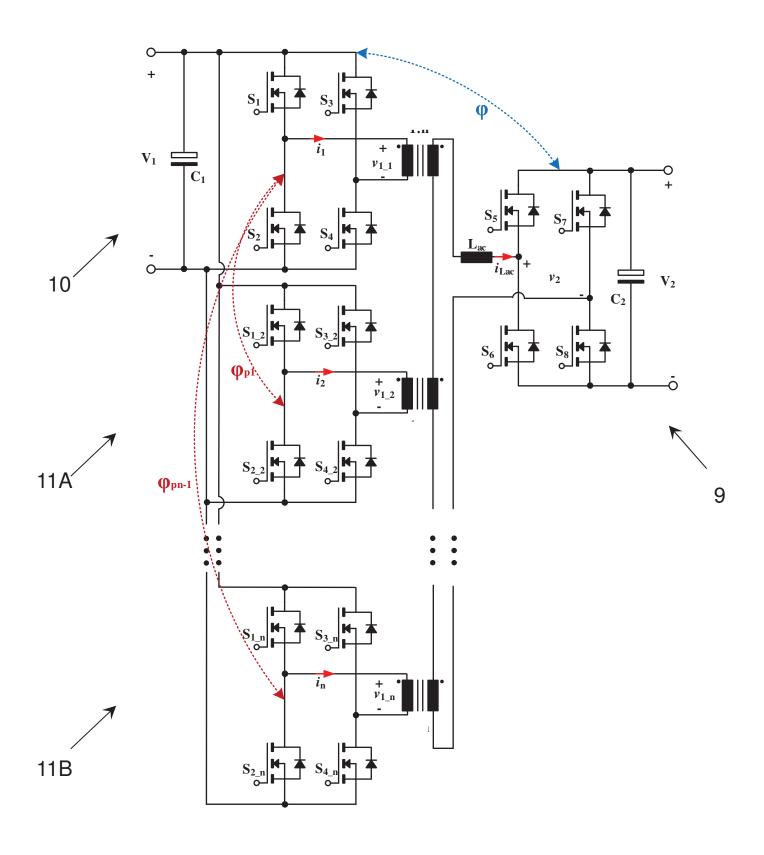

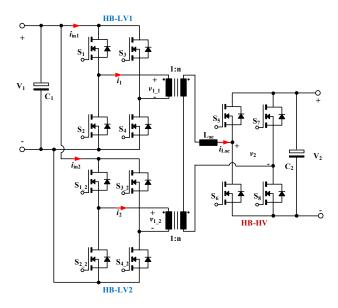

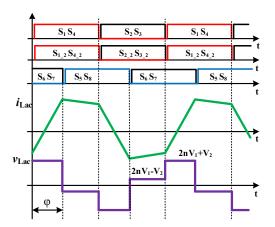

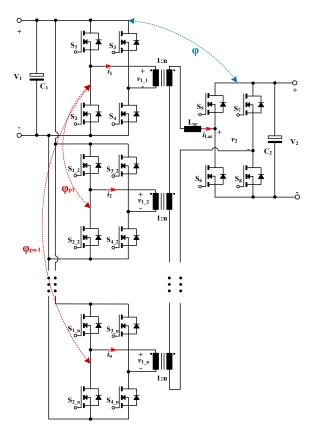

| 4.1  | Topology of the proposed P <sup>2</sup> DAB converter                                                                                                                                                                                                                                                                                                                   | 50 |

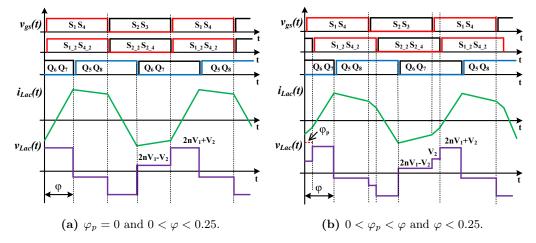

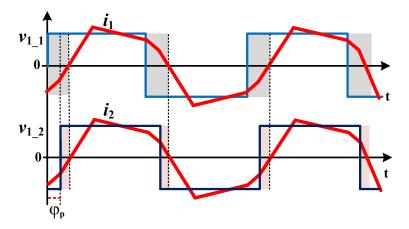

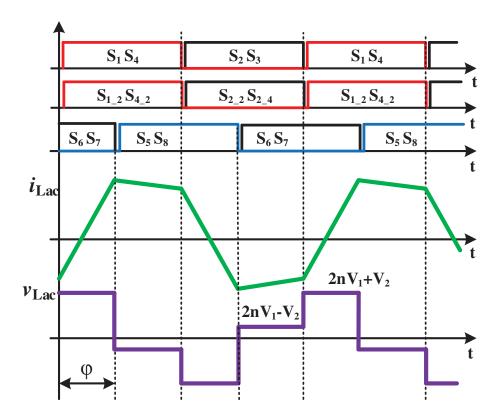

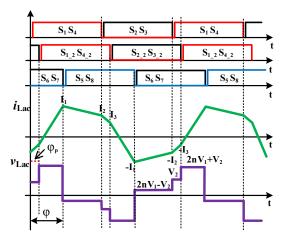

| 4.2  | Switching patterns of HB-LV1 $(S_1 - S_4)$ , HB-LV2 $(S_{1_2} - S_{4_2})$ and HB-HV $(Q_1 - Q_4)$ , ac inductor current $i_{Lac}$ and voltage $v_{Lac}$                                                                                                                                                                                                                 | 51 |

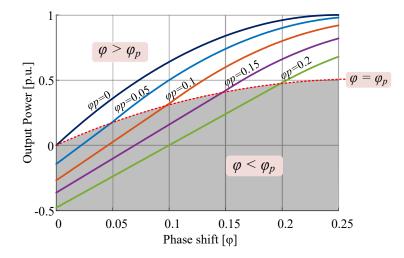

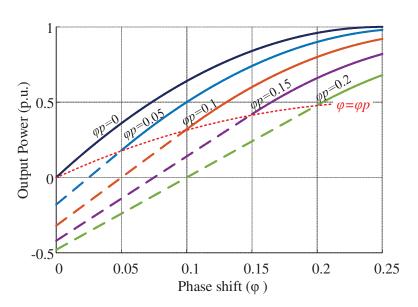

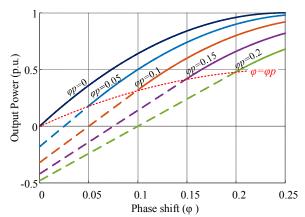

| 4.3  | Transferred power in terms of $\varphi$ and $\varphi_p$ , where the base unit is $nV_1V_2/4f_sL_{ac}$                                                                                                                                                                                                                                                                   | 52 |

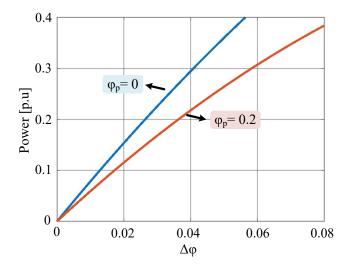

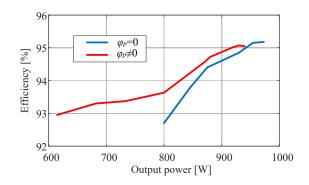

| 4.4  | Transferred power in terms of $\Delta \varphi$ for $\varphi_p = 0$ and $\varphi_p = 0.2$                                                                                               | 52 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

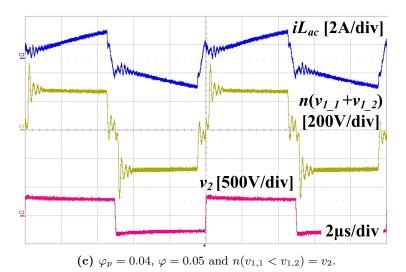

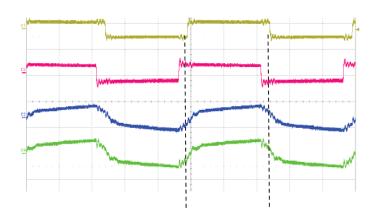

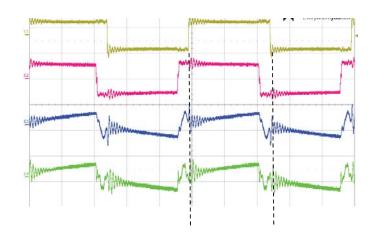

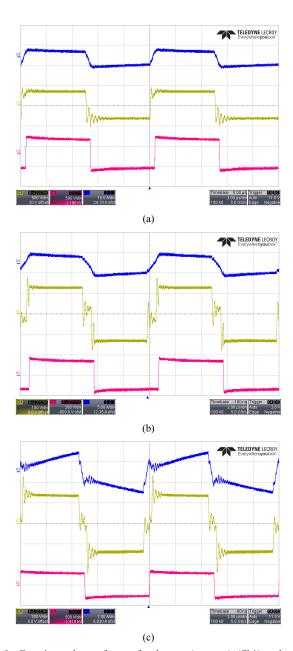

| 4.5  | Experimental waveforms of the reflected LVs voltage $n(v_{1,1}+v_{1,2})$ , voltage $v_2$ and ac inductor current $i_{Lac}$ with different phase shift angles $\varphi_p$ and $\varphi$ | 53 |

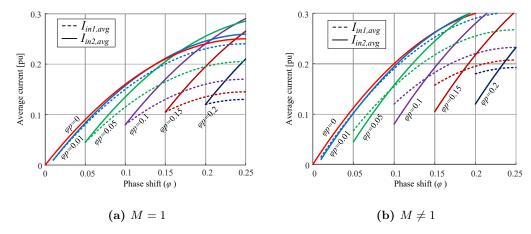

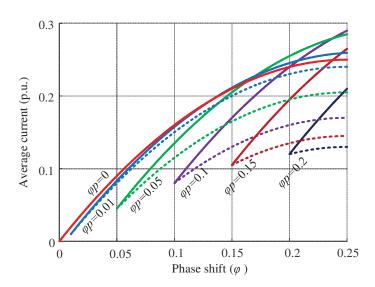

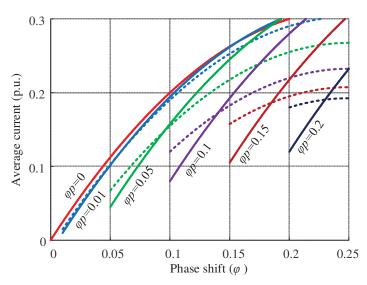

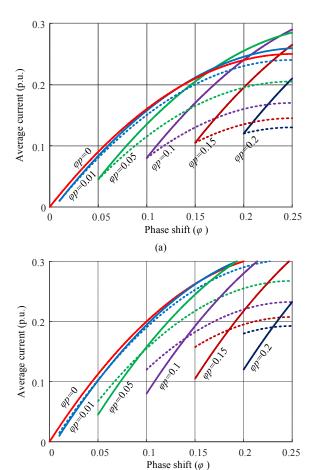

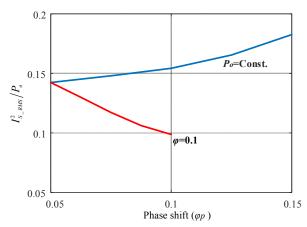

| 4.6  | Average input current $I_{in1,avg}$ and $I_{in2,avg}$ in terms of phase shift angle $\varphi$ and $\varphi_p$                                                                          | 55 |

| 4.7  | Ac voltage and current on the LVs of the $P^2DAB$ converter                                                                                                                            | 55 |

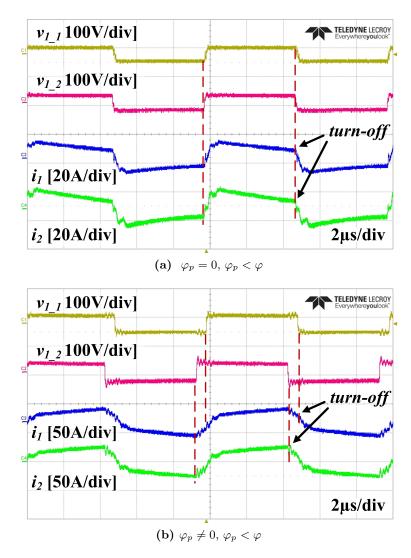

| 4.8  | Experimental waveforms of voltage $v_1$ , voltage $v_{12}$ , current $i_1$ and current $i_2$                                                                                           | 56 |

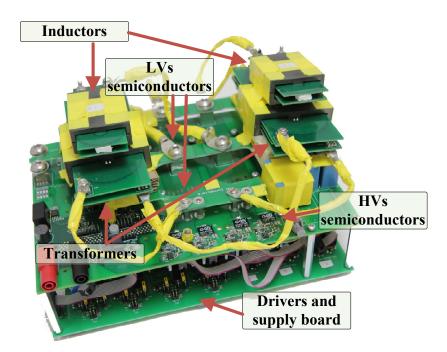

| 4.9  | Picture of the $P^2DAB$ converter prototype                                                                                                                                            | 57 |

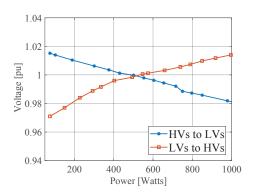

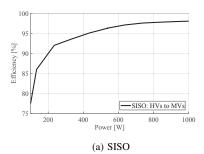

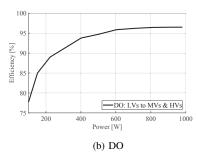

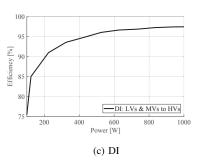

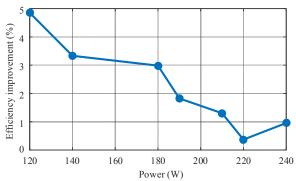

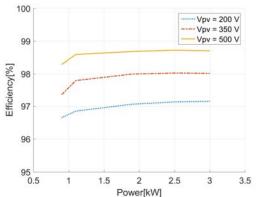

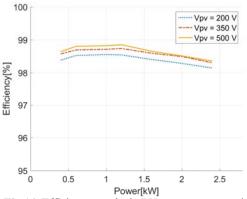

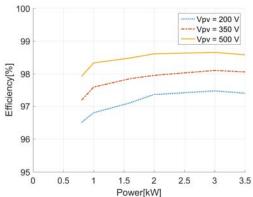

| 4.10 | Efficiency curves of the $P^2DAB$ converter prototype                                                                                                                                  | 57 |

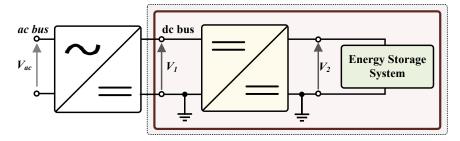

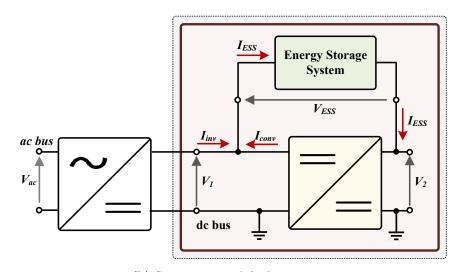

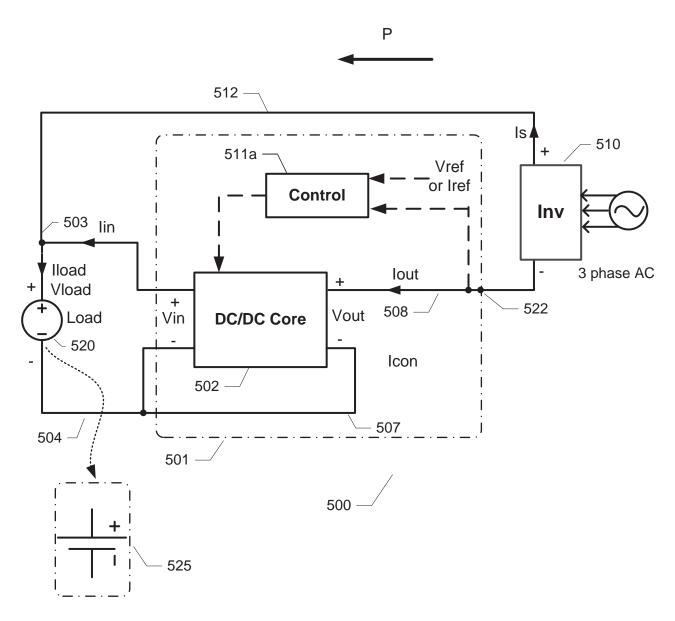

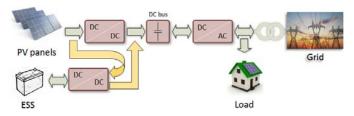

| 4.11 | Block diagram of a grid connected power conversion system for energy storage                                                                                                           | 58 |

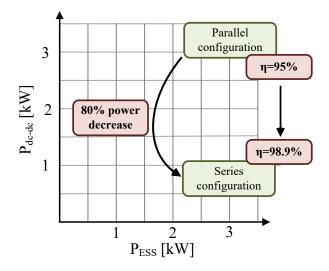

| 4.12 | Efficiency and power density improvements with the series connection power conversion system                                                                                           | 59 |

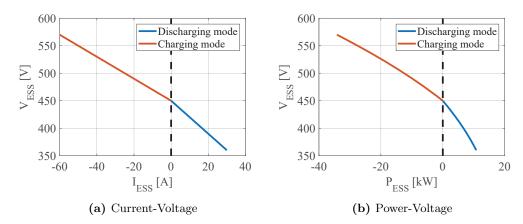

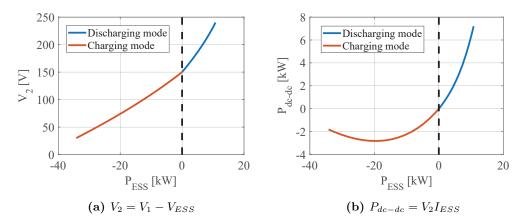

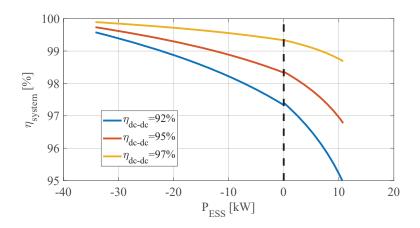

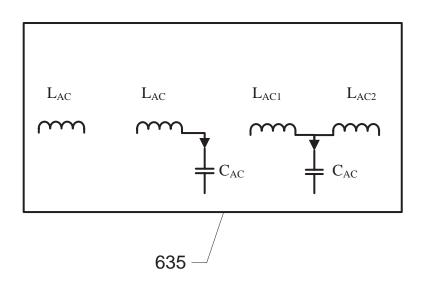

| 4.13 | Electrical characteristics of RFCs                                                                                                                                                     | 60 |

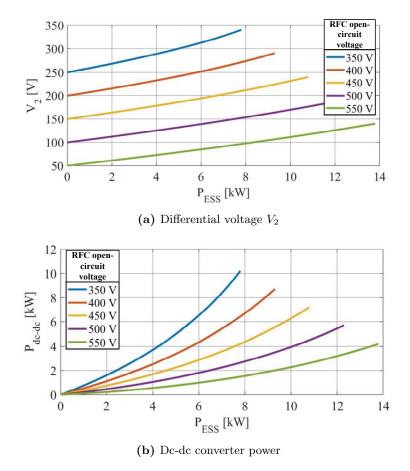

| 4.14 | Dc-dc converter voltage and power rating in function of ESS power. $$                                                                                                                  | 60 |

| 4.15 | Overall system efficiency for different $\eta_{dc-dc}$                                                                                                                                 | 60 |

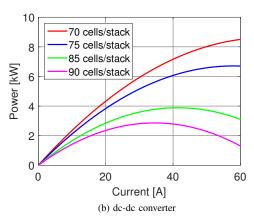

| 4.16 | Dc-dc converter specification for ESS with different voltage ratings of the ESS. The legend shows the open-circuit voltage of different ESS configurations                             | 61 |

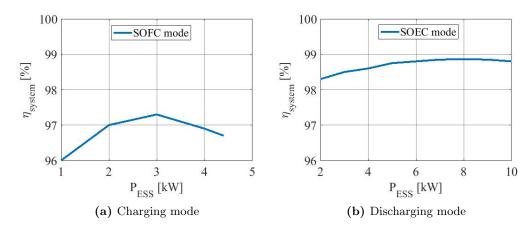

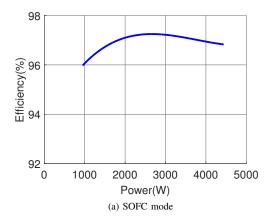

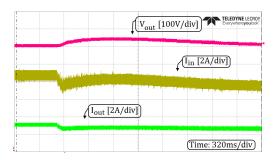

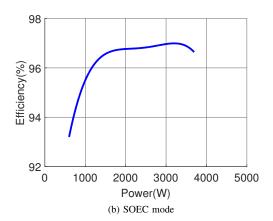

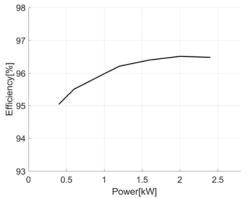

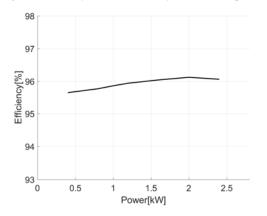

| 4.17 | Efficiency measurements of the dynamic conversion system in SOFC and SOEC mode                                                                                                         | 62 |

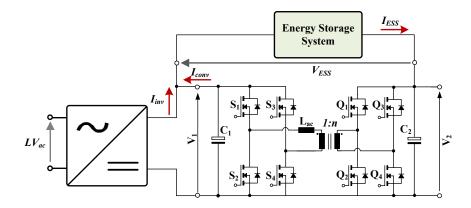

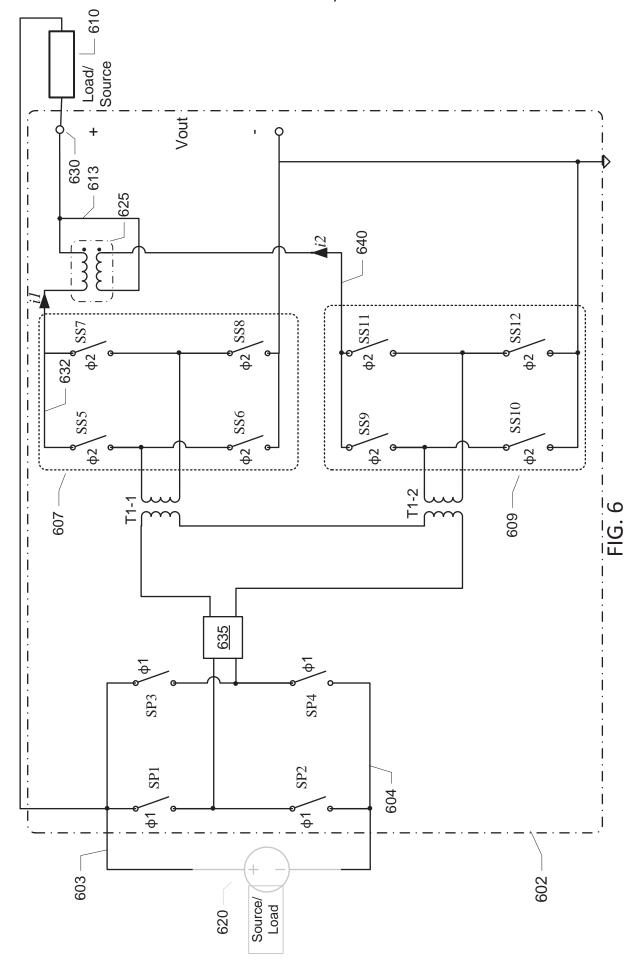

| 4.18 | Schematic of the S-PCS with a DAB converter                                                                                                                                            | 62 |

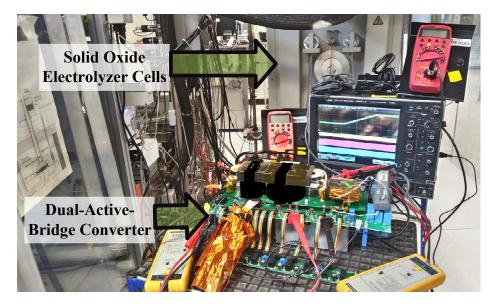

| 4.19 | Picture of the test site                                                                                                                                                               | 63 |

| 4.20 | I-V characteristics of the SOEC/SOFC tested                                                                                                                                            | 63 |

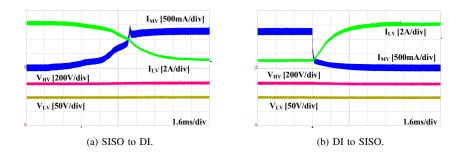

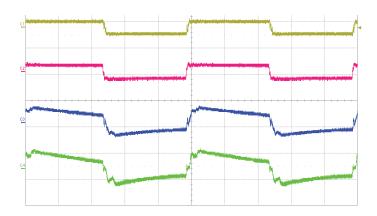

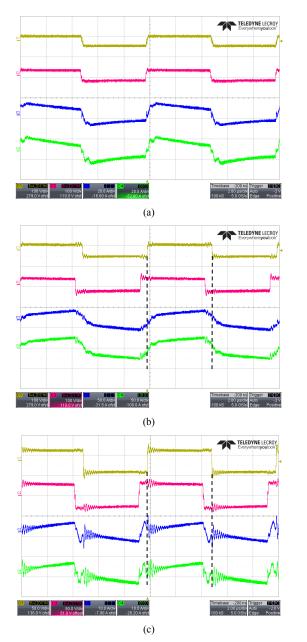

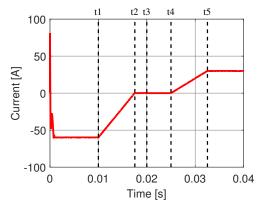

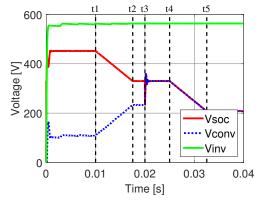

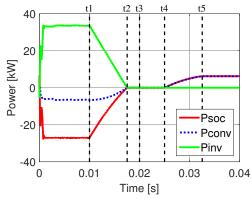

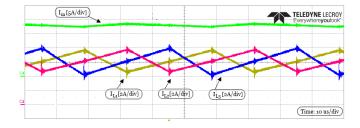

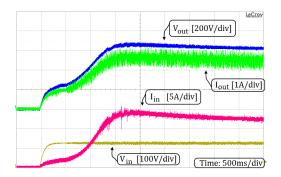

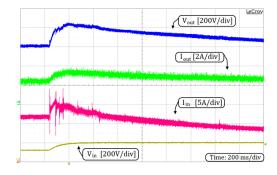

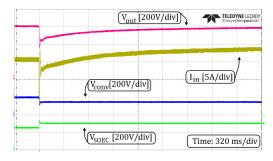

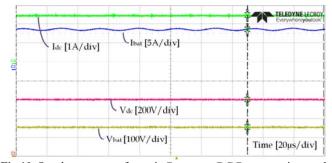

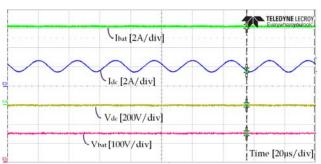

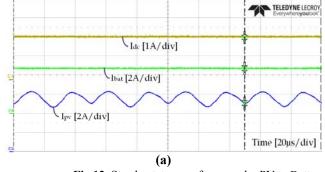

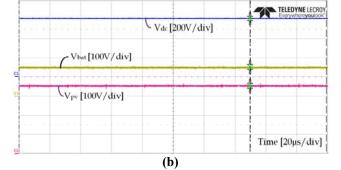

| 4.21 | Experimental waveforms of the series-connected DAB - RFC system                                                                                                                        | 64 |

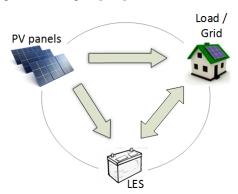

| 4.22 | Power flow of the three-port dc-dc converter for a PV-Battery system                                                                                                                   | 65 |

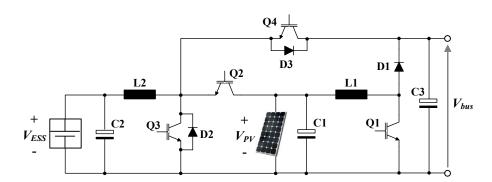

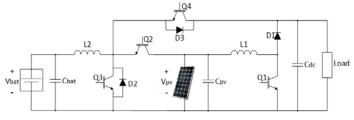

| 4.23 | Schematic of the three-port dc-dc converter                                                                                                                                            | 66 |

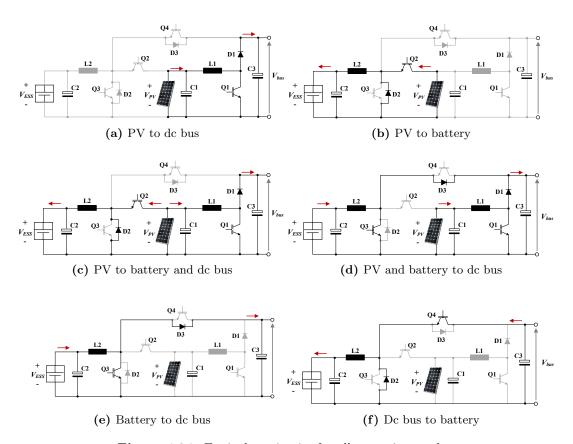

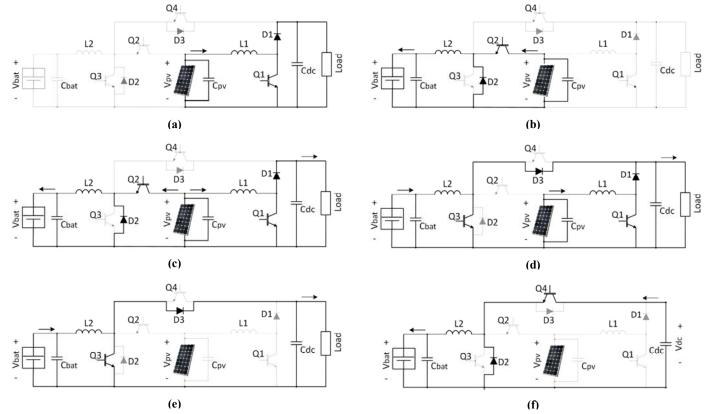

| 4.24 | Equivalent circuits for all operating modes                                                                                                                                            | 66 |

| 4.25 | Schematic of the two stages interleaved three-port dc-dc converter                                                                                                                     | 67 |

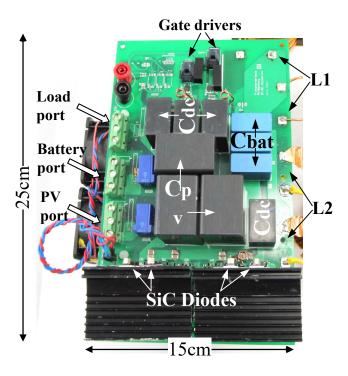

| 4.26 | Picture of the three port dc-dc converter prototype                                                                                                                                    | 68 |

| 4.27 | Picture of the coupled inductors                                                                                                                                                       | 68 |

| 6.1  | A high voltage gain DAB converter with multiple partially paralleled LV bridges.                                                                                                       | 74 |

# List of Tables

| 2.1 | Review of Solid State Transformers                         | 13 |

|-----|------------------------------------------------------------|----|

| 2.2 | Review of bidirectional dc-dc converters for ESSs          | 16 |

|     |                                                            |    |

| 3.1 | Specifications for the TP-SRC                              | 34 |

| 3.2 | Specifications of the Silicon devices used in the analysis | 35 |

| 3.3 | Specifications of the GaN devices used in the analysis     | 37 |

| 3.4 | Transformer specifications                                 | 42 |

|     |                                                            |    |

| 4.1 | Specifications for the $P^2DAB$ converter                  | 55 |

| 4.2 | Specifications for Lithium-ion batteries                   | 58 |

| 4.3 | Specifications for the three-port dc-dc converter          | 65 |

# Introduction

## 1.1 Background

We live in a world that runs on electricity. The flow of electrons shapes our daily lives in everything we produce and everything we do. Alternating current (ac) powers our grid, street-lights and freezers, while direct current (dc) supplies our everyday devices such as phones, laptops and and cars. Ac and dc have cooperated for decades, but now the world needs more power than ever before [2, 3] and with smaller environmental impact. In a "more dc world", we will be able to connect more efficiently renewable energy sources (RES) in extremely remote locations, wherever the wind is blowing, water flowing or sun is shinning [4, 5]. We will be able to capture the energy of the sun and transfer it from Sahara to Scandinavia or anywhere in between [5]. Electrical vehicles can be pulled up to any corner street and charge up as fast as it takes to have a coffee break [6]. Extremely energy consumers data centres will be capable to store and serve billions of web pages using less resources and space [7, 8]. Buildings and homes will be have the capacity to feed dc power directly and efficiently to the devices that run on dc power like appliances, computers and lightening [9-11]. Moving towards a distribution system with higher grade of dc where each kilowatt counts, we could live in a more efficient and reliable world while limiting the environmental impact.

In the last two decades, the integration of RES into our society has experienced an extraordinary development which is constantly progressing [2, 3]. Spurred by the costs decrease in photovoltaic (PV) panels and the high feed-in tariff, the decentralization of energy production has been advancing together with the development of RES. Besides the economic benefits for costumers and the environmental impact, distributed energy systems will grant the deferral of capital investment to maintain and upgrade grids to support load growth [5, 12]. As RES increase, the need for distributed storage will become essential. Without energy storage systems (ESS), when the production of electricity from RES exceeds the demand, negative pricing might occur and energy would be lost. ESSs adds flexibility to the system by balancing the energy production and the demand and thus, making a more effective use of the energy and preventing disruptive economics [12]. Moreover, through energy storage, additional services can be added to enhance the distribution system reliability and flexibility such as, frequency regulation, voltage support or backup power [13].

Thanks to the benefits of dc distribution and the tremendous increase of RESs and ESSs, future energy systems in residential applications are envisioned to evolve into multiple dc and ac microgrids [10, 11, 14–16]. Power electronics are a key component to fuel the potential of this evolution. In fact, power converters are used to interconnect

2 Introduction

all the units that compose the electrical distribution grid, such as PV panels, batteries and loads. In addition, in dc distribution systems, power converters play the role of the core transformer in conventional ac distribution systems, wherein they operate as power conditioning and as power routers among the multiple dc grids. The research areas in power electronics which will reinforce the electricity grid transformation range from improvements in interoperability of systems, manufacturability, reliability, modularity and scalability, reduction of costs and high efficiency power converters [5, 12, 17, 18]

### 1.2 Project objectives

High efficiency power electronics are a driving force for the disruption of dc distribution and empower the high penetration of RES and ESSs. Therefore, the aim of this project is to identify current limitations and challenges within power conversion in dc distribution and ESSs and to envision the opportunities that this challenges bring to the development of alternative high efficiency power conversion systems. Accordingly, the main objectives and/or contributions of this PhD project are summarized below:

- To identify the trends of power electronics for residential dc distribution and/or microgrids.

- To investigate the utilization of unregulated solid-state transformers as power routers between microgrids.

- To demonstrate high efficiency bidirectional dc-dc converters to interconnct multiple dc grids. The aim is to achieve dc-dc conversion efficiency of 99 % over wide power ranges.

- To identify the challenges for high efficiency power converters in energy storage applications.

- To investigate and propose alternative solutions for high efficiency power converters in energy storage applications. The aim is to achieve dc-dc conversion above 98% in high voltage gain and wide voltage range operation.

## 1.3 Dissertation scope

This dissertation summarizes and presents a more complete overview of the results achieved throughout the Ph.D. project entitled Advances in Bidirectional dc-dc Converter for Future Energy Systems which has been carried out from September 2015 until August 2018. The research carried out during this Ph.D. project has been presented or submitted in the form of peer review conference and journal papers as well as patent applications. These publications and patent applications constitute an essential part of this dissertation and hence, are included in the Appendices. In addition, App.A presents the list of publications, where joint publications, which has not been included in the Appendices, are also listed.

### 1.4 Thesis structure

The structure and content of the PhD dissertation are illustrated with Fig.1.1.

Chapter 1: Covers the background and motivation of this PhD project, describes the scope of the thesis and the project objectives and gives an overview of the content of the thesis.

Chapter 2: Describes the state-of-the art in microgrids and ESSs, and the review of high efficiency dc-dc converters for these applications.

Chapter 3: Presents the series-resonant converter in open-loop operation as a solidstate transformer to interconnect dc distribution systems. The design considerations for the specific application and design improvements for high efficiency operation are investigated.

Chapter 4: Presents three different solutions aiming to overcome different challenges of the energy storage systems.

Chapter 5: Summarizes the research and results obtained, conclude on the work presented in this thesis and describes the future work.

4 Introduction

$\textbf{Figure 1.1:} \ \, \textbf{Thesis outline}. \\$

# State-of-the-art

### 2.1 Future energy systems

In the recent years our society has been immersed in environmental issues of centralized traditional energy sources. In addition, the ageing of current distributions system and the growing demand of electrical energy have stressed this concerns. Even though the promising recent developments in energy decentralizations by means of renewable energy sources (RES) [2, 3], the increasing penetration of distributed energy sources into the traditional ac grid can cause additional problems such as voltage and frequency unstability [19, 20]. In order to solve these problems concepts such as "Microgrids" and "Smart grids" for the future distribution systems have been proposed. The microgrid concept was originally proposed in 2002 [21] and its operating principle was based on the principle of aggregating multiple micro-sources and loads into a single entity which can be interpreted as a single dispatch-able consumer and producer from the power systems perspective [13]. Nowadays, most of the microgrids are based on the traditional ac grid system as shown with Fig.2.1. However, large number of the units forming the microgrid generate dc voltages, e.g. photovoltaic (PV) panels, energy storage systems (ESSs) or electric vehicles (EV). These units require of dc-dc and dc-ac power converters to transfer or absorb power from the ac grid. These multiple power conversion stages increase the total energy consumption as well as reduces its reliability [10, 17]. More recently, microgrids systems based on a dc grid, as shown in Fig.2.2, have been proposed. Compared to the traditional ac grid, the dc grid can bring many advantages as (1) fewer power converters are required resulting in higher efficiency, higher power density and lower costs [7, 10, 22], (2) easier system integration, since issues related to the reactive power or grid synchronization are eliminated [8, 10], (3) higher efficiency in the power transmission, since there is no skin effect and ac losses [23] and (4) grid connected loads such as computers or lightning systems can be directly powered by the dc system [8, 14]. During the last decade, research on microgrids architectures has been established as a research topic by itself where the key features are control flexibility, robustness and reliability [13].

Conventionally, a microgrid structure with direct connection of the ESS to the dc bus has been the most popular. Direct connection of battery stacks to the dc bus results in very high system robustness due to the high capacitance of the ESS and the dynamic stability. On the other hand, the uncontollable voltage of the dc bus, which mostly depends of the battery state-of-charge, makes this system poorly flexible [13]. Interconnecting ESSs through power converters, allows an active regulation of the dc bus voltage and thus, flexibility of the system is largely increased [13, 22]. From this struc-

6 State-of-the-art

Figure 2.1: Building block of ac microgrid system.

Figure 2.2: Building block of dc microgrid system.

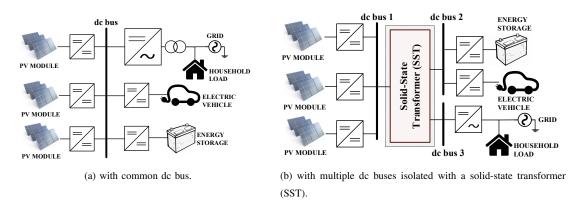

ture, multiple other architectures have been studied in the literature [8, 10, 13, 14, 24]. As isllustrated with Fig.2.3, microgrids in future energy saving buildings is envisioned to have multiple dc grids at different voltage levels for powering high voltage loads such as heating, ventilation or kitchen loads and low voltage loads such as computers or light-emitting diodes [8, 10, 14]. Although many efforts have been carried out to reach a consensus for standards on dc grids [25–30], the standardization is still one of the biggest barriers for the incursion of microgrids into the power system.

The smart grid and microgrid scenario with high penetration of RES is going to be further enhanced by ensuring a production, distribution and use of the energy as efficient as possible. In that terms, power electronics are being seriously considered as one of the key technologies that will empower the future energy systems at all levels of the electrical system. Using highly efficient power electronics in power generation, power transmission, power distribution and at end-user applications, can pave the way to the smart grid [12, 18, 31–33].

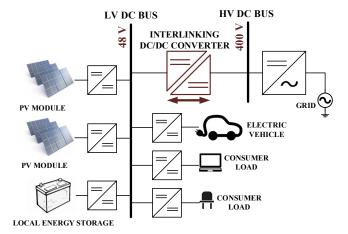

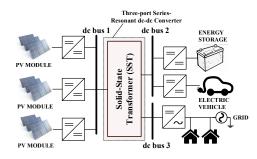

Figure 2.3: Building block of multiple dc microgrid system.

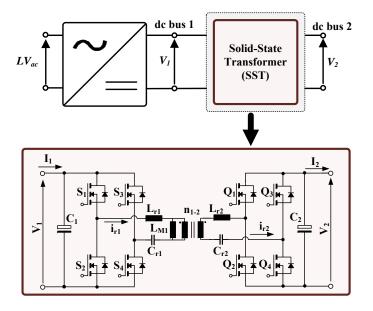

On this subject, during the last decade, a new power converter named solid-state transformer (SST) has caught much attention and been extensively studied for the distribution system [24]. Initially, the SST was proposed as a dc-dc converter with a high-frequency transformer to replace the utility grid line frequency transformer [24, 34]. Recently, the idea of a dc SST has also been proposed as an energy router in multi-bus dc microgrids as shown in Fig.2.4 [24, 35, 36]. Therefore, only single-stage conversion is needed to transfer power between the different dc grids.

In dc microgrid systems such as the one illustrated in Fig.2.4, the key components forming the dc cluster are summarized below:

- Renewable energy sources RES (PVs) and interfacing dc-dc converters.

- Energy storage systems ESSs (e.g. batteries and fuel cells).

- Interlinking converters (dc SSTs).

- Storage interfacing converters (bidirectional dc-dc converters).

#### 2.1.1 Energy storage systems

Another key element to enhance the smart grids irruption into the electrical grid is the integration of stationary storage systems. The uncontrollable and inherent characteristics of RES introduce additional issues with system stability, reliability and power quality [19, 20, 37]. ESSs provide an effective way of balancing power supply and consumption, in order to decouple energy generation from demand [31]. Moreover, ESSs can be used to address power quality issues and improve the system flexibility by providing ancillary services to the grid [38–41]. This makes the ESS indispensable in order to efficiently and reliably deliver sustainable, economic and secure electricity supply in the future distribution systems [38–41].

The main ESS for grid applications are summarized in [42, 43]:

8 State-of-the-art

Figure 2.4: Building block of dc solid-state transformer enabled dc microgrid.

- Batteries

- Regenerative fuel cells

- Pumped-hydro

- Flywheels

- Thermoelectric

- Super-capacitors

The selection of the ESS depends on the application and factors such as power and energy ratings, response time, weight and size and operating temperature [43, 44]. Reviews of ESSs for grid applications with RES can be found in [37, 43]. In residential applications, batteries are the most widely used ESS, where high energy-to-weight ratios are required [43]. On the other hand, regenerative fuel cells (RFC) represent an attractive alternative due to their high energy density and lower environmental disposal concerns [44, 45].

#### Batteries:

Batteries can be found in many types depending on its chemistry [46]. In residential and EV applications most of the ESSs are lead-acid or lithium-ion based battery systems. Typical nominal voltages of a single cell battery range between  $1.2\,\mathrm{V}$  to  $3.8\,\mathrm{V}$  [44, 46] depending on the chemistry. Therefore, battery suppliers provide battery packs with multiple number of cells stacked in series to achieve higher operating voltages and energy storage capacity. Typical nominal voltages of battery packs can be found in the low voltage range  $12\,\mathrm{V}\text{-}50\,\mathrm{V}$  [47] to higher voltage ranges  $350\,\mathrm{V}\text{-}550\,\mathrm{V}$  [48–50] depending on the application.

Although the electrical characteristics of batteries might differ with the technology used, typical discharge curves are similar to the one illustrated with Fig.2.5. The battery capacity or state-of-charge (SOC) determines the terminal voltage, which is usually flat and located around the nominal voltage  $V_{nom}$ . The nominal voltage is also dependent on other factors such as temperature or cycle-life. Typically, batteries are charged and discharged at a constant current until reaching the depth of discharge

Figure 2.5: Discharge curve of a lithium-ion battery. Datsheet:[1].

limits. When approaching the SOC superior and inferior limits, i.e. charge voltage and cut-off voltage respectively, constant voltage is applied to avoid any hazardous conditions such as battery overcharging or going beyond the cut-off voltage and charge voltage [38, 51]. Therefore, power converters in battery applications should operate in wide voltage ranges where its optimised operation should be around the battery nominal voltage.

#### Regenerative fuel cells:

Fuel cells are another kind of electrochemical device that uses a chemical reaction to produce electricity directly from the fuel. Typical example of a fuel cell technology is the hydrogen-based solid oxide. These types of fuel cells have been proved to have bidirectional capabilities, also recalled as Solid oxide electrolyzed cells /fuel cells (SOEC-SOFC) or regenerative fuel cells (RFC) [45].

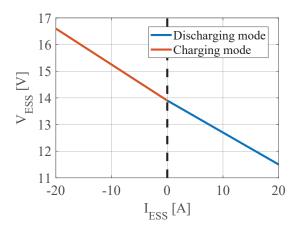

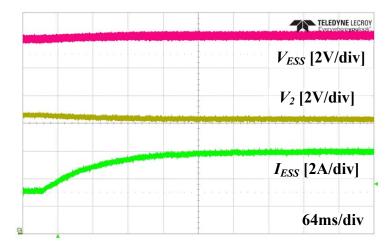

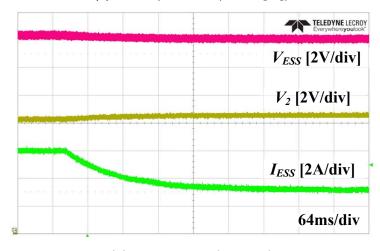

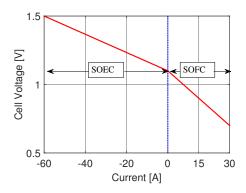

Electrical characteristics of RFC are dependent on a number of factors such as operating temperature, fuel composition or fuel pressure. Nevertheless, typical current-voltage characteristics of a single cell can be represented as illustrated with Fig.2.6. Although the mechanical processes of SOEC and SOFC are founded on the same basis, due to variation in the internal resistance and the current direction, the operating voltage in SOFC mode (discharging mode) is lower than in SOEC mode (charging mode) [52, 53]. In addition, in some cases tests demonstrated that power capability in SOEC mode is larger than in SOFC mode. Higher voltage ranges and power ranges are also achieved by stacking RFC in series.

Differently from the batteries, where normal operation is around the nominal voltage, RFCs nominal operation can range from maximum to minimum voltage. This requires of power electronic interfaces capable of operating in wide voltage ranges at the highest efficiency possible.

## 2.2 Dc-dc power converters for the future energy systems

Current activity towards high efficiency power electronics is mainly driven by three research areas, (I) converter topologies and system architectures, (II) control techniques

10 State-of-the-art

Figure 2.6: Typical current-voltage characteristics of a SOEC/SOFC single cell.

Figure 2.7: High voltage gain and multiple ports integration through high frequency transformer.

and (III) wide bandgap semiconductor devices.

From the topological viewpoint, research in bidirectional isolated dc-dc converters have gained increased attention during the past years. Due to the nature of each system, large different voltage levels have to be accommodated by the power converters. This has stimulated the interest on isolated power converters, even when galvanic isolation is not a requirement. The magnetic element, besides due to its conventional advantages regarding reliability, reduced noise and electromagnetic interference (EMI), it is also used to achieve certain dc gain ranges. In addition, the magnetic link from the high frequency transformer also eases the interconnection of multiple dc buses. As illustrated in Fig.2.7, multiple active switching bridges can be coupled to a multi-winding transformer, while the switching signals from each bridge can be used to regulate the voltage at each port and the power flow. In that way, the number of power conversion stages can be reduced, which can result in potential improvements in terms of efficiency and power density.

Conventional bidirectional isolated dc-dc converters are composed by at least one energy storage element, a capacitor, an inductor or a combination of two, and a bidirectional switching bridge connected at each of the transformer. Voltage and power flow is regulated at a constant switching frequency with pulse-width modulation (PWM). Authors in [54, 55] presented a review of conventional step-up/-down bidirectional isolated dc-dc converters. In the recent years, conventional isolated dc-dc converters have evolved into more complex topologies with the objective of increasing the system efficiency among other features, such as power density and reliability. In this aspect, soft-switching topologies have become popular in the academia as well as the industry. In soft-switching converters, the voltage or current during the semiconductors' switch-

ing transitions are zero. In that way, the energy related to the switching is zero and thus, the switching losses are highly reduced. Thanks to the lower switching losses, dc-dc converters can operate at higher switching frequency, which allows the implementation of high efficiency and high power density converters. Moreover, as a result of a reduction in the dv/dt and di/dt at switch turn-on and turn-off, soft-switching converters can potentially reduce the EMI [56, 57].

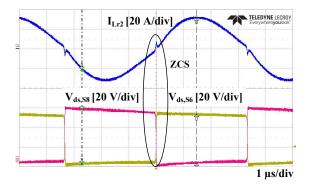

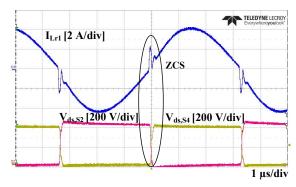

Soft-switching operation of a semiconductor device can be broadly classified into zerocurrent switching (ZCS) and zero-voltage switching (ZVS). In ZCS operation, the current flowing through the semiconductor is reduced to zero before the voltage across it increases. Contrarily, in ZVS operation, the voltage across the switching devices is brought to zero before the current increases. Different soft-switching techniques and converter topologies to achieve ZVS and ZCS operation have been studied in the literature [56] such as the resonant switching transitions by means of auxiliary circuits, ZVS through discontinuous conduction mode and the resonant and quasi-resonant power converters.

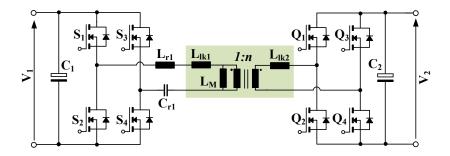

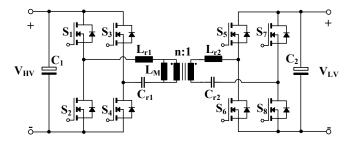

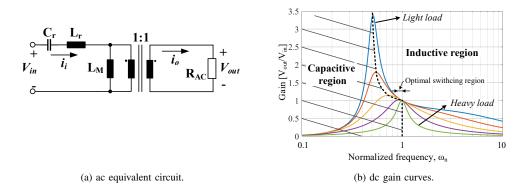

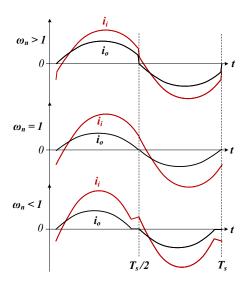

The traditional power converter topologies for soft-switching operation are the so-called resonant power converters. Resonant conversion in power electronics was firstly proposed in 1970 by F.C. Schwarz [58]. Resonant converters are composed by a switching bridge generating a voltage pulse which excites a resonant tank, creating a sinusoidal current at the primary side circuit. This sinusoidal current is transferred and scaled to the secondary side bridge and filtered by the output capacitance. Due to the sinusoidal current, the switches at the input and output bridges can operate with soft-switching. The resonant tank contains L-C networks which resonance frequency is tuned to match the fundamental component of the excitation voltage, i.e. the switching frequency. The dc voltage and current magnitudes can be regulated by changing the switching frequency closer or further from the resonance frequency. A multitude of resonant tank networks can be utilized to achieve different dc gain and resonant conversion characteristics [59]. From all the isolated resonant power converter topologies, one of the most popular is the series-resonant converter (SRC) or LLC converter. The SRC is composed by a series L-C network connected in series to the high-frequency transformer. The circuit schematic of a full-bridge SRC is shown in Fig.2.8. The SRC features ZVS at the input side switches and ZCS at the output side switches. At the same time, turn-off at the input side switches is carried out at low current, which leads to even lower switching losses. In addition, soft-switching operation and the current at turnoff is not load-dependent, but voltage dependent. This makes the SRC topology very attractive for applications with constant dc voltages, such as microgrid applications. On the other hand, in the SRC, ZVS is achieved with the magnetizing current of the transformer. This additional circulating current added up to the sinusoidal shape of the resonant current, results in larger rms currents and hence, higher conduction losses.

Beside the SRC, one of the most promising and studied soft-switched converter topologies in the past years is the dual-active-bridge (DAB) converter. The DAB was firstly proposed in 1991 by De Doncker [60]. The DAB converter topology is shown in Fig.2.9. Two full-bridges are interconnected with a high frequency transformer that provides both galvanic isolation and energy storage in its leakage inductance. Larger energy storage is achieved utilizing external ac inductors in series with the transformer. The two full-bridges typically operate at a fixed switching frequency and 50 % duty cycle, and the phase shift angle between the two bridges is used to control the magnitude and direction of power flow. Unlike other isolated dc-dc converter topologies, the DAB

12 State-of-the-art

Figure 2.8: Topology of the series resonant converter.

Figure 2.9: Topology of the dual active bridge.

has a symmetrical configuration, which enables bidirectional power flow with identical dc gain characteristics. By means of phase-shift modulation (PSM), the transformer current waveform becomes trapezoidal and delayed from the primary side transformer voltage. In that way, the energy stored in the transformer leakage inductance and the ac inductor after the primary side turn-off event is reused to achieve ZVS. Because of the trapezoidal shape of the transformer current and the reduced circulating current, the DAB bridge typically features reduced rms currents compared to the SRC [61]. On the other hand, turn-off commutation is carried out at larger current, which leads to increased switching losses [61]. Moreover, the transformer current is load dependent and thus, ZVS is lost under light load conditions [61]. The DAB bridge has been extensively studied since it was firstly proposed and multiple modulation strategies and topological variations have been addressed to improve its soft-switching characteristics and reduce the switching loss [62–72].

#### 2.2.1 Power converters for dc SST applications

For all the aforementioned reasons, the DAB and SRC are the most popular power converter topologies used in dc SST applications to interconnect dc buses. In App.D a review of SSTs based on the DAB and SRC has been performed and Table 2.1 presents the review summary.

The DAB, in contrast to the SRC, allows the integration of multiple active bridge coupled with a multi-winding transformer, wherein the phase-shift angle between each bridge can be used to control the power flow and regulate the voltage across each

|                 | DAB-based topologies |                  |                             | SRC-based topologies |                                     |                  |                   |

|-----------------|----------------------|------------------|-----------------------------|----------------------|-------------------------------------|------------------|-------------------|

| Study           | [73]                 | [74]             | [75]                        | [36]                 | [76]                                | [77]             | [78]              |

| Year            | 2014                 | 2018             | 2008                        | 2013                 | 2013                                | 2016             | 2018              |

| Power Flow      | $\Rightarrow$        | $\Rightarrow$    | $\Leftrightarrow$           | $\Leftrightarrow$    | $\Leftrightarrow$                   | $\Rightarrow$    | $\Leftrightarrow$ |

| No. ports $(n)$ | 2                    | 2                | 3                           | 4                    | 2                                   | 2                | 2                 |

| Control         | PSM                  | PSM              | PSM                         | PSM                  | PFM + PWM                           | Open-loop        | Open-loop         |

| Voltage rating  | $3.6\mathrm{kV};$    | $343\mathrm{V},$ | $300\mathrm{V};$            | 48 V; 48 V;          | 380 V;                              | 700 V;           | 760 V;            |

| $(V_1;; V_n)$   | 200 V                | $120\mathrm{V}$  | $42\mathrm{V};14\mathrm{V}$ | 48 V; 48 V           | 380 V                               | $600\mathrm{V}$  | $380\mathrm{V}$   |

| Power rating    | $9\mathrm{kW}$       | $800\mathrm{W}$  | $1.5\mathrm{kW}$            | $240\mathrm{W}$      | $5\mathrm{kW}$                      | $10\mathrm{kW}$  | $6\mathrm{kW}$    |

| Sw. frequency   | $3.6\mathrm{kHz}$    | $20\mathrm{kHz}$ | $100\mathrm{kHz}$           | $20\mathrm{kHz}$     | $55\mathrm{kHz}$ - $70\mathrm{kHz}$ | $20\mathrm{kHz}$ | $100\mathrm{kHz}$ |

| Max. efficiency | 92%                  | 96.3%            | 91.7%                       | -                    | 97.8 %                              | 98.61%           | 97.8%             |

Table 2.1: Review of Solid State Transformers.

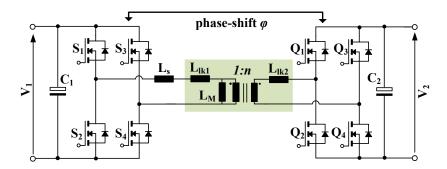

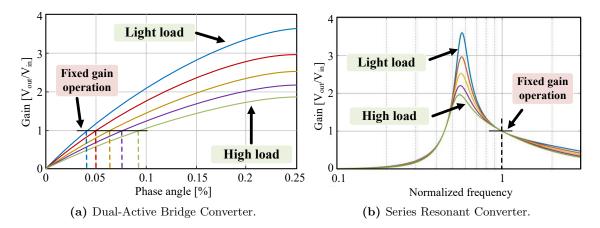

port. This makes the DAB an interesting topology for multi-port applications where voltage regulation at each port has to be carried out by the dc SST. On the other hand, the SRC presents inherited load regulation characteristics when operating at the resonance region, which makes it suitable for open-loop operation. Fig. 2.10 shows the dc gain characteristics of the DAB and SRC for different output power in function of the control parameter, where for the DAB is the phase shift angle  $\varphi$  and for the SRC is the normalized frequency. It can be observed that for the DAB the control parameter has to be actively regulated to maintain the same voltage gain under power fluctuations. Otherwise, the SRC can operate at a fixed switching frequency and fixed unity gain under power fluctuations. The SRC operating at the unity gain region is also known as dc transformer. In applications with constant dc bus voltages, such as microgrid and smart grid applications, the SRC dc transformer presents additional advantages into the system: (1) avoids the necessity of control loops, reducing the complexity of the control circuitry and software, (2) less number of sensors are required, (3) soft-switching operation under all operating conditions and (4) allows an optimal and simplified design for high efficiency and power density.

During the past couple of years, the SRC dc transformer has gained an increasing attention due to its advantages in dc SST applications [34, 69, 77–86]. Studies carried about the SRC dc transformer cover issues such as topology derivations to improve the performance of the converter [81, 82], reliability [77], high frequency operation with wide bandgap devices [86] or components design for high efficiency and power density [84, 87]. However, the design methodology of the open-loop SRC differs from the conventional closed-loop SRC. Design considerations such as maximum power transfer for soft-switching operation, load regulation to fulfil the design requirements or accurate selection of the resonant tank components and dead-time for reduced circulating energy were not fully covered in the literature by the start of this project.

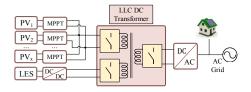

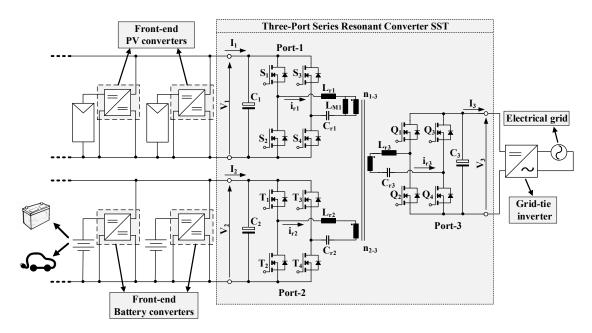

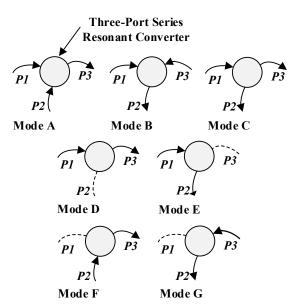

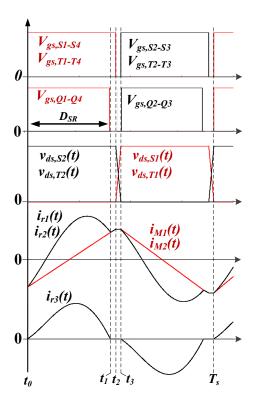

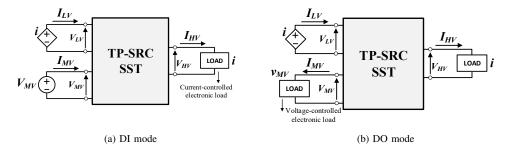

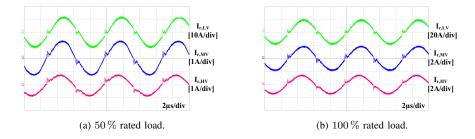

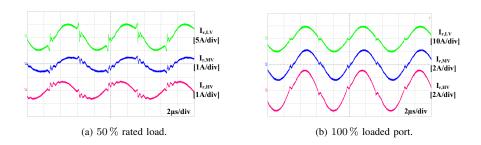

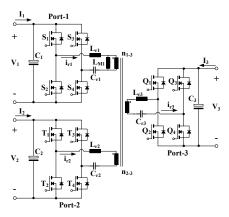

Moreover, for applications where multi-port dc SSTs are required to interconnect multiple dc buses, SRCs with three or more ports can be used. The three-port SRC (3P-SRC) was first proposed by [88]. The circuit topology presented in [88] operates at a fixed switching frequency with a centralized PSM scheme to regulate voltage and power flow. However, investigations about multi-port SRC dc transformer and its de-

14 State-of-the-art

**Figure 2.10:** Common dc gain characteristics for the DAB and SRC in terms of typical control parameter, i.e. phase angle for the DAB and switching frequency for the SRC, for different output power.

sign considerations have not been reported yet. In chapter 3 all the literature gaps regarding design considerations for the two-port and three-port SRC are covered and verified with experimental prototypes.

#### 2.2.2 Power converters for ESSs

Research challenges in power electronics for ESSs integration lay on the high efficiency operation with high voltage gain and in some cases, coupled with wide voltage ranges, as in RFC applications. In non-isolated topologies, the basic approach to achieve high voltage gain is the utilization of cascaded dc-dc converters. In high-power applications, where efficiency is a concern, it is often beneficial to use magnetic coupling to achieve higher voltage gain ratios. Interleaved configurations are also used in high current applications to reduce current stress on semiconductor devices and decrease the size of passive components. However, electrical isolation is often required in grid-connected applications where reliable power transfer with low noise and EMI are needed.

The DAB and SRC topologies are also popular isolated dc-dc converter topologies in ESS applications. However, in wide voltage range applications, their efficiency performance degradates [89]. It has been studied that, in some cases, their losses can be even higher than in traditional bidirectional isolated topologies [90]. Table 2.2 shows a review of bidirectional dc-dc converters for wide voltage range applications based on the SRC, the DAB converter and the boost full-bridge and half bridge converter.

The SRC, for instance, has to operate in wide frequency ranges to regulate wide voltage ranges. This increases the complexity of the magnetics design as well as the converter loses. In [91] the efficiency of the SRC is analysed under different output voltages. In this study, the efficiency of the SRC drops almost a 1.5% when the operating voltage is 29% below the optimal output voltage. Different approaches are proposed in the literature to improve the efficiency performance of the SRC in wide voltage range applications. In [76, 92–96] optimised design methodologies for the resonant tank components to achieve high efficiency operation are presented. Nowadays, first harmonic approximation (FHA) is the most used and simplest way to design the SRC. How-

ever, in wide voltage range applications the operating frequency is usually far from the resonance frequency which makes the FHA inaccurate. To solve this issue, authors in [97, 98] utilize numerical non-linear programming techniques to design the SRC for high efficiency operation. Studies in [91, 99] propose a variable dc bus voltage, which is regulated by the grid-tied inverter, to reduce the gain requirements for the SRC and thus, reduce the frequency range. Other researchers [76, 100] proposed fixed switching frequency operation in conjunction to PWM or PSM, in order to maintain soft-switching operation for larger operating ranges at the expense of increased circulating currents.

Regarding the DAB, in wide voltage range applications, the voltage unmatch between low voltage side and high voltage side causes that the isosceles trapezoid current waveform becomes a scalene trapezoid waveform. Consequently, the current at the turn-off event and the rms current increase. Which leads to higher switching losses and conduction losses. Targeting towards turn-off current reduction and ZVS extension, advanced modulation strategies were studied and adopted in the DAB. For instance, double or triple PSM, variable frequency modulation and PWM control [63, 64, 66–68, 101]. Various techniques to reduce the conduction losses at the low voltage side have also been proposed. The well-know method is to parallel semiconductor devices or converter modules [69–72]. However, parallel switching devices increases parasitic inductances and creates temperature imbalances among paralleled switches, complicating the circuit layout. In addition, thick copper or parallel structure must be applied to transformer windings resulting in high manufacturing cost and high interwinding capacitance. Furthermore, paralleling converter modules need additional efforts to eliminate circulating currents between units. Besides the current sharing at the low voltage side, methodologies to reduce the voltage stress at the high voltage side have also been proposed, such as the series connection of semiconductors and switching bridges [73, 74, 102].

16 State-of-the-art

Table 2.2: Review of bidirectional dc-dc converters for ESSs.

| Study | Year | Study Year Topology             | Switches Power | Power            | Sw. frequency                         | $V_1$           | $V_2$                                 | Efficiency 1                   | Efficiency 2                 | Power density           |

|-------|------|---------------------------------|----------------|------------------|---------------------------------------|-----------------|---------------------------------------|--------------------------------|------------------------------|-------------------------|

| [103] | 2012 | 2012 DAB                        | Si             | $6\mathrm{kW}$   | 40 kHz                                | 288 V           | 24 V - 48 V                           | 96.4% @ 36 V                   | 94.5 % @ 24 V                | Not given               |

| [104] | 2012 | DAB                             | IGBT           | $6\mathrm{kW}$   | $20\mathrm{kHz}$                      | $355\mathrm{V}$ | 50  V - 59  V                         | $96.9\% \oplus 59 \mathrm{V}$  | $93\%$ @ $55\mathrm{V}$      | Not given               |

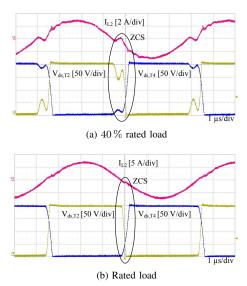

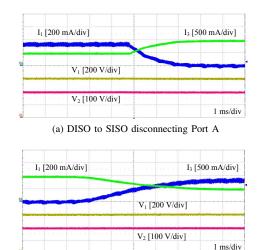

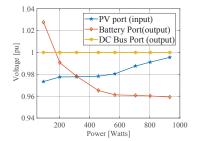

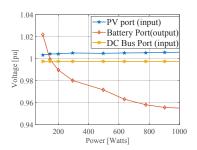

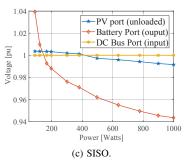

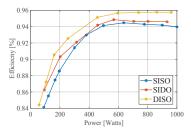

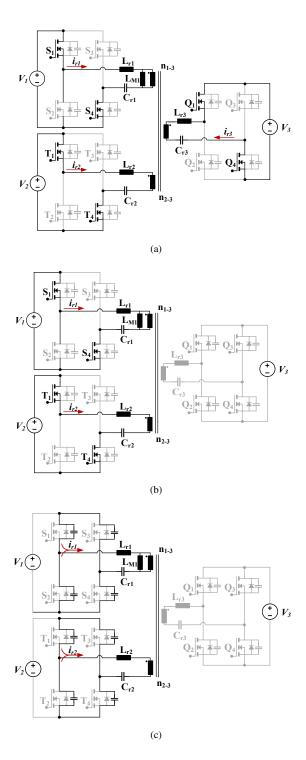

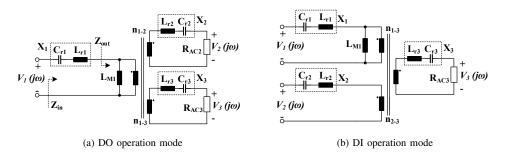

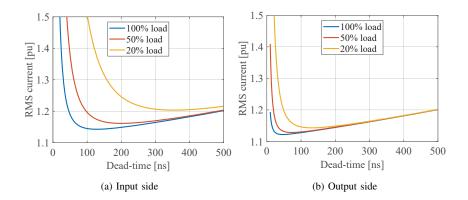

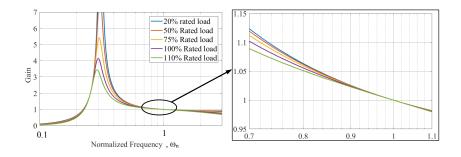

| [105] | 2017 | DAB                             | GaN            | $1\mathrm{kW}$   | $100\mathrm{kHz}$                     | $400\mathrm{V}$ | 11  V - 13  V                         | $98.3\% \ @ \ 12\mathrm{V}$    | Not given                    | $1.83\mathrm{Wcm^{-3}}$ |