# Isolated dc-dc power converter with active synchronous rectification

Ouyang, Ziwei; Zhao, Bin; Andersen, Michael Andreas Esbern

Publication date: 2020

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Ouyang, Z., Zhao, B., & Andersen, M. A. E. (2020). Isolated dc-dc power converter with active synchronous rectification. (Patent No. *WO2020157118*).

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

#

(10) International Publication Number WO 2020/157118 A1

06 August 2020 (06.08.2020)

(21) International Application Number:

PCT/EP2020/052143

(22) International Filing Date:

29 January 2020 (29.01.2020)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

19155153.0

01 February 2019 (01.02.2019) EP

- (71) Applicant: DANMARKS TEKNISKE UNIVERSITET [DK/DK]; Anker Engehmds Vej 101 A, 2800 Kgs. Lyngby (DK).

- (72) Inventors: OUYANG, Ziwei; Cedervasnget 29, st. tv., 2830 Virum (DK). ZHAO, Bin; No.5, Yanqi East Second Road, Huairou District, Beijing, 101400 (CN). AN¬

- **DERSEN, Michael Andreas Esbem;** Gurrehavevej 55, 3200 Helsinge (DK).

- (74) Agent: GUARDIAN IP CONSULTING IS; Diplomvej, building 381, 2800 Kgs. Lyngby (DK).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, WS, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV,

(54) Title: ISOLATED DC-DC POWER CONVERTER WITH ACTIVE SYNCHRONOUS RECTIFICATION

Fig. 2

(57) **Abstract:** The present invention relates to switched mode power supplies, and more particularly relates to an isolated DC-DC power converter comprising a secondary side active synchronous rectification circuit. The active synchronous rectification circuit comprises a network of passive components driven by a voltage across a rectification switch to generate a switch control signal for the rectification switch.

MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

# **Published:**

— with international search report (Art. 21(3))

# ISOLATED DC-DC POWER CONVERTER WITH ACTIVE SYNCHRONOUS RECTIFICATION

The present invention relates to switched mode power supplies, and more particularly relates to an isolated DC-DC power converter comprising a secondary side active synchronous rectification circuit. The active synchronous rectification circuit comprises a network of passive components driven by a voltage across a rectification switch to generate a switch control signal for the rectification switch.

# 10 BACKGROUND OF THE INVENTION

In the area of primary-side DC/DC converters with galvanic isolation, especially in low DC output voltage converters, the utilization of actively controlled transistor switches as rectifiers (instead of passive diodes) is a technique increasingly used due to the low conduction losses. In a DC-DC power converter, the rectifier or rectification switches are connected at a secondary side of a transformer and rectify power coupled through the transformer. The topology and number of components of the active synchronous rectification circuit as well as the way the rectification switch or switches are controlled on the secondary side of the converter is crucial for an efficient operation of the DC-DC power converter.

20

25

30

15

5

Typically, a switch driver circuit is used to generate a switch control or driving signal(s) for the rectification switch or switches. The switch driver circuit is a power amplifier that accepts a low-power control signal or voltage from an actively powered controller IC and produces a low-impedance drive signal for the control terminal, e.g. gate terminal or base terminal of the rectification switch or switches.

In isolated DC-DC power converter topologies with a primary side control signal, such as a modulated switch control signal, there is an absence of a controlling signal on the secondary side of the transformer. In such a topology, it is known to generate the switch control signal for the rectification switches on the primary side of the galvanic isolation - thus the control signal has to cross the galvanic isolation barrier e.g. using costly and space consuming optocouplers or isolation transformers etc. In

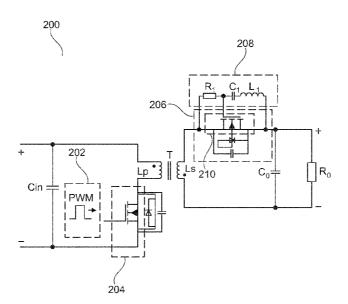

such approaches, as schematically illustrated by Fig. 1, a control signal may be derived by the gate driver circuit 106 from a PWM modulated switch control signal 102 for driving the rectifiers, wherein the PWM control signal is provided by an external and actively powered controller, e.g. by power supply voltage Vcc as illustrated in FIG. 1. The gate driver circuit 106 comprises active semiconductor switches like transistors Ql, Q2 to provide the previously discussed low-impedance and/or high voltage switch control signal. The PWM modulated switch control signal 102 is typically the one which is used for driving a semiconductor switch on the primary side of the converter. The external controller may be a digital controller DSP or Field Programmable Gate Arrays, FPGA, an analog controller, a timer, and/or an oscillator. Due to the requirement of the external controller and the auxiliary power supply to power the active semiconductor transistors Ql, Q2, the operational complexity and size of the switch driver circuit 106 of the DC-DC power converter increase which is disadvantageous. Further, cost of the gate driver circuit increases due to these additional components, which creates a hindrance in use of these gate driver circuits in the power conversion area.

Patent application CN104124874 (A) proposes an ultrahigh frequency isolated resonant converter comprising a Class  $\Phi 2$  inverter and a synchronous rectifier. A gate drive signal for the synchronous rectifier is derived from a separate (auxiliary) transformer winding and is applied to the gate of the rectification switch (transistor) through an inductor and a capacitor. Clearly, a separate transformer winding is required for deriving the gate drive signal, which is again not a cost effective solution. Further, due to the separate (auxiliary) transformer winding, a circuit of the converter proposed by CN104124874 (A) will be complex and less compact, which is again disadvantageous.

Therefore, there is a need to alleviate problems existing in the prior arts.

# SUMMARY OF THE INVENTION

5

10

15

20

25

30

A first aspect of the invention relates to an isolated DC-DC power converter comprising:

a transformer (T) having a primary winding (Lp) and a secondary winding (Ls);

a controllable switch connected in series with the primary winding (Lp) of the transformer (T) and driven by a modulated switch control signal;

an active synchronous rectification circuit connected to the secondary winding (Ls) of the transformer (T), the active synchronous rectification circuitry comprising a rectification switch (210) connected in series with the secondary winding (Ls); and

a switch driver circuit comprising a network of passive components driven by a voltage across the rectification switch, said network of passive components configured to generate a switch control signal for the rectification switch by lowpass filtering the voltage across the rectification switch.

Hence, the switch control signal may be derived from the voltage across the rectification switch by lowpass filtering of the voltage across the rectification switch. The lowpass filtering of the voltage across the rectification switch may be carried out by a network of passive components which may be series connected across the rectification switch to provide a compact, cost-efficient and self-driven active synchronous rectification circuit as discussed in additional detail below with reference to the appended drawings. One or several passive electrical components, such as a resistor, inductor or capacitor, of the network of passive components is/are preferably external to the rectification switch and may comprise respective SMD components.

25

30

5

10

15

20

The network of passive components may comprise a series connection of at least one inductor (LI), capacitor (Cl), and optionally a resistor (Rl) across the rectification switch (210) for example between drain and source terminals of a FET switch such as a MOSFET switch, insulated gate bipolar transistor (IGBT) switch, Gallium Nitride (GaN) switch etc. and wherein the switch control signal is applied to a gate terminal or base terminal of said FET switch.

The resistor Ri of the network of passive components is preferably connected between a control terminal and an output terminal of the rectification switch.

The network of passive components preferably comprises, or forms, a lowpass filter configured to filter the voltage across the rectification switch. The lowpass filter preferably has a cut-off frequency (frl) below a switching frequency of the modulated switch control signal, for example may the cut-off frequency (frl) be less than one-half of the switching frequency of the modulated switch control signal, as discussed in additional detail below with reference to the appended drawings.

10

5

The Q value of the lowpass filter is preferably larger than 3 such as larger than 5 or more preferably larger than 10 to provide rapid phase shift of the lowpass filtered switch control signal of the rectification switch as discussed in additional detail below with reference to the appended drawings.

15

20

25

The network of passive components may additionally comprise, or form, a band-reject filter which is configured to filter the voltage across the rectification switch. This band-reject filter may have a zero frequency (fr2) above the switching frequency of the modulated switch control signal such as at least three times higher than the switching frequency of the modulated switch control signal such as between three and five times higher as discussed in additional detail below with reference to the appended drawings.

The switching frequency of the modulated switch control signal may be higher than 100 kHz, or higher than 1 MHz, more preferably higher than 5 MHz. The modulated switch control signal may comprise a Pulse-Width Modulated (PWM) signal or a frequency modulated (FM) signal e.g. configured to control an output voltage, output current or output power of the power converter.

One embodiment of the present isolated DC-DC power converter comprises an inrush current limiter which is electrically connected, or coupled, to the switch driver circuit. The inrush current limiter is configured to disable the switch driver circuit for

a predetermined time period following power-on of the isolated DC-DC power converter.

A second aspect of the invention relates to a method of deriving a switch control signal of an active synchronous rectification circuit of an isolated DC-DC power converter, the method comprising:

10

15

20

25

30

applying a modulated switch control signal to a controllable switch connected in series with a primary winding (Lp) of an isolation transformer (T),

connecting an active synchronous rectification circuitry to a secondary winding (Ls) of the isolation transformer (T) to couple a rectification switch in series with the secondary winding (Ls);

deriving a switch control signal for the rectification switch by lowpass filtering a voltage across the rectification switch via a network of passive components; and applying the switch control signal to a control terminal of the rectification switch.

The isolated DC-DC power converter preferably comprises a transformer which functions as a galvanic isolation barrier between the primary side circuitry and secondary side circuitry of the DC-DC power converter. The transformer comprises a primary winding and a secondary winding that may be magnetically coupled via a magnetically permeable core. The primary side circuitry of the DC-DC power converter comprises the controllable switch connected in series with the primary winding (Lp) of the transformer (T) and driven by a modulated switch control signal. The controllable switch may comprise a controllable transistor switch such as a MOSFET, IGBT or GaN FET.

The network of passive components may comprise a series connection of at least one inductor, one capacitor and optionally a resistor, connected across the rectification switch (210). Hence, the network of series connected passive components may be

coupled between a drain terminal and source terminal of a MOSFET or GaN FET type of rectification switch.

According to a preferred embodiment, the isolated DC-DC power converter comprises an inrush current limiter coupled to the switch driver circuit, said inrush current limiter configured to disable the switch driver circuit for a predetermined time period following power-on or start-up of the isolated DC-DC power converter.

## BRIEF DESCRIPTION OF THE DRAWINGS

5

20

- Preferred embodiments of the invention will be described in more detail below with reference to the enclosed drawings, in which

- FIG. 1 is an electrical circuit diagram of a gate driver according to the prior art,

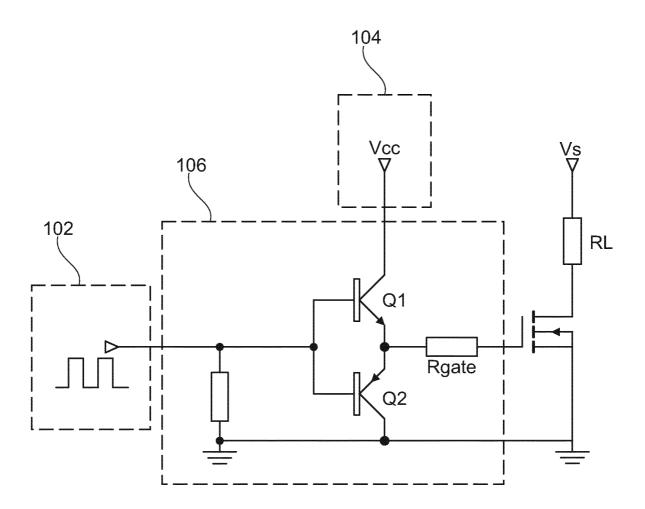

- 15 FIG. 2 is a simplified electrical circuit diagram of an isolated DC-DC power converter in accordance with an exemplary embodiment of the invention,

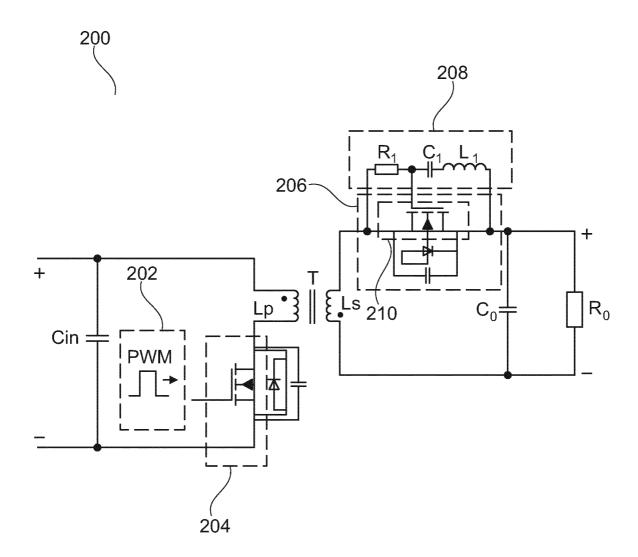

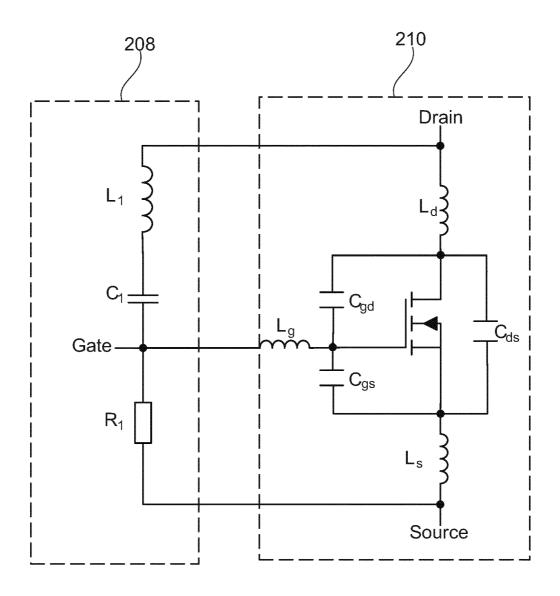

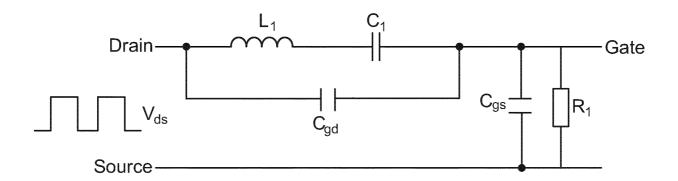

- FIG. 3 is a simplified electrical circuit diagram of a switch driver circuit for a secondary side rectification switch of the isolated DC-DC power converter shown in FIG. 2,

- FIG. 4 is another simplified electrical circuit diagram of the switch driver circuit shown in FIG. 3,

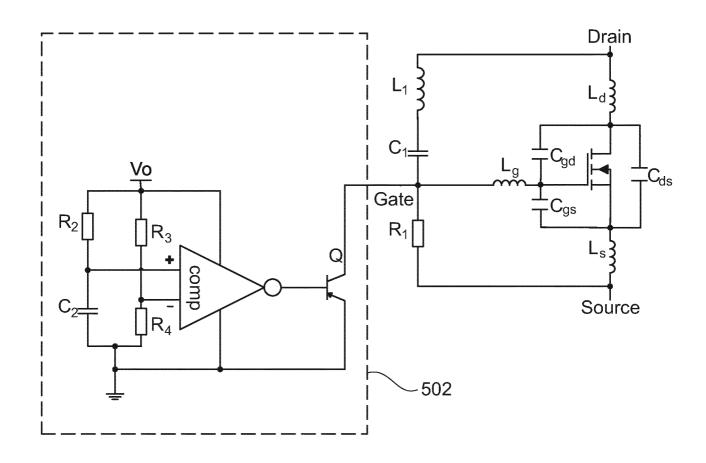

- FIG. 5 is a simplified electrical circuit diagram of an inrush current limiter that may be included in the isolated DC-DC power converter shown in FIG. 2,

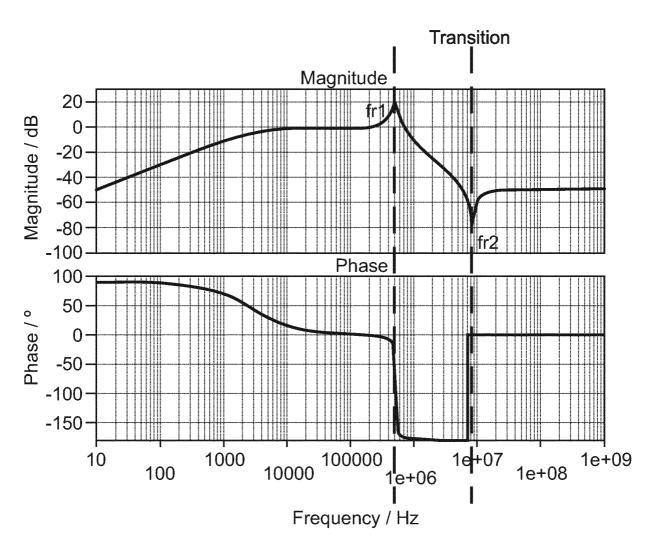

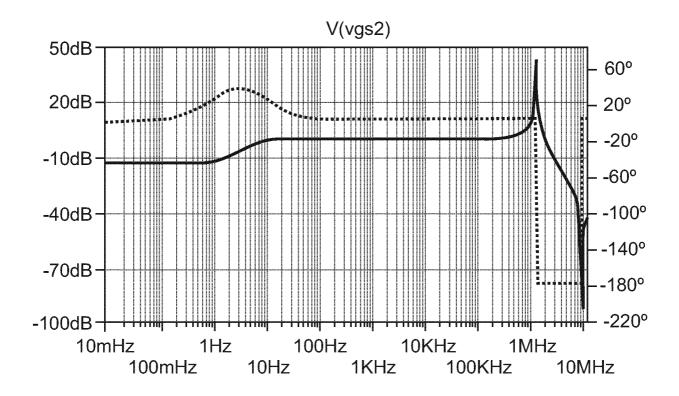

- FIG. 6 shows a gain-phase Bode plot/frequency response plot of a passive components network forming part of the switch driver circuit,

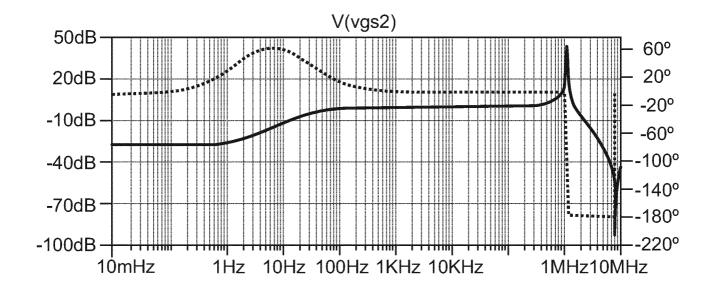

- FIG. 7 shows a bode plot corresponding to simulation results for an isolated DC-DC power converter in a flyback topology without DC bias of a gate signal, or control signal, of the rectification switch,

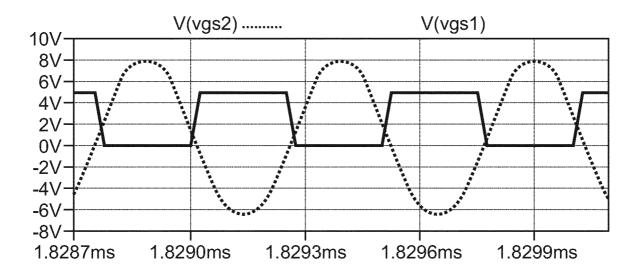

FIG. 8 shows time domain simulation results for a controllable primary side switch and the rectification switch of an isolated DC-DC power converter in a flyback topology without DC bias of the gate signal,

- FIG. 9 shows a bode plot of corresponding simulation results for an isolated DC-DC power converter in a flyback topology with DC bias of the gate signal,

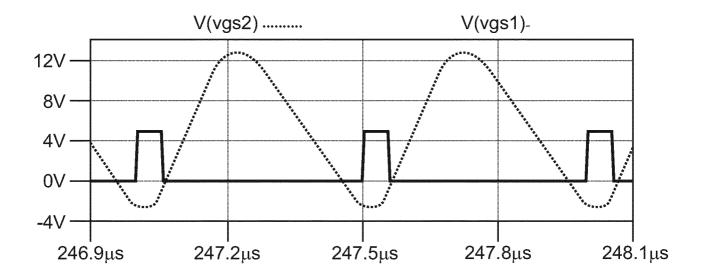

- FIG. 10 shows time domain simulation results for the primary side switch and the rectification switch of an isolated DC-DC power converter in a flyback topology with DC bias of a gate signal,

10

5

In the figures, the same reference symbols or signs are used for same or corresponding elements. The discussion of the figures dispenses with discussing elements with the same reference signs in different figures when deemed appropriate for sake of conciseness.

15

20

25

30

#### DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

An isolated DC-DC power converter of the present invention includes an active synchronous rectification circuit having at least one rectification switch, and further includes a switch driver circuit for producing a control signal for the at least one rectification switch. The present switch driver circuit is based on a network of passive components, such as resistors, capacitors and inductors, and can therefore be viewed as a passive circuit. The network of passive components is driven by a voltage drop across the rectification switch. Thereby, eliminating the need of an external power supply and active components for operation. Further, the network of passive components is configured to generate the switch control signal for the rectification switch or switches by lowpass filtering the voltage across the rectification switch, e.g. the drain-source voltage of a FET type rectification switch.

The output voltage of the DC-DC power converter at the secondary side of the isolation transformer is utilized by the switch driver circuit. Clearly, the present switch driver circuit for the rectification switch may be viewed as a self-driven

circuit or boot-strap circuit exclusively powered by the secondary side voltage and current of the isolation transformer. This feature renders the circuit topology of the secondary side circuitry of the present isolated DC-DC power converter simple and cost-effective over the conventional DC-DC power converters.

Referring to FIG. 2, an isolated DC-DC power converter 200 is shown. For brevity the isolated DC-DC power converter 200 is referred herein below as converter 200. The converter 200 includes a transformer T having a primary winding Lp, supplied with a DC voltage e.g. at a capacitor Cin, and a secondary winding Ls supplying power to a load Ro of the converter. A primary side arranged controllable semiconductor switch 204 is connected in series with the primary winding Lp of the transformer T. The power converter can e.g. be a flyback converter. The controllable semiconductor switch 204 is controlled by a modulated control signal 202, which may be PWM modulated or frequency modulated, generated by a controller (not shown in figures). The modulated control signal is applied to a control terminal, e.g. gate terminal or base terminal, of the controllable primary side semiconductor switch 204. The skilled person will understand that the modulated control signal may be generated by an output voltage control or regulation loop, e.g. feedback loop, configured to control output power, output voltage or output current delivered to the load Ro of the DC-DC power converter 200.

The secondary side of the converter 200 includes an active synchronous rectification circuit 206 connected to the secondary winding Ls of the transformer T. The active synchronous rectification circuit 206 includes at least one rectification switch 210 along with other circuit components. The skilled person will appreciate that other embodiments of the invention may include two or more rectification switches with respective switch driver circuits. In an embodiment, the rectification switch 210 is a metal-oxide-semiconductor field-effect transistor, MOSFET. The active synchronous rectification circuitry 206 is further connected to the converter load Ro. The rectified voltage may be smoothed or stabilized e.g. by a capacitor CO connected across output terminals of the power converter.

The active synchronous rectification circuitry 206 further includes a passive components network 208 connected across the drain and source terminals of the rectification switch 210. The passive components network is configured to derive a lowpass filtered and phase-shifted control signal which is coupled to and drives the gate terminal of the rectification switch 210.

5

10

15

20

25

30

As shown in figure 2, the switch driver circuit which drives the control/gate terminal of the rectification switch 210 comprises a passive components network 208, i.e. a series connection of an inductor Li, a capacitor Ci, and a resistor Ri arranged from the drain terminal to the source terminal of the rectification switch 210. The inductor Li, capacitor Ci and a resistor Ri of the passive components network 208 are preferably external, physical separate, components to the rectification switch 210, i.e. not formed by the below-discussed parasitic components of the rectification switch 210. The inductor Li, capacitor Ci and a resistor Ri of the passive components network 208 may for example be formed by respective SMD components for easy assembly on a suitable carrier substrate, e.g. printed circuit board, of the isolated DC-DC power converter 200.

Referring to FIGS. 2 - 4, the switch driver circuit is excited by a voltage drop across input and output terminals of the rectification switch, i.e. the drain-source terminals of the rectification switch 210 of the present embodiment, and the passive components network 208 is configured to derive a lowpass filtered control voltage or signal and apply the latter to the gate terminal of the rectification switch 210. The voltage drop across the rectification switch 210 is derived from the output voltage at the secondary side of the transformer T and utilized by the switch driver circuit 208.

As shown in FIG. 4, the voltage drop across the rectification switch 210, i.e. the drain-source voltage  $V_{d_S}$ , is applied as an input voltage to the passive components network 208. As mentioned above, the passive components network 208 comprises series connected passive components: inductor Li, capacitor Ci, and resistor Ri connected between the drain and source terminals of the rectification switch 210. The passive components network 208 preferably also comprises one or more of intrinsic

capacitances  $C_{gs}$  and  $C_{gd}$  and intrinsic inductance  $L_g$  of the rectification switch 210 such as the intrinsic drain-source  $C_{gd}$  and intrinsic gate-source capacitance  $C_{gs}$  etc. of a MOSFET or GaN type rectifier switch to tailor a transfer function of the passive components network 208 as discussed below in additional detail.

In some embodiments of the passive components network 208, the respective capacitances or inductances of one or both of the intrinsic capacitances  $C_{gs}$  and  $C_{gd}$  may be too small to reach a target or desired transfer function of the passive components network 208, e.g. the lowpass cut-off frequency frl and/or the second resonant frequency fr2. In the latter embodiments, the respective capacitances of one or both of the intrinsic capacitances  $C_{gs}$  and  $C_{gd}$  may be increased by connecting additional external, capacitors in parallel with the intrinsic capacitances  $C_{gs}$  and  $C_{gd}$  he passive components network 208 is preferably configured to create or provide a  $2^{nd}$  order lowpass filter exhibiting a lowpass cut-off frequency or resonance frequency frl to perform the previously discussed lowpass filtering of the drain-source voltage  $V_{ds}$  of the rectification switch 210. The lowpass cut-off frequency or resonance frequency frl is calculated according to:

$$f_{r1} = \frac{1}{2\pi\sqrt{L_1 \cdot (C_1 + C_{qs})}}$$

The cut-off frequency frl of the lowpass filter may be less than about one-half of the first harmonic of the switching frequency of the modulated switch control signal applied on the primary side circuit. In this manner, the first harmonic of the voltage across the rectification switch, i.e. the drain-source voltage  $V_{\rm d_S}$  in the present embodiment, is attenuated and phase shifted approximately 180 degrees at the output of the passive components network 208. The output of the passive components network 208, e.g. tapping node in-between the capacitor Ci and resistor Ri, supplies the lowpass filtered and phase shifted switch control signal to gate terminal of the rectification switch (210). The tapping node of the passive components network 208 may be directly connected via a wire or trace to the gate terminal of the rectification switch (210) without any intervening active components like transistors.

The intrinsic gate-drain MOSFET capacitance  $C_{gd}$  and the inductor Li creates a second resonant frequency, or zero frequency, fr2 of the transfer function of the passive components network 208.

5 The second resonant frequency fr2 is calculated according to:

10

15

20

$$f_{r2} = \frac{1}{2\pi\sqrt{L_1 \cdot C_{gd}}}$$

The zero frequency, fr2 is preferably tuned or designed to be at least five or ten times higher than the lowpass cut-off frequency firl to create a relatively wide transition frequency region with lowpass filter response between these two frequencies frl and fr2. The lowpass filter preferably exhibits a relatively high Q value, such as above 5 or 10, at the cut-off frequency frl to ensure a rapid phase shift above the cut-off frequency frl.

The switching frequency of the modulated switch control signal is selected to be above the lowpass cut-off frequency frl such that the first harmonic and third harmonic of the modulated switch control signal are placed within this wide transition frequency region. Further, the resistance of the resistor Ri of the passive components network 208 is designed to attenuate gain of the transfer function of the passive components network 208 at DC or zero Hz with a predetermined value e.g. more than 10 dB or 20 dB or 30 dB. More specifically, the resistance of Ri is preferably configured to, or tuned for, obtaining a predetermined DC bias voltage of the control/gate signal of the rectification switch 210. The DC bias voltage of the gate signal may be conveniently adjusted by adjusting a resistance of the resistor Ri.

- In an embodiment, respective values of the inductor Li, capacitor Ci, and resistor Ri of the passive components network 208 are selected based on:

- (i) required attenuation level of a DC component of the voltage  $V_{d_s}$ ,

- (ii) required attenuation of the first harmonic and the third harmonic of the drain-source voltage  $V_{ds}$  to an adequate level, and

11

30 (iii) shifting the phase in the transition region by about 180 degrees.

The switching frequency of the rectification switch 210 can be varied as long as these three conditions (i)-(iii) are satisfied. The constraints enable the use of the switch driver circuit in power converter applications requiring variable frequency of the modulated switch control signal - such as in case of Discontinuous Conduction Mode, DCM flyback and LLC DC-DC power converters. The aforementioned adequate level is determined based on amplitude of the drain-source voltage  $V_{\rm ds}$ , duty cycle D, and particular type of rectification switches used in the active synchronous rectification circuitry 206.

10

5

An adequate level (G) may be determined using the following equation:

$$G = 20 * \log |\frac{Vgs}{Vds1}|$$

Where  $V_{dSi}$  is the amplitude of the first harmonic of the drain-source voltage  $V_{dS}$  and  $V_{gS}$  represents the gate-source voltage, i.e. switch control signal, of the rectification switch 210.

15

20

25

Referring to FIG. 5, the power converter 200 may additionally include an inrush current limiter 502 coupled to the switch driver circuit. The inrush current limiter 502 is configured to disable the switch driver circuit for a pre-determined time period after power-on of the isolated DC-DC power converter to avoid the flow of inrush current which otherwise may build-up during a start-up phase of the converter 200. During the start-up phase, a transistor Q, e.g. a FET or bipolar transistor, is in an ON-state causing the gate-source voltage of the rectification switch 210 to be pulled to ground or zero volt. This results in a disabling of the switch driver circuit. After the pre-determined time period, the capacitor C2 has been charged from the power supply voltage Vo of the converter such that the output of comparator, comp, changes state and switches the transistor Q to its OFF state, thereby enabling the switch driver circuit 208.

FIG. 6 - FIG. 10 show various time-domain simulation results for an exemplaryisolated DC-DC power converter possess flyback topology.

# (a) Simulation without DC bias of the gate signal

Input voltage of the converter - 100 V

Output voltage - 15V

10

15

5 Duty cycle of a primary side/ main controllable switch - 46%.

Exemplary parameters values of the passive components network

| <u>Parameter</u>           | <u>Value</u>                |

|----------------------------|-----------------------------|

| $\mathrm{C}_{\mathrm{gd}}$ | 3-9 pF                      |

| $C_{ m gs}$                | 250 – 295 pF                |

| $\mathrm{C}_{ds}$          | 120 – 140 pF                |

| $R_1$                      | $400 - 500 \text{ k}\Omega$ |

| $L_1$                      | 50-70 uH                    |

| C <sub>1</sub>             | 7-15 nF                     |

| $f_{s}$                    | 2-3 MHz                     |

A frequency response plot of the passive components network 208 is shown in FIG. 6, wherein phase shift is 180 degrees and voltage gain is -10 dB at 2 MHz which is the switching frequency of the modulated switch control signal. The gain of the transfer function of the passive components network 208 is also attenuated at third harmonic frequency at 6 MHz. The DC component of the switch voltage  $V_{d_S}$  is also attenuated with about -25 dB which leads to substantially zero volt DC bias to the lowpass filtered switch control signal, i.e. gate voltage, of the rectification switch (210).

A time domain simulation of the switch voltages  $V_{d_S}$  and  $V_{gs}$  of the rectification switch (210) is shown in FIG. 8. The full line plot V(vgsl) of FIG. 8 represents the modulated switch control signal driving signal the primary side controllable switch

and the dotted line plot V(vgs2) represents the corresponding lowpass filtered switch control signal of the rectification switch (210). It is evident by inspection of FIG. 8 that the ON/OFF state transitions of the primary side controllable switch are phase shifted with about 180 degrees relative to the ON/OFF state transitions of the rectification switch (210) as expected.

5

10

15

20

25

(b) <u>Simulation results using DC bias of the switch control signal of rectification switch</u>

When the DC input voltage, which typically is derived from a mains voltage, to the DC-DC power converter increases to 375 V, in order to maintain the converter DC output voltage at 15V, the duty cycle of the modulated switch control signal decreases. Thereby, increasing the duty cycle of the control signal of the rectification switch. In such instances, a DC bias may advantageously be introduced to the control signal of the rectification switch. In the instant simulation this is achieved by increasing the resistance of R 1 of the passive components network 208 from 500  $\kappa$   $\Omega$  to 3 M $\Omega$  to change the duty cycle of the rectification switch.

A frequency response plot (including magnitude and phase) of the revised the passive components network 208 is shown in FIG. 9 and a corresponding time-domain simulation of the switch voltages  $V_{d_S}$  and  $V_{g_S}$  of the rectification switch (210) is shown in FIG. 10. The full line plot V(vgsl) represents the modulated switch control signal driving signal of the primary side controllable switch and the dotted line plot V(vgs2) represents the corresponding lowpass filtered switch control signal, i.e. gate voltage, of the rectification switch (210). The lowpass filtered switch control signal V(vgs2) has now a DC bias or off-set of about 5V leading to an increase of duty cycle.

### **CLAIMS**

1. An isolated DC-DC power converter comprising:

5 a t

a transformer (T) having a primary winding (Lp) and a secondary winding (Ls);

a controllable switch (204) connected in series with the primary winding (Lp) of the transformer (T) and driven by a modulated switch control signal;

10

an active synchronous rectification circuit (206) connected to the secondary winding (Ls) of the transformer (T), the active synchronous rectification circuitry (206) comprising a rectification switch (210) connected in series with the secondary winding (Ls); and

a switch driver circuit (208) comprising a network of passive components driven by a voltage across the rectification switch (210),

#### characterized in that

the network of passive components is configured to generate a switch control signal for the rectification switch (210) by lowpass filtering the voltage across the rectification switch (210).

20

25

15

- 2. An isolated DC-DC power converter according to claim 1, wherein the network of passive components comprises a series connection of at least one inductor (Li), capacitor (Ci), and optionally a resistor (Ri) across the rectification switch (210) for example between drain and source terminals of a MOSFET switch or a GaN switch (210).

- 3. An isolated DC-DC power converter according to claim 1 or claim 2, wherein the resistor (Ri) is connected between a control terminal and an output terminal of the rectification switch (210).

30

4. An isolated DC-DC power converter according to claim 1, wherein the rectification switch (210) comprises a FET transistor, e.g. a Gallium

Nitride FET or a metal-oxide-semiconductor FET (MOSFET), or an insulated gate bipolar transistor (IGBT); and wherein the switch control signal is applied to a gate terminal or base terminal of said FET transistor.

5 S. An isolated DC-DC power converter according to claim 1, wherein the network of passive components comprises a lowpass filter configured to filter the voltage across the rectification switch (210); said lowpass filter having a cut-off frequency (frl) below a switching frequency of the modulated switch control signal.

10

30

- 6. An isolated DC-DC power converter according to claim 5, wherein the cut-off frequency (frl) of the lowpass filter is less than one-half of the switching frequency of the modulated switch control signal.

- 15 7. An isolated DC-DC power converter according to claim 5 or 6, wherein a Q value of the lowpass filter is larger than 3 such as larger than 5 or more preferably larger than 10.

- 8. An isolated DC-DC power converter according to any of claims 5-7, wherein the network of passive components additionally comprises a band-reject filter configured to filter the voltage across the rectification switch (21); said band-reject filter having a zero frequency (fr2) above the switching frequency of the modulated switch control signal such as at least three times higher than the switching frequency of the modulated switch control signal such as between three and five times higher.

- 9. An isolated DC-DC power converter according to any of the preceding claims, wherein the switching frequency of the modulated switch control signal is higher than 100 kHz, or higher than 1 MHz, more preferably higher than 5 MHz.

10. An isolated DC-DC power converter according to any of the preceding claims, wherein the modulated switch control signal comprises a Pulse-Width Modulated (PWM) signal or a frequency modulated (FM) signal to control an output voltage of the converter.

5

11. An isolated DC-DC power converter according to any of the preceding claims, further comprising an inrush current limiter (502) coupled to the switch driver circuit (208), said inrush current limiter (502) configured to disable the switch driver circuit (208) for a predetermined time period following power-on of the isolated DC-DC power converter.

10

12. A method of deriving a switch control signal of an active synchronous rectification circuit (206) of an isolated DC-DC power converter, the method comprising:

15

applying a modulated switch control signal to a controllable switch (204) connected in series with a primary winding (Lp) of an isolation transformer (T),

20

connecting an active synchronous rectification circuitry (206) to a secondary winding (Ls) of the isolation transformer (T) to couple a rectification switch (210) in series with the secondary winding (Ls);

deriving a switch control signal for the rectification switch (210) by lowpass filtering a voltage across the rectification switch (210) via a network of passive components; and applying the switch control signal to a control terminal of the rectification switch.

25

30

13. A method of deriving a switch control signal according to claim 12, wherein said lowpass filtering of the voltage across the rectification switch (210) has cut-off frequency (frl) below a switching frequency of the modulated switch control signal.

Fig. 1

Fig. 2

Fig. 3

4/10

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig. 8

9/10

Fig. 9

10/10

Fig. 10

#### INTERNATIONAL SEARCH REPORT

International application No

PCT/EP2020/052143

A. CLASSIFICATION OF SUBJECT MATTER

INV. H02M1/08 H02M3/335 H03K5/08 H03K17/08 H03K17/082

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H02M H03K

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

#### **EPO-Internal**

| Category*   | Citation of document, with indication, where appropriate, of the relevant passages                                                    | Relevant to claim No.        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| X<br>Y<br>A | US 2012/063175 A1 (WANG DONG [US] ET AL)<br>15 March 2012 (2012-03-15)<br>paragraphs [0010], [0057] - [0060],<br>[0063]; figures 3-14 | 1,12<br>2-7,<br>9-11,13<br>8 |

| Υ           | US 5 343 383 A (SHINADA YOHSUKE [JP] ET AL) 30 August 1994 (1994-08-30) column 4, lines 11-21; figures 1, 2A, 3A, 3B, 4               | 2-7,9,<br>10,13              |

| Y           | US 2016/211657 A1 (HAYASHI KEI [JP]) 21 July 2016 (2016-07-21) paragraphs [0090], [0095], [0133]; figure 10                           | 11                           |

| X Further documents are listed in the continuation of Box C.                                                                             | X See patent family annex.                                                                                                                                                                                                                 |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| * Special categories of cited documents :                                                                                                | "T" later document published after the international filing date or priority                                                                                                                                                               |  |  |  |

| "A" document defining the general state of the art which is not considered to be of particular relevance                                 | date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                                                                                                     |  |  |  |

| E " earlier application or patent but published on or after the international filing date                                                | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive                                                                                                     |  |  |  |

| "L" document which may throw doubts on priority claim(s) orwhich is cited to establish the publication date of another citation or other | step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination |  |  |  |

| special reason (as specified) "O" document referring to an oral disclosure, use, exhibition or other                                     |                                                                                                                                                                                                                                            |  |  |  |

| means                                                                                                                                    | being obvious to a person skilled in the art                                                                                                                                                                                               |  |  |  |

| "P" document published prior to the international filing date but later than the priority date claimed                                   | "&" document member of the same patent family                                                                                                                                                                                              |  |  |  |

| Date of the actual completion of the international search                                                                                | Date of mailing of the international search report                                                                                                                                                                                         |  |  |  |

|                                                                                                                                          |                                                                                                                                                                                                                                            |  |  |  |

| 15 April 2020                                                                                                                            | 23/04/2020                                                                                                                                                                                                                                 |  |  |  |

| Name and mailing address of the ISA/                                                                                                     | Authorized officer                                                                                                                                                                                                                         |  |  |  |

European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016

Kanelis, Konstantin

# **INTERNATIONAL SEARCH REPORT**

International application No

# PCT/EP2020/052143

|             |                                                                                                                                                                                                            | PC1/EP2020/052143     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| C(Continua  | tion). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                 |                       |

| Category*   | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                         | Relevant to claim No. |

| Category* γ | Citation of document, with indication, where appropriate, of the relevant passages  US 8 278 997 B1 (KIM SANGSUN [US] ET AL) 2 October 2012 (2012-10-02) column 8, lines 44-46; figures 2, 4, 6, 8, 11, 13 | Relevant to claim No. |

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/ EP2020/052 143

| Patent document cited in search report |    | Publication date |     | Patent family member(s) |           | Publication date |

|----------------------------------------|----|------------------|-----|-------------------------|-----------|------------------|

| us 2012063 175                         | A1 | 15-03 -20 12     | CA  | 275 1936                | A1        | 10-03 -20 12     |

|                                        |    |                  | US  | 2012063 175             | <b>A1</b> | 15-03 -20 12     |

| us 5343383                             | Α  | 30-08 - 1994     | JP  | 28 19932                | B2        | 05 - 11 - 1998   |

|                                        |    |                  | JР  | H05252737               | Α         | 28-09 - 1993     |

|                                        |    |                  | US  | 5343383                 | Α         | 30-08 - 1994     |

| us 2016211657                          | A1 | 21-07 -20 16     | CN  | 1055 18992              | Α         | 20-04 -20 16     |

|                                        |    |                  | DE  | 1120 13007409           | T5        | 09-06 -20 16     |

|                                        |    |                  | JР  | 6264379                 | B2        | 24-01-20 18      |

|                                        |    |                  | JР  | WO20 15033449           | A1        | 02-03 -20 17     |

|                                        |    |                  | US  | 20 162 11657            | A1        | 21-07 -20 16     |

|                                        |    |                  | wo  | 2015033449              | <b>A1</b> | 12-03 -20 15     |

| us 8278997                             | B1 | 02-10-20 12      | NON | ıE                      |           |                  |