**DTU Library**

## Directional Nanoscale Silicon Etching using $SF_6$ and $O_2$ Plasma

Nguyen, Vy Thi Hoang

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA): Nguyen, V. T. H. (2020). Directional Nanoscale Silicon Etching using  $SF_6$  and  $O_2$  Plasma. DTU Nanolab.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## Directional Nanoscale Silicon Etching using SF<sub>6</sub> and O<sub>2</sub> Plasma

Vy Thi Hoang Nguyen

A thesis submitted to Technical University of Denmark in partial fulfillment of the requirements for acquiring the degree of Doctor of Philosophy

November 30<sup>th</sup>, 2020

Supervisors: Professor Henri Jansen,

DTU Nanolab, Technical University of Denmark

Associate professor Flemming Jansen,

DTU Nanolab, Technical University of Denmark

Director Jörg Hübner,

DTU Nanolab, Technical University of Denmark

#### **DTU Nanolab**

National Center for Nano fabrication and Characterization Technical University of Denmark

Ørsteds Plads, Building 347 2800 Kongens Lyngby,

Denmark

Telephone: + 45 45 25 57 43 E-mail: info@nanolab.dtu.dk

## **Preface**

During the past three years, I have had great opportunities to meet and work with many wonderful people who directly or indirectly influenced me to become what I am today. This is a special moment for me to look back and express my gratitude to all of them.

The first and deepest thank goes to my supervisor, Henri Jansen for his enthusiatic guidance and continuous encouragement over the years. He is such a supportive supervisor who spends most of the time in cleanroom to accompany, discuss and guide me through difficult experimental designs. Without his supervision, I would not be able to overcome numbers of challenges in this thesis. He is not only a supervisor but also a special friend whom I can trust and talk comfortably about any issue in my life.

I wish to give sincerest thanks my other supervisors, Flemming Jensen and Jørg Hubner for always being available whenever I have concerns about the research goals or administrative processes. Their comments, discussion and orientation have contributed greatly to the development of this thesis. Without their inputs, this thesis would have not been completed.

I would like to thank all the staffs at DTU Nanolab for giving me access to cleanroom equipment and providing me with the necessary technical supports. Thank Bingdong Chang for his help and advice in the first year when I just started and was not familiar with the system. Thank Anita Stick who has prepared and arranged very well for my enrolment at DTU Nanolab. Thank to her help, all the administrative works related to my project went so smoothly and correctly. I also would like to thank people at Mesa+, the Netherlands for hosting my external stay. Special thanks to Kechun Ma, Meint De Boer, Erwin Berenschot, Niels Tas for their warming welcome, good discussion and support during my stay.

I want to thank my best friends in Viet Nam: Ha, Thu, Nhi, chi Hien, chi Linh for always caring and worrying about me. I know that I am not alone even we are so far away. I also want to thank friends in Denmark: Mai, anh Tuan, chi Thuy, anh Nhut, anh Ngu, chị Yen, Khoa, Vy, Thuan, Trang for all the good time we have had together. A special thank to Hoa for his introduction and inspiring me to follow the academic road in Denmark. His working experience is always valuable for me.

Finally and most importantly, I am grateful to my parents Nguyen Tung and Hoang Thi Hue, my sister Nguyen Thi Hoang Thu, my brother Nguyen Van Hoang Hai for their unconditional love, care and supports. They are the biggest motivations for me to accomplish this thesis.

Kongens Lyngby, November 30<sup>th</sup> 2020 Vy Thi Hoang Nguyen

## **Abstract**

Plasma etching is important to realize fine geometry for the fabrication of silicon nanostructures. The Bosch process is probably the most popular technique in the nanofabrication industries today. However, the high roughness with finite sidewall scallop size and hard to remove fluorocarbon residue on the sidewalls of etched structures make the process less favorable for nanoscale engineering. This PhD project focuses on the development of a reliable and stable technology for nanoscale silicon plasma etching which addresses both issues. The specific contributions of this thesis are summarized below.

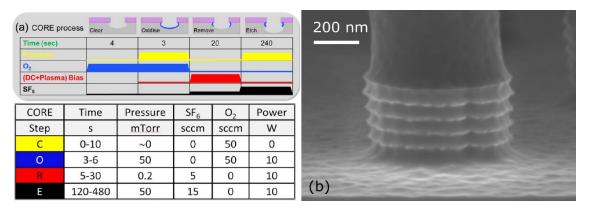

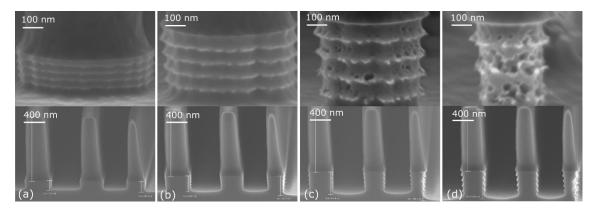

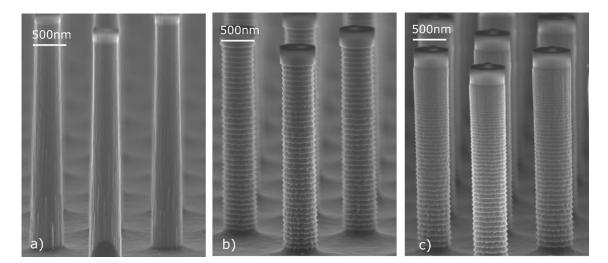

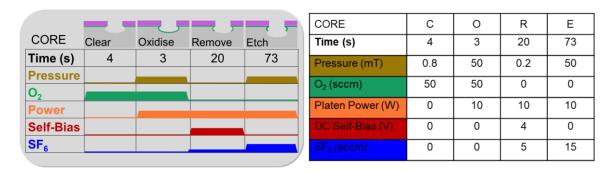

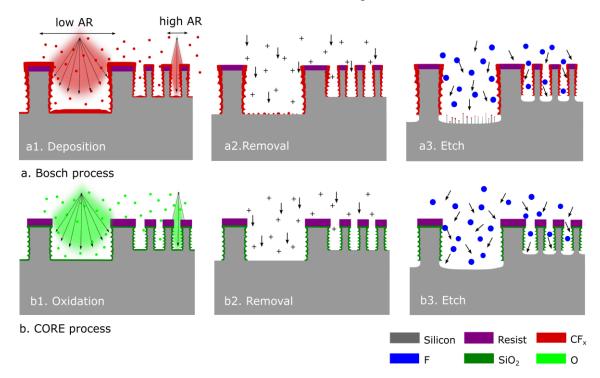

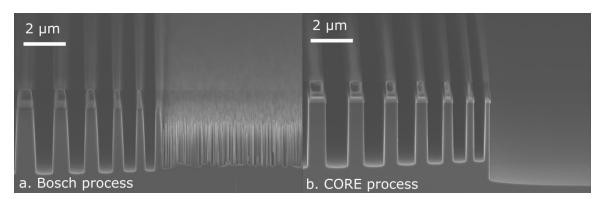

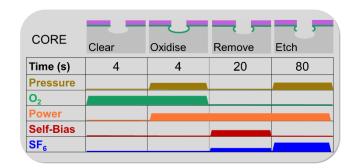

First, a fluorocarbon-free directional silicon etching procedure called CORE (stands for Clear, Oxidize, Remove, and Etch) has been developed in which a switching sequence of SF<sub>6</sub> and  $O_2$  is operated at room temperature. Compared to other etch processes, the CORE sequence has the advantage of precise profile control, high selectivity, small sidewall roughness and flexible process programming. It also shows an excellent performance in nanoscale structures with an accurate and controllable etch rate between 1 and 50nm/min (and  $SiO_2$ -selectivity of ca. 35) using the etch-tool in the RIE-mode. By adding the ICP source (DRIE-mode), a directional etch rate up to  $1\mu$ m/min and selectivity >200 for  $SiO_2$  is possible.

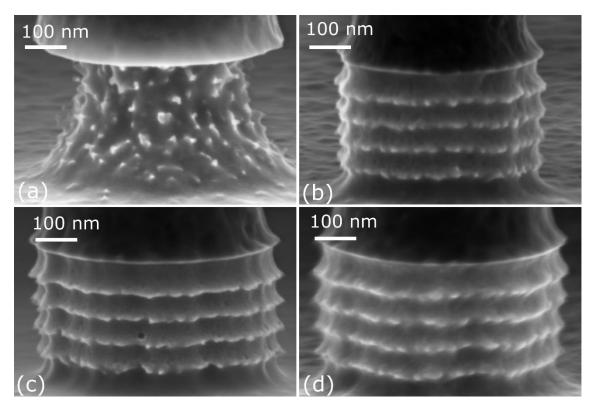

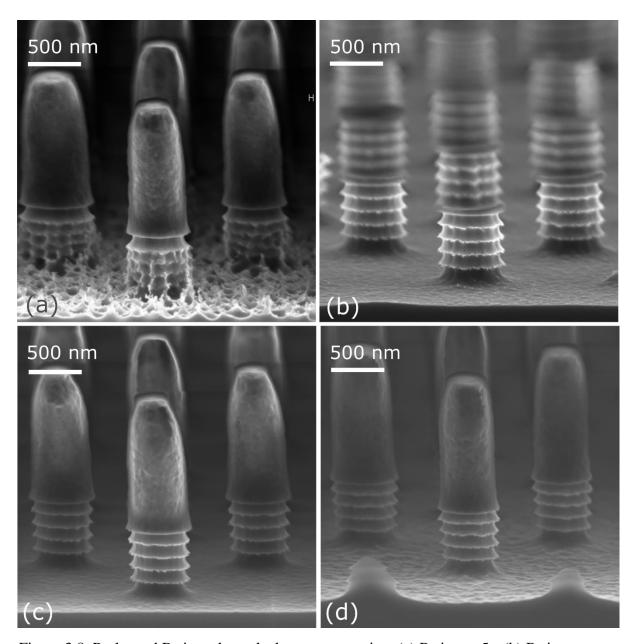

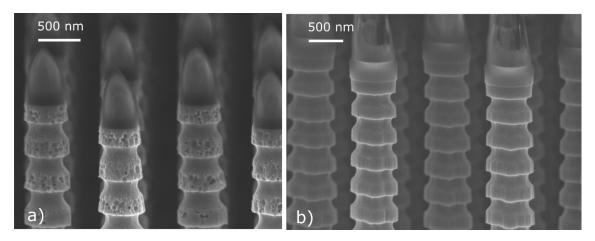

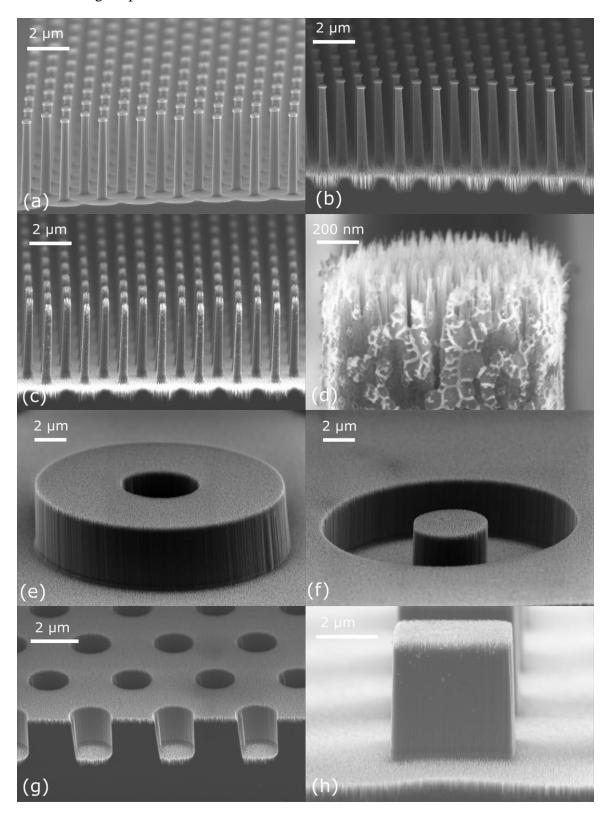

Second, the formation of black silicon (BSi) in SF<sub>6</sub>/O<sub>2</sub> plasma has been investigated based on the CORE sequence. By manipulating its parameters and utilizing the self-limiting property of the oxidation step, the CORE sequence can easily be modified to create either BSi-full or BSi-free surfaces independent of the aspect ratio of the etch features. The latter distinguishes the BSi formation clearly from other directional processes, thus provides a versatile tool for creating BSi anywhere at anytime, as it is called 'BSi on Demand'.

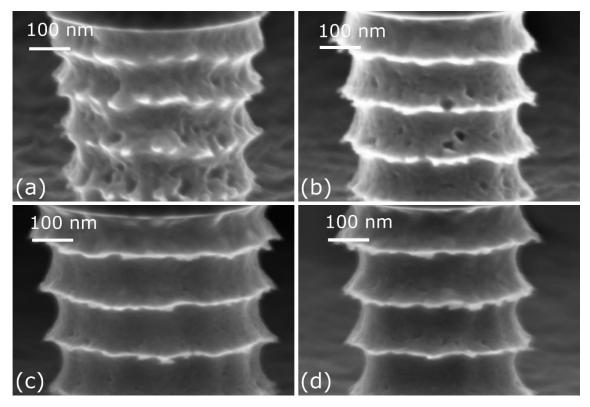

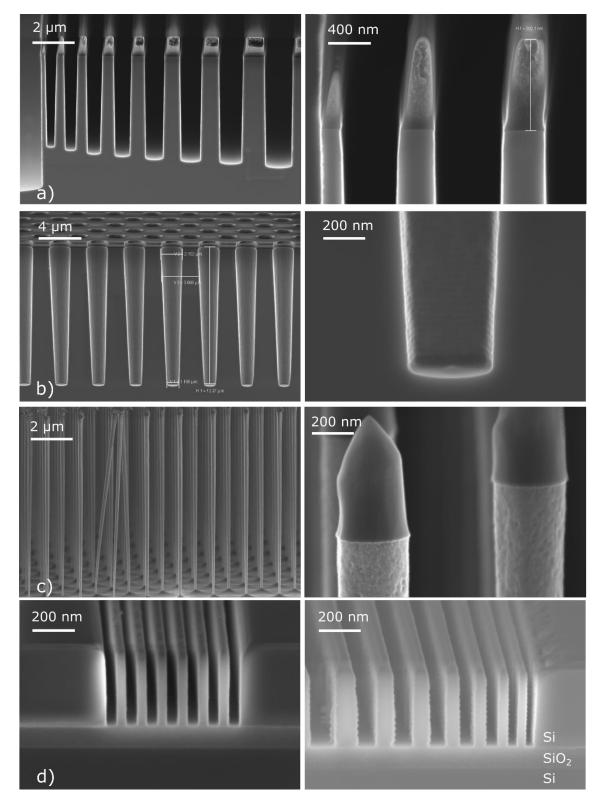

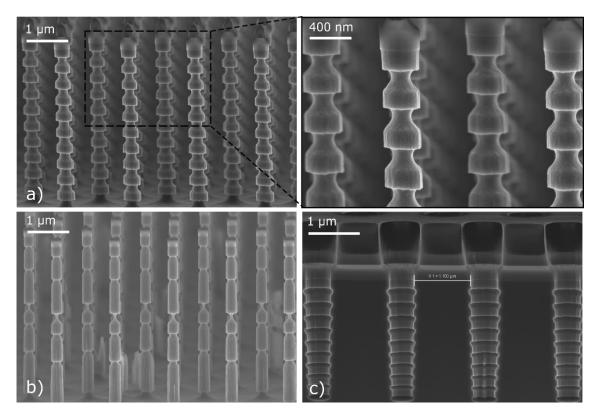

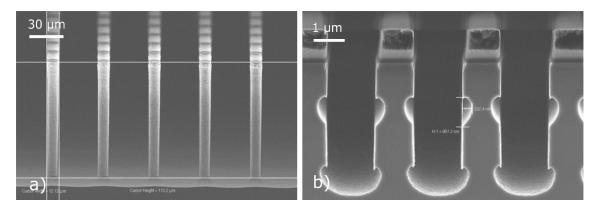

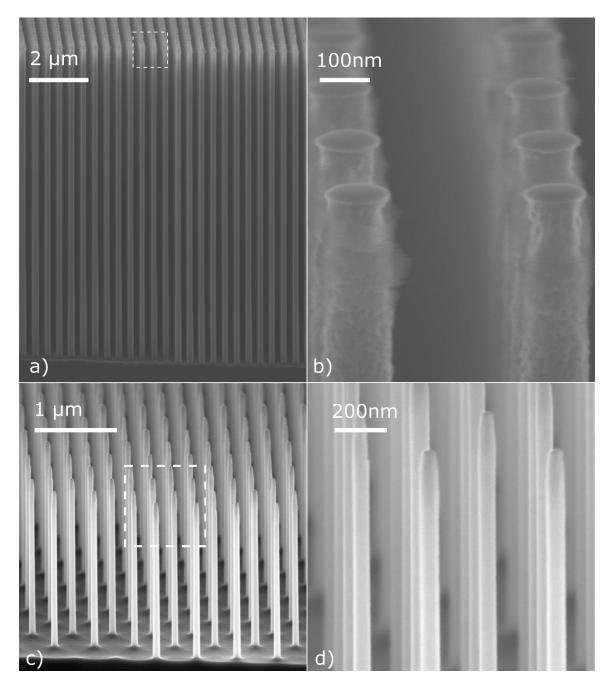

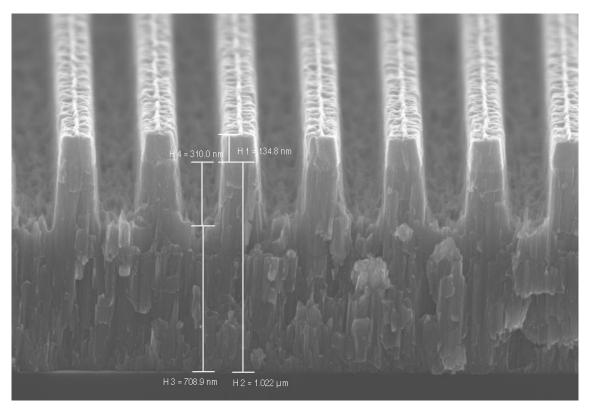

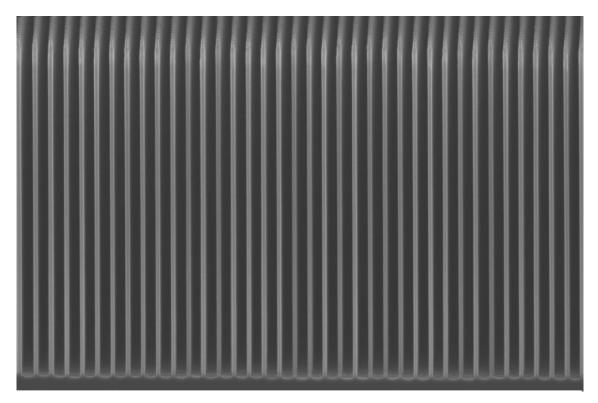

Third, the performance of the CORE sequence has been demonstrated to fabricate ultrahigh aspect ratio (HAR) nanofeatures. The effect of different CORE parameters on the etch rate and profile are investigated and optimized with respect to low mask undercut and high directionality (vertical) etch. The nanopillar arrays (200nm diameter, 400nm pitch and 60nm diameter, 500nm pitch) have smooth straight sidewalls with aspect ratios beyond 55 for gaps and up to 200 for pillars. Due to the very mild plasma condition (less than 40W RIE power), the mask selectivity can be tuned above 500.

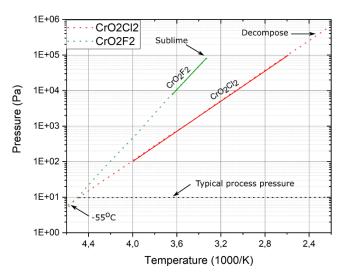

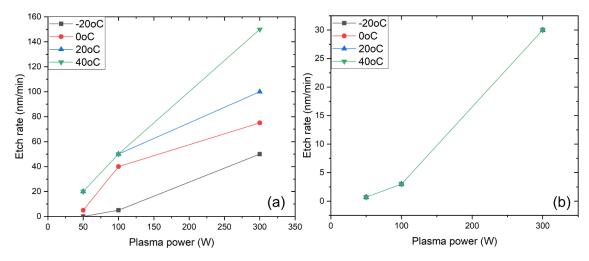

Finally, a procedure for Cr etching using SF<sub>6</sub> and O<sub>2</sub> plasma has been demonstrated for the first time. The etch mechanism is explained by considering the formation of volatile chromyl fluoride in which the Cr is first reacting with oxygen radicals and the formed CrO<sub>x</sub> subsequently reacts with fluorine radicals into CrO<sub>2</sub>F<sub>2</sub>. For the mixed mode, the proposed etch procedure performs at 300W plasma power with etch rates of Cr up to

150nm/min for a  $SF_6/O_2$  gas ratio below 1%. For the switched mode, the etch rate is around 7nm/min with high selectivity with respect to silicon (> 20) and better profile control.

## Resumé

Plasmaætsning er en vigtig metode til realisering af højt opløste geometriske emner ved fremstilling af nanostrukturer i silicium. Den såkaldte Bosch proces er formentlig den mest fremherskende teknik indenfor nanofabrikations-industrien i dag. I denne forbindelse er den høje ruhed som følge af korrugerede sidevægge, såkaldte "scallops", og rester af fluorcarbon-baserede forbindelser, problemer, som gør Bosch-processen mindre favorabel indenfor nanoskala fremstillingsmetoder. Det foreliggende PhD projekt omhandler udviklingen af en pålidelig og stabil nanoskala plasmaætsnings-teknologi i silicium, som adresserer begge problemstillinger. De specifikke bidrag fra denne afhandling er opsummeret i det følgende.

For det første er en fluorcarbon-fri retningsbestemt siliciumæts-procedure kaldet CORE (forkortelse af de engelske udtryk Clear, Oxidize, Remove og Etch) blevet udviklet, i hvilken alternerende sekvenser af SF<sub>6</sub> and O<sub>2</sub> benyttes ved stuetemperatur. Sammenlignet med andre ætseprocesser har CORE processen fordele ved præcis profilkontrol, høj selektivitet, lav sidevægsruhed og fleksibel procesprogrammering. Den demonstrerer ligeledes fremragende resultater for nanoskala strukturer med nøjagtige og kontrollerbare ætserater mellem 1 og 50 nm/min (og en SiO<sub>2</sub>-selektivitet på ca. 35) ved brug af ætseudstyret i RIE-tilstand. Når ICP-kilden tilføjes (DRIE-tilstand) er det muligt at opnå en retningsbestemt æts med ætserate op til 1µm/min og selektivitet >200 for SiO<sub>2</sub>.

For det andet er dannelse af "sort silicium" (engelsk: black silicon (BSi)) ved ætsning i et  $SF_6/O_2$  plasma, baseret på CORE-sekvensen, blevet undersøgt. Ved justering af dens parametre og udnyttelse af den selvbegrænsende egenskab af oxidationssteppet kan CORE-sekvensen let modificeres til enten at frembringe hele BSi overflader eller BSi-fri overflader uafhængigt af aspektforholdet for de ætsede strukturer. Denne egenskab adskiller dannelsen af BSi klart fra andre retningsbestemte ætseprocesser og giver dermed et alsidigt værktøj til fremstilling af BSi "hvor som helst" til "ethvert tidspunkt" og derfor betegnelsen "BSi efter behov".

For det tredie er det med CORE-sekvensen blevet demonstreret muligt at frembringe nanostrukturer med ultra-højt aspektforhold. Effekten af forskellige CORE-parametre på ætserate og ætseprofil er blevet undersøgt og optimeret med henblik på minimering af maske-undersæts og forbedring af retningsbestemt (vertikal) æts. Rækker af ætsede nanosøjler (200nm diameter, 400nm repetitionsafstand og 60nm diameter, 500nm repetitionsafstand) fremviser glatte, rette sidevægge med aspektforhold mellem 55 for huller og op til 200 for søjler. På grund af de meget milde plasma betingelser (mindre end 40 W RIE effekt) kan maskeselektiviteten justeres til over 500.

Endelig er der for første gang demonstreret en procedure for Cr-ætsning baseret på et  $SF_6$  og  $O_2$  plasma. Ætsemekanismen forklares ud fra dannelsen af chromylfluorid, hvor Cr indledningsvis reagerer med O-radikaler, hvorefter den dannede  $CrO_x$  reagerer med F-radikaler, hvilket resulterer i  $CrO_2F_2$ . Ved "mixed mode" kørsel med 300 W plasmaeffekt resulterer den foreslåede ætseprocedure i Cr ætserater op til 150nm/min for et  $SF_6/O_2$  gasforhold mindre end 1%. Ved "switched mode" kørsel er ætseraten omkring 7nm/min med høj selektivitet i forhold til silicium (> 20) og med bedre profilkontrol.

## **Table of Contents**

| Preface                                                                                                             | i   |

|---------------------------------------------------------------------------------------------------------------------|-----|

| Abstract                                                                                                            | iv  |

| Resumé                                                                                                              | vi  |

| Chapter 1. Introduction                                                                                             | 1   |

| 1.1. Background and motivation                                                                                      | 1   |

| 1.2. Thesis objectives                                                                                              |     |

| 1.3. Thesis outline                                                                                                 | 5   |

| References                                                                                                          | 7   |

| Chapter 2. Introduction of plasma etching                                                                           | 10  |

| 2.1. Basics of plasmas                                                                                              | 10  |

| 2.1.1. Plasma and collision process in a plasma                                                                     |     |

| 2.1.2. Plasma parameters                                                                                            | 13  |

| 2.1.3. DC bias, ion sheath and ion motion in the sheath                                                             | 14  |

| 2.2. Introduction of plasma etching                                                                                 | 16  |

| 2.2.1. Etching mechanism                                                                                            |     |

| 2.2.2. Mechanism of anisotropic etching                                                                             |     |

| 2.2.3. Characterization of the etch performance                                                                     |     |

| 2.3.4. Etch profiles obtained after the plasma etching                                                              |     |

| 2.3. Silicon etching using fluorine-based plasma                                                                    |     |

| 2.3.1. Mixed mode                                                                                                   |     |

| 2.3.2. Switched mode                                                                                                |     |

| Reference                                                                                                           |     |

| Chapter 3. The CORE sequence                                                                                        | 30  |

| 3.1. Introduction                                                                                                   | 31  |

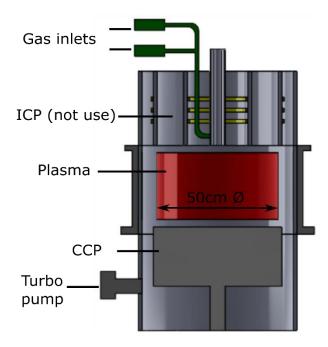

| 3.2. Equipment and experimental                                                                                     | 35  |

| 3.3. Results.                                                                                                       |     |

| 3.3.1. Development of the CORE process                                                                              |     |

| 3.3.2. Demonstration of the CORE process                                                                            |     |

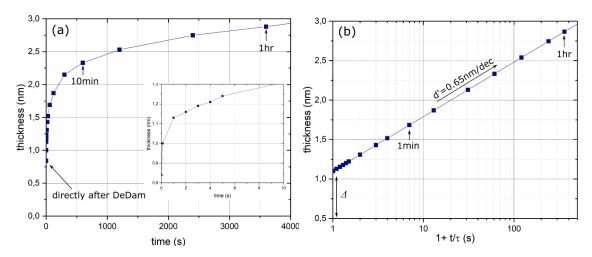

| 3.3.3. Plasma oxidation and the self-limiting property                                                              |     |

| 3.5. Conclusions                                                                                                    |     |

| References                                                                                                          | 53  |

| Chapter 4. On the formation of Black Silicon in SF <sub>6</sub> -O <sub>2</sub> plasma: The Grand and BSi or Demand |     |

| sequence and BSi on Demand                                                                                          |     |

| 4.1. Introduction                                                                                                   |     |

| 4.2. Materials and Methods                                                                                          |     |

| 4.3. Results and Discussions                                                                                        |     |

| 9. J. L. CHALACICHNUC OF DOLLHEIDE DOSCH AHU HIE CAUNE SEGMENCE                                                     | 0.1 |

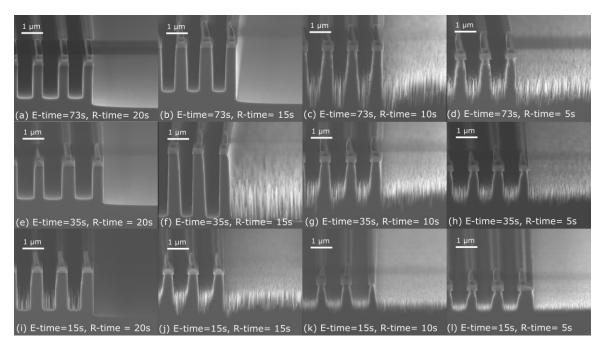

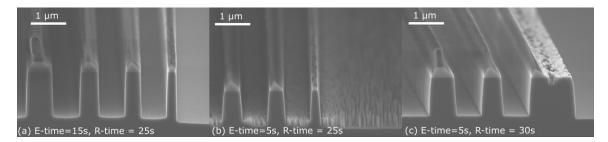

| 4.3.2. The effect of R-step on the formation of BSi                                               | 64  |

|---------------------------------------------------------------------------------------------------|-----|

| 4.3.3. The effect of E-step on the formation of BSi                                               | 65  |

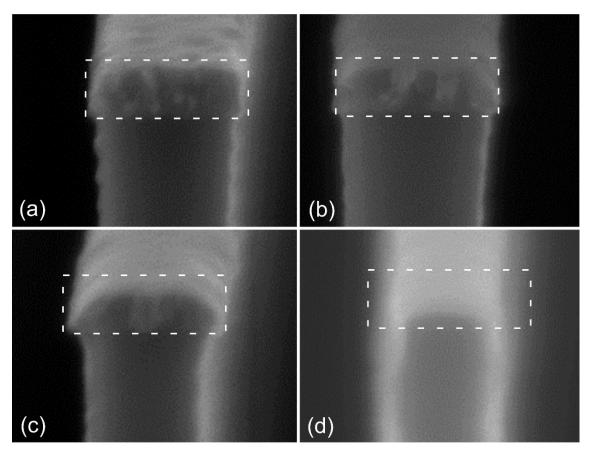

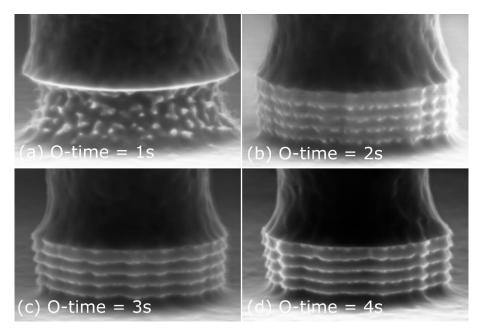

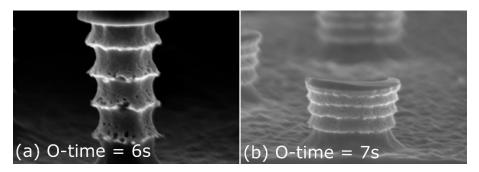

| 4.3.4. The effect of O-step on the formation of BSi                                               | 67  |

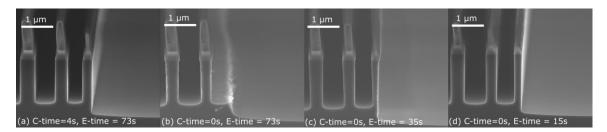

| 4.3.5. The effect of C-step on the formation of BSi                                               |     |

| 4.3.6. Black silicon on demand                                                                    | 68  |

| 4.4. Conclusions                                                                                  | 70  |

| References                                                                                        | 70  |

| Chapter 5. Ultrahigh aspect ratio etching of silicon in $SF_6$ - $O_2$ plasma:                    |     |

| sequence and chromium mask                                                                        | 73  |

| 5.1. Introduction                                                                                 | 74  |

| 5.2. Materials and Methods                                                                        | 74  |

| 5.3. Results and Discussions                                                                      | 76  |

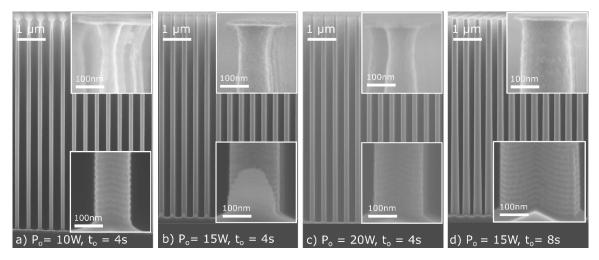

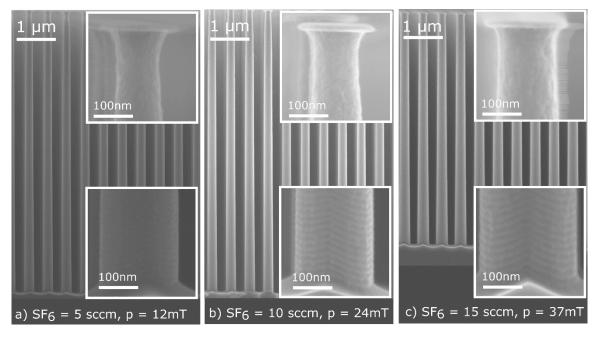

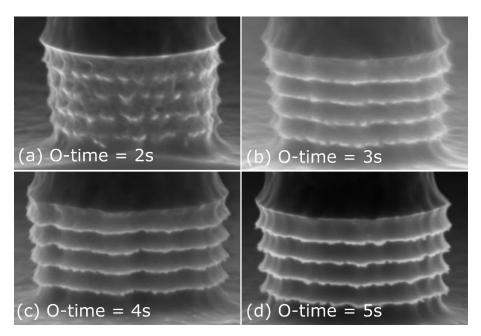

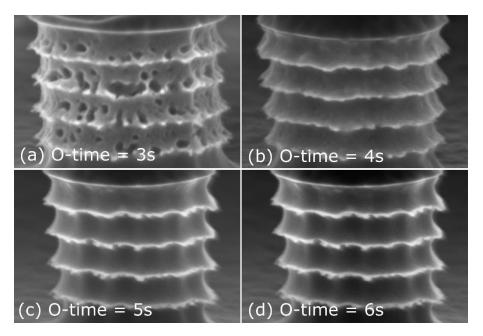

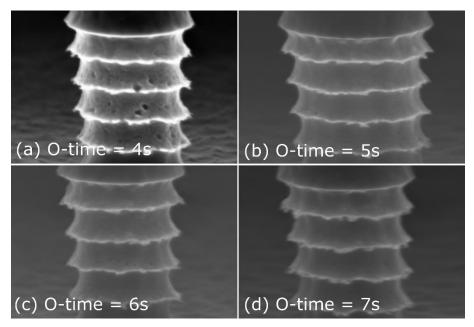

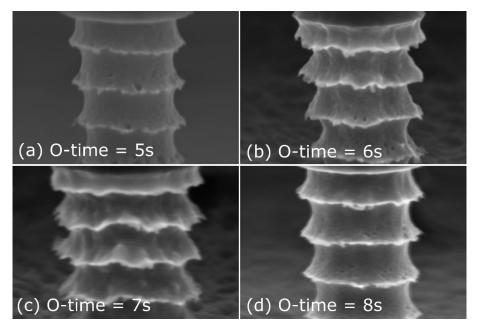

| 5.3.1. The effect of O-parameters                                                                 | 77  |

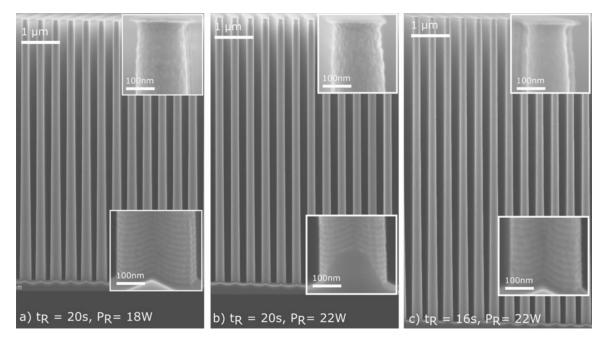

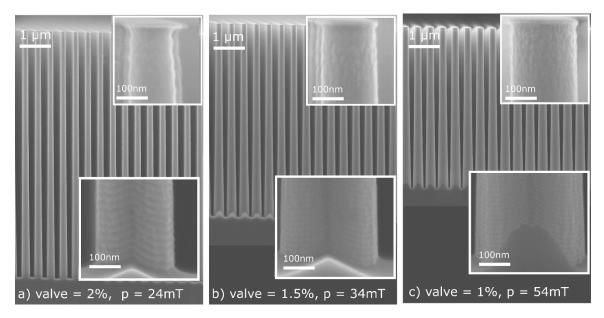

| 5.3.2. The effect of R-parameters                                                                 | 78  |

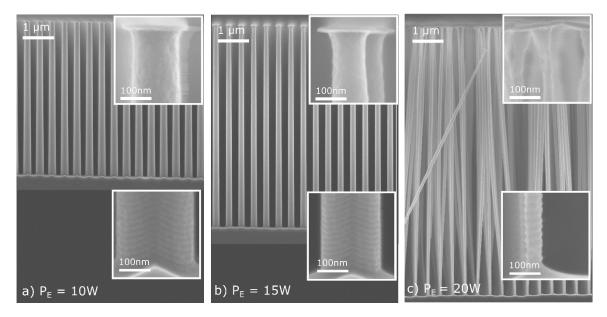

| 5.3.3. The effect of E-parameters                                                                 | 78  |

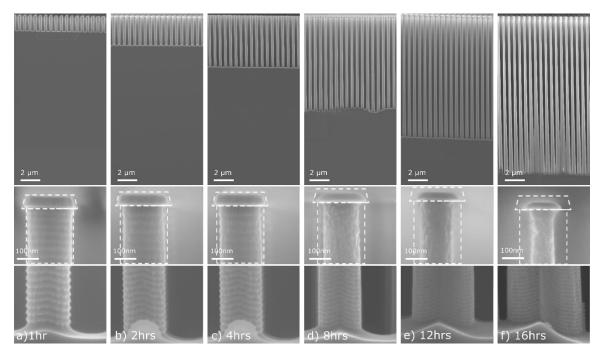

| 5.3.4. The effect of total etch time                                                              |     |

| 5.3.5. Ultra-HAR silicon etching                                                                  |     |

| 5.3.6. Chromium mask etching and retraction                                                       |     |

| 5.3.7. The effect of the carrier wafer                                                            |     |

| 5.4. Conclusions                                                                                  |     |

| References                                                                                        | 88  |

| Chapter 6. Cr and CrO <sub>x</sub> Etching using SF <sub>6</sub> and O <sub>2</sub> Plasma        | 91  |

| 6.1. Introduction                                                                                 | 91  |

| 6.2. Materials and Methods                                                                        | 94  |

| 6.3. Results and Discussion                                                                       |     |

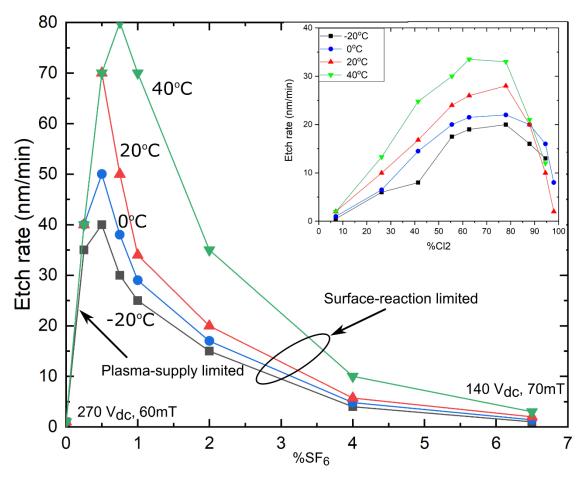

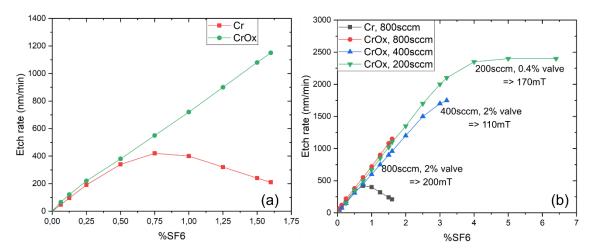

| 6.3.1. The effect of SF <sub>6</sub> /O <sub>2</sub> ratio on the Cr etch rate                    |     |

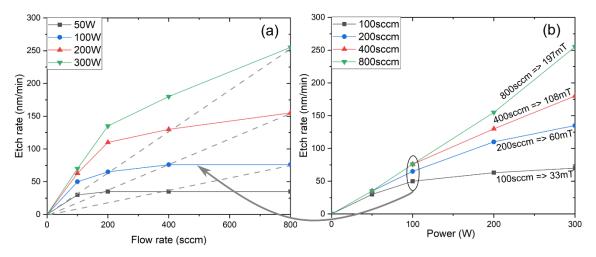

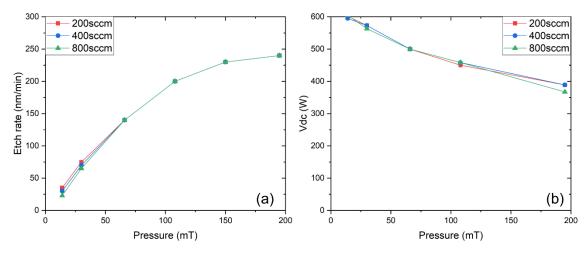

| 6.3.2. The effect of plasma power and gas flux on the Cr etch rate                                |     |

| 6.3.3. The effect of SF <sub>6</sub> /O <sub>2</sub> ratio on the CrOx etch rate                  |     |

| 6.3.4. The etching mechanism of Cr and CrO <sub>x</sub> in SF <sub>6</sub> +O <sub>2</sub> plasma |     |

| 6.3.5. Cr patterning using SF <sub>6</sub> and O <sub>2</sub> plasma                              |     |

| 6.4. Conclusion                                                                                   |     |

| References                                                                                        | 108 |

| Chapter 7. Conclusions and Outlook                                                                | 111 |

| 7.1. Conclusion                                                                                   | 111 |

| 7.2. Outlook                                                                                      | 113 |

| Appendix A. The CORE sequence                                                                     | 115 |

| Appendix B. Abbreviation                                                                          | 118 |

| Annendix C. List of publication                                                                   |     |

## Chapter 1. Introduction

#### 1.1. Background and motivation

Advances in the semiconductor industry in recent years has been attributed to the development of very large scale integration (VLSI) technology in which various functional devices are built into a small chip size with improved performance. Many VLSI devices such as microprocessors, central process unit (CPU), dynamic random access memory (DRAM), etc. are growing quickly with the device density continue to double approximately every 2 years following the exponential growth of Moore's law<sup>1</sup>. In addition to density increases, the device scaling also plays an important role in the development of VLSI technology. It is estimated that the minimum feature size of the VLSI devices has been shrunk down approximately by 30% every 2-3 years, and a process that enables 3nm feature size has been established in 2020 by IMEC (Leuven, Belgium) and ASML (Veldhoven, Netherlands)<sup>2-4</sup>.

To realize a high VLSI device density, it requires a large number of devices integrated into a single chip and an effective approach is to make each device as small as possible. The key for achieving this is based on fine geometry processing which is comprised of three basic pillars – deposition, lithography and etching – placed in an arbitrary adaptable sequence of process steps to create the requested devices. Until recently, focus has been directed to upgrade the lithographic tools to decrease the lateral resolution. Following the development of photolithography, etching technologies have also participated in the race towards smaller dimensions and high density. With the lithographic tools pushing the critical dimension further down and the improvement of etch tools/recipes, the dimensions of micro electromechanical systems (MEMS) devices are rapidly decreasing and commercial nano electromechanical systems (NEMS) are underway.

The scaling down scenario in the semiconductor industry, however, is about to reach its limitations because of the technical challenge in improving device performance and power assumption at the shrinking size. To overcome this barrier, the VLSI technology is forced to further evolve and a lot of research study is focusing on the replacement of conventional planar devices by nonplanar structures to enable the increasing of device

density or functionality per cubic centimeter. In 2007, Tanaka et al. proposed a threedimensional (3D) gate stack NAND flash memory consists of stacked layers of poly-Si and the insulating film one after the other to increase the device density<sup>5</sup>. This 3D structure is called bit-cost scalable (BiCS) flash memory and is promising for ultrahigh density memory. A similar transition from planar to 3D devices can also be observed in logic transistors such as fin field-effect transistor (FinFET) that results in the development of a vertical transistor with a gate-all-around (GAA) structure<sup>6,7</sup>. These complex structures create stringent technical challenge on the fabrication technologies. For example, fabrication of 3D gate stacks requires an etching technology capable of opening high aspect ratio holes in a single step through all the stacked layers. Etching technology is also important in the fabrication of through-silicon vias (TSVs) for chip-to-chip connections in the 3D integrated circuits<sup>8,9</sup>. Large cavities are etched for subsequent chips or wafer scale packaging and sensor structures may comprise multi-wafer stacks with one or more having through wafer etches. Therefore, the etching technology needs to be developed for high speed etching with excellent profile control but still able to offer low rate for etching thin gate film.

In the early days of integrated circuits processing, the etching technology was mainly based on wet chemicals to transfer the lithographic patterns into the target film. In 1970s, plasma etching was introduced and quickly replaced wet etching to become the mainstream etching technology in semiconductor industry<sup>10,11</sup>. During the plasma process, gas species (e.g. SF<sub>6</sub>, CHF<sub>3</sub>, O<sub>2</sub>, etc.) are injected into a vacuum chamber and ionized (by radio frequency, microwave, etc.) to generate the etching chemistry consisting of reactive radicals, electrons and ions with high energy. The use of plasma to clean or transfer patterns was motivated primarily by the need to reduce the chemical waste associated with the use of wet etchants. However, other advantages of plasma etching later became more apparent such as the possibility to create highly anisotropic profiles without depending on the crystal orientation and the ability to achieve high aspect ratio structures.

The development of plasma etching for patterning semiconductor devices has evolved along two main paths: physical (sputtering) and chemical etching. Each path has different fabrication mechanisms and goals. The sputtering method is needed when there is no chemical etchants available to etch a specific substrate materials or when the patterning could not be easily accomplished by wet etching. For example, in the fabrication process of beam-leads devices, it is hardly possible to use chemical etchants to etch the platinum and titanium below the gold layer because the chemicals used to etch platinum (e.g. aqua regia) can etch the gold much faster<sup>12</sup>. Therefore in this case, the devices patterning is carried out only by utilizing an energetic ion flux to physically sputtering the platinum layer<sup>13,14</sup>. The typical sputtering equipment uses a blocking capacitor to couple a radio frequency (RF) generator to the electrode on which the substrate has been placed<sup>15</sup>. With this configuration, a negative bias is produced on the wafer electrode and the energetic ions will be accelerate toward this bias electrode to bombard the substrate. The sputtering

method has a disadvantage of redeposition of materials that results in the positively tapered etch profiles with low selectivity and low etch rates <sup>16,17</sup>. The second path, the chemical plasma etching, is intended to use as an alternative of wet etching in the fabrication of integrated circuits. It is characterized by the minimal ion bombardment and purely chemical etching. The chemical plasma etching started when Stephen Irving demonstrated the ability of using oxygen plasma to strip photoresist and later on recognized the possibility of using either fluorine or chlorine-based compounds for etching other materials (e.g. SiO<sub>2</sub> or aluminum)<sup>18,19</sup>. A classical reactor type for chemical plasma etching is the barrel in which wafers were placed in a quartz chamber with external electrodes<sup>20</sup>. A RF generator is applied across the electrodes to create the plasma when the appropriate gas is introduced into the chamber. This configuration is adequate for resist stripping but suffers from poor etch uniformity which is important for the device processing. In a further development, a parallel plate reactor is introduced in which the wafers are placed on the ground electrodes while RF is applied to the opposite one<sup>21</sup>. This approach gives high etch rates and selectivity but with an isotropic etch profiles.

These two paths in plasma etching converged when Hosokawa et al. introduced fluorine and chlorine-based gases (e.g. CF<sub>4</sub>, CCl<sub>2</sub>F<sub>2</sub>, CCl<sub>3</sub>F, etc.) into a RF sputtering apparatus in order to enhance the etching rate of various materials<sup>22</sup>. This innovated technique, now called reactive ion etching (RIE) or ion enhanced plasma etching, has become the method of choice for pattering devices in the semiconductor industry<sup>23</sup>. Due to the combination of the physical sputtering and chemical activity of reactive radicals, it enables the achievement of profiles control with high etch rate and selectivity<sup>24</sup>. Depending on the gas chemistry, a wide range of materials such as silicon, silicon oxide, aluminum, chromium, etc... can be etched with a high level of fidelity making the fabrication of complex devices more practicable. In this thesis we will focus on the technical development in plasma etching of silicon as it is a favorable material in semiconductor industry with an appropriate bandgap (around 1.12eV), high refractive index (~ 3.88 at wavelength of 632nm) and other superior properties<sup>25</sup>. Silicon can be etched in the halogen based (e.g. fluorine, chlorine and bromine) plasma with the gas of choice depends on specific applications. In general, Cl- and Br-based plasma are primarily used to achieve anisotropic etch profiles while F-based plasmas are used for isotropic etching because of the spontaneous reaction of the F radicals with silicon<sup>26</sup>. The F-based plasmas also etch silicon faster than the Cl- or Br-based plasma. Therefore, for applications such as micromachining for MEMS devices or TSVs when larger depths or heights must be created in silicon, F-based plasmas are the better choice.

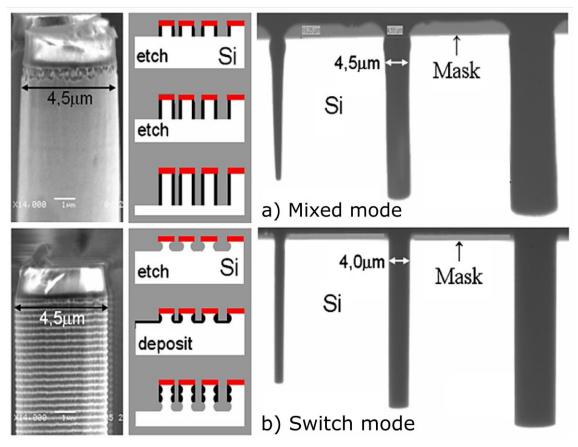

Although requirements for the etching performance may be different depends on specific devices and applications, there is still a standard criteria for a plasma etching process in which the etch profiles are expected to be anisotropic with minimize undercut and high etch rate. Since silicon is etched spontaneously in F-based plasmas causing in large undercut of the mask, different techniques has been developed to prevent this isotropic nature. Zhang et al. proposed a mixed process in which the etching gas SF<sub>6</sub> and the O<sub>2</sub>

inhibitor gas are introduced into the chamber at the same time resulting in a reasonable directional etch profile with less undercutting<sup>27</sup>. However, this technique comes with a weak sidewall protection and the etch profiles are pattern dependent (e.g. smaller trenches generally show a more positive tapered profile than the wider ones<sup>28</sup>). In 1988, Tachi et al. demonstrated that the horizontal silicon etch rate can be reduced drastically by cooling the substrate to below -100°C and highly anisotropic etch profiles can be obtained<sup>29</sup>. This is because at low temperature, the created silicon oxy fluoride (SiO<sub>x</sub>F<sub>y</sub>) products start to freeze at the surface, thus improves the sidewall protection. This method is commonly known as cryogenic etching and has been studied intensively in the past years<sup>30-32</sup>. However, the pattern dependency cannot be removed in this way and mixed mode etch recipes are typically highly design specific that requires cumbersome optimizations.

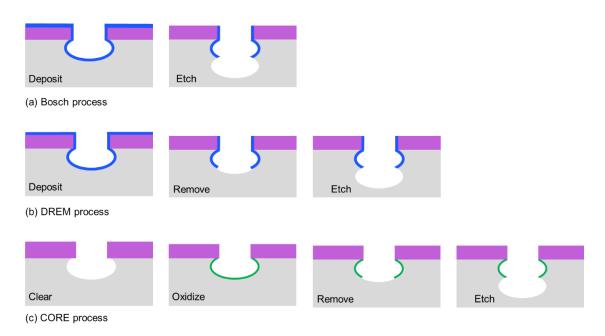

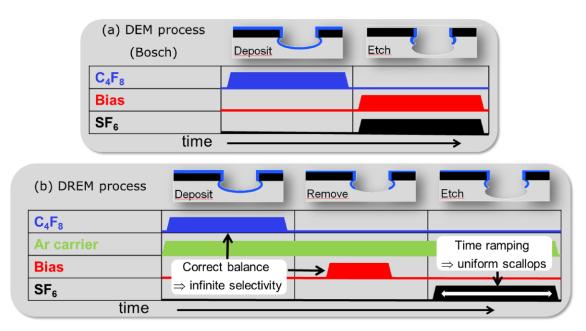

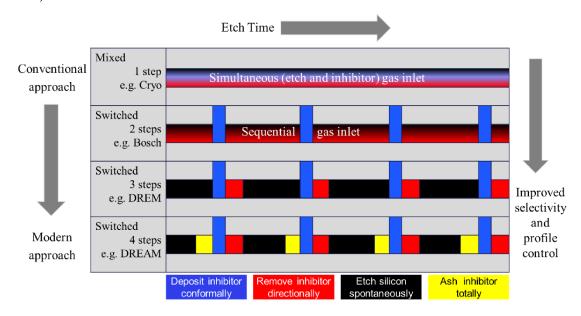

With the introduction of the patented 2-steps Bosch process in 1994, the switched etching of complicated structures gained popularity and becomes probably the most popular technique in MEMS production facilities today<sup>33,34</sup>. It uses a repeating sequence of plasma enhanced deposition to passivate silicon features, a physical etch for directional removal of this layer at the base of the features, and an isotropic etch for silicon removal at the cleared surfaces. The Bosch process creates prominent scallops, but it also forms nice directionality and the pattern dependency almost vanishes, which makes process optimization relatively easy. Moreover, it enables a better selectivity than mixed mode because bias is only applied during the etch step and not continuously. The Bosch process can be further improved by decoupling the bias from the etch step and forming the 3-steps process called DREM (Deposit, Remove, and Etch Many times)<sup>35</sup>. Compare with the traditional Bosch process, the DREM process has the advantage of higher etch selectivity, uniform sidewall roughness and better control of the etch process.

Although it is widely used, the switched process is not well suited to the nanoscale due to finite sidewall scallop size and undercut unless rate and selectivity are severely compromised. Typically it is not applied below 500nm trench feature sizes – although 200nm features have been demonstrated<sup>35</sup>. Transport effects 'down the etched cavity' limit rate and selectivity while aspect ratios, profile and passivation control are more challenging. For example, aspect ratios beyond 30 are rarely utilized and fluctuations in the results are common. Another RIE technique called atomic layer etching (ALE) has been proposed to etch silicon at nanoscale<sup>36</sup>. It uses chlorine-based plasma and exploit the self-limiting property of reaction between chlorine and silicon surface to create a monolayer of nonvolatile silicon chlorides (SiCl<sub>4</sub>). This nonvolatile SiCl<sub>4</sub> monolayer then can be removed by a mild argon ion bombardment. The ALE technique claims to be able to control the etch depth in atomic resolution and transfer patterns with atomic-scale fidelity while maintaining both the material properties and feature dimensions<sup>37</sup>. However, the limited etch rate and low mask selectivity limit the flexibility of this technique for various application purposes.

Understanding the increasing demands and technical challenges in silicon etching at nanoscale, this PhD project aimed to develop a technology for nanoscale silicon plasma etching towards a reliable and sustainable solution which addresses these issues. The project objectives are presented in the next section.

#### 1.2. Thesis objectives

In this project, the usability of SF<sub>6</sub> and O<sub>2</sub> plasma will be studied as a replacement for Bosch process to avoid fluorocarbon (FC) residue and facilitate the nanoscale silicon etching with profile control and sufficient mask selectivity preferably at room temperature. The aim is to get a fundamental understanding of the special challenges involved in etching silicon at nanoscale including the physics and chemistry involved. Based on this understanding, a reliable and sustainable technology for nanoscale silicon etching will be established for future application. Specific goals include:

- Develop a generic procedure for directional etching of silicon based on SF<sub>6</sub>/O<sub>2</sub> plasma which is able to operate at room temperature to prevent thermal runaway. The etch profiles are required to be controllable (e.g. straight, positive or negative tapered) with minimized sidewall roughness and pattern independent. The developing etching procedure should perform excellent at nanoscale accuracy with a low etch rates but still be able to perform for microstructures without the need for further process optimization in between. In addition, it must be flexible in programming, tool friendly and clean to avoid the process drift causing severe effects on the overall throughput and reproducibility as in the Bosch process.

- Based on the established process for directional silicon etching, develop a procedure for the fabrication of ultra-high aspect ratio (HAR) nanostructures (> 100) with low mask undercut and high directionality. A further task is to find a mask material that have high selectivity towards silicon and then investigating the highest achievable aspect ratio using that material as a mask.

- Demonstrate the ability of the developed technology in fabrication of various structures for different applications such as black silicon on demand, tuning fork, spiral structures, 3D nanostructures, etc.

#### 1.3. Thesis outline

This thesis consists of seven chapters with the main focuses of each chapter are described as below:

- Chapter 1 will introduce about the motivation and objection of the project.

- Chapter 2 will give a general introduction about plasma etching. In the first part, the plasma is presented with a general overview about its basic properties. There is also a discussion about the radio frequency (RF) discharge, ion sheath and the motion of ion in the sheath. The second part introduces plasma etching with the focus on plasma-

surface interaction and the difference in etching mechanism between isotropic and anisotropic etching. Parameters for characterization of the etch results such as the etch rate, loading effect, aspect ratio dependent etching (ARDE), selectivity, and etch profiles will also be described.

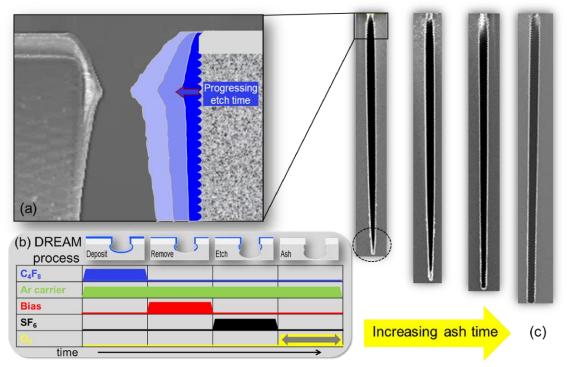

- Chapter 3 will present a study on the development of a fluorocarbon-free directional silicon etching procedure called CORE (standing for Clear, Oxidize, Remove, and Etch) in which a switching sequence of SF<sub>6</sub> and O<sub>2</sub> is operated at room temperature. The CORE process resembles the well-known SF<sub>6</sub>-based Bosch process, but the usual C<sub>4</sub>F<sub>8</sub> inhibitor is replaced by O<sub>2</sub> oxidation with a self-limiting characteristic. In this chapter, the effect of varying the time in each step on the etch profiles is carefully investigated. Based on the obtained results, the design rules of the CORE sequence are formulated for further optimization. Then other etching characters includes profile tuning, mask selectivity, 3D fabrication and microscale etching process will be presented sequentially. The last part of the chapter will discuss about the self-limiting property of the CORE sequence.

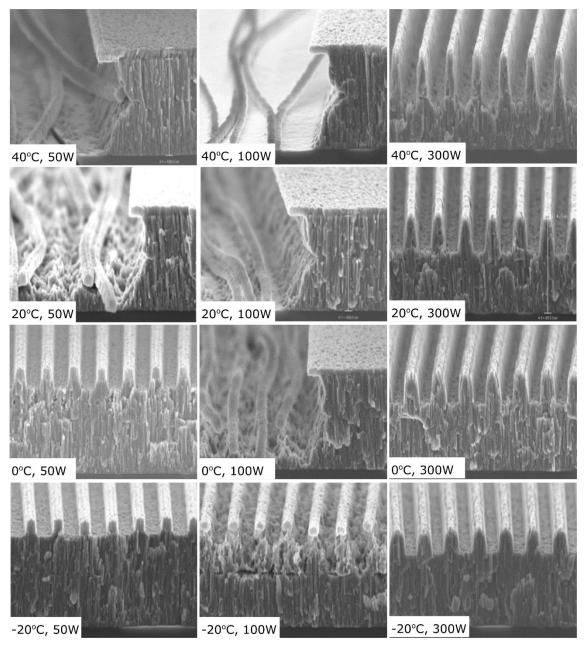

- Chapter 4 will present a study on the formation of black silicon (BSi) in SF<sub>6</sub>/O<sub>2</sub> plasma. In this chapter, different sources that contribute to the formation of BSi are documented and explained. Then a method to prevent and control the onset of BSi is proposed based on the CORE sequence. Due to the self-limiting property of the oxidation step, the formation and controllability of BSi in the CORE sequence is different from how BSi presents itself in the FC-based sequences. The effect of different process parameters of the CORE sequence on the creation of masks and formation of BSi are carefully investigated. By manipulating these parameters, the ability to create either BSi-full or BSi-free surfaces independent of the aspect ratio of the etching features is feasible.

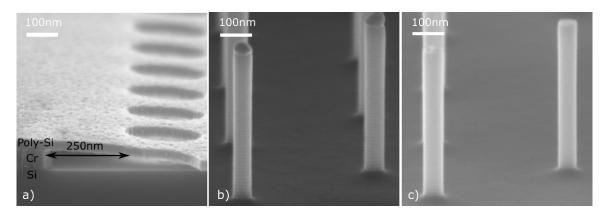

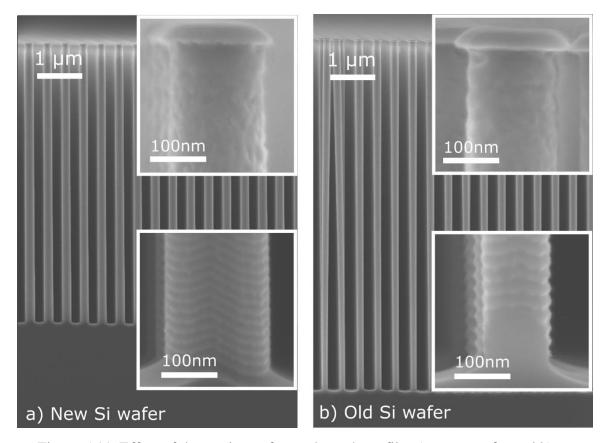

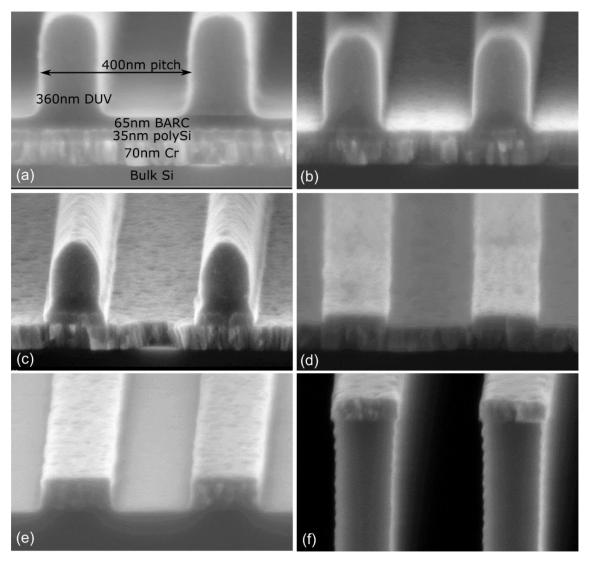

- Chapter 5 will present a procedure to fabricate ultra-HAR silicon pillars using chromium mask and the CORE sequence. In this chapter, the effect of different CORE parameters (e.g. O-time, R-power, and E-pressure) on the etch rate and profile are carefully investigated and optimized with respect to low mask undercut, smooth sidewall and high directionality. In addition to the CORE parameters, we also examine the effect of total etch time on the evolution of ultra-HAR silicon pillars. Then based on the gained knowhow, the CORE recipe is fine-tuned to get ultra-HAR features with straight and smooth sidewalls. Finally, the retraction of chromium mask in SF<sub>6</sub>/O<sub>2</sub> plasma and the effect of carrier wafer on the etch rate will be discussed.

- Chapter 6 will present a procedure to etch Cr and CrO<sub>x</sub> using SF<sub>6</sub> and O<sub>2</sub> plasma as an alternative of the conventional Cl<sub>2</sub>+O<sub>2</sub> plasma. The etch mechanism is explained by considering the formation of volatile chromyl fluoride (CrO<sub>2</sub>F<sub>2</sub>) which sublimes readily at room temperature. First, the effect of different plasma parameters (SF<sub>6</sub>/O<sub>2</sub> ratio, plasma power, gas flux, loading) on the Cr and CrO<sub>x</sub> etch rate will be studied using non-patterned samples. These non-patterned samples are simply used to find

some quick indication on the overall etch rate performance without considering the selectivity or etch profile. Then based on this obtained information, the patterned samples will be etched with the optimized plasma settings using both mixed mode and switched mode of SF<sub>6</sub> and O<sub>2</sub> plasma. Finally, the Cr etch procedure will be combined with other established etch process to demonstrate a complete fabrication scheme of silicon nanostructures using Cr as a mask.

• Chapter 7 will summarize the thesis and present an outlook for future development.

#### References

- 1. Schaller, R.R., 1997. IEEE spectrum, 34(6), pp.52-59.

- 2. https://www.semiconductors.org/resources/2015-international-technology-roadmap-for-semiconductors-itrs/

- 3. https://irds.ieee.org/editions/2016

- 4. https://www.electronicsweekly.com/news/business/imec-asml-achieve-24nm-line-pitch-2020-02/

- 5. Tanaka, H., Kido, M., Yahashi, K., Oomura, M., Katsumata, R., Kito, M., Fukuzumi, Y., Sato, M., Nagata, Y., Matsuoka, Y. and Iwata, Y., 2007, June. In 2007 IEEE Symposium on VLSI Technology (pp. 14-15). IEEE.

- 6. De Marchi, M., Sacchetto, D., Frache, S., Zhang, J., Gaillardon, P.E., Leblebici, Y. and De Micheli, G., 2012, December. In Electron Devices Meeting (IEDM), 2012 IEEE International (pp. 8-4). IEEE.

- 7. Moon, D.I., Choi, S.J., Kim, C.J., Kim, J.Y., Lee, J.S., Oh, J.S., Lee, G.S., Park, Y.C., Hong, D.W., Lee, D.W. and Kim, Y.S., 2011. IEEE Electron Device Letters, 32(4), pp.452-454.

- 8. Ramaswami, S., Dukovic, J., Eaton, B., Pamarthy, S., Bhatnagar, A., Cao, Z., Sapre, K., Wang, Y. and Kumar, A., 2009. IEEE Transactions on Device and Materials Reliability, 9(4), pp.524-528.

- 9. Puech, M., Thevenoud, J.M., Gruffat, J.M., Launay, N., Arnal, N. and Godinat, P., 2008. arXiv preprint arXiv:0805.0919.

- 10. Coburn, J. W., & Winters, H. F. (1979). Journal of Applied physics, 50(5), 3189-3196.

- 11. Coburn, J. W., & Winters, H. F. (1979). Journal of vacuum Science and Technology, 16(2), 391-403.

- 12. Williams, K.R., Gupta, K. and Wasilik, M., 2003. Journal of microelectromechanical systems, 12(6), pp.761-778.

- 13. Lepselter, M.P., Waggener, H.A., MacDonald, R.W. and Davis, R.E., 1965. Proceedings of the IEEE, 53(4), pp.405-405.

- 14. Lepselter, M.P., 1966. Bell System Technical Journal, 45(2), pp.233-253.

- 15. Davidse, P.D., 1969. Journal of The Electrochemical Society, 116(1), p.100.

- 16. Lehmann, H.W., Krausbauer, L. and Widmer, R., 1977. Journal of Vacuum Science and Technology, 14(1), pp.281-284.

- 17. Saussac, J., Margot, J. and Chaker, M., 2009. Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films, 27(1), pp.130-138.

- 18. Irving, S.M., 1971. Solid State Technology, 14, pp.47-51.

- 19. Irving, S.M., Lemons, K.E. and Bobos, G.E., Signetics Corp, 1971. Gas plasma vapor etching process. U.S. Patent 3,615,956.

- 20. Bersin, R.L., 1970. Solid State Technology, 13(6), p.39.

- 21. Reinberg, A., Texas Instruments Inc, 1973. Radial flow reactor. U.S. Patent 3,757,733.

- 22. Hosokawa, N., Matsuzaki, R. and Asamaki, T., 1974. In Paper from' Proceedings of the Sixth International Vacuum Congress'', Jap. J. Appl. Phys. Supplement 2. Tokyo, Japan. 1974, 435-438.

- 23. Bondur, J.A., 1976. Journal of Vacuum Science and Technology, 13(5), pp.1023-1029.

- 24. Lehmann, H.W. and Widmer, R., 1978. Journal of Vacuum Science and Technology, 15(2), pp.319-326.

- 25. Yaws, C.L., Dickens, L.L., Lutwack, R. and Hsu, G., 1981. Solid State Technology, 24(1), pp.87-92.

- 26. Flamm, D.L., 1990. Pure and Applied Chemistry, 62(9), pp.1709-1720.

- 27. Zhang M, Li JZ, Adesida I, Wolf ED. Journal of Vacuum Science & Technology B: Microelectronics Processing and Phenomena. 1983 Oct;1(4):1037-42.

- 28. Jansen, H., de Boer, M., Legtenberg, R. and Elwenspoek, M., 1995. Journal of Micromechanics and Microengineering, 5(2), p.115.

- 29. Tachi, S., Tsujimoto, K. and Okudaira, S., 1988. Applied physics letters, 52(8), pp.616-618.

- 30. Jansen, H., De Boer, M., Wensink, H., Kloeck, B. and Elwenspoek, M., 2001. Microelectronics Journal, 32(9), pp.769-777.

- 31. De Boer, M.J., Gardeniers, J.G., Jansen, H.V., Smulders, E., Gilde, M.J., Roelofs, G., Sasserath, J.N. and Elwenspoek, M., 2002. Journal of microelectromechanical systems, 11(4), pp.385-401.

- 32. Dussart, R., Tillocher, T., Lefaucheux, P. and Boufnichel, M., 2014. Journal of Physics D: Applied Physics, 47(12), p.123001.

- 33. Laermer, F. and Schilp, A., Robert Bosch Gmbh, 1994. Verfahren zum anisotropen Ätzen von Silicium.

- 34. Laermer, F. and Schilp, A., Robert Bosch GmbH, 1996. Method of anisotropically etching silicon. U.S. Patent 5,501,893.

- 35. Chang, B., Leussink, P., Jensen, F., Hübner, J. and Jansen, H., 2018. Microelectronic Engineering, 191, pp.77-83.

- 36. Athavale, S.D. and Economou, D.J., 1996. Journal of Vacuum Science & Technology B:Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena, 14(6), pp.3702-3705.

- 37. Kanarik, K.J., Lill, T., Hudson, E.A., Sriraman, S., Tan, S., Marks, J., Vahedi, V. and Gottscho, R.A., 2015. Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films, 33(2), p.020802.

# Chapter 2. Introduction of plasma etching

Plasma etching is an important technology in semiconductor industry to transfer patterns defined by lithography into a target material. In the first part of this chapter, the plasma is presented with a general overview on its basic properties. There is also a discussion about the radio frequency (RF) discharge, ion sheath and the motion of ions in the sheath. The second part introduces plasma etching with the focus on the plasma-surface interaction and the difference in etching mechanisms between isotropic and anisotropic etching. Parameters for characterization of the etch results such as etch rate, loading effect, aspect ratio dependent etching (ARDE), selectivity, and etch profiles will also be described.

#### 2.1. Basics of plasmas

#### 2.1.1. Plasma and collision process in a plasma

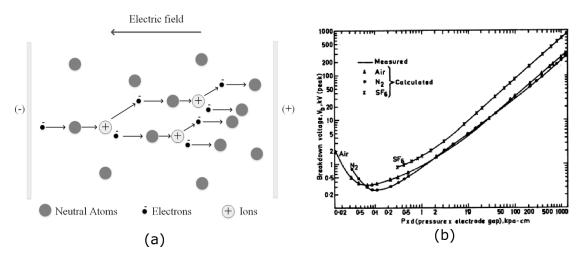

Plasma is the forth fundamental state of matter that contains freely moving charged particles (ions and electrons) in a gas volume and is therefore highly conductive. Consider a chamber filled with a gas. A gas is highly insulating but will always have a few freely moving electrons inside. When a power source is applied on the chamber electrodes, the generated electric field will accelerate these electrons towards the positively charged anode. Under the correct conditions, these electrons gain energy high enough to ionize gas and liberate additional electrons. These collisions create an ever-increasing number of free electrons (avalanche) while passing towards the anode and will generate a gas discharge or plasma. This mechanism is illustrated in Figure 2.1a. Important plasma characteristics are the electron density  $(n_e)$  and ion density  $(n_i)$  which are substantially equal to each other thus making a plasma electrically neutral from the macroscopic viewpoint.

Figure 2.1. (a) Principle of a gas discharge. (b) The Paschen curve<sup>1</sup>

An important discharge property is the Paschen curve<sup>1</sup>. It shows the relationship between the minimum breakdown voltage needed to create plasma and the chamber pressure (calculated as the pressure p times the separated distance d between two electrodes). In Figure.2.1b, the breakdown voltage needed to create plasma has a minimum around 0.1kpa.cm ~ 0.7 Torr.cm. When the chamber pressure is too low, there are not enough collisions to cause avalanche while at the high chamber pressure, there is not enough RF energy gained by the accelerating electrons to cause ionization. This is why the plasma process needs to take place in a vacuum chamber with the pressure range between a few milliTorrs and a few hundreds of milliTorrs.

Plasma can be categorized into two main types: fully ionized plasma (referred to as arc discharge or high temperature plasma) and weakly ionized plasma (referred to as glow discharge or low temperature plasma). In this study, we only consider cold plasma as it is widely used in the semiconductor industry for etching materials. The degree of plasma ionization is defined as  $\frac{n_i}{n_i+n_n}$ , with  $n_i$  is the density of ions and  $n_n$  is the density of neutral species. Typically, a plasma used for etching has an ionized degree between  $10^{-6}$  and  $10^{-}$ <sup>4</sup>. This means that the majority of the particles remain neutral and only one ion/electron pair are generated out of every 10,000 neutral particles. In the standard plasma system such as a glow discharge or capacitively coupled plasma (CCP), the ion density is within a range of  $10^9$ - $10^{11}$  cm<sup>-3</sup> whereas in an inductively coupled plasma (ICP) system, a higher ion density of  $10^{12}$  cm<sup>-3</sup> can be achieved<sup>2</sup>.

In plasma, the collisions between moving electrons and atoms/molecules are categorized as elastic collision and inelastic collisions. With an elastic collision, only the kinetic energy changes while the internal energy remains unchanged. This type of collision tends to take place when the electron energy is low in between gas molecules. Assume a moving mass m<sub>1</sub> collides with a stationary mass m<sub>2</sub> at an angle α to the line joining the centers of  $m_1$  and  $m_2$ . The fractional energy E transferred from mass  $m_1$  to mass  $m_2$  can be derived by the conversation of linear momentum and energy<sup>3</sup>:

$$\frac{E_2}{E_1} = \cos^2(\alpha) \frac{4m_1 m_2}{(m_1 + m_2)^2} \tag{2.1}$$

When  $m_1 = m_2$  and the collision is frontal ( $\alpha = 0$ ), this fraction has the maximum of 1. It means that mass  $m_2$  gains an energy equal to that of mass  $m_1$  and mass  $m_1$  will lost all of its kinetic energy. This situation resembles the collision of billiard balls. In contrast, when an electron strikes a molecule, because the electron's mass is so much smaller than the molecule, the transfer function can be simplified as  $4m_1/m_2$  ( $\sim 10^{-5}$  for SF<sub>6</sub> molecules). Therefore, very little energy can be transferred from an electron to a molecule through an elastic collision. In plasma the more interesting collisions are inelastic, where the internal energy a struck molecule gains can be calculated as:

$$\frac{\Delta U}{E_1} = \cos^2(\alpha) \frac{m_2}{m_1 + m_2} \tag{2.2}$$

So, whereas the elastic energy transfer from an electron to a  $SF_6$  molecule is close to 0%, this may rise to near 100% by inelastic collision. Consequently, electrons driven by the RF generator will lose their kinetic energy mostly by the inelastic collisions and will only slightly raise the gas temperature. This is why they are frequently referred to as cold plasma. Some of the typical collisions processes in plasma are described as below:

- Excitation and relaxation: In the excitation process, a moving electron that collides with an atom will transfer its kinetic energy to the bound electron in the atom and enables this electron to jump to a higher energy level. The excited electron stays at high level for a short time and then falls back to the ground state. This relaxation will emit a photon and create the plasma glow. A general excitation process can be described as A + e → A\* + e → A + e + hv, in which A denotes a neutral atom, A\* denotes A at the excited state, h is the Planck's constant and v is the frequency of the emitted light.

- Dissociation: If the kinetic energy of the colliding electron is higher than the binding energy of the molecule, the dissociation process may occur. This reaction process can be described as AB + e → A + B + e. The dissociation process will create highly active species called radicals that will contribute to the enhancement of chemical activities. For example, in SF<sub>6</sub> plasma, the fluorine radical produced after dissociation will etch silicon spontaneously.

- Ionization: The process in which a primary electron removes an electron from an atom, producing a positive ion and an extra electron is called electron impact ionization. The reaction process can be described as A + e → A<sup>+</sup> + 2e. The prime feature of discharges is its conductance due to ionization, with perhaps as many as 10<sup>18</sup> electron-ion pairs being produced per second.

• Attachment: There is a possibility that a low energetic electron colliding with an atom may join the atom and turn it into a negative ion. This process is known as electron attachment. The reaction process can be described as A + e → A⁻. The noble gases already have the outer shell filled with electrons, thus have little or no probability to form negative ions. However, halogen atoms (e.g. F, Cl, and Br) have an unfilled state in their outer shells, thus have high electron affinity to form negative ions.

#### 2.1.2. Plasma parameters

The energy of a particle is related to its temperature. For gases the colliding particles will have the same temperature and thus thermal energy, irrespective their size. In contrast, in plasma there exists a lack of thermal equilibrium between the various particles. This is due to the difference in the kinetic energy gained by these particles under the applied electric field. Because electrons have a much smaller mass compared to ions or molecules, they will move faster and thus gain larger kinetic energy. The relationship between the kinetic energy and temperature of an electron is expressed as:

$$E_{rms} = \frac{1}{2} m_e v_{rms}^2 = \frac{3}{2} k T_e \tag{2.3}$$

in which  $m_e$  is the electron mass, v is the velocity, k is the Boltzmann's constant and  $T_e$  is the electron temperature. Since the average electron energy in a weakly ionized plasma is typically around 2eV, according to equation (2.3) the calculated electron temperature  $T_e \sim 15000 K$ . The ion temperature  $T_i$  and gas temperature  $T_g$  are much lower: typically 500K and 400K, respectively. Although the electron temperature  $T_e$  is very high, the wafers and etch chamber remain at a low temperature because the electron mass is too small to heat them up.

For a collection of moving molecules or electrons colliding with each other, the collision frequency is calculated as:

$$f_{gg}(gas - gas) = \sigma n_g v_{avg} 4\sqrt{2}$$

(2.4a)

$$f_{eg}(electron - gas) = \sigma n_g v_{ave}$$

(2.4b)

where  $\sigma$  is the collision cross section, n is the density and  $v_{av}$  is the average speed. The mean free path is defined as the average distance a molecule or electron travels between collisions. Based on the collision frequency, the mean free path can be derived as:

$$\lambda_g = \frac{v_{avg}}{f_{gg}} = \frac{1}{\sigma n_a 4\sqrt{2}} \tag{2.5a}$$

$$\lambda_e = \frac{v_{ave}}{f_{eg}} = \frac{1}{\sigma n_g} = \frac{kT}{\sigma p_g}$$

(2.5b)

So, according to equation 2.5, the mean free path of an electron is much larger (approximate 6 times larger) than the gas molecule due to its very small size. It is also noticed that the mean free path is inversely proportional to the pressure. The lower the

pressure, the longer the mean free path. This is because less particles exist at a low pressure so that they will be able to travel without collisions for a longer distance.

Since a plasma is conducting, it will respond to local changes in potential. If a charged particle is inserted into a plasma, a cloud of opposite charges will quickly surround the particle. This prevents an electric field to develop outside the cloud. This phenomenon is called Debye shielding and the cloud is called the sheath. The Debye length is referred to the thickness of the sheath and can be formulated by the equation below:

$$\lambda_D = \sqrt{\frac{\varepsilon_0 k T_e}{nq^2}} \tag{2.6}$$

For an etch system with the plasma density of  $\sim 10^9$ - $10^{12}$ , the Debye length is typically in the range of 0.01 to 0.1mm. This value is significantly smaller than the dimension of the reactor chamber. Therefore, a plasma is considered as macroscopically neutral. Given the Debye length, we can describe the oscillation of electrons inside a plasma. When a group of electrons are displaced with respect to the ions, a restoring force is developed and pulls the charges back toward each other. They accelerate to their equilibrium positions and then separate in the opposite sense. The frequency of this motion is estimated as:

$$\omega_{pe} = \frac{v_e}{\lambda_D} = \sqrt{\frac{nq^2}{m\varepsilon_o}}$$

(2.7)

Plasma oscillations are classified into plasma-electron oscillations and plasma-ion oscillations. The frequency of plasma-electron oscillation is usually very high since the mass of an electron is small. For a SF<sub>6</sub> plasma of density  $n=10^{10} cm^{-3}$ , the frequency of electron and ion are approximate 1GHz and 2MHz, respectively. A typical RF frequency of plasma sources is 13.56MHz. This frequency is low enough to enable electrons to respond and extract electrical energy while the ions cannot follow the fluctuation and will stay relatively motionless.

#### 2.1.3. DC bias, ion sheath and ion motion in the sheath

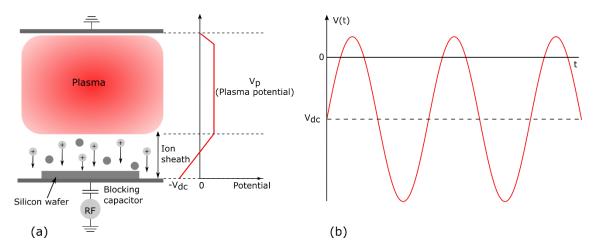

DC bias is an important plasma parameters that controls the etch rate, selectivity and profile. Thus in the first part we will give a brief introduction about the generation of DC bias. Figure 2.2a is an illustration of a parallel plate etch tool in which the upper electrode is grounded and the lower electrode is connected to an RF power generator through a blocking capacitor. With the RF alternating potential, the polarity on the lower electrode is changed accordingly. When the polarization is positive the plasma electrons will be attracted to the lower electrode and when the electrode is negative polarized, the electrons will be repelled and positive ions will be attracted. However, because the frequency of the RF alternating potential is very high (commonly 13.56 MHz), the ions are too heavy to follow the alternating RF field and thus unable to travel across the plasma sheath. On

the other hand, electrons with much smaller mass can respond and will therefore gradually charge both electrodes and leaving the plasma positively charged. If both electrodes would have the same area facing the plasma, nothing special would happen. However, in RIE plasma systems, the lower electrode (cathode) has a much smaller area than the opposing chamber wall (anode). This difference in area is causing that the cathode will acquire a much more negative voltage with respect to the plasma than the anode. As a result, a measurable DC bias (or self-bias) is generated between two electrodes (the cathode being more negative than the anode) and denoted as V<sub>dc</sub>. Typically, the chamber (i.e. anode) is grounded and the positive plasma potential V<sub>p</sub> is taken with respect to the grounded anode. The V<sub>dc</sub> value depends on the RF power and is in the range of ten to several hundred of volts. Because of the average negative potential of the lower electrode, the ions are attracted towards the bottom electrode and will bombard a sample placed on that electrode. The larger the  $V_{dc}$  in combination with  $V_p$ , the stronger the bombardment will be. This ion bombardment is involved in the etching process.

The magnitude of voltage induced at an electrode is dependent on its surface area. The relationship of the induced voltages and surface areas between two electrodes can be approximated as<sup>4</sup>:

$$\frac{V_1}{V_2} = \left(\frac{S_2}{S_1}\right)^4 \tag{2.8}$$

in which  $V_1$ ,  $V_2$  are the voltages induced at each electrode and  $S_1$ ,  $S_2$  are the surface areas, respectively. This means that for the smaller electrode (cathode), a higher voltage is induced. In an etching system, the anode electrode (the chamber wall) is designed much larger than the cathode electrode (the platen where the wafer is placed) so that an adequate V<sub>dc</sub> is induced at the wafer while induced voltage at the chamber wall is minimized to prevent sputtering of the wall material.

Figure 2.2b shows the potential waveform at the cathode when it reaches the equilibrium state. At this state, the cathode is negatively charged most of the time and turns positive for a small period during each cycle. Therefore, high electron currents flow onto the cathode only for a short time while the much lower ion currents flow almost continuously. When the cathode is negatively charged, electrons will be pushed away and therefore almost no electrons exist in the nearest region of the cathode. This region is called the ion sheath in which almost no electron collision will happen and excitation and relaxation events are rare. For this reason, no light is coming out from this region and, therefore it is called the dark space. The ion sheath thickness can be represented by the following equation:

$$d = \frac{2}{3} \left(\frac{\varepsilon_o}{j_i}\right)^{\frac{1}{2}} \left(\frac{2e}{m_i}\right)^{\frac{1}{4}} \left(V_p - V_{dc}\right)^{\frac{3}{4}}$$

(2.8)

Where  $j_o$  is the ion current density,  $\varepsilon_o$  is the permittivity of vacuum, e is the electric charge,  $m_i$  is the ion mass and  $V_p$  is the plasma potential. For a high density plasma such as the inductively coupled plasma, the ion sheath thickness is on the order of 0.01 to 1cm.

Figure 2.2. (a) Illustration of the DC bias and ion sheath in a RF plasma. (b) Voltage waveform at the cathode in a RF plasma.

As mentioned earlier, the plasma is electrical conductive in which electrons and ions travel in random directions. The ions that reach the wafer surface will have an energy equal to what they have in the plasma plus what they have gained in passing through the ions sheath. Therefore the total obtained energy of ions when reaching the wafer equals  $V_p + V_{dc}$ , which will drive the etching mechanism. The directionality of the impinging ions depends on the pressure as collisions inside the plasma sheath will divert the ions from their trajectory. This scattering of ions in the ion sheath is determined by comparing the ion sheath thickness and ion mean free path. If the mean free path of ion is much larger than the ion sheath thickness, ion can travel to the sample surface with almost no scattering. This directionality of ions is an important factor for anisotropic etching and will be discussed in the next section.

#### 2.2. Introduction of plasma etching

#### 2.2.1. Etching mechanism

Plasma etching is an important technology in semiconductor industry to transfer the lithographic defined patterns into the target materials. The basic concepts of plasma etching are making use of a glow discharge to crack relatively stable molecules into chemically reactive and ionic species that will react with the material to be etched and form volatile products. More specifically, a suitable feed gas (e.g. SF<sub>6</sub> for silicon etching) is introduced to an etch system (RIE, ICP) and the gas phase etching environment, consisting of neutrals, electrons, ions, radicals, etc., is generated through the process of

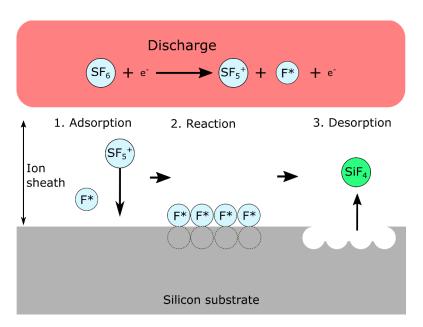

electron-impact dissociation/ionization. The reactive species will diffuse from the plasma bulk to the sample surface (silicon wafer), that is placed on an RF driven capacitively coupled electrode. The positive ions from the bulk of the plasma are attracted to the sample by the DC self-bias and plasma potential that assist the etching. A series of reaction processes will happen when the radicals and ions arrive on the sample surface, which are shown in Figure 2.3 for the case of etching silicon with  $SF_6$  plasma.

Figure 2.3. A schematic illustration of plasma etching in the case of silicon etching with SF<sub>6</sub> plasma.

- Adsorption: when plasma species reach the silicon substrate or the chamber wall, they

will adsorb. This adsorption depends on the chemical affinity and surface temperature.

The lower the temperature at the surface, the thicker the adsorbed layer becomes.

Therefore, the chamber walls are normally set at higher temperature than the silicon

surface to avoid chamber contamination and other interactions.

- Reaction: a chemical reaction between the adsorbed radicals and the sample atoms will take place and create etch products. In case of etching silicon with SF6 plasma, the chemical reactions between the F radicals and the silicon atoms occur spontaneously forming the volatile silicon tetrafluoride (SiF4). However, for other halogens such as chlorine or bromine, the chemical reaction between Cl/Br radicals and silicon atoms does not happen spontaneous. In this case, ion bombardment is needed to provide energy for the absorbed radicals to attack the backbones of silicon atoms efficiently, thus enhance the reaction.

- Desorption: when the chemical reaction between the reactive radical and the silicon atoms finish, the reaction by-products should desorb from the surface so that the etch

- can continue. This requires that the products of the reaction must have a high vapor pressure at the substrate temperature so that they are volatile at the process conditions.

- Exhaust: after the etch products desorb from the sample surface, they will diffuse into the plasma chamber and should be pumped out. Otherwise, plasma-induced dissociation of product molecules will occur and re-deposition can take place.

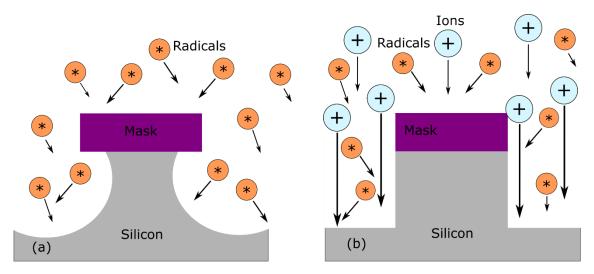

Figure 2.4. (a) Isotropic etching. (b) Anisotropic etching.

Figure 2.4 illustrates the difference between isotropic and anisotropic etching. For an etching process in which only the radicals of the plasma are attributed to the removal of the target materials, the etching will proceed not only in the vertical direction, but also in the horizontal direction. This is because the radicals diffuse from the bulk of plasma to the sample randomly by Brownian motion and get access to the sample at all directions. This phenomenon is called isotropic etching and results in an undercut under the mask. In some applications such as surface micromachining, the buried layer can be removed completely by using isotropic etching. However, undercut caused by isotropic etching will make fine patterning more difficult. In order to transfer the lithographic patterns with a high level of fidelity, it is desired that the etching should proceed only in a vertical direction. This type of etching is referred to as anisotropic etching which will be explained more in the next section.

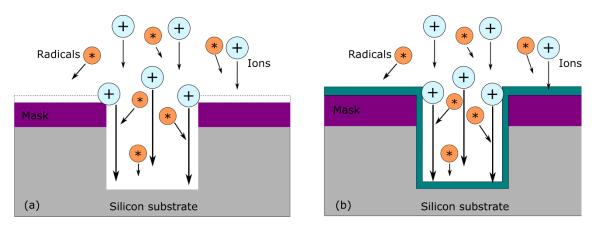

#### 2.2.2. Mechanism of anisotropic etching

As mention earlier, anisotropic etching is realized when the reaction between radicals and sample surface proceed only in the vertical direction. One approach to achieve this goal is using incoming ions to strike the etch target surface at normal incidence in order to induce the surface reactions. Figure 2.5a shows an anisotropic etch in which the reaction between the radicals and sample material is facilitated by impinging kinetic ions. This is

called ion-induced etching in which the ion bombardment will increase the etch rate significantly<sup>5</sup>. Otherwise, the etch rate will be very low when it is etched only by the radicals or by physical sputtering. The main cause of this phenomenon is believed to be due to the effect of temperature at the bombarded areas<sup>6</sup>. When the ions attack this area, its temperature becomes so high that enhance the radicals reactions. As a result, the etch rate by ion-assisted reactions goes up in orders of magnitude larger than that by only neutral radicals. Because the ions imping the wafer in a vertical direction, it is possible to achieve anisotropic etching in which the etch rate in the vertical direction (by ion-assisted reactions) is much faster than in the horizontal direction (by radicals). This is the mechanism of realizing anisotropic etching by ion-induced reactions.

Another approach to obtain anisotropic etching is to protect the sidewall from lateral etching by putting a passivation gas together with the etch gas into the etching chamber. The passivation gas will form a thin layer all over the sample surface, thus prevent the sidewall from the invasion of radicals during the etching process. Figure 2.5b shows a model illustrating the sidewall passivation process. Because the ions come to the sample surface in the vertical direction, only the horizontal part of the passivation layer is sputtered away and the etching proceeds through the reactions between the exposed sample surface and the radicals. On the other hand, the passivation layer on the sidewalls remains since there are almost no ions coming at this angle. As a result, the sidewalls are protected from the attack of radicals while the etching occurs in the vertical direction makes it possible to achieve anisotropic etching. This approach is used for many materials and especially helpful when etching with a gas chemistry that is in essence isotropic. For example, silicon etching with fluorine chemistry will occurs isotropically so that a passivation method is needed to prevent the lateral etching. In this case, either oxygen or fluorocarbon can be added to the etch gas to create the passivation layer 7-9. The passivation step can either happen simultaneously with the etching process or it can be done in a so-called Bosch process where the etch step and passivation steps are sequentially altered<sup>10</sup>.

Figure 2.5. (a) Ions-induced etching. (b) Ions-inhibitor passivation.

#### 2.2.3. Characterization of the etch performance

In an etching process, there are different requirements that depend on the specific application. Some parameters are widely used in order to characterize the etch performance, which are illustrated in Figure 2.6a.

#### Etch rate

The usual first parameter to evaluate is the etch rate, which is defined as the thickness of the film that has been etched divided by the etch time. The process condition can be modified such that the etch rate will get as high as possible for high throughput microscale etching or it can be made very low for nanoscale etching. For an etch process with only chemical reactions the etch rate is typically high but also isotropic. In contrast, for purely physical sputtering the etch rate is very low but directional. However, by combining both methods, the synergetic effect leads to a strong increase in the etch rate while preserving directionality. The gas chemistry also has a strong impact on the etch rate. With a specific sample material, the etching gas should be selected so that it results in a higher surface reactions and desorption of etch byproducts. For examples, it is known that the fluorides of silicon are more volatile than the chlorides<sup>11</sup>. Therefore when the fluorides chemistry is used, the etch products desorb more easily and the etch rate becomes higher.

#### **Selectivity**

The next parameter is the selectivity which is calculated as the ratio between the etch rate of the mask and the target film. This parameter indicate how well the mask can protect the underlying structures while etching proceeds. A high selectivity means that less mask material is etched away while the target film is removed. In photolithography, normally thinner resist film is used to enhance the resolution on the devices. Therefore a high selectivity is necessary to ensure that the resist will be able to sustain the etch process. The etch selectivity is dependent on the parameter setting in the etch process in which the ion energy and the bonding strength of atoms should be considered<sup>12</sup>. Since the reaction occurs in a direction that creates a larger bond strength, the gas chemistry can be selected corresponding to the etch target so that the selectivity can be improved. For example, the bond strength between silicon and halogen gases (Cl, Br, and F) is smaller than that of Si-O, therefore these gases can be used for the etching of silicon with SiO<sub>2</sub> as a mask<sup>13</sup>. In this case, the etch rate of SiO<sub>2</sub> will be very low with respect to silicon and a high selectivity will be achieved. Another effective approach to increase the selectivity is to decrease the ion energy in a gas system in which the etch rate of the mask material is much dependent on the ion energy than that of the etched target. Therefore, when the ion energy is lower, the mask material will be etched away slower resulting in a high selectivity.

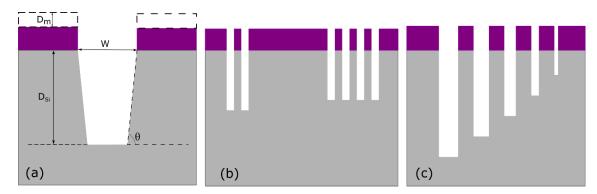

#### Etch profile

In anisotropic etching, the etch profiles should have straight sidewalls with minimized dimensional shifts from the mask patterns. However, in some cases, the sidewalls of the etch profiles may be not perfectly straight with a deviation of an angle  $\theta$  from the vertical. We call it positive tapered if the angle  $\theta < 90^{\circ}$  and negative tapered if the angle  $\theta > 90^{\circ}$ . A positive tapered profile is normally created by reposition of materials on the sidewall. This can be either passivation layer created by the plasma chemistry or non-volatile materials which is sputtered off by the ion bombardment <sup>14</sup>. A positive tapered sidewall is preferred in applications such as nanoimprinting to fabricate master molds with tilted sidewalls so that an imprinted polymer can be released easier <sup>15</sup>. A negative tapered profile can happen when a trench/hole with an isotropic chemistry is etched in combination with a passivating chemistry. When the trench/hole gets deeper, the passivation gets thinner and the etching will start having a lateral component. This will lead to a negative tapered etch shape. The negative tapered profiles should be avoided since it can create shadow effects for the post etch processing.

Figure 2.6. (a) Parameters for characterization of the etch performance. (b) Microloading effect. (c) Aspect ratio dependent etching (ARDE).

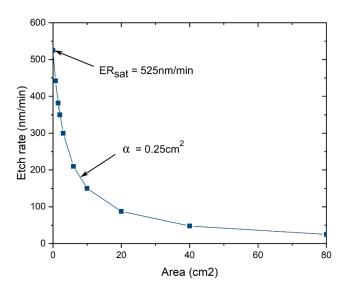

#### Loading effect

The loading effect is the phenomenon in which the etch rate during plasma etching depends on the total exposed area<sup>16</sup>. It is observed when the etch rate in a batch etcher decreases according to the increased number of wafers in the processing chamber. This effect is called macroloading to differentiate it from the microloading effect in which the local variation in patterns densities can lead to the local variation of the etch rate <sup>17-19</sup>. The microloading is not pronounced for an etching process in which the etch rate is limited by ion bombardment<sup>20</sup>. However, for an etching process limited by reactive species, the areas with high pattern density will have lower etch rate than the areas with low pattern density as shown in Figure.2.6b<sup>21</sup>. This is because for the regions of higher pattern density, there will a higher local depletion of reactive species resulting is the decrease of

etch rate. In order to reduce the nonuniformity caused by the microloading effect, the process parameters can be modified by increasing the gas flow rate or decreasing the plasma pressure<sup>22</sup>.

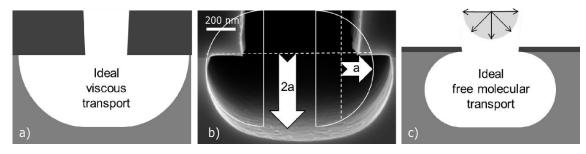

#### Aspect ratio dependent etching (ARDE)

Aspect ratio dependent etch rate (ARDE) or RIE lag is a well-known phenomenon in plasma etching that describes how the etch rate depends on the aspect ratio of the patterns<sup>23, 24</sup>. The aspect ratio (AR) is defined as the depth of the feature divided by its width. Figure.2.6c shows the schematic demonstration of ARDE lag phenomenon. The silicon trenches with various dimensions are etched simultaneously resulting in a lower etch rate in the smaller trenches than in the bigger ones. This implies that the etch rate decreases when the etched depth increases and the ARDE phenomenon is affected by the aspect ratio rather than by the width or the depth of the trench. There are several main factors causing the ARDE phenomenon with the dominant one depending on the plasma process and the material being etched. Some studies show that ARDE occurs because of the depletion or reflection of reactive radicals along the trench<sup>25, 26</sup>. Other studies demonstrate chemistries where the decrease of ion flux at the bottom of the trench slows down the etch process<sup>27, 28</sup>.

#### 2.3.4. Etch profiles obtained after the plasma etching

In plasma etching, the etch profile is expected to be straight with the same width both at the top and bottom of the patterns. However, the obtained etch profiles may be different and depends on the etch conditions and target material. Let us have a look at various etch profiles obtained after etching.

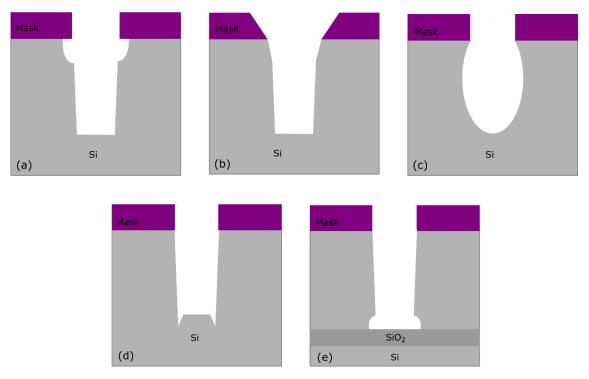

#### Undercut

The undercut profile is a result of lateral etching of material under the mask where the passivation layer has been eroded. This removal of passivation layer may be caused by the bombardment of ions being reflected from the mask or deflected by due to differential charges to the sidewall. The passivation layer can also be removed by chemical etching of the reactive radicals. Once it is removed, the reactive radicals can laterally etch the target materials and create undercut (Figure.2.7a). Normally, the undercut occurs under the mask where the radicals flux is largest and the passivation layer is more vulnerable. In order to prevent the undercut, a stronger passivation step should be implemented to provide a better sidewall protection that is able to resist the whole etching process.

#### **Faceting**

Faceting of the mask during etching is mainly caused by the ion sputtering. Since the sputtering yield depends on the angle of incoming ions, the sharp corners of the mask will be eroded faster than other parts due to a higher momentum transfer and faceting occurs<sup>29</sup>.

As a result, sidewalls of the mask will slowly become positive tapered and attain at an angle correlated to the maximum sputtering rate. When the etching proceeds, the ions bombardment will continue to erode the mask and the positive tapered will be transferred into the silicon features as shown in Figure 2.7b.

#### **Bottling**

Bottling is a phenomenon in which the etch profiles have the arched sidewalls with the largest width of the trenches/holes is not localized at their entrance (Figure 2.7c). It is mainly caused by the collisions of ions during their travel through the ion sheath. The more collisions, the broader the ion distribution function will be. This divergence of ion flux to the sidewall will weaken the passivation layer causing bottling. The consequence of bottling is that it will make the process of filling trenches/holes more difficult because the top part may close before the other part is filled. Bottling can be minimized by lowering the pressure or increasing the DC bias. Both solutions sharpen the ion angular distribution of the incoming ion flux.

#### **Trenching**