Downloaded from orbit.dtu.dk on: May 02, 2024

**DTU Library**

# Power converter assembly

Nour, Yasser A. A; Thanh, Hoà Lê; Ammar, Ahmed Morsi; Larsen, Dennis Øland; Llimós Muntal, Pere

Publication date: 2021

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Nour, Y. A. A., Thanh, H. L., Ammar, A. M., Larsen, D. Ø., & Llimós Muntal, P. (2021). Power converter assembly. (Patent No. *WO2021234158*).

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

#

(10) International Publication Number WO 2021/234158 A1

25 November 2021 (25.11.2021)

*H05K 1/18* (2006.01) *H01L 23/538* (2006.01) **H01L 23/13** (2006.01)

(21) International Application Number:

(51) International Patent Classification:

PCT/EP2021/063689

(22) International Filing Date:

21 May 2021 (21.05.2021)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

20176041.0

22 May 2020 (22.05.2020)

EP

- (71) Applicant: DANMARKS TEKNISKE UNIVERSITET [DK/DK]; Anker Engelunds Vej 101, 2800 Kongens Lyngby (DK).

- (72) Inventors: NOUR, Yasser A. A.; c/o Danmarks Tekniske Universitet, Anker Engelunds Vej 101, 2800 Kongens Lyngby (DK). THANH, Hoà Lê; c/o Danmarks Tekniske Universitet, Anker Engelunds Vej 101, 2800 Kongens Lyngby (DK). AMMAR, Ahmed Morsi; c/o Danmarks Tekniske Universitet, Anker Engelunds Vej 101, 2800 Kongens Lyngby (DK). LARSEN, Dennis Øland; c/o Danmarks Tekniske Universitet, Anker Engelunds Vej 101, 2800 Kongens Lyngby (DK).

- gens Lyngby (DK). **LLIMÓS MUNTAL, Pere**; c/o Danmarks Tekniske Universitet, Anker Engelunds Vej 101, 2800 Kongens Lyngby (DK).

- (74) Agent: HØIBERG P/S; Adelgade 12, 1304 Copenhagen K (DK).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, IT, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, WS, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM,

(57) Abstract: The present disclosure relates to a power converter assembly comprising: an interposer; an integrated circuit, such as a power management integrated circuit, arranged in a cavity or pocket of the interposer or monolithically integrated in the interposer; one or more electrical components stacked on a top side of the interposer; and one or more vias arranged in the interposer forming electrical connections in the interposer, wherein the integrated circuit and the electrical components are configured to perform a power conversion of an input voltage to an output voltage.

#

TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

### **Declarations under Rule 4.17:**

— of inventorship (Rule 4.17(iv))

### **Published:**

— with international search report (Art. 21(3))

## Power converter assembly

The present disclosure relates to a power converter assembly, in particular to a high-power density DC-DC converter manufactured in/on a three dimensional silicon interposer.

## 5 Background

In smart electronics systems, for example, internet of things (IoTs) devices, light emitting diode (LED) lightings and other consumer electronic products, a general trend is that an increasing number of functions is packed into a limited space. These systems consequently require more compact and more efficient power converters, preferably also with lower manufacturing costs.

Miniaturized power converters play an important role in achieving the aforementioned goals and can be categorized into three categories. The first category is Power systems on chip (PwrSoC), in which all active and passive components are integrated on the same die. The second category is power system in package (PwrSiP) in which individual components of the converter are co-packaged together with a power management integrated circuits die. The third category is power modules in which prepackaged discrete components are assembled on a printed circuit board.

One challenge with developing smaller power converters is thermal management. The development towards smaller power converters typically implies increased temperature, generally, or at least in certain areas in the power converters. The higher the density, the higher the risk of accidents and power loss due to increased temperature during operation.

25

30

10

15

There is thus a need for a solution for highly efficient power converters with improved thermal performance.

#### Summary

The present disclosure therefore relates to an improved high-power density power converter assembly for performing a power conversion of an input voltage to an output voltage. According to a first embodiment, the power converter assembly comprises:

- an interposer;

- an integrated circuit, such as a power management integrated circuit, arranged in a cavity or pocket of the interposer or monolithically integrated in the interposer;

- one or more electrical components stacked on a top side of the interposer; and

- one or more vias in the interposer,

wherein the integrated circuit and the electrical components are configured to perform a power conversion of an input voltage to an output voltage. Preferably, the one or more electrical components comprise one or more passive electrical components.

10

15

20

25

30

35

5

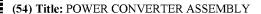

Preferably, the interposer is made of a material having a high thermal conductivity. One example of a suitable material for the interposer is silicon. Silicon is also easy to process and relatively cheap. By implementing a 3D integrated power converter using a high thermal conductivity interposer as substrate, the power converter assembly can provide very efficient integrated heat dissipation. Fig. 5 shows an exemplary embodiment of the presently disclosed power converter assembly.

A silicon substrate can be used a carrier for power converter components and provide electrical connectivity between various parts. The substrate may be referred to as a routing substrate or a routing interposer. Passive components (capacitors, inductors and transformers) can be processed in and/or on the interposer.

According to one embodiment, the interposer has a pocket or cavity to host an integrated circuit. More specifically, the integrated circuit may be a power management integrated circuit for a power converter, such as a buck converter. The power management integrated circuit may be configured to perform voltage regulation and/or voltage scaling using the one or more passive electrical components. One or more vias, such as through-silicon vias, arranged in the interposer and forming electrical connections between the passive electrical components and the integrated circuit through the interposer, are filled with, for example, copper and electrically isolated from the interposer. An inductor (and/or other passive components) can then be stacked and attached on top of the interposer.

In a further embodiment, the integrated circuit is monolithically integrated in the interposer. This can be achieved by post-processing the interposer to add through-silicon vias from the top and/or bottom side. An inductor (and/or other electrical

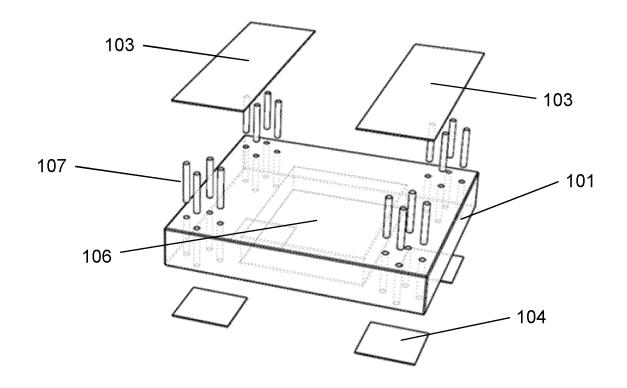

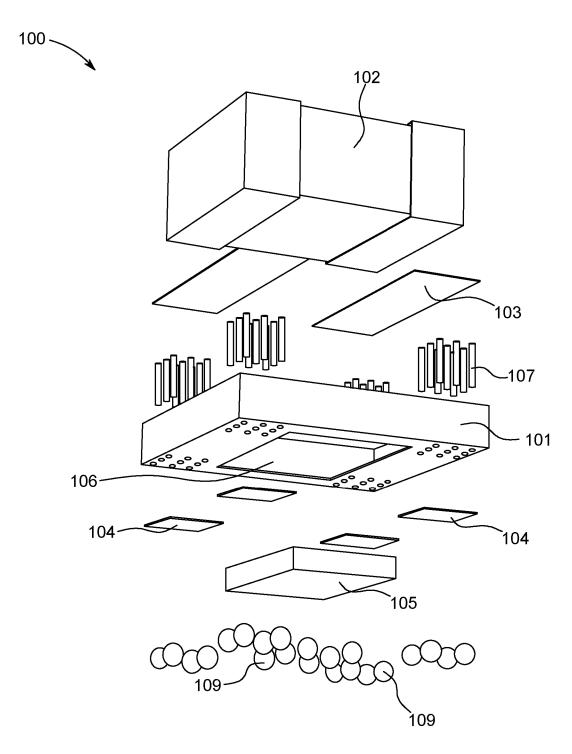

components) can then be stacked and attached on top of the interposer. The power converter assembly may further comprise routing layers on both sides of the interposer. the routing layers comprising conductive traces. In this embodiment there is, preferably, insulation layers on both sides of the interposer between the interposer and the routing layers to prevent electrical connection between the interposer and the routing layers. Moreover, as illustrated in the example of fig. 5, the power converter assembly may comprise top-side pads connected to the passive component(s). Each top-side pad may be connected to one or more bottom-side pads through a plurality of parallel through-interposer-vias, such as through-silicon-vias. In this regard it can be noted that the through-interposer-vias are configured to carry high electrical current of the power converter, which breaks with the common practice of using through-vias to carry signals. Further vias and electrical connections, such as second through-vias form the bottom side to the integrated circuit, or other connections of, for example the integrated circuit is placed in a recess, and/or third through-vias from the top side to the integrated circuit may also be used. The second and/or third through-vias mat typically be much thinner than the through-interposer-vias, which are dimensioned to carry high electrical current.

The inventors have realized that by using a silicon interposer designed to have a high thermal conductivity as a routing substrate and a thermal dissipater, a very small power converter with improved thermal performance can be implemented. Using a silicon substrate allows integration with integrated circuits processes, such as post-processing of the integrated circuits to add through-silicon vias and redistribution layers.

#### **Description of drawings**

5

10

15

20

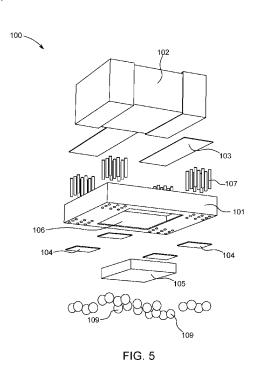

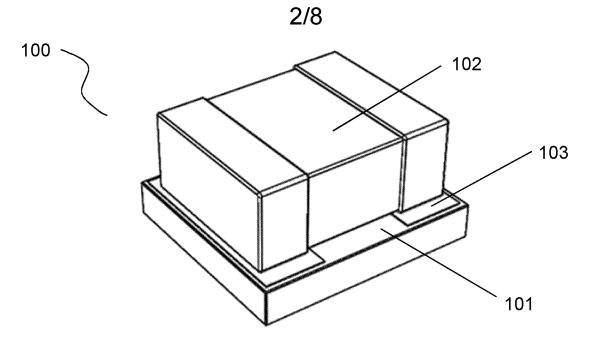

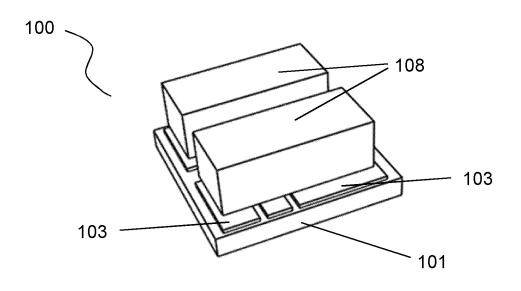

- Fig. 1 shows an embodiment of the presently disclosed power converter assembly having an integrated circuit monolithically integrated in an interposer.

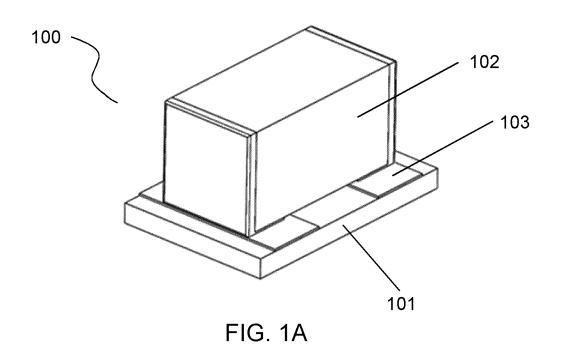

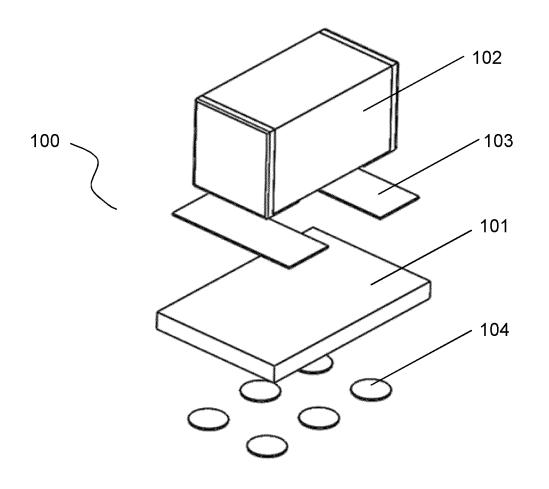

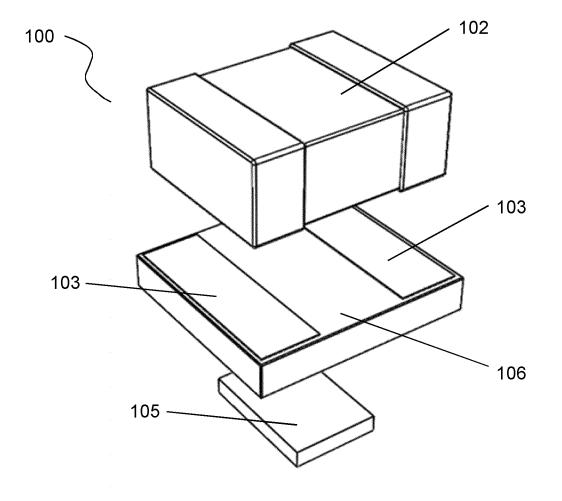

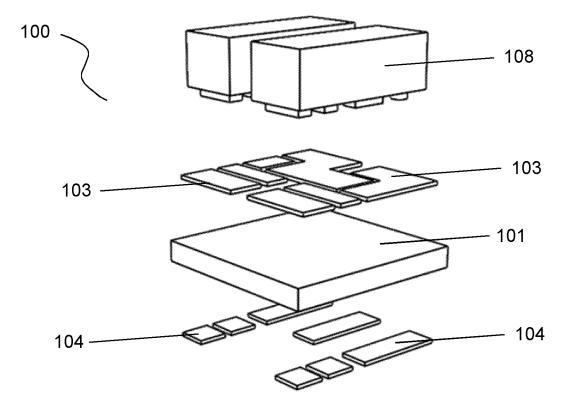

- Fig. 2 shows an embodiment of the presently disclosed power converter assembly having an integrated circuit in a cavity of an interposer.

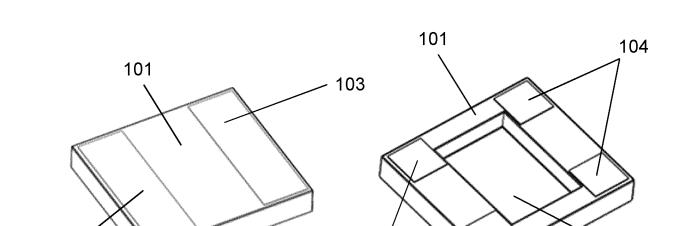

- Fig. 3 shows an exemplary embodiment of the presently disclosed interposer.

- Fig. 4 shows a further embodiment of the presently disclosed power converter assembly having two GaN FETs stacked on top of the interposer.

- Fig. 5 shows an embodiment of the presently disclosed power converter assembly having an integrated circuit in a cavity of an interposer.

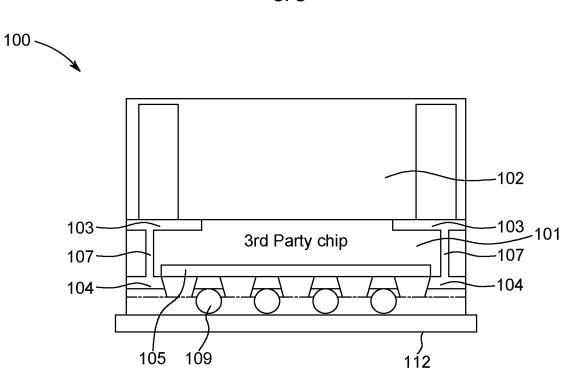

- Fig. 6 shows an embodiment of the presently disclosed power converter assembly further comprising a printed circuit board, which could, alternatively, be any other

suitable type of substrate, on which the interposer is mounted and in this case may serve as a part of the power converter assembly

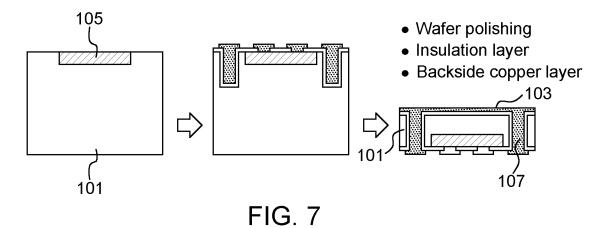

Fig. 7 shows an exemplary embodiment and process of variants of through-vias, such as through-silicon vias.

Fig. 8-9 show further embodiment of the presently disclosed power converter assembly.

## **Detailed description**

The present disclosure relates to power converter assembly comprising an interposer, preferably a silicon interposer. The power converter assembly comprises an active circuit, such as an integrated circuit, which may be, for example, a power management integrated circuit. The active circuit can be monolithically integrated in the interposer. Alternatively, the active circuit can be arranged in a cavity or pocket of the interposer. One or more passive electrical components, such as an inductor, can then be stacked on a top side of the interposer. Preferably, the interposer has one or more through silicon vias forming electrical connections in the silicon substrate. The power converter assembly may take various shapes and configurations, which are described in further detail in the present disclosure. The integrated circuit and the passive electrical components may be configured to perform a power conversion of an input voltage to an output voltage.

20

25

30

35

5

10

15

An interposer is an electrical interface routing between one socket or connection to another. The conventional purpose of an interposer is to spread a connection to a wider pitch or to reroute a connection to a different connection. An interposer can also be seen as a bridge or a conduit that allows electrical signals to pass through it and onto another element. Interposers are frequently used in multi die chips or boards.

According to a first example, a silicon interposer with a pocket to host a power management circuit for a buck converter is used. This embodiment, in which a cavity or pocket of the interposer is used to host the integrated circuit, has the advantage that third-party integrated circuits, including power management integrated circuits, can be arranged in the cavity. The interposer can then be post-processed to create through silicon vias and routing to make the power assembly complete. The silicon substrate has through silicon vias filled with copper and electrically isolated from the substrate. The buck converter's inductor is then stacked and attached on top of the substrate.

According to a second example, a power management integrated circuit of a buck

WO 2021/234158 PCT/EP2021/063689 5

converter is integrated in a silicon die. The silicon die is then post-processed to add through silicon vias and, optionally, bottom side routing and/or top side routing. Adding routing layers on both sides of the interposer is an efficient way of integrating the whole power converter function into a single entity with a very high routing density. The power converter assembly may further comprise routing layers on both sides of the interposer, the routing layers comprising conductive traces. In this embodiment there is, preferably, insulation layers on both sides of the interposer between the interposer and the routing layers to prevent electrical connection between the interposer and the routing layers. The insulation layers preferably have a thickness of at least 100 nm. The buck converter's inductor is then stacked and attached on top of the substrate.

The power converter assembly may further comprise active electrical components stacked on the top side of the interposer. In certain embodiments, the power converter assembly may further comprise an integrated functional application. As an example, the load or application that the power is used for may be integrated. This may involve, for example, a micro controller arranged on the top side of the interposer. In a further embodiment, the load or application may be the integrated circuit arranged in a cavity or pocket of the interposer or monolithically integrated in the interposer. In this embodiment the power converter assembly may comprise a power management integrated circuit stacked on the interposer, wherein the integrated circuit constitutes a load of the power converter assembly. The power converter assembly may further comprise the load and/or an integrated application of the power converter arranged on the top side of the interposer. In one embodiment, the power converter assembly comprises bottom side routing on the bottom side of the interposer. This can be achieved, for example, by post-processing the interposer to add bottom side copper. Similarly, the power converter assembly may comprise top side routing on the top side of the interposer. This can be achieved, for example, by post-processing the interposer to add top side copper. One or more of any of the vias may be connected to the top side routing.

30

35

5

10

15

20

25

The power converter assembly may further comprise routing layers on both sides of the interposer, the routing layers comprising conductive traces. The thickness of the conductive traces may be between 1µm and 50µm. In this embodiment there is, preferably, insulation layers on both sides of the interposer between the interposer and the routing layers to prevent electrical connection between the interposer and the routing layers. Moreover, as illustrated in the example of fig. 5, the power converter

5

10

15

20

assembly may comprise top-side pads connected to the passive component(s). Each top-side pad may be connected to one or more bottom-side pads through a plurality of parallel through-interposer-vias, such as through-silicon-vias. In this regard it can be noted that the through-vias are configured to carry high electrical current of the power converter, which breaks with the common practice of using through-vias to carry signals. A high electrical current may, in this context, be seen as a current of at least 50 mA, preferably at least 100 mA, more preferably at least 500 mA, even more preferably at least 1000 mA. The through-vias may have a diameter between 10µm and 100µm. The plurality of parallel through-interposer-vias represent a way of increasing the current-carrying capability. At the same time, the plurality of parallel through-interposervias is a way of increasing the area between the vias and the substrate through which heat can be dissipated. This embodiment can therefore achieve superior thermal cooling performance compared to convention PCB technology. Preferably, the throughvias comprise an electrical insulation layer towards the interposer. Atomic-layerdeposition aluminum oxide (ALD-AL<sub>2</sub>O<sub>3</sub>) may be used as electrical insulation layer. ALD-AL<sub>2</sub>O<sub>3</sub> has properties that can enhance breakdown voltage and increase thermal performance. The following table provides a comparison of SiO<sub>2</sub> and ALD-AL<sub>2</sub>O<sub>3</sub>.

| Properties              | Thermally-growth SiO₂ | ALD-AL <sub>2</sub> O <sub>3</sub> |  |

|-------------------------|-----------------------|------------------------------------|--|

| Thermal conductivity    | 1.3 (W/mK)            | 2 (W/mK)                           |  |

| Dielectric strength     | 10 (MV/cm)            | 30 (MV/cm)                         |  |

| Deposition temperature  |                       |                                    |  |

| (e.g. < 400 C° for CMOS | 900 – 1100 C°         | 150 – 300 C°                       |  |

| compatible)             |                       |                                    |  |

This means that even if a thinner, such as three times thinner, layer of ALD-AL<sub>2</sub>O<sub>3</sub> (compared to SiO<sub>2</sub>) is used, the same required electrical isolation can be achieved. At the same time 53% better thermal dissipation is achieved. AL<sub>2</sub>O<sub>3</sub> also enables post-CMOS integration due to its low deposition temperature.

The power converter assembly can be mounted on a printed circuit board. In this embodiment, further routing may be added to the printed circuit board. In one embodiment of the presently disclosed power converter assembly, the vias comprise first through-interposer-vias from the top side of the interposer to a bottom side of the interposer, wherein the first through-vias form electrical connections between the

5

10

15

20

25

30

35

passive electrical components and routing on the printed circuit board. An example of this is shown in fig. 5, in which top-side pads (103) are connected to first throughinterposer-vias (107) extending through the interposer (101) and connected to bottomside pads (104). Fig. 5 does not show a printed circuit board, which would be possible to include. In fig. 5 the integrated circuit (105) is arranged in a cavity (106) of the interposer (101). Therefore, the power converter assembly may comprise top-side pads (103) for connecting the one or more passive electrical components to the throughvias. The power converter assembly may further comprise bottom-side pads (104) connected to the through-interposer-vias (107). The power converter assembly may comprise second through-vias, or any suitable electrical connections, from the bottom side of the interposer to the integrated circuit. For example, the second through-vias may connect a conducting layer or conductive traces of the bottom side with a monolithically embedded integrated circuit or integrated circuit arranged in a cavity of the interposer. If the power converter assembly is mounted on a printed circuit board to bottom-side pads may be connected to routing on the printed circuit board via solder balls. The routing on the printed circuit board is further connected to the integrated circuit from the bottom side of the interposer. If the integrated circuit is exposed, as in fig. 5, the routing can be connected to terminals of the integrated circuit. The interposer may comprise a lid on a bottom side of the interposer for closing the cavity, thereby encapsulating the integrated circuit in the interposer. If the cavity has a lid, or if the integrated circuit is monolithically integrated in the silicon interposer, vias can be postprocessed to form second through-vias from the bottom side of the interposer to the integrated circuit. One non-limiting example of such a process is shown in fig. 7. The power converter assembly may further comprise third through-vias from the top side of the interposer to the integrated circuit. The third through-vias may be defined as vias connecting a top side conductive layer to monolithically embedded integrated circuit or integrated circuit arranged in a cavity of the interposer.

The thermal conductivity of a material is a measure of its ability to conduct heat. The defining equation for thermal conductivity is  $q = -k\Delta T$ , where q is the heat flux, k is the thermal conductivity and  $\Delta T$  is the temperature gradient. In the International System of Units (SI), thermal conductivity is measured in watts per meter-kelvin (W/(mK). The presently disclosed power converter assembly may be made of a material having a high thermal conductivity, preferably a thermal conductivity of at least 50 W/(m K), more preferably a thermal conductivity of at least 100 W/(m K), even more preferably a

thermal conductivity of at least 150 W/(m K) at 27°C. Silicon has a thermal conductivity of 159 W/(m K) at 27°C.

Passive components may comprise capacitors, inductors and/or transformers. In one embodiment of the power converter assembly, the one or more passive electrical components comprise at least one inductor. By using a 3D interposer with an integrated power management circuit and a stacked inductor, not only the thermal performance is improved. The footprint compared to existing power converter solutions can also be significantly reduced. If a relatively large inductor, or several inductors, are stacked on the interposer to cover at least 50% of the surface of the top side, or even 70% or more of the surface of the top side, the performance in terms of power conversion per surface unit can be very high. Fig. 6 shows an example of how an inductor can occupy most of the space of the top surface of the interposer. Furthermore, the one or more passive electrical components may comprise at least one capacitor and/or at least one transformer and/or at least one resistor.

Power management circuits are devices that control the flow and direction of electrical power. Many electrical devices have multiple internal voltages (e.g., 5 V, 3.3 V, 1.8 V, etc.) and sources of external power (e.g., wall outlet, battery, etc.), meaning that the power design of the device has multiple requirements for operation. Power management integrated circuit (PMIC) may refer to devices having an individual power related function or that incorporate more than one function, such as different power conversions and power controls such as voltage supervision and undervoltage protection.

25

30

35

5

10

15

20

The PMIC may include battery management, voltage regulation, and charging functions. The presently disclosed power converter assembly may be configurable to perform dynamic voltage scaling. In one embodiment the power converter assembly is a DC-DC power converter assembly having multiple input voltage levels and multiple output voltage levels wherein the power management integrated circuit is configured to manage a number of power conversion rates between the input voltage levels and output voltage levels. In one embodiment the DC-DC power converter assembly is configured to convert an input voltage of 2.2-6 V to an output voltage of 0.5-4.2 V.

The power converter assembly may be a DC-DC power converter assembly, such as a buck converter assembly. Other possible converters are boost converters and fly-back

converters. The converters of the power converter assembly may be step-up or stepdown converters. The power converter assembly may also be a resonant power converter assembly.

In one embodiment of the power converter assembly the one or more electrical components comprise gallium nitride (GaN) transistors. GaN transistors are, in general terms, faster and more efficient than classic silicon devices. GaN has, to some extent, demonstrated the capability to be the displacement technology for silicon semiconductors in power conversion applications. However, the GaN technology is not compatible with the available silicon device processing and manufacturing technology. Therefore, preferably GaN transistors are stacked on the interposer. In one embodiment, the one or more passive electrical components comprise two GaN field-effect transistors, wherein power converter assembly is a GaN half-bridge power stage and wherein the integrated circuit is a gate driver integrated circuit.

15

20

25

30

35

10

5

The dimensions of the power converter assembly depend on the application and power conversion requirements. However, in order to improve the heat dissipation, the interposer may have a total height (including the integrated circuit) of at least 130% of the height of the integrated circuit. The power converter assembly ma comprise and interposer having a total height of at least 0.2 mm, preferably at least 0.3 mm. Fig. 6 shows an embodiment of the presently disclosed power converter assembly mounted on a printed circuit board. The height of this embodiment is approximately 1.5 mm, including the inductor. The length and width are approximately 2.2 mm. This exemplary embodiment has an input voltage  $V_{\text{IN}} = 5 \text{ V}$ , an output voltage  $V_{\text{OUT}} = 1.2 \text{ V}$  and an output current  $I_{\text{OUT}} = 1 \text{ A}$ .

## **Detailed description of drawings**

The invention will in the following be described in greater detail with reference to the accompanying drawings. The drawings are exemplary and are intended to illustrate some of the features of the presently disclosed power converter assembly, and are not to be construed as limiting to the presently disclosed invention.

Fig. 1 shows an embodiment of the presently disclosed power converter assembly (100). Fig. 1A shows the assembly (100) in an assembled configuration. Fig. 1B shows the assembly (100) in an exploded view. In this embodiment the integrated circuit is not visible since it is monolithically integrated in the silicon interposer (101). A passive

**WO 2021/234158 PCT/EP2021/063689** 10

electrical component in the form of an inductor (102) is stacked on the top side of the interposer (101). A pair of top-side pads (103) are connected to the inductor (102). A number of bottom-side pads (104) are arranged on the bottom side of the interposer (101).

5

10

15

20

25

30

35

Fig. 2 shows an embodiment of the presently disclosed power converter assembly (100). Fig. 2A shows the assembly (100) in an assembled configuration. Fig. 2B shows the assembly (100) in an exploded view. In this embodiment the integrated circuit (105) is arranged in a cavity (not visible) of the interposer. A passive electrical component in the form of an inductor (102) is stacked on the top side of the interposer (101). A pair of top-side pads (103) are connected to the inductor (102).

Fig. 3 shows an exemplary embodiment of the presently disclosed interposer (101). Fig. 3A-B show the interposer (101) in an assembled configuration. Fig. 3C shows the interposer (101) in an exploded view. The interposer (101) has a cavity (106), two pair of top-side pads (103) and four bottom-side pads (104). The top-side pads (103) may be connected to a passive component, such as the inductor (102) shown in fig. 1. Through-interposer-vias (107), such as through-silicon-vias, are arranged in the interposer (101) and form electrical connections between the top-side pads (103) and bottom-side pads (104). The vias (107) are configured in groups of parallel vias connected between a top-side pad (103) and a bottom-side pad (104) to be able to carry power of the power converter assembly and to increase the area between the vias and the interposer (101).

Fig. 4 shows a further embodiment of the presently disclosed power converter assembly (101) having two GaN FETs (108) stacked on top of the interposer (101). Fig. 4A shows the assembly (100) in an assembled configuration. Fig. 4B shows the assembly (100) in an exploded view. In this embodiment the integrated circuit is not visible since it is monolithically integrated in the silicon interposer (101). The interposer (101) has top-side pads (103) and bottom-side pads (104).

Fig. 5 shows an exploded view of an embodiment of the presently disclosed power converter assembly (100). The power converter assembly (100) has an integrated circuit (105) arranged in a cavity (106) of the interposer (101). A passive electrical component in the form of an inductor (102) is stacked on the top side of the interposer (101). A pair of top-side pads (103) are connected to the inductor (102). The top-side

5

10

15

20

25

30

35

pads (103) are further connected to vias (107) extending through the interposer (101) and connected to bottom-side pads (104). The vias (107) are configured in groups of parallel through-interposer-vias connected between a top-side pad (103) and a bottom-side pad (104) to be able to carry power of the power converter assembly. On the bottom side of the power converter assembly solder balls (109) are used to connect the bottom-side pads (104) to bottom side routing. If the integrated circuit (105) is exposed on the bottom side, the routing can be directly connected to electrical connectors of the integrated circuit (105). If the integrated circuit (105) is monolithically integrated in the silicon interposer (101), it may be necessary to have second through-vias (not visible) from the bottom side of the interposer (101) to the integrated circuit (105). There may also be a lid on the cavity (106) of the interposer (101).

Fig. 6 shows an embodiment of the presently disclosed power converter (100) assembly on a printed circuit board (112). The power converter assembly (100) has an integrated circuit (105) embedded in the interposer (101). A passive electrical component in the form of an inductor (102) is stacked on the top side of the interposer (101). Top-side pads (103) are connected to the inductor (102). The top-side pads (103) are further connected to through-interposer-vias (107) extending through the interposer (101) and connected to bottom-side pads (104). The power converter (100) assembly is disposed on a printed circuit board (112). Second through-vias (not visible) are used to connect bottom side routing from the bottom side of the interposer (101) to the integrated circuit (105). insular

Fig. 7 shows an exemplary embodiment and process of the through-interposer-vias (107). In fig. 7, through-interposer-vias (107) are shown. As a person skilled in the art would understand, there are suitable technology processes for making electrical connections to the integrated circuit, including second and/or third through-vias. The vias do not necessarily have to be formed using the exemplary process. Connection between the top side of the interposer (101) and the integrated circuit (105) and/or between the bottom side of the interposer (101) and the integrated circuit (105) can be formed in this manner.

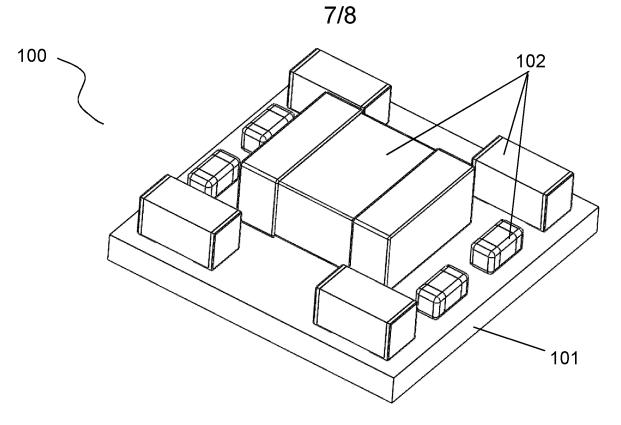

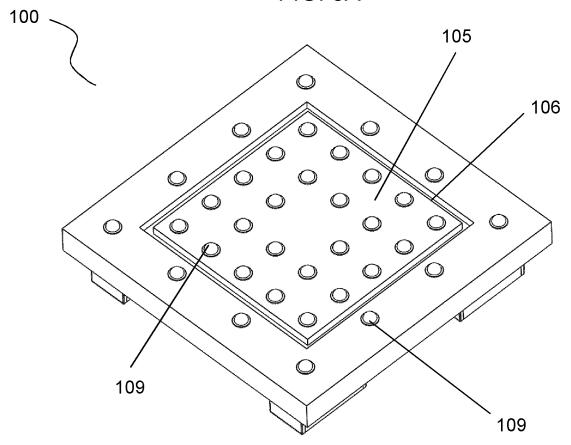

Fig. 8 shows an embodiment of the presently disclosed power converter assembly (100). Fig. 8A shows the assembly (100) from the top side and fig. 8B shows the assembly (100) from the bottom side. In this embodiment the integrated circuit (105) is a PMIC (105) arranged in a cavity (106) of the interposer. A number of passive

electrical components (102) are stacked on the top side of the interposer (101). A number of solder balls (109) on the bottom side of the interposer (101) and integrated circuit (105) can be used to connect the integrated circuit (105) and passive electrical components (102) to routing, which, preferably is disposed on a printed circuit board.

5

10

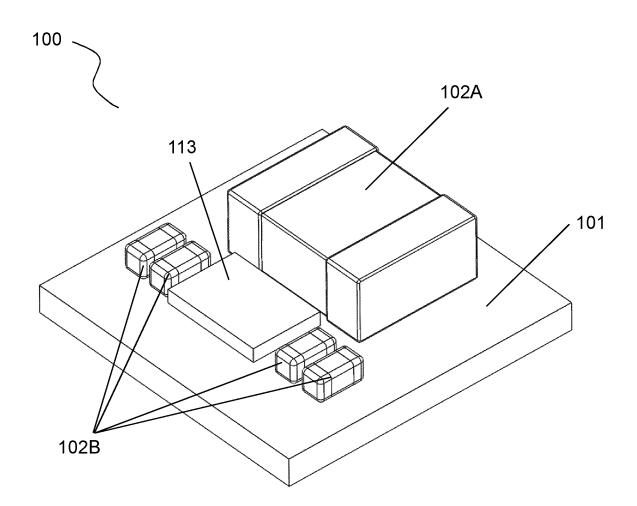

Fig. 9 shows an embodiment of the presently disclosed power converter assembly (100), wherein an integrated circuit (not visible) is integrated in the interposer (101). An inductor (102A), four capacitors (102B) and an additional IC, such as a power management IC (113) in the form of a Buck converter IC, are stacked on the top side of the interposer (101). In this embodiment the integrated circuit (not visible) inside the interposer (101) may be, for example, a micro controller, which may constitute the load or application that is powered by the power converter arrangement.

#### List of elements in figures

15 100 – power converter assembly

101 – interposer

102 - passive electrical component

103 – top-side pads

104 – bottom-side pads

20 105 – integrated circuit

106 - cavity

107 – through-interposer-vias

108 - GaN FET

109 – solder balls

25 112 – printed circuit board

113 – additional IC/power management IC

#### Further details of the invention

- 1. A power converter assembly comprising:

- an interposer;

- an integrated circuit, such as a power management integrated circuit,

arranged in a cavity or pocket of the interposer or monolithically integrated

in the interposer;

- one or more electrical components stacked on a top side of the interposer;

and

5

10

25

30

one or more vias, such as through silicon vias, arranged in the interposer forming electrical connections between the electrical components and the integrated circuit through the interposer,

wherein the integrated circuit and the electrical components are configured to perform a power conversion of an input voltage to an output voltage.

- 2. The power converter assembly according to item 1, wherein the electrical components comprise passive electrical components and/or active electrical components stacked on the top side of the interposer.

- 3. The power converter assembly according to any one of the preceding items, further comprising a printed circuit board, wherein the power converter assembly is mounted on the printed circuit board.

- 4. The power converter assembly according to item 3, wherein the vias comprise first through-vias from the top side of the interposer to a bottom side of the interposer, wherein the first through-vias form electrical connections between the passive electrical components and routing on the printed circuit board.

- 5. The power converter assembly according to item 4, wherein the routing on the printed circuit board is further connected to the integrated circuit from the bottom side of the interposer.

- 6. The power converter assembly according to any one of items 3-5, further comprising top-side pads for connecting the one or more passive electrical components to the through-vias.

- 7. The power converter assembly according to any one of items 3-6, further comprising bottom-side pads connected to the through-vias.

- 8. The power converter assembly according to any one of the preceding items, wherein the vias comprise second through-vias from the bottom side of the interposer to the integrated circuit.

- The power converter assembly according to any one of the preceding items, further comprising third through-vias from the top side of the interposer to the integrated circuit.

- 5 10. The power converter assembly according to any one of the preceding items, further comprising a micro controller arranged on the top side of the interposer, the power converter assembly further comprising a load and/or an integrated application of the power converter arranged on the top side of the interposer.

- 10 11. The power converter assembly according to any one of items 1-9, further comprising a power management integrated circuit stacked on the interposer, wherein the integrated circuit constitutes a load of the power converter assembly.

- 15 12. The power converter assembly according to any one of the preceding items, wherein the interposer is made of silicon.

20

25

30

- 13. The power converter assembly according to any one of the preceding items, wherein the interposer comprises a lid on a bottom side of the interposer for closing the cavity, thereby encapsulating the integrated circuit in the interposer.

- 14. The power converter assembly according to any one of the preceding items, wherein the interposer is made of a material having a high thermal conductivity, preferably a thermal conductivity of at least 50 W/(m K), more preferably a thermal conductivity of at least 100 W/(m K), even more preferably a thermal conductivity of at least 150 W/(m K).

- 15. The power converter assembly according to any one of the preceding items, wherein the one or more passive electrical components comprise at least one inductor.

- 16. The power converter assembly according to item 15, wherein the at least one inductor covers at least 50% of the surface of the top side, preferably at least 70% of the surface of the top side.

- 17. The power converter assembly according to any one of the preceding items, wherein the one or more passive electrical components comprise at least one capacitor and/or at least one transformer and/or at least one resistor.

- 5 18. The power converter assembly according to any one of the preceding items, further comprising bottom side routing on the bottom side of the interposer.

10

15

25

- 19. The power converter assembly according to item 18, wherein the bottom side routing is connected to bottom-side pads, preferably through solder balls.

- 20. The power converter assembly according to any one of the preceding items, further comprising top side routing on the top side of the interposer.

- 21. The power converter assembly according to item 20, wherein the one or more vias are connected to the bottom side routing and/or the top side routing.

- 22. The power converter assembly according to any one of the preceding items, wherein the integrated circuit is a power management integrated circuit.

- 23. The power converter assembly according to item 22, wherein the power management integrated circuit is configured to perform voltage regulation and/or voltage scaling using the one or more passive electrical components.

- 24. The power converter assembly according to any one of the preceding items, wherein the power converter assembly is a DC-DC power converter assembly.

- 25. The power converter assembly according to item 24, wherein the DC-DC power converter assembly is a buck converter.

- 30 26. The power converter assembly according to item 24, wherein the DC-DC power converter has multiple input voltage levels and multiple output voltage levels and wherein the power management integrated circuit is configured to manage a number of power conversion rates between the input voltage levels and output voltage levels.

- 27. The power converter assembly according to item 24, wherein the DC-DC power converter assembly is configured to convert an input voltage of 2.2-6 V to an output voltage of 0.5-4.2 V.

- 28. The power converter assembly according to any one of the preceding items, wherein the one or more passive electrical components comprise two GaN field-effect transistors, and wherein power converter assembly is a GaN half-bridge power stage and wherein the integrated circuit is a gate driver integrated circuit.

- 29. The power converter assembly according to any one of the preceding items, wherein the interposer has a total height of at least 130% of the height of the integrated circuit.

- 30. The power converter assembly according to any one of the preceding items, wherein the interposer has a total height of at least 0.2 mm, preferably at least 0.3 mm.

#### Claims

5

10

15

20

- 1. A power converter assembly comprising:

- an interposer;

- an integrated circuit, such as a power management integrated circuit,

arranged in a cavity or pocket of the interposer or monolithically integrated in the interposer;

- one or more electrical components stacked on a top side of the interposer; and

- one or more vias arranged in the interposer,

wherein the integrated circuit and the electrical components are configured to

perform a power conversion of an input voltage to an output voltage.

- 2. The power converter assembly according to claim 1, wherein the electrical components comprise passive electrical components and/or active electrical components stacked on the top side of the interposer.

- 3. The power converter assembly according to any one of the preceding claims, further comprising a printed circuit board, wherein the interposer assembly is mounted on the printed circuit board, wherein the vias comprise first through-interposer-vias from the top side of the interposer to a bottom side of the interposer, wherein the first through-interposer-vias form electrical connections between the passive electrical components and routing on the printed circuit board, and wherein the routing on the printed circuit board is further connected to the integrated circuit from the bottom side of the interposer.

- 4. The power converter assembly according to claim 3, further comprising top-side pads for connecting the one or more passive electrical components to the through-interposer-vias.

- 5. The power converter assembly according to any one of claims 3-4, further comprising bottom-side pads connected to the through-interposer-vias.

- 6. The power converter assembly according to any one of the preceding claims, comprising a plurality of parallel through-interposer-vias, such as through-

silicon-vias, connecting top-side pads connected to the one or more passive electrical components with bottom-side pads.

- 7. The power converter assembly according to claim 6, wherein the through-interposer-vias have a diameter between 10µm and 100µm.

- 8. The power converter assembly according to any one of claims 6-7, wherein the through-interposer-vias comprise an electrical insulation layer towards the interposer.

10

15

20

5

- 9. The power converter assembly according to claim 8, wherein the insulation layer is atomic-layer-deposition aluminum oxide (ALD-AL<sub>2</sub>O<sub>3</sub>).

- 10. The power converter assembly according to any one of claims 6-9, wherein the through-interposer-vias are configured for carrying high electrical current of the power converter assembly.

- 11. The power converter assembly according to any one of the preceding claims, wherein the vias comprise second through-vias or other suitable electrical connections from the bottom side of the interposer to the integrated circuit.

- 12. The power converter assembly according to any one of the preceding claims, further comprising third through-vias from the top side of the interposer to the integrated circuit.

25

13. The power converter assembly according to any one of the preceding claims, further comprising a micro controller arranged on the top side of the interposer, the power converter assembly further comprising a load and/or an integrated application of the power converter arranged on the top side of the interposer.

- 14. The power converter assembly according to any one of the preceding claims, further comprising routing layers on both sides of the interposer, the routing layers comprising conductive traces.

- 35

- 15. The power converter assembly according to claim 14, further comprising insulation layers on both sides of the interposer between the interposer and the

5

10

20

30

35

routing layers to prevent electrical connection between the interposer and the routing layers.

- 16. The power converter assembly according to claim 15, wherein the insulation layers have a thickness of at least 100 nm.

- 17. The power converter assembly according to any one of the preceding claims, further comprising a power management integrated circuit stacked on the interposer, wherein the integrated circuit constitutes a load of the power converter assembly.

- 18. The power converter assembly according to any one of the preceding claims, wherein the interposer is made of silicon.

- 15 19. The power converter assembly according to any one of the preceding claims, wherein the interposer comprises a lid on a bottom side of the interposer for closing the cavity, thereby encapsulating the integrated circuit in the interposer.

- 20. The power converter assembly according to any one of the preceding claims, wherein the integrated circuit is a power management integrated circuit, wherein the power management integrated circuit is configured to perform voltage regulation and/or voltage scaling using the one or more passive electrical components.

- 21. The power converter assembly according to any one of the preceding claims, wherein the power converter assembly is a DC-DC power converter assembly.

- 22. The power converter assembly according to claim 21, wherein the DC-DC power converter has multiple input voltage levels and multiple output voltage levels and wherein the power management integrated circuit is configured to manage a number of power conversion rates between the input voltage levels and output voltage levels.

- 23. The power converter assembly according to any one of the preceding claims, wherein the one or more passive electrical components comprise two GaN field-effect transistors, and wherein power converter assembly is a GaN half-

**WO 2021/234158 PCT/EP2021/063689** 20

bridge power stage and wherein the integrated circuit is a gate driver integrated circuit.

FIG. 1B

FIG. 2A

FIG. 2B

103

FIG. 3A FIG. 3B

104

FIG. 3C

FIG. 4A

FIG. 4B

5/8

FIG. 5

6/8

FIG. 6

FIG. 8A

FIG. 8B

FIG. 9

#### INTERNATIONAL SEARCH REPORT

International application No PCT/EP2021/063689

A. CLASSIFICATION OF SUBJECT MATTER INV. H05K1/18 H01L23/538 H01L23/13 ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)  $H05\,K-H01\,L$

HOOK HOIL

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                             | Relevant to claim No.      |

|-----------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Х         | US 2016/113117 A1 (LIU CHUN-TIAO [TW] ET<br>AL) 21 April 2016 (2016-04-21)                                                     | 1-6,10,<br>12-15,<br>20-23 |

| Υ         | figure 5 paragraphs [0038], [0042]                                                                                             | 7-9,11,<br>16-19           |

| Υ         | US 2017/236809 A1 (TRIMBERGER STEPHEN M<br>[US] ET AL) 17 August 2017 (2017-08-17)<br>figure 3<br>paragraphs [0002], [0028]    | 17,18                      |

| Y         | US 9 761 547 B1 (KUNKEE ELIZABETH T [US]<br>ET AL) 12 September 2017 (2017-09-12)<br>figure 4<br>column 5, paragraph 23-58<br> | 11,19                      |

| X Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | X See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier application or patent but published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filing date but later than the priority date claimed | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art  "&" document member of the same patent family |  |

| Date of the actual completion of the international search  16 July 2021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date of mailing of the international search report $26/07/2021$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Name and mailing address of the ISA/ European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                           | Authorized officer  Dardel, Blaise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

## **INTERNATIONAL SEARCH REPORT**

International application No

PCT/EP2021/063689

| C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                                                                 |                       |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Category*                                            | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                              | Relevant to claim No. |  |  |  |

| Υ                                                    | US 9 740 079 B1 (DAVIDS PAUL [US] ET AL)<br>22 August 2017 (2017-08-22)<br>column 9, lines 40-45                                                                                                                                                                                                                                                | 7                     |  |  |  |

| Y                                                    | CHUI K ET AL: "High Aspect Ratio (>10:1) Via-Middle TSV with High-k Dielectric Liner Oxide", 2019 IEEE 21ST ELECTRONICS PACKAGING TECHNOLOGY CONFERENCE (EPTC), IEEE, 4 December 2019 (2019-12-04), pages 721-724, XP033732058, D0I: 10.1109/EPTC47984.2019.9026683 [retrieved on 2020-03-05] page 722; table 1                                 | 8,9                   |  |  |  |

| Υ                                                    | US 2015/179610 A1 (KHAN REZAUR RAHMAN [US]                                                                                                                                                                                                                                                                                                      | 16                    |  |  |  |

| Α                                                    | ET AL) 25 June 2015 (2015-06-25) paragraphs [0026], [0093]                                                                                                                                                                                                                                                                                      | 14,15                 |  |  |  |

| A                                                    | US 2017/331371 A1 (PARTO PARVIZ [US]) 16 November 2017 (2017-11-16) claims 1,35 figures 3-5                                                                                                                                                                                                                                                     | 1-23                  |  |  |  |

| Α                                                    | SRIDHAR ARVIND ET AL: "Exploration of inductor-based hybrid integrated voltage regulator architectures", 2016 6TH ELECTRONIC SYSTEM-INTEGRATION TECHNOLOGY CONFERENCE (ESTC), IEEE, 13 September 2016 (2016-09-13), pages 1-6, XP033015888, DOI: 10.1109/ESTC.2016.7764679 the whole document                                                   | 1-23                  |  |  |  |

| Α                                                    | SUN RUIZE ET AL: "Development of GaN Power IC Platform and All GaN DC-DC Buck Converter IC", 2019 31ST INTERNATIONAL SYMPOSIUM ON POWER SEMICONDUCTOR DEVICES AND ICS (ISPSD), IEEE, 19 May 2019 (2019-05-19), pages 271-274, XP033574628, DOI: 10.1109/ISPSD.2019.8757674 ISBN: 978-1-7281-0580-2 [retrieved on 2019-07-08] the whole document | 1-23                  |  |  |  |

| Α                                                    | O'MATHUNA CIAN: "PwrSiP power supply in package power system in package", 2016 INTERNATIONAL SYMPOSIUM ON 3D POWER ELECTRONICS INTEGRATION AND MANUFACTURING (3D-PEIM), IEEE, 13 June 2016 (2016-06-13), pages 1-21, XP032962515, DOI: 10.1109/3DPEIM.2016.7570569 the whole document                                                           | 1-23                  |  |  |  |

## **INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/EP2021/063689

| Patent document<br>cited in search report | Publication<br>date | Patent family<br>member(s)                           | Publication<br>date                    |

|-------------------------------------------|---------------------|------------------------------------------------------|----------------------------------------|

| US 2016113117 A1                          | 21-04-2016          | CN 105529916 A<br>TW 201616621 A<br>US 2016113117 A1 | 27-04-2016<br>01-05-2016<br>21-04-2016 |

| US 2017236809 A1                          | 17-08-2017          | US 2017236809 A1<br>WO 2017142637 A1                 | 17-08-2017<br>24-08-2017               |

| US 9761547 B1                             | 12-09-2017          | NONE                                                 |                                        |

| US 9740079 B1                             | 22-08-2017          | NONE                                                 |                                        |

| US 2015179610 A1                          | 25-06-2015          | EP 2887393 A2<br>US 2015179610 A1                    | 24-06-2015<br>25-06-2015               |

| US 2017331371 A1                          | 16-11-2017          | US 2017331371 A1<br>US 2019229618 A1                 | 16-11-2017<br>25-07-2019               |

|                                           |                     |                                                      |                                        |