# Cryogenic multiplexing using selective area grown nanowires

Olšteins, Dāgs; Nagda, Gunjan; Carrad, Damon J.; Beznasyuk, Daria V.; Petersen, Christian E. N.; Martí-Sánchez, Sara; Arbiol, Jordi; Jespersen, Thomas S.

Published in: Nature Communications

Link to article, DOI: 10.1038/s41467-023-43551-1

Publication date: 2023

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Olšteins, D., Nagda, G., Carrad, D. J., Beznasyuk, D. V., Petersen, C. E. N., Martí-Sánchez, S., Arbiol, J., & Jespersen, T. S. (2023). Cryogenic multiplexing using selective area grown nanowires. *Nature Communications*, 14(1), Article 7738. https://doi.org/10.1038/s41467-023-43551-1

# General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# nature communications

**Article**

https://doi.org/10.1038/s41467-023-43551-1

# Cryogenic multiplexing using selective area grown nanowires

Received: 31 May 2023

Accepted: 13 November 2023

Published online: 25 November 2023

Check for updates

Dāgs Olšteins  $\textcircled{0}^{1,2}$ , Gunjan Nagda  $\textcircled{0}^{1}$ , Damon J. Carrad  $\textcircled{0}^{2}$ , Daria V. Beznasyuk  $\textcircled{0}^{2}$ , Christian E. N. Petersen  $\textcircled{0}^{2}$ , Sara Martí-Sánchez $^{3}$ , Jordi Arbiol  $\textcircled{0}^{3,4}$  & Thomas S. Jespersen  $\textcircled{0}^{1,2} \boxtimes$

Bottom-up grown nanomaterials play an integral role in the development of quantum technologies but are often challenging to characterise on large scales. Here, we harness selective area growth of semiconductor nanowires to demonstrate large-scale integrated circuits and characterisation of large numbers of quantum devices. The circuit consisted of 512 quantum devices embedded within multiplexer/demultiplexer pairs, incorporating thousands of interconnected selective area growth nanowires operating under deep cryogenic conditions. Multiplexers enable a range of new strategies in quantum device research and scaling by increasing the device count while limiting the number of connections between room-temperature control electronics and the cryogenic samples. As an example of this potential we perform a statistical characterization of large arrays of identical quantum dots thus establishing the feasibility of applying cross-bar gating strategies for efficient scaling of future selective area growth quantum circuits. More broadly, the ability to systematically characterise large numbers of devices provides new levels of statistical certainty to materials/device development.

Quantum electronics are rapidly maturing towards large-scale integrated (LSI) circuits incorporating a multitude of interacting quantum devices. There is therefore an onus on potential quantum materials candidates to exhibit both high-precision reproducibility and scalability potential. Semiconductor nanowires (NWs) constitute an important platform for quantum electronics since the electronic confinement intrinsic to the structure simplifies the fabrication of complex devices<sup>1-4</sup>, the flexibility of contact materials enables hybridization with important quantum materials such as superconductors<sup>1,3,5-9</sup>, and increased capacity for strain relaxation over bulk materials enables exploration of exotic heterostructures<sup>2,6,8,10</sup>. Conventional NWs grown perpendicular to the substrate have been highly successful for highperformance electronics, simple complementary circuits, and in fundamental mesoscopic physics<sup>1-11</sup>. However, the difficulty in fabricating individual vertical devices, and the insufficient precision and yield of techniques for transferring NWs to the planar geometry compatible with standard semiconductor processing<sup>12-14</sup> has thus far inhibited the development of LSI NW circuits. A promising alternative is the bottom-up growth of in-plane semiconductor NWs directly on a suitable device substrate using selective area growth<sup>15-18</sup> (SAG). In SAG, the positions and dimensions of NWs are controlled by lithographically defining openings in a dielectric mask, enabling the controlled growth of large-scale networks and NW arrays<sup>16,19,20</sup>. While proof-of-principle single NW devices, e.g., field effect transistors (FETs)<sup>21,22</sup>, Hall crosses<sup>23</sup>, quantum interferometers<sup>20,24</sup>, hybrid superconducting devices<sup>24,25</sup>, and quantum dots (QDs)<sup>26</sup> have been reported, scalability towards integrated quantum circuits—a central motivation behind the development of SAG and similar bottom-up grown planar nanostructures<sup>27,28</sup>—has not been addressed.

Here, we make the first demonstration of LSI circuits based on SAG. Starting from large arrays of thousands of SAG NWs we fabricate multiplexer (MUX) circuits that operate at the deep cryogenic

<sup>1</sup>Center For Quantum Devices, Niels Bohr Institute, University of Copenhagen, 2100 Copenhagen, Denmark. <sup>2</sup>Department of Energy Conversion and Storage, Technical University of Denmark, 2800 Kongens Lyngby, Denmark. <sup>3</sup>Catalan Institute of Nanoscience and Nanotechnology (ICN2), CSIC and BIST, Campus UAB, Bellaterra, Barcelona, Catalonia, Spain. <sup>4</sup>ICREA, Passeig de Lluís Companys 23, 08010 Barcelona, Catalonia, Spain. <sup>5</sup>e-mail: tsaje@dtu.dk

conditions relevant to quantum electronics. Cryogenic multiplexers are key ingredients towards scaling quantum electronics<sup>29-32</sup> as the number of addressable devices scales exponentially—rather than linearly—with the number of connecting control lines. This is crucial for reducing heat load from wiring between the cryogenic sample and room temperature, and integrated MUX circuits allow highly dense packing of devices utilizing chip-area conventionally required for bonding and routing. Our setup allows us to address and measure 512 individual SAG quantum devices using only 37 control lines.

Our architecture also includes de-multiplexers (d-MUX) connected back-to-back with the corresponding MUX, enabling us to unambiguously confirm the functionality of the circuit, identify faulty operation among the thousands of NW FETs, and self-correct against most failure modes.

Introducing on-chip multiplexing to bottom-up grown nanostructures enables new strategies in quantum electronics research, such as automated searches through large ensembles of devices for rare or exotic phenomena, and systematic, statistically significant exploration of the correlation between device performance and, e.g., materials properties or device geometry. To demonstrate the potential of the latter we perform a statistical characterization of device reproducibility within a large array of nominally identical SAG NW QDs. QD arrays are promising candidates for implementing quantum computation and simulation<sup>33-35</sup>, and quantifying device-to-device reproducibility-enabled by the MUX circuit-is crucial for the successful development of cross-bar gate architectures which constitute an important strategy for limiting gate counts in realistic large-scale implementations<sup>36,37</sup>. We find that all QDs of the array can be concurrently tuned to the Coulomb Blockade using only three shared cross-bar gates further confirming the potential of SAG as a scalable platform for quantum devices.

#### Results

#### Material and electrical properties

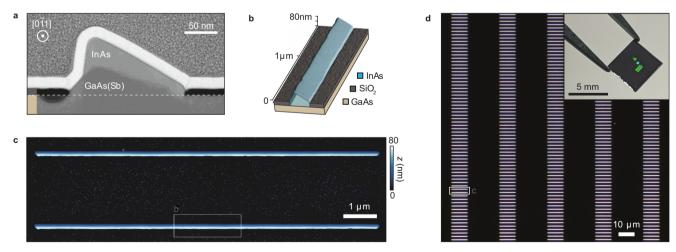

Our circuits are based on [0  $\bar{1}$  1] oriented InAs SAG NWs grown using molecular beam epitaxy (MBE) on GaAs (3 1 1)A substrates. See Methods and Supplementary Section S1 for details. Figure 1a shows a cross-sectional high-angle annular dark-field scanning transmission electron microscope (HAADF STEM) micrograph of a single NW, and Fig. 1b shows a combined schematic and atomic force microscope

(AFM) micrograph of an NW section. The conducting InAs channel sits atop an insulating GaAs substrate and GaAs(Sb) buffer  $^{20}$ . The NWs are terminated with {111}A facets as a consequence of the (311)A substrate symmetry, producing the asymmetric cross-section. Detailed structural analysis is presented in Supplementary Section S2. Figure 1c, d illustrate the capacity for scale-up inherent to SAG, through an AFM micrograph and dark-field optical microscope micrograph of representative sections of a 512  $\times$  16 array of nominally identical 10  $\mu$ m-long NWs. The inset to Fig. 1d shows a photograph of a cleaved 5  $\times$  5 mm piece of the growth wafer containing ~18,000 SAG NWs, 9216 of which were used for device fabrication; the diffraction from the large arrays is visible.

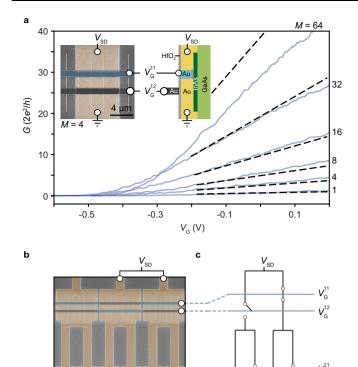

The Fig. 2a inset shows a scanning electron microscope (SEM) micrograph of a typical device along with a schematic cross-section. The device includes 4 SAG NWs connected in parallel by Ti/Au ohmic contacts and a 1 µm long gated segment (see Methods for fabrication details). Two gates are seen: one which acts on the exposed InAs NWs (blue), thereby controlling the conductivity, and one which is screened by the metal contact, and thus has no effect on the underlying NW (gray). This gate is, however, important for the MUX operation as discussed below. Figure 2a shows the conductance, G, as a function of gate voltage,  $V_G$ , measured at a temperature of  $T = 20 \,\mathrm{mK}$  for 6 different devices with varying numbers of NWs, M=1,4,16,32,64 after subtraction of a constant series resistance  $R_S$  (see Methods). The devices act as normally-on, n-type FETs with identical threshold voltages, and the dashed lines show a common fit to the relation  $G = KM(V_G - V_{TH})$  with fixed parameters K = 0.12 mS/V and  $V_{\rm TH} = -0.4 \, \text{V}$ . Except for M = 64 where G is somewhat lower than expected, G is proportional to M as expected for equally contributing NWs and the linear scaling with  $V_G$  is typical for NW FETs. The deviation for M = 64 may be due to a high sensitivity to the estimate of  $R_S$  when the device resistance is low (Methods). Importantly, Figure 2a shows that SAG devices manufactured in parallel exhibit consistent G vs.  $V_{G}$ , with reproducible, M-independent  $V_{TH}$ , enabling the use of large-M FETs as building blocks in LSI SAG circuits.

#### **SAG multiplexers**

We utilize the  $V_{\rm TH}$  reproducibility to operate the circuit shown in Fig. 2b. SAG FETs are connected in a hierarchical MUX structure, with each level consisting of devices fabricated on different rows of the SAG

**Fig. 1** | **Nanowire structure and morphology. a** Cross-sectional HAADF STEM micrograph of a SAG NW, showing the InAs conducting channel atop the GaAs substrate and GaAs(Sb) MBE-grown buffer. The NW exhibits an asymmetric triangular shape imposed by the (311) substrate symmetry. The shape is not important for the present study which could equally well have been based on NWs grown on, e.g., (111) or (100) substrates with higher symmetry. **b** Combined schematic/3D

AFM micrograph of a 2 µm long section of a single NW. **c** AFM micrograph of two SAG NWs. **d** Optical dark-field microscope image of a section of an InAs SAG NW array. Each NW is -150 nm wide and 10 µm-long and individual NWs are spaced by  $20\times 2$  µm. Inset: Photograph of an as-grown sample. The large NW arrays are visible in green due to the diffraction of light.

10 µm

**Fig. 2** | **Realizing a MUX circuit using NW FETs. a** Conductance, G, as a function of gate voltage  $V_G$  for NW FETs based on 1, 4, 8, 16, 32, and 64 SAG NWs in parallel (blue) and expected linear trends (black dashed). The inset shows an SEM micrograph of an NW FET based on 4 SAG NWs, Ti/Au Ohmic contacts in gold, Ti/Au gate in blue. The gate in dark gray is screened by the underlying ohmic contact as illustrated by the cross-section schematic. **b** SEM micrograph of NW FETs arranged in a MUX circuit. Gates are screened in alternating elements as indicated by the blue/gray false coloring. **c** A schematic representation of the circuit in **b**.

NW array in Fig. 1d. Each gate spans the respective row, and the positions of the gated segment alternate such that for each NW FET, one gate (blue) tunes the carrier density of the NWs while the other is screened (gray). Input signals are thus directed through the MUX as illustrated in the schematic in Fig. 2c. With this design, each additional level doubles the number of outputs such that an n level MUX has  $2^n$  outputs and requires 2n gates for operation.

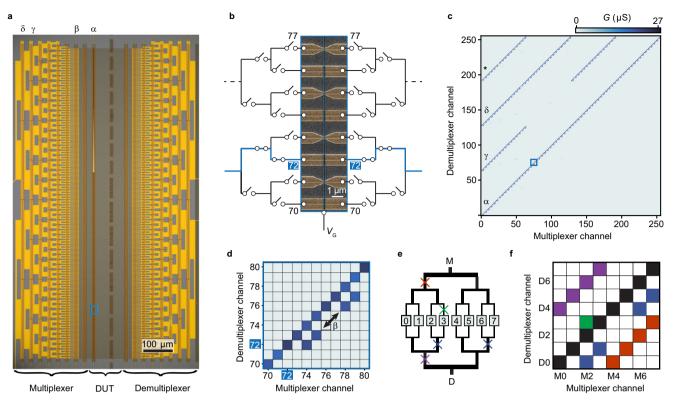

Figure 3a shows an optical micrograph of an 8-level MUX circuit connected back-to-back to a corresponding 8-level d-MUX. The circuit has a footprint of ~ 0.6 × 1.1 mm and incorporates 8192 individual SAG NWs in the form of 1996 interconnected FETs. Combining the 32 gate lines with two separate source-drain pairs enables individual addressing of any of the 512 devices under test (DUT) located in the gap between the MUX/d-MUX units. Where the DUT themselves consist of FETs with a single common gate, and 37 control lines thereby enabling experiments on 512 devices. In our case, the DUT in Fig. 3a consists of SAG devices with different functionalities and properties. For example, the SEM micrograph in Fig. 3b shows DUT devices #70-#77. Oddnumbered devices #71, #73, #75, #77 are SAG NW FETs with a contact separation of 100 nm and a common top gate. The even-numbered channels consist of continuous metal paths covering the NW. These allow confirmation of the MUX/d-MUX function irrespective of the DUT performance and also provide reference measurements of the MUX and d-MUX series resistance.

Before discussing DUT properties, we analyze the functionality of the MUX/d-MUX circuit. Figure 3c shows the conductance of the

circuit for each of the 65536 combinations of the first 256 MUX and d-MUX channels. The measurement was performed with positive voltage on the DUT gates, which were therefore all conducting. Indeed, high conductance is observed along the main diagonal,  $(\alpha)$ , which corresponds to both MUX and d-MUX addressing the same DUT channel. This confirms that none of the 1996 SAG NW FETs of the MUX/d-MUX pair fail to conduct which would lead to regions of no conductance along the diagonal. In the case of negative  $V_G$  on the DUT level, every second pixel of the diagonal has G = 0 (Supplementary section S5). In the ideal case, the diagonal would be the only non-zero value of the conductance matrix. However, finite offdiagonal conductivity also appears following a repeating pattern every 4, 64, and 128 channels in Fig. 3c and d  $(\beta, \gamma, \delta)$ . Since the FETs are conducting at  $V_G = 0 \text{ V}$ , finite current at these combinations of MUX and d-MUX channels corresponds to rows of NW FETs failing to respond to the gates. This was likely due to a break in gate lines or a failing bond wire, which can occur for large, complex circuits. Figure 3e, f schematically illustrates the correlation between the patterns of the matrix and FETs failing to pinch-off turn-off at various positions in the circuit. For example, a non-responsive gate, on the second d-MUX level from the DUT layer (blue cross in Fig. 3e) would allow transport for (MUX, d-MUX) combinations (2, 0), (3, 1), (6, 4), and (7, 5) as indicated by blue in Fig. 3f. Comparing to the measurement in Fig. 3c, d the periodically repeating off-diagonal pattern can be assigned to failures of one of the gates in the MUX levels marked with the corresponding labels in Fig. 3a. The additional feature appearing at d-MUX channel 192 (\*) results from the combination of faulty FETs at channels 64 and 128 (Supplementary Section S7 and S8 provide further analysis of the faults of the circuit).

Importantly, the MUX/d-MUX configuration allows for identifying and in most cases self-corrects for malfunctioning elements of the SAG circuit; the double redundancy makes the measurement tolerant towards non-symmetrical errors, as, e.g., a non-functioning gate on the MUX side will be intrinsically corrected for by the function of the corresponding d-MUX gate. While errors appearing symmetrically in the MUX and d-MUX side of the circuit cannot be corrected for, they can be identified in the conductance matrix and the corresponding DUT can be excluded from experiments/analysis. This is schematically illustrated in Fig. 3e, f: if the MUX/d-MUX FETs fail to pinch-off at the symmetric red/purple positions, addressing levels 0, 1, 2, and 3 would also mix signals from levels 4, 5, 6, 7, respectively. Such a situation is readily identified by the symmetric off-diagonal nonvanishing elements in the conductance matrix (purple and red in Fig. 3f). We note that FETs failing to pinch-off would pass unnoticed in single-ended MUX layouts<sup>32</sup> where DUT share a common ground. The opposite case, where MUX FETs fail to open would result in periodic non-conductive elements in the diagonal of the matrix. Other examples of MUX/d-MUX circuits are discussed in Supplementary Section S6, showing that even with the number of failures typical for research-level devices, the selfcorrecting nature of MUX/d-MUX configuration generally protects against a reduction in the available number of DUT. We note that broken gate lines or failing bond wires should be readily eliminated and with a near unity yield of the NW FETs, future device generations could be successfully operated in a single-ended configuration.

As a final comment on MUX operation, we note that bandwidth is a key issue for control electronics. In our experiments, bandwidth was limited by the cryogenic setup, being optimized for low electron temperature, including 5 kHz low-pass filtering of each line. The MUX operation was uninhibited up to these frequencies (Supplementary Section S9). While we expect much higher bandwidth for individual NW similar to previous InAs NW devices operating at GHz<sup>11,38,39</sup>, a radiofrequency MUX will require a circuit redesign to account, e.g., for impedance matching at every node, and may likely require additional fabrication steps. We also note, that while heat dissipation is negligible in the current experiments it could become relevant upon increasing

**Fig. 3** | **Operation of a NW-based MUX-deMUX circuit. a** Optical microscope image of MUX/d-MUX circuit based on InAs SAG NW arrays. Devices under test (DUT) are labeled  $\alpha$  and labels  $\beta$ ,  $\gamma$ ,  $\delta$  indicate FET gates failing to deplete and related to corresponding off-diagonal signals in panel **c**. For the device shown 500 of the 512 lines were connected at the DUT level. The number of DUT was doubled from  $2^8$  = 256 by using two source/drain pairs. **b** SEM micrograph of the DUT area indicated by the blue box in panel **a**, showing 8 devices connected to the MUX and d-MUX channels. Every second channel is shorted for use as a reference to obtain the series resistance of the adjacent channel. **c** Conductance matrix of all 65,536 combinations of source and drain channels of the first 256 connections of the

circuit. The color of each pixel corresponds to the measured conductance of the specific channel combination. The uninterrupted diagonal feature shows that all of the DUTs are addressable and conducting. **d** Expanded view of the conductance matrix within the blue square in **c**. **e** Schematic three-level MUX/d-MUX. The colored crosses mark a FET failing to deplete and panel **f** shows the corresponding signatures on the conductance matrix. When operated at the diagonal, the circuit is immune to such errors except for symmetric pairs such as red/purple. This case can, however, be identified in the conductance matrix as regions with symmetric off-diagonal finite conductance, and accounted for in subsequent measurements.

operation frequency and/or further scaling up of the number of channels.

# **Multiplexing of QD arrays**

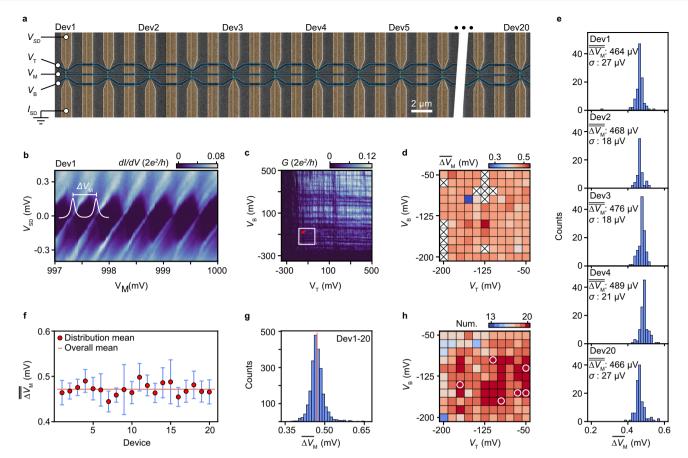

Eliminating the device-count roadblock by the MUX/d-MUX circuit enables fundamentally new experimental approaches in quantum electronics. For example, adding statistical significance to the characterization and optimization of device performance and material properties is crucial for efforts toward up-scaling quantum circuits. As an example, we demonstrate here the use of the circuit for establishing statistical reproducibility within large ensembles of lithographically identical devices. An array of 50 lithographically identical SAG QD devices were embedded in the DUT layer as shown in Fig. 4a. Potentials  $(V_{\rm T}, V_{\rm M}, V_{\rm B})$  applied to three shared gates (top, middle, bottom) simultaneously tune the electrostatics of all 50 devices. This cross-bar approach is an important strategy for limiting the gate count in the upscaling of QD arrays, however, the successful operation requires significant reproducibility between devices<sup>36,37</sup>. Here, we benchmark the consistency in the SAG NW QD array by comparing the statistical distributions of QD parameters among devices labeled Dev1-Dev20. First, however, since InAs SAG QDs have thus far not been demonstrated, we establish the characteristics of a single device (Dev1).

Figure 4c shows G vs.  $V_{\rm T}$  and  $V_{\rm B}$  for fixed  $V_{\rm M}$ =1V. Pinch-off is at ~-150 mV for both  $V_{\rm T}$  and  $V_{\rm B}$ , and horizontal/vertical structures are attributed to resonances below each gate modulating the transmission<sup>5</sup>. With both gates near pinch-off, electrons are ideally

confined to an NW segment below the middle gate, thus defining a QD. Indeed, fixing  $V_{\rm T}$  and  $V_{\rm B}$  at the position of the red dot in Fig. 4c, diamond-shaped regions of low conductance associated with Coulomb blockade (CB) are observed in the map of the differential conductance,  $dI/dV_{SD}$ , vs. source bias  $V_{SD}$  and  $V_{M}$ , as shown in Fig. 4b. The V<sub>SD</sub>-height of the diamonds provides an estimate of the QD addition energy, being the sum of the electrostatic charging energy  $E_{C}$  and the single-particle level spacing  $\Delta E$ . As discussed in Supplementary Section S10 the QDs have  $\Delta E \ll E_C$  and from Fig. 4b we estimate  $E_{\rm C} \sim 210 \pm 15 \,\mu \rm eV$ . The capacitance between the QD and the middle plunger gate is estimated as  $C_G = e/\overline{\Delta V_M} = 0.4$  fF where  $\overline{\Delta V_M} = 0.46$  mV is the average value CB peaks spacings in the range of Fig. 4b. This  $C_G$ value agrees with the result (0.37fF) of simple capacitance estimate based on the gate layout (Supplementary Section S10) and thus supports that in this particular gate-configuration, the QD confinement is defined by gates as intended.

To investigate the sensitivity to the tuning,  $G(V_{\rm M})$  was measured at  $11\times 11$  equally spaced  $(V_{\rm T},V_{\rm B})$  points, spanning the white square in Fig. 4c. CB peaks were identified at 108 of the 121 gate-tunings and Fig. 4d shows the corresponding map of  $\overline{\Delta V_{\rm M}}$ . No systematic trend is observed and the distribution of  $\overline{\Delta V_{\rm M}}$  shown in Fig. 4e (top), is symmetric with a mean  $\overline{\Delta V_{\rm M}} = 464~\mu{\rm V}$  and standard deviation  $\sigma = \pm~27~\mu{\rm V}$ , again consistent with a QD defined between the top and bottom gates.

The choice of range for the cross-bar gate-tunings in Fig. 4b, d was based on the gate characterization specific for Dev1 (Fig. 4c). We now use the MUX circuit to gather statistics for the different devices in

**Fig. 4** | **Characterization of the SAG QD ensemble. a** SEM micrograph of an array of NW QD devices. Contacts (gold) are spaced by 900 nm, top/middle/bottom cross-bar gates (blue) are 300/200/300 nm wide and have a 150 nm spacing. The gates are shared between 50 devices of which 20 were analyzed in detail. Each device is paired with a short line for reference. **b** Source-drain bias spectrum (differential conductance dl/dV vs.  $V_{\rm SD}$  and  $V_{\rm M}$ ) of Dev1 showing Coulomb diamonds. When sweeping  $V_{\rm M}$  the barrier gates were compensated for a slight capacitive cross coupling (Supplementary Section S10).  $V_{\rm T}$  and  $V_{\rm B}$  starting values correspond to the red point in **c**. **c** Conductance G vs.  $V_{\rm T}$  and  $V_{\rm B}$  for Dev1. **d** Map showing  $\overline{\Delta V_{\rm M}}$  of Dev1

for various  $V_{\rm T}$  and  $V_{\rm B}$  combinations within the white square in  ${\bf c}$ . Crossed points have no identifiable Coulomb peaks.  ${\bf e}$  Histograms of  $\overline{\Delta V_{\rm M}}$  for Dev1-Dev4 and Dev20 in the same  $V_{\rm T}$  and  $V_{\rm B}$  range.  ${\bf f}$  Distribution of  $\overline{\Delta V_{\rm M}}$  for Dev1-Dev20. The red dots indicate  $\overline{\Delta V_{\rm M}}$  of each device and orange line shows  $\overline{\Delta V_{\rm M}}$  across all devices, error bars show the standard deviation.  ${\bf g}$  Histogram showing overall distribution of  $\overline{\Delta V_{\rm M}}$  for all devices. Orange line indicates the average value and corresponds to the line in  ${\bf f}$ .  ${\bf h}$  Number of devices with observable Coulomb peaks at each combination of  $V_{\rm T}$  and  $V_{\rm B}$ . White circles show points where all 20 devices have  $\overline{\Delta V_{\rm M}}$  within  $2\sigma$  of the common average.

order to probe the consistency across the array while keeping these same tuning parameters. Values of  $\overline{\Delta V_{\rm M}}$  were extracted from  $G(V_{\rm M})$ traces measured for all devices and all gate-points. All devices were operational and exhibited coulomb blockade and from the resulting 2420 gate-traces, 17,924 CB peaks were identified and fitted. Examples of measured data and peak analysis are presented in Supplementary Sections S12 and S13. The distributions of  $\overline{\Delta V_{\rm M}}$  for all devices are included in Supplementary Section S14 and examples for Dev1-4 and Dev20 are shown in Fig. 4e. A comparison of the distributions and their mean values,  $\overline{\Delta V_{\rm M}}$ , among the devices of the array, is shown in Fig. 4f. Except for Dev7, the distribution means fall within one  $\sigma$  of the overall common mean. The spread between devices could be affected by structural variations between nanowires due to SAG processing or to variations in post-growth device processing. The spread within each devices could be related to changes in the effective confinement potential with gate tunings and may be different between devices due to random impurity in the vicinity of the devices.

Finally, Fig. 4g shows the joint distribution of all  $\overline{\Delta V_{\rm M}}$  and Fig. 4h illustrates the number of devices displaying CB for all measured combinations of  $V_{\rm T}$ ,  $V_{\rm B}$ . In 27 out of the 121 point in cross-bar gate space, all 20 devices simultaneously exhibited CB. The circles mark the 7 tunings where all devices fulfill the stricter criterion of showing CB and having  $\overline{\Delta V_{\rm M}}$  within  $\pm 2\sigma$  of the joint mean peak spacing.

Figure 4f-h constitutes a key result of the current study, establishing both a level of device-to-device reproducibility supporting the potential of SAG for as a scalable platform for quantum electronics. Further, the statistical bench-marking of the QD devices explicitly demonstrates a key example of the new possibilities enabled by the integration of MUX/d-MUX circuits.

# **Discussion**

In conclusion, we successfully fabricated and operated cryogenic multiplexers/de-multiplexer circuits based on InAs NWs grown bottom-up by selective area growth. The circuit removes the limitations on device count in conventional cryogenic electronics thus enabling new experimental strategies such as searches through large ensembles of devices for rare or exotic phenomena, establishing the correlation between device performance and materials properties or device geometry, and establishing the statistical reproducibility among devices—a prerequisite for further scaling quantum of circuits. This capacity was demonstrated by statistically characterizing an ensemble of SAG QDs. The methods developed here complement cryo complementary metal oxide semiconductor technologies by enabling scaling and integration within bottom-up quantum materials which constitute a unique platform, e.g., with hybrid semiconductor/superconductor quantum technologies. In general, the methods

enable optimization of quantum materials and devices based on the automated acquisition of statistically significant datasets rather than proof-of-principle examples. This direction will be empowered by the ongoing developments of advanced data evaluation<sup>40</sup> and machine learning<sup>41-43</sup> for unsupervised and optimized acquisition and tuning of large ensembles of quantum devices with many tuning parameters<sup>44-46</sup>. The circuit may be expanded further by replacing the single lines in the current design with a multi-channel bus<sup>47</sup> to enable, e.g., integration of charge sensors, multi-terminal devices, complex gate architectures, and/or the operating the MUX as a multi-channel DAC<sup>48</sup>.

## **Methods**

For SAG fabrication and synthesis, a 10 nm SiO<sub>2</sub> mask layer was first deposited on epi-ready GaAs (3 1 1)A substrates by plasma-enhanced chemical vapor deposition. 0.15 × 10 μm rectangular openings were defined in the oxide along the  $[0\bar{1}1]$  direction by e-beam lithography (EBL) and dry etching. The openings were arranged in  $512 \times 16$  arrays with a pitch of 2 um and 20 um along the  $[0\bar{1}1]$  and  $[\bar{2}33]$ , respectively (Fig. 1d). GaAs(Sb)/InAs double layer NWs were selectively grown in the openings where the GaAs(Sb) buffer was introduced to improve the crystal surface for the subsequent InAs transport channel<sup>20</sup>. Synthesis details and structural analysis are provided in Supplementary Sections S1 and S2. For device fabrication, Ti/Au ohmic contacts to the SAG NWs were defined on the growth substrate by standard EBL, metal evaporation, and liftoff. Subsequently, a 15 nm HfO2 gate dielectric was deposited by atomic layer deposition and top-gates were defined by electron beam lithography, metal evaporation, and liftoff. The QD devices in Fig. 4 have a contact separation of 900 nm, top/middle/ bottom cross-bar gates are 300/200/300 nm wide, and have a 150 nm spacing. Electrical measurements were carried out in a dilution refrigerator with a base temperature of 20 mK. The conductance,  $G = I/V_{SD}$ , where I is the drain current generated by source voltage  $V_{SD}$ , was measured as a function of the gate potential,  $V_G$ , using standard lock-in techniques. The series resistance R<sub>S</sub> for data presented in Fig. 2 was estimated by fitting the  $G(V_G)$  traces with the standard expression<sup>49</sup>  $G = (R_S + \frac{L^2}{\mu_{FE}C(V_G - V_{TH})})^{-1}$  where L is the gate length, C is gate capacitance simulated as described in Supplementary Sections S3 and S4, and  $\mu_{\rm FE}$  is the electron mobility. When sweeping  $V_{\rm M}$  in the QD measurements, the barrier gates were compensated for a slight capacitive cross-coupling (Supplementary Section S10).

#### Data availability

The electrical transport data generated in this study have been deposited in the Figshare database under the accession code https://doi.org/10.11583/DTU.c.6788313.

# References

- Mourik, V. et al. Signatures of majorana fermions in hybrid superconductor-semiconductor nanowire devices. Science 336, 1003–1007 (2012).

- Hu, Y. et al. A Ge/Si heterostructure nanowire-based double quantum dot with integrated charge sensor. Nat. Nanotechnol. 2, 622–625 (2007).

- Hofstetter, L., Csonka, S., Nygård, J. & Schönenberger, C. Cooper pair splitter realized in a two-quantum-dot Y-junction. *Nature* 461, 960–963 (2009).

- Fasth, C., Fuhrer, A., Björk, M. T. & Samuelson, L. Tunable double quantum dots in InAs nanowires defined by local gate electrodes. *Nano Lett.* 5, 1487–1490 (2005).

- Doh, Y.-J. et al. Tunable supercurrent through semiconductor nanowires. Science 309, 272–275 (2005).

- Xiang, J., Vidan, A., Tinkham, M., Westervelt, R. M. & Lieber, C. M. Ge/Si nanowire mesoscopic Josephson junctions. *Nat. Nano-technol.* 1, 208–213 (2006).

- Larsen, T. W. et al. Semiconductor-nanowire-based superconducting gubit. Phys. Rev. Lett. 115, 127001 (2015).

- Krogstrup, P. et al. Epitaxy of semiconductor-superconductor nanowires. Nat. Mater. 14. 400–406 (2015).

- Hays, M. et al. Direct microwave measurement of andreev-boundstate dynamics in a semiconductor-nanowire Josephson junction. *Phys. Rev. Lett.* 121, 047001 (2018).

- Svensson, J., Dey, A. W., Jacobsson, D. & Wernersson, L.-E. III–V nanowire complementary metal–oxide semiconductor transistors monolithically integrated on Si. Nano Lett. 15, 7898–7904 (2015).

- Tomioka, K., Yoshimura, M. & Fukui, T. A III-V nanowire channel on silicon for high-performance vertical transistors. *Nature* 488, 189–192 (2012).

- Freer, E. M., Grachev, O., Duan, X., Martin, S. & Stumbo, D. P. Highyield self-limiting single-nanowire assembly with dielectrophoresis. *Nat. Nanotechnol.* 5, 525–530 (2010).

- Yao, J., Yan, H. & Lieber, C. M. A nanoscale combing technique for the large-scale assembly of highly aligned nanowires. *Nat. Nano*technol. 8, 329–335 (2013).

- 14. Li, M. et al. Bottom-up assembly of large-area nanowire resonator arrays. *Nat. Nanotechnol.* **3**, 88–92 (2008).

- Wang, N. et al. Shape engineering of InP nanostructures by selective area epitaxy. ACS Nano 13, 7261–7269 (2019).

- 16. Op het Veld, R. L. et al. In-plane selective area InSb–Al nanowire quantum networks. *Commun. Phys.* **3**, 1–7 (2020).

- Raya, A. M. et al. GaAs nanoscale membranes: prospects for seamless integration of III-Vs on silicon. *Nanoscale* 12, 815–824 (2020).

- Bollani, M. et al. Selective area epitaxy of GaAs/Ge/Si nanomembranes: a morphological study. Crystals 10, 57 (2020).

- Aseev, P. et al. Selectivity map for molecular beam epitaxy of advanced III–V quantum nanowire networks. Nano Lett. 19, 218–227 (2019).

- 20. Krizek, F. et al. Field effect enhancement in buffered quantum nanowire networks. *Phys. Rev. Mater.* **2**, 093401 (2018).

- Beznasyuk, D. V. et al. Doubling the mobility of InAs/InGaAs selective area grown nanowires. *Phys. Rev. Mater.* 6, 034602 (2022).

- 22. Friedl, M. et al. Template-assisted scalable nanowire networks. *Nano Lett.* **18**, 2666–2671 (2018).

- 23. Lee, J. S. et al. Selective-area chemical beam epitaxy of In-plane InAs one-dimensional channels grown on InP(001), InP(111)B, and InP(011) surfaces. *Phys. Rev. Mater.* **3**, 084606 (2019).

- Vaitiekėnas, S. et al. Selective-area-grown semiconductorsuperconductor hybrids: a basis for topological networks. *Phys. Rev. Lett.* 121, 147701 (2018).

- 25. Hertel, A. et al. Gate-tunable transmon using selective-area-grown superconductor-semiconductor hybrid structures on silicon. *Phys. Rev. Appl.* **18**, 034042 (2022).

- Ten Kate, S. C. et al. Small charging energies and g-factor anisotropy in PbTe quantum dots. Nano Lett. 22, 7049–7056 (2022).

- Schmid, H. et al. Template-assisted selective epitaxy of III–V nanoscale devices for co-planar heterogeneous integration with Si. Appl. Phys. Lett. 106, 233101 (2015).

- 28. Gooth, J. et al. Ballistic one-dimensional inas nanowire cross-junction interconnects. *Nano Lett.* **17**, 2596–2602 (2017).

- Pauka, S. et al. Characterizing quantum devices at scale with custom cryo-CMOS. Phys. Rev. Appl. 13, 054072 (2020).

- Paquelet Wuetz, B. et al. Multiplexed quantum transport using commercial off-the-shelf CMOS at sub-kelvin temperatures. Quantum Inf. 6, 1–8 (2020).

- 31. Smith, L. W. et al. Statistical study of conductance properties in one-dimensional quantum wires focusing on the 0.7 anomaly. *Phys. Rev. B* **90**, 045426 (2014).

- Smith, L. W. et al. High-throughput electrical characterization of nanomaterials from room to cryogenic temperatures. ACS Nano 14, 15293–15305 (2020).

- 33. Loss, D. & DiVincenzo, D. P. Quantum computation with quantum dots. *Phys. Rev. A* **57**, 120 (1998).

- Tomioka, K., Motohisa, J. & Fukui, T. Rational synthesis of atomically thin quantum structures in nanowires based on nucleation processes. Sci. Rep. 10, 1–9 (2020).

- 35. Vandersypen, L. M. & Eriksson, M. A. Qauntim computing with semiconductor spins. *Phys. Today* **72**, 8–38 (2019).

- Li, R. et al. A crossbar network for silicon quantum dot qubits. Sci. Adv. 4, eaar3960 (2018).

- 37. Borsoi, F. et al. Shared control of a 16 semiconductor quantum dot crossbar array. https://arxiv.org/abs/2209.06609 (2022).

- Johansson, S., Memisevic, E., Wernersson, L.-E. & Lind, E. High-frequency gate-all-around vertical InAs nanowire MOSFETs on Si substrates. *IEEE Electron. Device Lett.* 35, 518–520 (2014).

- 39. Egard, M. et al. Vertical InAs NAnowire Wrap Gate Transistors with  $F_t$ >7 GHz and  $F_{max}$ >20 GHz. Nano Lett. **10**, 809–812 (2010).

- 40. Lesage, A. A. J. et al. Assisted extraction of the energy level spacings and lever arms in direct current bias measurements of one-dimensional quantum wires, using an image recognition routine. *J. Appl. Phys.* **117**, 015704 (2015).

- 41. Zwolak, J. P. et al. Autotuning of double-dot devices in situ with machine learning. *Phys. Rev. Appl.* **13**, 034075 (2020).

- 42. Moon, H. et al. Machine learning enables completely automatic tuning of a quantum device faster than human experts. *Nat. Commun.* **11**, 4161 (2020).

- 43. Nguyen, V. et al. Deep reinforcement learning for efficient measurement of quantum devices. *Quantum Inf.* **7**, 1–9 (2021).

- Lennon, D. T. et al. Efficiently measuring a quantum device using machine learning. Quantum Inf. 5, 1–8 (2019).

- 45. Darulová, J. et al. Autonomous tuning and charge-state detection of gate-defined guantum dots. *Phys. Rev. Appl.* **13**, 054005 (2020).

- Chatterjee, A. et al. Autonomous estimation of high-dimensional coulomb diamonds from sparse measurements. *Phys. Rev. Appl.* 18, 064040 (2022).

- Ward, D. R., Savage, D. E., Lagally, M. G., Coppersmith, S. N. & Eriksson, M. A. Integration of on-chip field-effect transistor switches with dopantless Si/SiGe quantum dots for high-throughput testing. *Appl. Phys. Lett.* **102**, 213107 (2013).

- Puddy, R. K. et al. Multiplexed charge-locking device for large arrays of quantum devices. Appl. Phys. Lett. 107, 143501 (2015).

- 49. Gül, Ö. et al. Towards high mobility InSb NAnowire Devices. *Nanotechnology* **26**, 215202 (2015).

#### **Acknowledgements**

This research was supported by research grants from Villum Fonden (Grant no.: 00013157) (T.S.J.) and the European Research Council under the European Union's Horizon 2020 research and innovation program (Grant no.: 716655 and 866158) (T.S.J.) and Microsoft Quantum. ICN2 acknowledges funding from Generalitat de Catalunya (Grant no.: 2021SGR00457) (J.A.). This study is part of the Advanced Materials program and was supported by MCIN with funding from the European Union NextGenerationEU (Grant no.: PRTR-C17.11) (J.A.) and by General-

itat de Catalunya. The authors thank the support from "ERDF A Way of Making Europe", by the "European Union". ICN2 is supported by the Severo Ochoa program from Spanish MCIN/AEI (Grant no.: CEX2021-001214-S) and is funded by the CERCA Program/Generalitat de Catalunya. Authors acknowledge the use of instrumentation as well as the technical advice provided by the National Facility ELECMI ICTS, node "Laboratorio de Microscopías Avanzadas" at the University of Zaragoza. We acknowledge support from CSIC Interdisciplinary Thematic Platform (PTI+) on Quantum Technologies (PTI-QTEP+).

#### **Author contributions**

D.O. fabricated devices, performed electrical measurements, and analyzed data. G.N. developed NW growth and grew NW samples, performed AFM, and analyzed data. D.C. performed electrical measurements and analyzed data. D.B. developed NW growth. C.P. analyzed data. S.M.S. and J.A. performed cross-section TEM, GPA, and EELS analysis. T.S.J. conceptualized the experiment and analyzed the data.

### **Competing interests**

The authors declare no competing interests.

#### **Additional information**

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41467-023-43551-1.

**Correspondence** and requests for materials should be addressed to Thomas S. Jespersen.

**Peer review information** *Nature Communications* thanks Anton Potocnik, and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

**Reprints and permissions information** is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit <a href="http://creativecommons.org/licenses/by/4.0/">http://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2023