**DTU Library**

# Capacitive Micromachined Ultrasound Transducers for Super resolution Ultrasound Real-time imaging of Erythrocytes

Pedersen, Stine Løvholt Grue

Publication date: 2023

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Pedersen, S. L. G. (2023). Capacitive Micromachined Ultrasound Transducers for Super resolution Ultrasound Real-time imaging of Erythrocytes. DTU Health Technology.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# **DTU Health Tech**Department of Health Technology

# TECHNICAL UNIVERSITY OF DENMARK

# Ph.D. Thesis

# CAPACITIVE MICROMACHINED ULTRASOUND TRANSDUCERS FOR SUPER RESOLUTION ULTRASOUND REAL-TIME IMAGING OF ERYTHROCYTES

Author: Stine Løvholt Grue Pedersen Supervisors:

Prof. Erik Vilain Thomsen

Prof. Jørgen Arendt Jensen

$31^{\rm st}$  July 2023

Kgs. Lyngby, Denmark

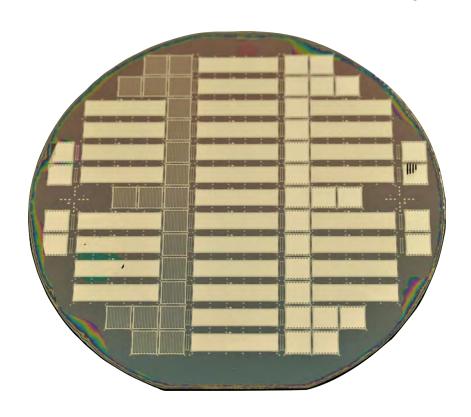

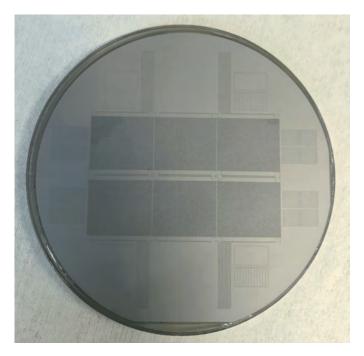

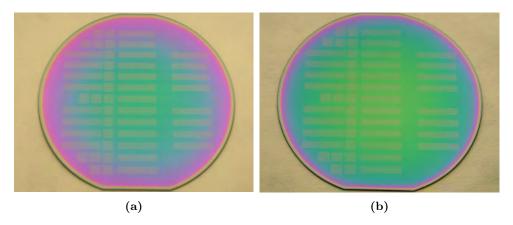

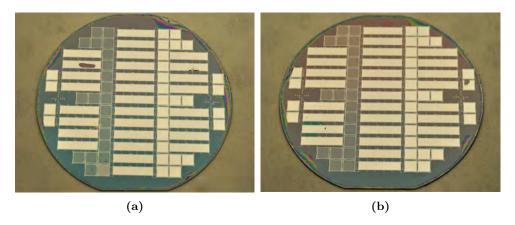

Cover image: Wafer with CMUT arrays designed and fabricated during this project for super resolution imaging.

Technical University of Denmark Department of Health Technology

Ørsteds Plads 345C 2800 Kgs. Lyngby Denmark

Web: www.healthtech.dtu.dk E-mail: healthtech-info@dtu.dk Author e-mail: stlope@dtu.dk

## Preface

This Ph.D. thesis has been submitted to The Technical University of Denmark (DTU) as a partial fulfillment of the requirements for the degree of Doctor of Philosophy. The research has been supervised by Professor Erik Vilain Thomsen and Professor Jørgen Arendt Jensen. This thesis comprises a recapitulation of the research conducted from June 2019 to July 2023 at the Institute of Health Technology at DTU.

Prior to this Ph.D. project, the MEMS group at DTU Health Technology had conducted research within the field of Capacitive Micromachined Ultrasonic Transducer (CMUT) for several years. As a result, a profound knowledge of CMUT technology was already established prior to my research.

Stine Løvholt Grue Pedersen Kgs. Lyngby, July 2023

# Summary

Medical ultrasound is a widely used imaging modality, which is considered harmless and cost-effective compared to other imaging modalities like X-rays and CT scans. The ultrasound system relies on a transducer responsible for emitting and receiving ultrasonic waves. Conventional scanner systems utilize a piezo ceramic transducer, typically composed of lead zirconate titanate (PZT) materials.

This thesis investigates an alternative transducer technology, called Capacitive Micromachined Ultrasound Transducers (CMUT), which is fabricated using conventional semiconductor methods. CMUT-based transducers offer various advantages compared to conventional PZT probes, such as temperature stability, greater design flexibility, and broader bandwidth.

The primary objective of this Ph.D. project was to design, develop, and fabricate a linear CMUT-based array for super-resolution ultrasound imaging in real-time of erythrocytes, with the ultimate goal of detecting cancer and diabetes at an earlier stage.

Additionally, the project aimed to design and develop an alternative transducer implementation method utilizing backside contacting, allowing for the integration of a CMUT-based array into a laparoscope. Related process optimization was conducted for processes essential to achieve successful backside contacting and was implemented on a 2D CMUT-based array.

A theoretical framework was provided to enhance the understanding of the CMUT behavior, including the derivation of classical expressions for essential CMUT parameters. Finite element analysis was employed to extend the classical theory to a wider range of plate geometries and clamping conditions.

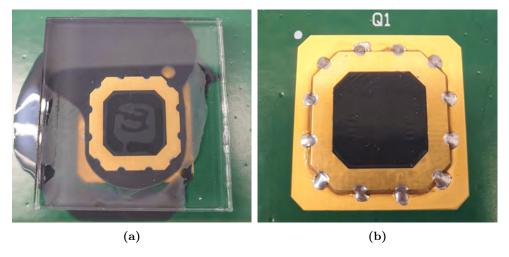

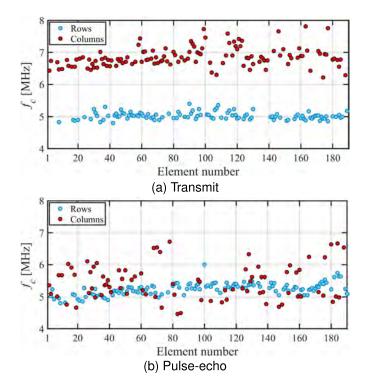

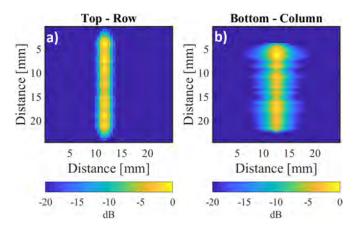

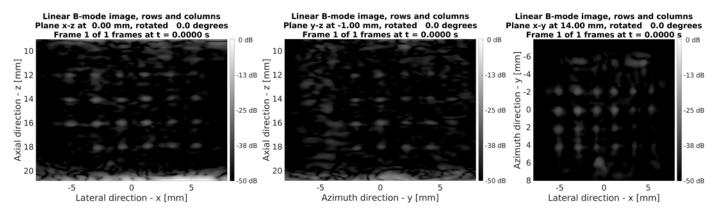

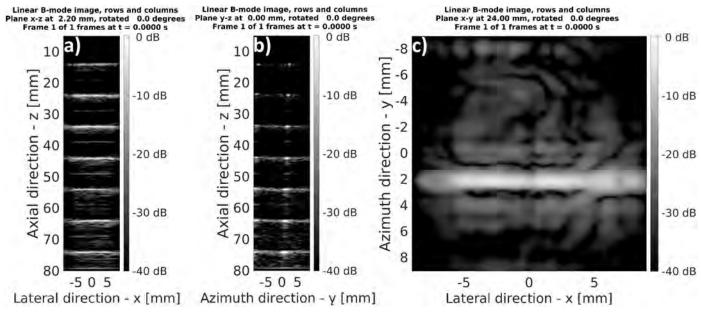

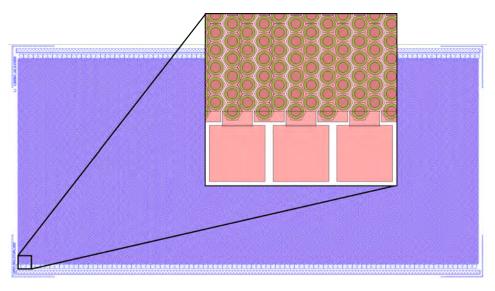

A 15 MHz transducer with an element pitch of  $\lambda/2$  was fabricated and electrically characterized using a novel wafer-level characterization method. The method employed a step-wise selection approach, exclusively focusing on the most promising arrays to save time compared to a comprehensive characterization of all arrays. Four 16-element arrays were assembled and subsequently acoustically characterized, demonstrating successful performance with bandwidths exceeding 100 % during transmission and ranging from

vi SUMMARY

$85\,\%$  to  $120\,\%$  based on pulse-echo measurements.

Medicinsk ultralyd er en udbredt billedteknik, der betragtes som harmløst og har lavere omkostninger sammenlignet med andre billedmodaliteter såsom røntgen og CT-scanning. En central del af ultralydssystemet er transduceren, som faciliterer udsendelsen og modtagelsen af ultralydsbølger. Konventionelle scanner systemer bruger en piezokeramisk transducer, som typisk er sammensat af materialer såsom blyzirkonattitanat (PZT).

Denne afhandling undersøger en alternativ transducerteknologi kaldet Kapacitive Mikromekaniske Ultralydstransducere (forkortet CMUT), der fremstilles ved hjælp af konventionelle halvledermetoder. CMUT-baserede transducere har flere fordele sammenlignet med konventionelle PZT-prober, såsom temperaturstabilitet, større designfleksibilitet og bredere båndbredde.

Det primære formål med dette Ph.D.-projekt var at designe, udvikle og fabrikere en højfrekvent lineær CMUT-baseret transducer til medicinsk billeddannelse anvendelig til superopløsning i realtid af erytrocytter (røde blodlegemer) med det ultimative formål at detektere kræft og diabetes på et tidligere stadie.

Desuden havde projektet til formål at designe og udvikle en alternativ implementeringsmetode af transduceren ved at anvende bagkontaktering, hvilket muliggøre integration af en CMUT-baseret transducer i et laparoskop. Den nødvendige procesoptimering for at opnå succesfuld bagsidekontaktering blev udført og implementeret på et 2D CMUT array.

Den første del af afhandlingen indeholder en teoretisk gennemgang af essentielle CMUT parametre baseret på klassisk plade teori. For at opnå en bedre forståelse for opførslen af tykke plader, som er påkrævet for at opnå høj frekvens, blev "finite element"-analyse implementeret til at udvide forståelsen fra den klassiske teori til et større parameterrum for pladegeometrier og grænsebetingelser.

En 15 MHz transducer med et element pitch på  $\lambda/2$  blev fabrikeret og elektrisk karakteriseret ved hjælp af en nyudviklet "wafer-lever"-karakteriseringsmetode. Metoden er baseret på en trinvis tilgang og udvægelsesmetode til udelukkende at fokusere på de mest lovende arrays for at spare tid i forhold til en omfattende karakterisering af alle arrays. Fire 16-elements ar-

viii RESUMÉ

rays blev monteret på "chip carrier boards" og efterfølgende indkasplet før de gennemgik en akustisk karakterisering, hvilket demonstrerede en ydeevne med båndbredder over  $100\,\%$  under udsendelse og varierende fra  $85\,\%$  til  $120\,\%$  baseret på puls-ekko-målinger.

## Acknowledgements

First, and foremost, I would like to dedicate a huge thanks to Professor Erik Vilain Thomsen for your exceptional guidance and moral support as my main supervisor throughout this project. I would also like to thank my co-supervisor Professor Jørgen Arendt Jensen for your guidance, dedication, and insightful feedback helping me in the right direction. Thanks for your endless optimism creating a unique and inspiring research environment. I am truly honored for you to let me take part in your cutting-edge research and try to push the limits every day.

Furthermore, I would like to thank the entire team of the MEMS group at DTU Health Technology: Rune Sixten Grass, Kitty Steenberg, Mélanie Audoin, Mathias Engholm, Andreas Havreland, Martin Lind Ommen, and Kasper Fløng Pedersen. I genuinely appreciate the remarkable professional support and collaboration we have shared. I am incredibly proud of the things we have accomplished and for the work environment, you have created. Additionally, I want to thank the students who have worked under my supervision. Your dedication and contributions have played a crucial role in the development and advancement of CMUT technology.

Last, but definitely not least, I would like to extend my deepest gratitude to my family for their support throughout this journey. A special thanks to my daughter, Nora, and you Martin for your unwavering love, support, and encouragement and for always believing in me.

# Acronyms

**AFM** Atomic Force Microscope

AOE Advanced Oxide Etch

ASE Advanced Silicon Etch

BARC Bottom Anti-Reflection Coating

**BGA** Ball-Grid Array

BHF Buffed HydroFluoric acid

**BOX** Burried OXide

$\mathbf{CCB}$  Chip Carrier Board

Cf Capacitance-frequency

${f CFU}$  Center for Fast Ultrasound Imaging

CMUT Capacitive Micromachined Ultrasonic Transducer

**CPT** Classical Plate Theory

${f CV}$  Capacitance-Voltage

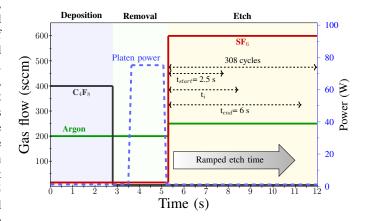

**DREM** Deposit, Remove, Etch, Multistep

$\mathbf{DTU}$  Technical University of Denmark

$\mathbf{DUT}$  Device Under Test

**EMI** Electromagnetic Interference

xii Acronyms

ERC European Research Council

FEM Finite Element Method

FSDT First order Shear Deformation Theory

$\mathbf{H}_3\mathbf{PO}_4$  Phosphoric acid

**HCP** Hexagonal Closed-Packed

**HEPA** High Efficiency Particulate Air

HF HydroFluoric acid

HNO<sub>3</sub> Nitric acid

IUS International Ultrasound Symposium

${f IV}$  current-voltage

KOH Potassium Hydroxide

LNA Low-Noise Amplifier

LOCOS LOCal Oxidation of Silicon

LPCVD Low Pressure Chemical Vapour Deposition

**MEMS** Micro Electro-Mechanical Systems

NAVMI Non-dimensionalized Added Virtual Mass Incremental

**PL** Photo Luminescence

**PSOI** Poly-Silicon-On-Insulator

PZT Lead Zirconate Titanate

**RIE** Reactive Ion Etching

**SEM** Scanning Electron Microscope

**SNR** Signal-to-Noise Ratio

SOI Silicon-On-Insulator

SURE 3-D Super resolution Ultrasound Real time imaging of Erythrocytes

**Zf** impedance-frequency

# Contents

| Preface      |        |                                  |    |  |  |  |  |

|--------------|--------|----------------------------------|----|--|--|--|--|

| Sı           | ımm    | ary                              | v  |  |  |  |  |

| $\mathbf{R}$ | Resumé |                                  |    |  |  |  |  |

| $\mathbf{A}$ | ckno   | wledgements                      | ix |  |  |  |  |

| $\mathbf{A}$ | crony  | yms                              | ix |  |  |  |  |

| 1            | Intr   | roduction                        | 1  |  |  |  |  |

|              | 1.1    | CMUT                             | 3  |  |  |  |  |

|              | 1.2    | Transducer for a Laparoscope     | 8  |  |  |  |  |

|              | 1.3    | Transducer for SURE              | 10 |  |  |  |  |

|              | 1.4    | Publications                     | 12 |  |  |  |  |

|              | 1.5    | Thesis Outline                   | 13 |  |  |  |  |

| <b>2</b>     | Tra    | nsducer Modeling                 | 15 |  |  |  |  |

|              | 2.1    | Classical Plate Theory           | 16 |  |  |  |  |

|              | 2.2    | Resonance Frequency in Immersion | 21 |  |  |  |  |

|              | 2.3    | Effective Radius Theory          | 31 |  |  |  |  |

|              | 2.4    | Shear Effects on Plates          | 35 |  |  |  |  |

|              | 2.5    | Chapter Summary                  | 42 |  |  |  |  |

| 3            | Des    | ign and Simulations              | 45 |  |  |  |  |

|              | 3.1    | Array Design                     | 46 |  |  |  |  |

|              | 3.2    | Mask Layout                      | 61 |  |  |  |  |

|              | 3.3    | Single LOCOS Cavity Design       | 65 |  |  |  |  |

|              | 3 4    | Cavity Study                     | 76 |  |  |  |  |

xiv CONTENTS

|                                                      | 3.5                          | Chapter Summary                              | . 80  |  |  |  |

|------------------------------------------------------|------------------------------|----------------------------------------------|-------|--|--|--|

| 4                                                    | Pro                          | cess Development                             | 83    |  |  |  |

|                                                      | 4.1                          | Bottom Electrode Separation                  | . 84  |  |  |  |

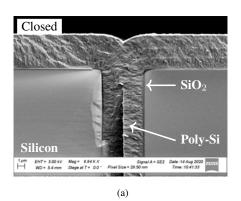

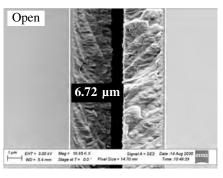

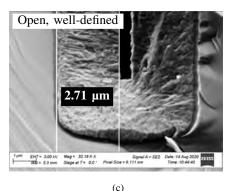

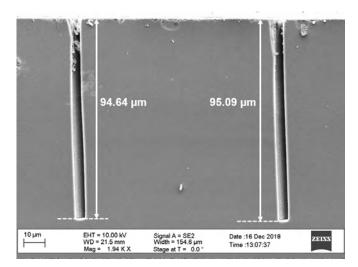

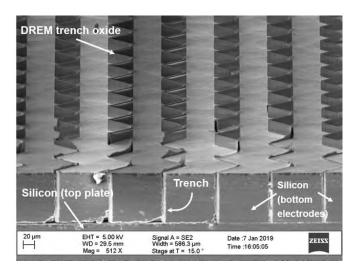

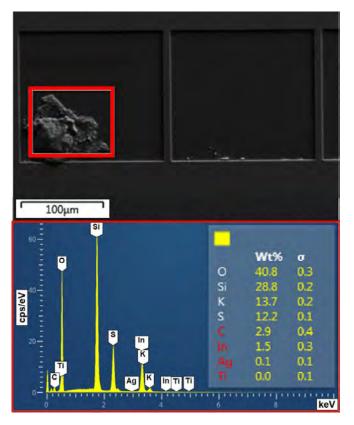

|                                                      | 4.2                          | DREM and Trench Filling                      | . 85  |  |  |  |

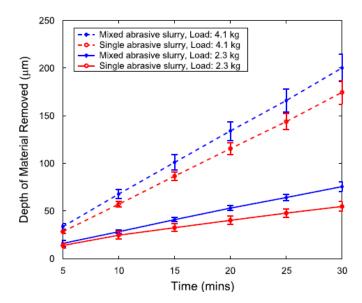

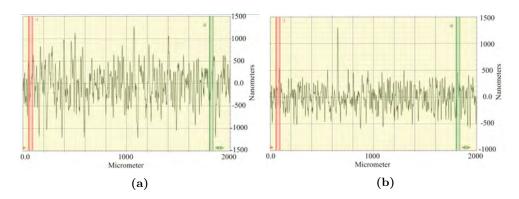

|                                                      | 4.3                          | Lapping                                      | . 90  |  |  |  |

|                                                      | 4.4                          | Chapter Summary                              | . 100 |  |  |  |

| 5                                                    | Transducer Fabrication 1     |                                              |       |  |  |  |

|                                                      | 5.1                          | Silicon Bumps                                | . 105 |  |  |  |

|                                                      | 5.2                          | Gap Definition                               |       |  |  |  |

|                                                      | 5.3                          | Fusion Bonding                               |       |  |  |  |

|                                                      | 5.4                          | Metallization and Electrode Definition       |       |  |  |  |

|                                                      | 5.5                          | Chapter Summary                              |       |  |  |  |

| 6                                                    | Characterization: Method 129 |                                              |       |  |  |  |

| Ū                                                    | 6.1                          | Measurement Setup                            |       |  |  |  |

|                                                      | 6.2                          | Visual Inspection                            |       |  |  |  |

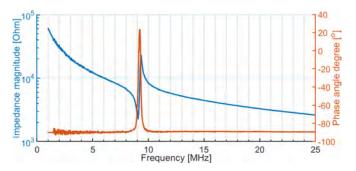

|                                                      | 6.3                          | Impedance Measurements                       |       |  |  |  |

|                                                      | 6.4                          | Voltage Measurements                         |       |  |  |  |

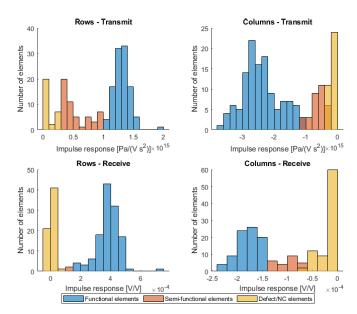

|                                                      | 6.5                          | Yield                                        |       |  |  |  |

|                                                      | 6.6                          | Pull-in and Frequency Analysis               |       |  |  |  |

|                                                      | 6.7                          | Stability Measurements                       |       |  |  |  |

|                                                      | 6.8                          | Chapter Summary                              |       |  |  |  |

| 7                                                    | Cha                          | aracterization: Results                      | 151   |  |  |  |

| •                                                    | 7.1                          | Maskless LOCOS Wafer                         |       |  |  |  |

|                                                      | $7.1 \\ 7.2$                 | Double LOCOS Wafer                           |       |  |  |  |

|                                                      | 7.3                          | Chapter Summary                              |       |  |  |  |

| 0                                                    | ۸                            |                                              | 183   |  |  |  |

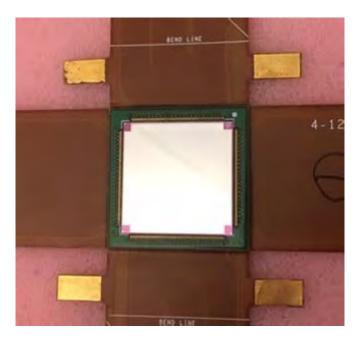

| 8                                                    | 8.1                          | embly and Acoustic Characterization Assembly |       |  |  |  |

|                                                      |                              |                                              |       |  |  |  |

|                                                      | 8.2                          | Impedance Measurements                       |       |  |  |  |

|                                                      |                              | Acoustic Characterization                    |       |  |  |  |

| 0                                                    |                              |                                              |       |  |  |  |

| 9 Conclusion and Outlook                             |                              |                                              | 201   |  |  |  |

| Bibliography                                         |                              |                                              |       |  |  |  |

| Appendices                                           |                              |                                              |       |  |  |  |

| Appendix A Paper A - Radiation Impedance Analysis    |                              |                                              |       |  |  |  |

| Appendix B. Paper B - Electrical Insulation of CMUTs |                              |                                              |       |  |  |  |

CONTENTS xv

| Append                     | $\operatorname{dix}  \operatorname{C}  \operatorname{Paper}  \operatorname{C}  \operatorname{-}  \operatorname{A}  \operatorname{Hand-Held}  190{+}190  \operatorname{Row-Column}$ |            |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| $\mathbf{C}\mathbf{M}^{T}$ | UT Probe                                                                                                                                                                           | 233        |

| Append                     | dix D OnScale Simulations                                                                                                                                                          | <b>251</b> |

| Append                     | dix E Mask Layout LapMUT                                                                                                                                                           | 253        |

| E.1                        | LapMUT-A Design                                                                                                                                                                    | 253        |

| E.2                        | LapMUT-B Design                                                                                                                                                                    | 257        |

| Append                     | dix F Athena Oxidation Models Study                                                                                                                                                | 261        |

| Append                     | dix G Oxide Thickness                                                                                                                                                              | 265        |

|                            |                                                                                                                                                                                    | 267        |

| H.1                        | Maskless LOCOS Wafer                                                                                                                                                               | 267        |

| H.2                        | Double LOCOS Wafer                                                                                                                                                                 | 271        |

| Append                     | dix I Athena Simulation Code                                                                                                                                                       | 273        |

| I.1                        | Single LOCOS Cavity Design                                                                                                                                                         | 273        |

| I.2                        | Double LOCOS Process                                                                                                                                                               | 278        |

| I.3                        | RIE Process                                                                                                                                                                        | 281        |

| I.4                        | Maskless LOCOS Process                                                                                                                                                             | 283        |

| Append                     | dix J Fabrication Processes                                                                                                                                                        | 287        |

| J.1                        | Single LOCOS Process                                                                                                                                                               | 287        |

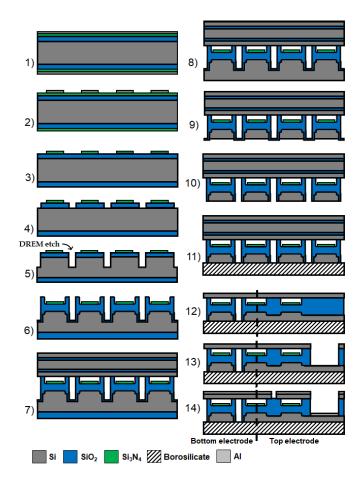

| J.2                        | Double LOCOS Process                                                                                                                                                               | 290        |

| J.3                        | RIE Process                                                                                                                                                                        | 300        |

| J.4                        | Maskless LOCOS Process                                                                                                                                                             | 307        |

xvi CONTENTS

# CHAPTER 1

# Introduction

The foundation of the field of ultrasound was established from the discovery of the piezoelectric effect first documented by Pierre and Jacques Curie in the early 1880s [1]. In 1946 the French physiotherapist André Denier first proposed the use of ultrasound to create images of the internal structures of the human body [2]. Unluckily, Denier did not manage to build a successful device, resulting in the Austrian neurologist Karl Theo Dussik, in collaboration with his brother Friedreich, to become the first to generate an ultrasonic image for medical purposes [2]. Since the 1950s, the medical ultrasound industry has emerged remarkably, and sonography is now a widely used imaging modality for visualization of soft tissues. The fundamental principle behind modern sonography is still the piezoelectric effect. Examples of one of the most well-known applications are fetus sonographs captured during pregnancy using both 2D and 3D techniques. Compared to other imaging modalities, such as X-rays and CT scans, ultrasound is considered harmless and provides real-time imaging. Furthermore, it is a portable and non-invasive imaging technology that is relatively inexpensive. These factors contribute to its widespread availability in comparison to other imaging modalities. This is further emphasized by the mission of the company Butterfly Network, Inc. (Guilford, CT, USA) whose mission is to produce a hand-held ultrasound device at a price making it achievable worldwide [3]. In 2018 the company released the first handheld, single-probe, whole-body system based on semiconductor technology, more specifically Capacitive Micromachined Ultrasonic Transducer (CMUT) technology.

However, ultrasound does have some limitations. It offers lower resolution and penetration depth compared to X-rays, CT scans, and MRIs. Despite these drawbacks, its numerous advantages have made it a valuable

imaging tool in the medical field.

Ultrasound is defined as acoustic pressure waves with a frequency exceeding 20 kHz, which is beyond the detectable limit for human audibility. Ultrasound images are created by transmitting a pressure wave into a medium. Subsequently, the wave interacts with objects within the medium, resulting in reflection and scattering. The echo signal produced by this interaction is then detected by a transducer, and signal post-processing is employed to generate the well-known grayscale ultrasound B-mode images.

Essential for the ultrasound system is therefore the transducer, which serves the dual purpose of transmitting and receiving the signal. Ultrasonic transducers are found in various shapes and frequencies, each tailored to a specific application. For instance, in cardiovascular ultrasound, the probe must be designed to fit between the ribs to visualize the movement of the heart. This is necessary due to a significant mismatch in acoustic impedance between the bone and tissue. In addition, imaging through bones is infeasible, due to a high signal attenuation, which ranges from 16 dB/MHz cm to 23 dB/MHz cm [4].

Up till this day, the majority of commercially available ultrasound transducers are based on Lead Zirconate Titanate (PZT) materials. When a potential is applied across a PZT crystal it results in material deformation, which generates and emits a sound wave. A piezoelectric crystal can consist of various chemical compositions and extensive investigation and optimization have been conducted over the years [5,6]. During this thesis, the term PZT will be used as a general reference.

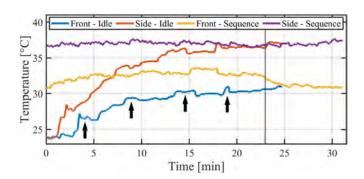

However, these PZT-based transducers have some disadvantages limiting the use for some imaging sequences. In applications involving long bursts of pulsed excitations, the primary limiting factor is the heating that occurs within the transducer itself [7]. Examples of such applications include color Doppler, therapeutics, and B-mode imaging employing coded excitation. Particularly, coded excitation is an interesting technique that can enhance image quality. This imaging technique has shown a significant improvement in penetration depth while preserving both axial resolution and contrast [8,9]. This means that one of the essential requirements for the transducer is to limit or even eliminate the self-heating problem experienced by the PZT transducer. Furthermore, the transducer should ideally have a frequency bandwidth exceeding 100 %.

In 1994, the first semiconductor-based ultrasound transducer was proposed by Khuri-Yakub as an alternative to the conventional PZT transducer. This innovative concept was presented in the conference proceeding "A surface micromachined electrostatic ultrasonic air transducer" [10]. The paper introduced a  $1.9\,\mathrm{MHz}$  air transducer with a bandwidth of  $20\,\%$ , which was four times better than the reference piezo transducer available at the same

1.1. CMUT 3

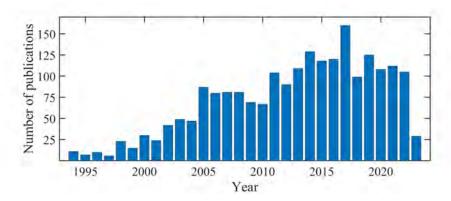

Figure 1.1: Overview of published CMUT papers since 1994. The keywords applied in the search tool Scopus were: "capacitive micromachined ultrasonic transducer\*" or "CMUT\*" or "Electrostatic ultrasonic air transducer" or "Capacitive Transducer\*" or "Surface Micromachined Transducer\*"

time. The silicon-based structure was fabricated using a sacrificial release process. An extended version of the paper was published in 1996 as a journal article by the same authors [11]. This publication described the temperature insensitivity of the CMUT in comparison with the very temperature sensitive PZT transducer. The publication became the foundation of the later CMUT research field. Since the mid/late 1990s the CMUT structure has gained widespread interest worldwide, and the number of publications has gradually increased over the years, as presented in Fig. 1.1. Development of CMUT-based arrays is the main focus of this thesis.

#### 1.1 CMUT

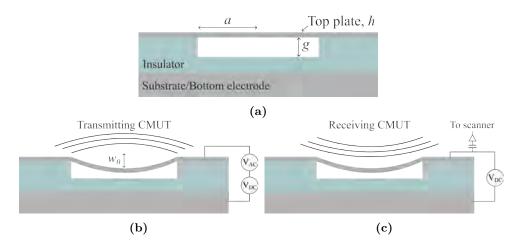

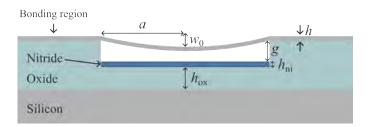

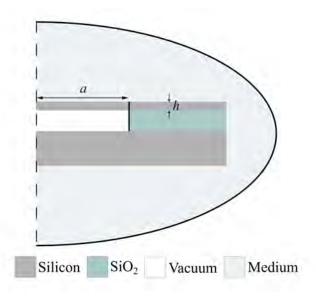

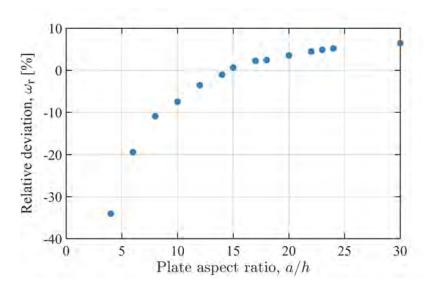

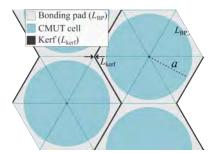

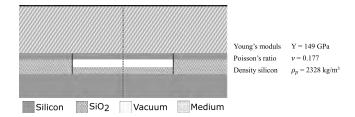

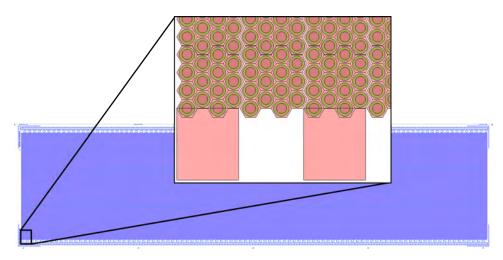

A CMUT is a miniature capacitive device that consists of a solid substrate and a flexible top plate, which are separated by an electrically insulating material and a cavity with a defined gap height g. A cross-sectional illustration of the structure is given in Fig. 1.2a. The most commonly used cell layout is either squared or circular [12]. This thesis simply addresses circular cells, with the radius defined as a. The device frequency is determined by the combination of the cell radius and the thickness of the top plate, which is denoted h.

The working principle behind the CMUT is depicted in Fig. 1.2b and 1.2c for transmit and receive, respectively. When a DC potential is applied across the structure, an electrostatic force is generated, causing the flexible top plate to deform towards the substrate. Simultaneously, a mechanical restoring force arises from the stiffness of the plate, counteracting the attraction and establishing an equilibrium state. In this stable position, the plate exhibits a specific center deflection denoted as  $w_0$ . If the applied volt-

Figure 1.2: Cross-sectional illustration of a CMUT cell. (a) Outlines the key definitions for the structure and shows the cell without applied bias. (b) Depicts the working principle behind the CMUT in transmit. Sound waves are generated by superimposing an AC potential on top of a DC potential. (c) Shows how a pressure wave causes the plate to bend in receive. The signal is transformed into an electrical signal read by the scanner. The figures are not drawn to scale.

age is further increased beyond a certain threshold, known as the pull-in or collapse voltage  $(V_{\rm pi})$ , the electrostatic force overcomes the spring force in the plate, resulting in a collapse of the top plate onto the substrate. The insulating material within the cavity is designed to prevent an electrical breakdown of the device when a potential exceeding the pull-in voltage is applied.

Following the preload of the plate, the CMUT is actuated by superimposing an AC signal on top of the DC potential. This induces oscillations of the plate, leading to emission of an acoustical pressure wave. In receive mode, the echoed signal deforms the plate. This mechanical deformation is translated into an electrical signal by measuring a change in capacitance. Through signal processing algorithms, a collection of such signals is transformed into ultrasonic images of the internal structures of the body.

CMUTs offer significant advantages over PZT transducers in terms of design and fabrication flexibility. This is primarily caused by the utilization of semiconductor technology for CMUT fabrication, which provides a larger design space with lithography as the limiting horizontal factor. In contrast, PZT transducers are often fabricated by dicing separate elements in a crystal, making the width of the saw blade a limiting factor for PZT probe fabrication. Furthermore, CMUTs offer more than 100% bandwidth due to better acoustic matching with the propagation medium. Finally, studies have demonstrated that replacing PZT with CMUTs can effectively minimize the problem of probe self-heating [13–15].

1.1. CMUT 5

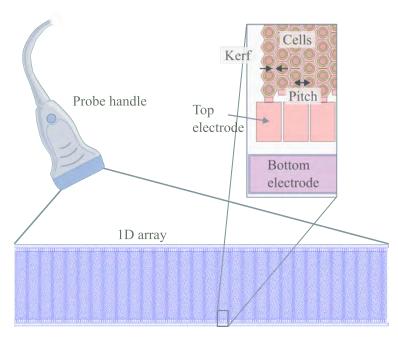

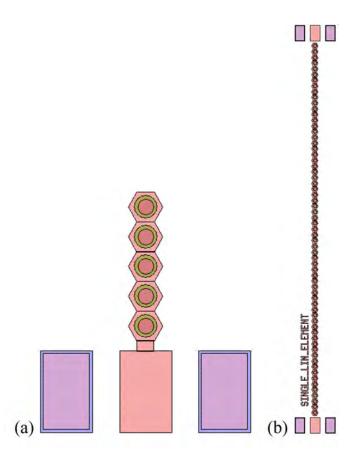

**Figure 1.3:** Overview of a CMUT-based linear 1D array defining array relevant parameters. Inspired from [16].

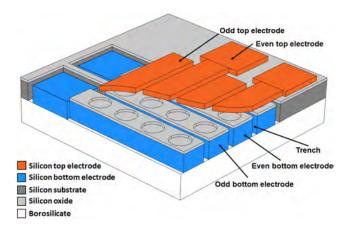

The field of ultrasound imaging provides both 2D and 3D image acquisition [17–19]. These two modalities require different probes: 1D arrays are used to acquire 2D images, while 2D arrays are utilized for 3D imaging [20,21]. Various array layouts exist within both categories. This project primarily focuses on 1D arrays, which are also referred to as linear arrays. The outline of a typical linear array, comprising 384 elements, is provided in Fig. 1.3. Each element contains multiple CMUT cells. The distance between the center of two neighboring elements is defined as the pitch, while the width between the elements is referred to as the kerf. According to the findings in [22], the element pitch is a crucial design parameter, that can reduce grating lobes remarkably, thus providing improved image quality. Many linear arrays typically contain a shared bottom electrode, while the top electrode is separated for the individual elements. The elements are then assessed through wire bonds employed for electrical integration [13, 23]. However, alternative structures with a common top electrode and separate bottom electrodes have also been studied in literature [24–27].

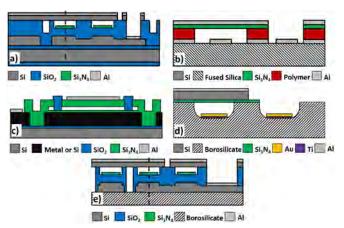

Besides the enhanced design flexibility, the utilization of semiconductor techniques facilitates various fabrication methods, each with its individual advantages. Overall two categories exist: the sacrificial release process and the wafer bonding process. The wafer bonding category can be further categorized into various bonding techniques, and an incomplete list includes

fusion bonding, anodic bonding, thermocompression bonding, and adhesive bonding [28]. During this thesis, the investigated fabrication techniques are all based on the fusion bonding technique, which is therefore the bonding technique extensively discussed in the following sections.

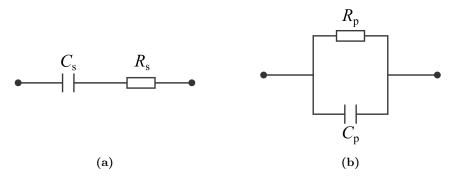

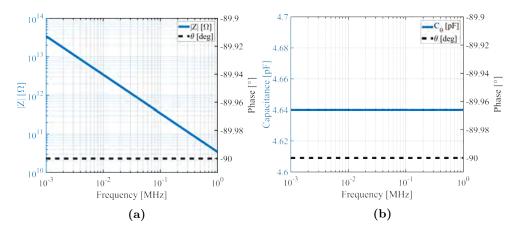

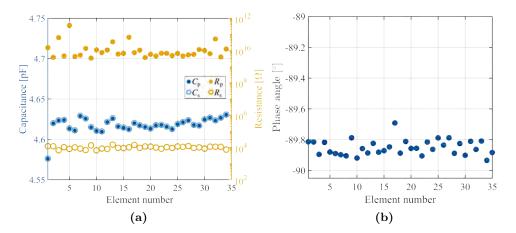

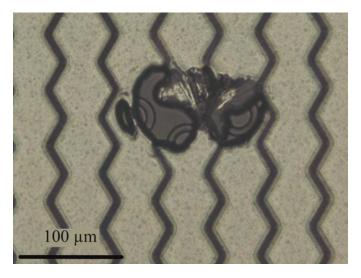

#### 1.1.1 Literature Review

The initial suggestion of a CMUT structure was fabricated using a sacrificial release process [11], which has been optimized and refined over the years [29, 30]. The sacrificial release process is based on surface micromachining techniques, where a sacrificial layer is deposited underneath the top plate material. The CMUT structure is subsequently released by wet etching the sacrificial layer through vias in the plate. The etch selectivity between the sacrificial layer and the plate material is crucial for the process. The technique is in general simple and the first proposed process only included one lithography step. Compared to the wafer bonding technique, the sacrificial release process is a high yield process [28]. However, there are certain limitations and drawbacks associated with this approach. These include stiction-related issues, which can impede the release process. Additionally, the stresses experienced by the plate material may pose challenges. Finally, the sacrificial releases process has constraints on the obtainable plate thickness as well as the cavity height [31]. This can impose limitations on the overall design and performance of the system.

In 2002 and 2003, an alternative method was proposed utilizing wafer bonding techniques [32,33]. This approach employs two wafers: one serving as the substrate where the cavities are defined, and one wafer acting as the top plate. In the early stage of CMUT fabrication using wafer bonding, the cavities were formed by etching into either the substrate or a grown insulating oxide layer. The second wafer consisted of a commercially available Silicon-On-Insulator (SOI) wafer, which was fusion bonded to the substrate wafer. General advantages of wafer bonding processes include greater design flexibility in gap height and top plate thickness. Furthermore, wafer bonding provides a high bonding strength and is highly temperature stable. It facilitates bonding various atmospheric environments, including vacuum. However, compared to the sacrificial release process, the wafer bonding technique generally has a lower yield. The most critical step in this fabrication method is the bonding step itself, which requires a high level of cleanliness, low surface roughness (less than 1.0 nm), and limited wafer bow (less than 5 μm for a 4" wafer) [34].

A reverse sacrificial release process was proposed in 2005 by [26]. This method involved depositing the top plate as the first layer and subsequently building the CMUT structure towards the bottom substrate. It resulted in a common grounded top electrode facing the patient and allowing for electrical integration from the backside, as demonstrated in [20].

1.1. CMUT 7

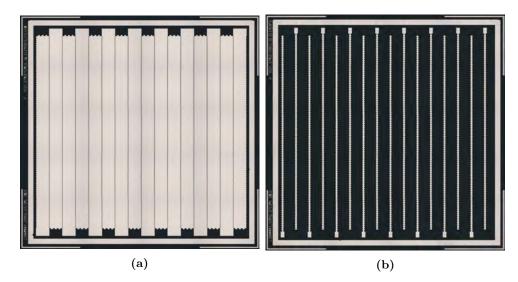

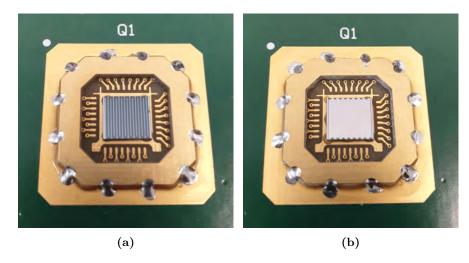

**Figure 1.4:** Four CMUT-based linear probes designed and fabricated by Ph.D. Søren E. Diedrichsen [16].

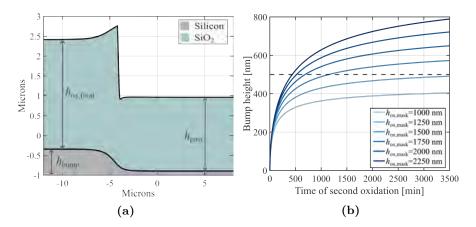

The first use of a LOCal Oxidation of Silicon (LOCOS) process combined with the fusion bonding approach for CMUT fabrication was published in 2008 [35]. This approach improved the gap height control while reducing the parasitic capacitance. In 2011 the proceeding was supplemented by a more detailed journal paper [36]. The substrate was fabricated by applying two consecutive thermal oxidation steps to form bumps in the silicon. The oxide layer was removed before a conventional LOCOS process was performed using a masking nitride layer. The LOCOS process formed the cavities and prepared the substrate for the subsequent fusion bonding process.

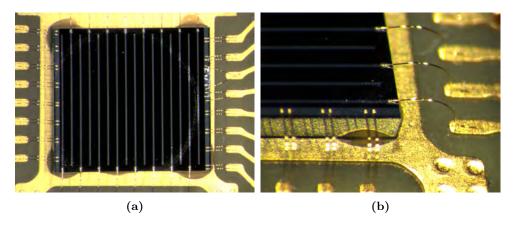

Within the research group of the author, various alternative LOCOS based designs and fabrication methods have been investigated for linear CMUTs [16]. An image of four successfully integrated probes is provided in Fig. 1.4. One of the utilized fabrication methods employed two consecutive LOCOS processes: one to form the silicon bumps and one to create the device cavities. The substrate wafer was then fusion bonded to a SOI wafer. The work resulted in full integration of four probes as part of a collaboration with BK Medical (Herley, DK).

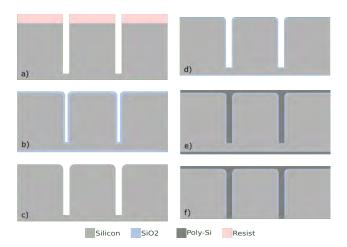

The fabrication processes applied in this thesis all rely on a combination of LOCOS and fusion bonding. Fusion bonding was chosen due to its advantages over sacrificial release and anodic bonding methods. To accommodate a requirement on high emission frequency, a thick top plate is necessary, which is challenging to achieve with sacrificial release processes [28]. Furthermore, recent findings documented problems with vertical short circuits for the anodic bonding process. These shorts are related to gold pen-

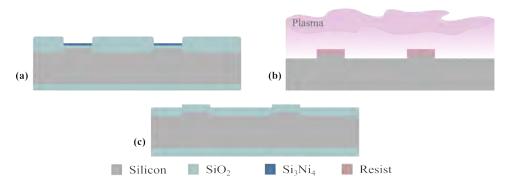

**Figure 1.5:** Illustrations of the three processing methods tested for silicon bump fabrication during this Ph.D. project. (a) Shows fabrication using a LOCOS-based process, (b) shows a dry-etching based process, and (c) depicts a method applying two consecutive thermal oxidation steps.

etrating a barrier nitride layer connected to the highly doped poly-silicon top electrode and severely decreases the yield [37]. Research conducted by Havreland et. al. [38,39] highlighted concerns about the  $\omega RC$  product, where  $\omega$  represents the angular frequency, and R and C denote the element resistance and capacitance, respectively. The study specifically investigated the impact on the pressure profile along the element for silicon-based devices. However, this does not pose a problem for linear arrays, due to their relatively small elevation height compared to 2D arrays with a high element count. Finally, fusion bonding has been extensively used and optimized within this research group over the last years [16, 39–42]. These processes have demonstrated excellent stability over time and negligible or none dielectric charging effects. This work formed the foundation for the further developments presented in this thesis.

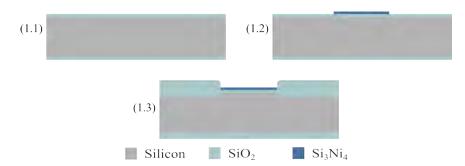

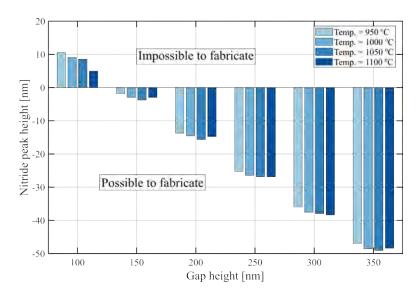

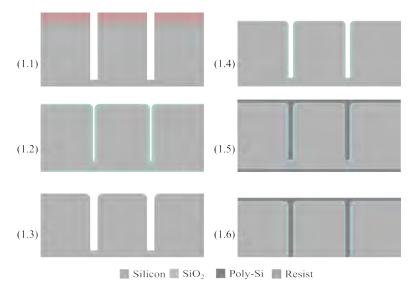

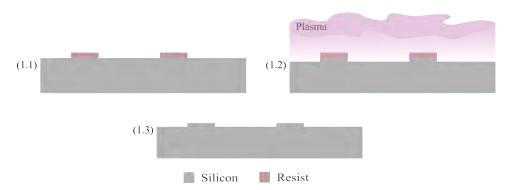

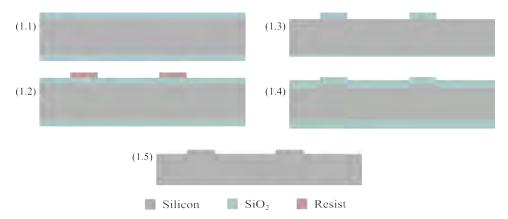

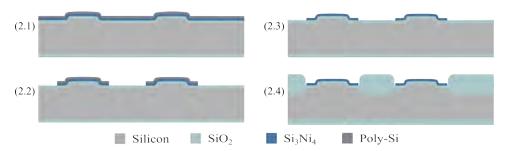

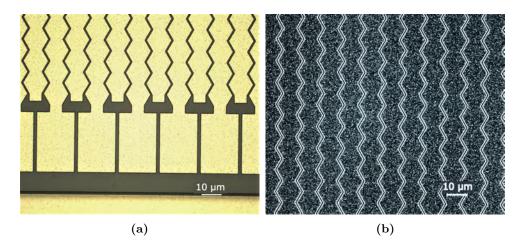

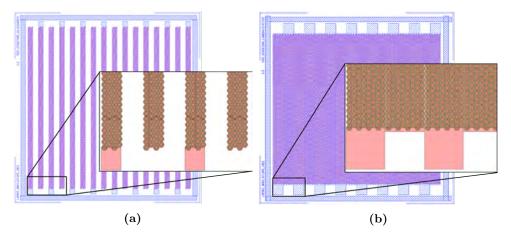

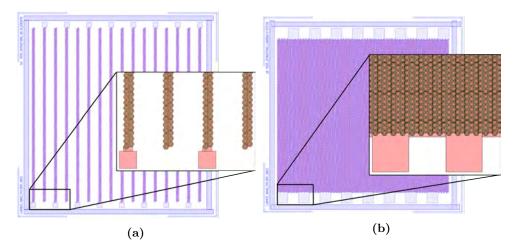

As part of the research conducted during this Ph.D. project, three methods for fabricating the silicon bumps were tested and compared for optimal performance and throughput. Illustrations of the methods are provided in Fig. 1.5. The first method is based on the LOCOS process, using a nitride masking layer shown in (a). It serves as a standard method within this research group. The second method is a time-optimized alternative that utilizes dry etching, depicted in (b). The third method follows the approach proposed by Park et al. [36] and involves two consecutive thermal oxidation processes, as shown in (c).

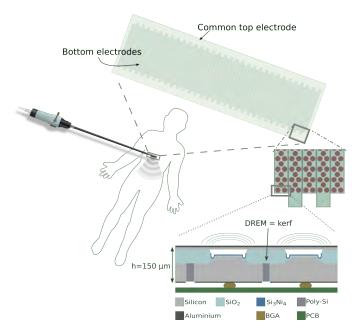

# 1.2 Transducer for a Laparoscope

Ultrasound imaging involves a fundamental trade-off between penetration depth and resolution. To obtain high-resolution images, a probe with a high frequency is necessary. However, higher frequencies lead to increased

**Figure 1.6:** Conceptual overview of a laparoscope with an integrated ultrasound transducer used for guidance during surgery in the abdomen.

attenuation, resulting in a reduction in Signal-to-Noise Ratio (SNR) and limited penetration depth. To overcome this, a smaller transducer size can be employed for in vivo imaging during surgical procedures. By reducing the transducer size, the required penetration depth is decreased, facilitating the acquisition of higher resolution images using a high-frequency transducer. An example of such an integrated transducer is found in a laparoscope, which is a minimally invasive technique [43] with a typical diameter of approximately 5 mm [44]. An illustration of the concept is provided in Fig. 1.6, where the ultrasound transducer is located at the end of the laparoscope.

This Ph.D. project was initially performed in collaboration with the company BK Medical, aiming to integrate a CMUT into a laparoscope, for high resolution visualization of the abdomen. The objective was to fabricate a small-sized transducer array that maintained a high image quality. To meet this goal, certain requirements had to be met for the array. Semiconductor-based technologies used for CMUT fabrication provide significant design flexibility, making them suitable for realization of a high-frequency laparoscopic ultrasound transducer.

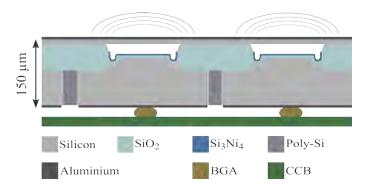

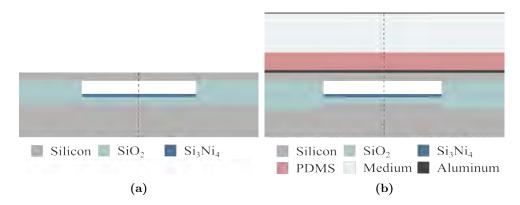

Miniaturizing the array was crucial for its implementation in the laparoscope due to space limitations. To maximize the active area of the array in the limited available space, an alternative method, compared to wire bonding approaches, was considered for electrical integration with a Chip Carrier Board (CCB). This involved using the substrate as a via architecture and contact point for Ball-Grid Array (BGA) bonding, as proposed in previous studies [45, 46]. This bonding technique mitigates parasitic contributions from wire bonds and is suitable for large-scale production. It requires separate bottom electrodes and a common top electrode connected to the ground. Furthermore, this approach moves the operational bias voltage away from the patients and eliminates the need for an external electromagnetic interference shield. In the existing literature, successful backside contacting of

**Figure 1.7:** Proposed structural cross-section of two CMUT cells integrable with a laparoscope. The bottom electrode is separated by a high aspect ratio silicon etching process. The illustration includes bonding to a CCB and is reprinted from Paper B.

CMUTs has been demonstrated using through-silicon vias filled with polysilicon or utilizing air-filled trenches as insulation [24, 25].

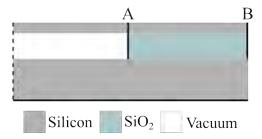

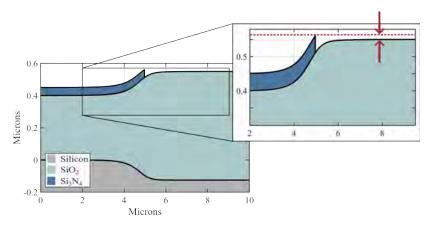

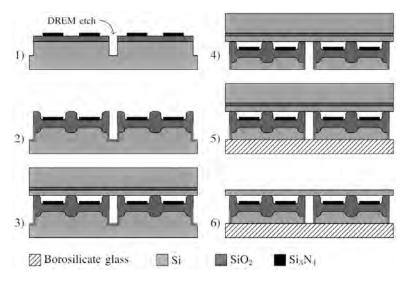

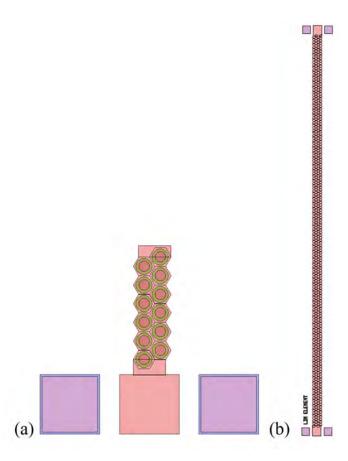

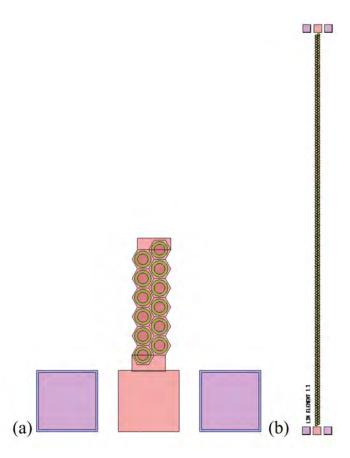

A conceptual cross-sectional overview of a CMUT structure with separate bottom electrodes is provided in Fig. 1.7. The CMUT cells are fabricated by a LOCOS process, with a bump structure in the center of the cavity. To achieve bottom electrode separation, high aspect ratio silicon trenches are created through a dry etching process described in [47]. These trenches are subsequently electrically insulated from each other using a thermal oxide and mechanically reinforced by poly-silicon plugs. After fusion bonding of the top plate to the substrate, the device can be mounted on a custom-made CCB utilizing BGA bonding methods.

Due to a discontinued collaboration with BK Medical, the scope of the Ph.D. project was changed. Therefore, the fully integrated laparoscopic design was never realized. However, significant efforts were dedicated to optimizing two crucial steps involved in the separation of the bottom electrodes. These optimizations were subsequently implemented in a 2D transducer design, resembling the one described in Paper C.

### 1.3 Transducer for SURE

This Ph.D. project has partly contributed to the "3-D Super resolution Ultrasound Real-time imaging of Erythrocytes" (SURE) project. The overall objective of the project is to develop an innovative super-resolution ultrasound-based imaging technique capable of resolving capillary flow in the human body. This method involves tracking of individual red blood cells (erythrocytes), which will be a paradigm shift in medical imaging that can innovate and enhance the diagnosis of diseases such as cancer and dia-

betes, as well as various cardiovascular conditions. Early diagnosis is crucial for optimal and effective treatment. The SURE project, funded by the European Research Council (ERC), is a collaborative synergy research initiative involving multiple stakeholders, including the MEMS Applied-Sensors group and the Center for Fast Ultrasound Imaging (CFU), both located at The Technical University of Denmark (DTU) (Kongens Lyngby, DK). Furthermore, Copenhagen University Hospital and The University of Copenhagen are also key participants in the project.

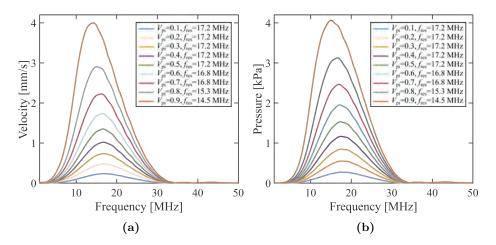

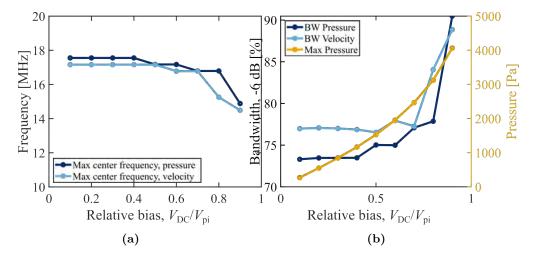

While the ultimate goal of the project is to achieve 3D ultrasound imaging, the foundation for realizing this includes the development of a well-functioning 2D super resolution imaging system. Therefore, a significant part of this thesis focuses on the design, development, and fabrication of a suitable CMUT-based linear transducer. A key parameter of the transducer is the resonance frequency,  $f_{\rm res}$ , which affects both the axial and the lateral resolution of the image. The axial resolution is defined as

$$\lambda = \frac{c_{\rm m}}{f_{\rm res}} \tag{1.1}$$

where  $c_{\rm m}$  denotes the speed of sound in the medium. For body tissue an average value of 1540 m/s is often used [4]. The lateral resolution depends on the imaging depth,  $Z_{\rm depth}$  and the aperture width, and is defined as

$$FWHM = \lambda \frac{Z_{\text{depth}}}{N \times \text{pitch}} = \lambda F_{\#}.$$

(1.2)

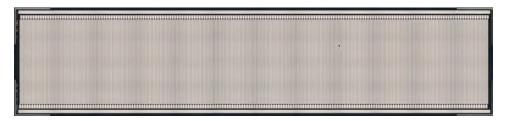

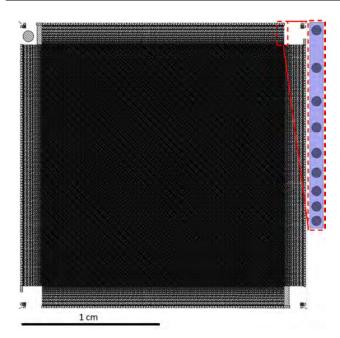

Here N is the number of elements and  $F_{\#}$  refers to the F-number, which should be as small as possible to increase the lateral resolution. Based on these relations it can be deduced that high image resolution necessitates a high resonance frequency, as well as a wide aperture, hence a large number of elements. Consequently, the objective was to fabricate a 15 MHz transducer with 384 elements.

Furthermore, the importance of the element periodicity was investigated in the study presented in [22]. The publication compared simulations and measurements for a probe with  $\lambda$ -pitch and  $\lambda/2$ -pitch. The results demonstrated that, particularly for a low number of emission lines, the  $\lambda/2$ -pitch transducer exhibited minimal, negligible grating lobes artifacts. Grating lobes can cause a degradation in the point spread function, and thereby reduce the image quality. Based on these findings, an essential requirement for the array designed for the SURE project involved having a pitch equal to  $\lambda/2$ .

#### 1.4 Publications

This thesis is partly based on the following publications in which the author has contributed as either the main author or as co-author.

Paper A (2022): S. L. Grue Pedersen, A. S. Havreland, O. Hansen and E. V. Thomsen.

"Accurate Radiation Impedance Analysis for CMUT Design," Published in *Proceedings of IEEE International Ultrasonics Symposium*, 2022, pp. 1-4.

Paper B (2020): S. L. Grue, M. Engholm and E. V. Thomsen.

"Electrical Insulation of CMUT Elements Using DREM and Lapping," Published in *Proceedings of IEEE International Ultrasonics Symposium*, 2020, pp. 1-4.

Paper C (2022): R. S. Grass, M. Engholm, A. S. Havreland, C. Beers, M. L. Ommen, S. L. G. Pedersen, L. N. Moesner, M. B. Stuart, M. T. Bhatti, B. G. Tomov, J. A. Jensen, and E. V. Thomsen.

"A Hand-Held 190+190 Row-Column Addressed CMUT Probe for Volumetric Imaging,"

Published in *IEEE Open Journal of Ultrasonics*, Ferroelectrics, and Frequency Control, 2022, vol. 2, pp. 220-236.

In addition to the above publications, the author participated physically at the 2019 IEEE International Ultrasonic Symposium (IUS). In 2020 at the online version of the conference, the author presented a poster about "Electrical Insulation of CMUT Elements Using DREM and Lapping" (Paper B), which is also presented in Chapter 4. In 2021 the author contributed with a poster presentation regarding "Analytical CMUT Modelling using Effective Radius Theory", which is further elaborated in Chapter 2. Finally, the author participated in person at the conference in 2022, presenting a poster about "Accurate Radiation Impedance Analysis for CMUT Design" (Paper A). This work is presented in Chapter 2.

#### **Articles in Preparation**

Currently, three articles are in preparation and in partly writing.

The first article is an in-depth description of the work presented at the IUS conference in 2021 about analytical modeling using effective radius theory on CMUTs. This work takes stress distributions in the top plate into account and considers the influence of the clamping conditions on the resonance frequency, the pull-in voltage, and the plate deflection. The conducted work is presented in Chapter 2, Section 2.3.

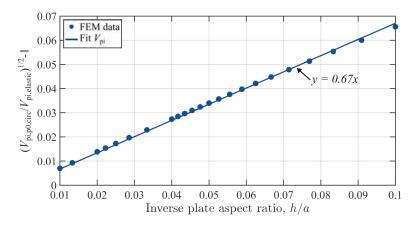

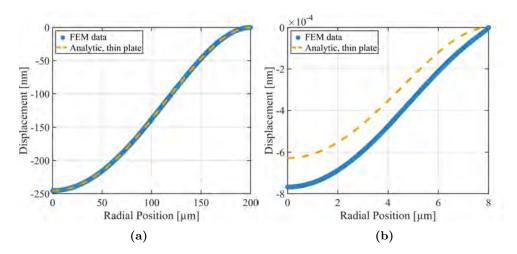

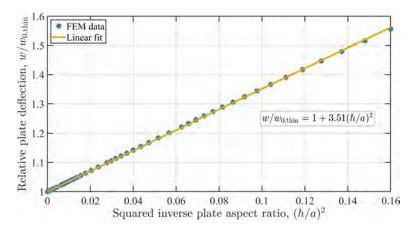

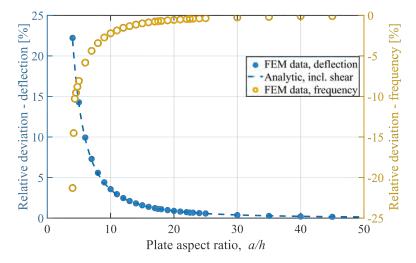

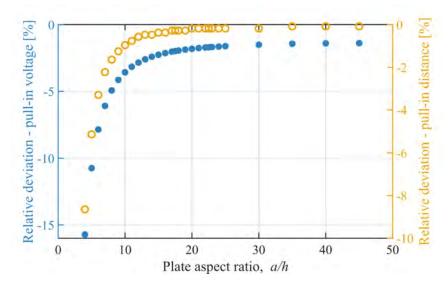

The second paper investigates the influence of shear effects on key parameters for the CMUT when decreasing the plate aspect ratio due to requirements on high frequency and small pitch arrays. The work is based on Finite Element Method (FEM) simulations of the plate deflection, resonance frequency in vacuum and immersion, as well as the pull-in voltage and distance. The simulations are evaluated against expression without shear effects and new analytical expressions encountering such effects are currently under development. The work is presented in Chapter 2, Section 2.4.

The third planned article includes integration of a 384 linear array with  $\lambda/2$ -pitch into an in-house made prototype probe described and developed by Ph.D. student Kasper F. Pedersen [48]. The paper is intended to include the entire process from design specifications, to fabrication method, electrical characterization, and probe assembly followed by acoustical characterization, all steps performed within this research group. Currently, a CCB is under development enabling integration of the array into the prototype probe. The CCB is expected to be finalized within the coming months. The work is presented from Chapter 3 to 8.

#### 1.5 Thesis Outline

The remaining of this thesis is divided into nine chapters. Chapter 2 starts by presenting the well-establish classical plate theory widely used for initial analytical array design. Thereafter, a more accurate approximation of the radiation impedance is provided and implemented in the equation of motion used to derive the resonance frequency in immersion. It is followed by a study on the bonding conditions where the stress distribution in the bonding region is included. Finally, the chapter presents a simulation based study, where shear effects in the plate are considered for CMUT key parameters.

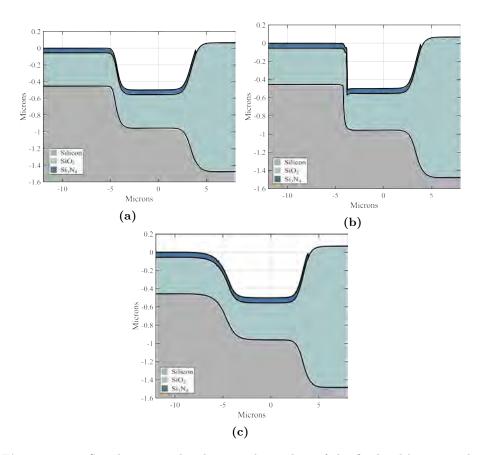

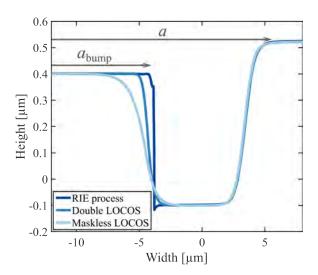

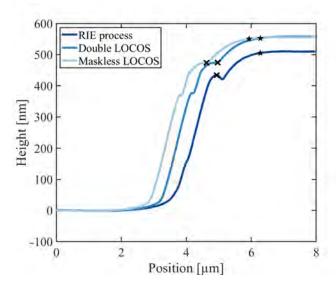

Chapter 3 introduces the design methodology used for array design. This work includes both analytical calculations as well as simulation based results. The applied mask layout is subsequently introduced, followed by a simulation based study on the parameter space for a single LOCOS process. The chapter ends with a study analyzing the outline of the cavity comparing the three different fabrication methods, employed for array fabrication.

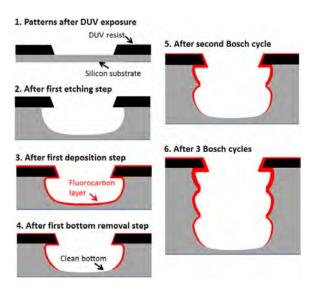

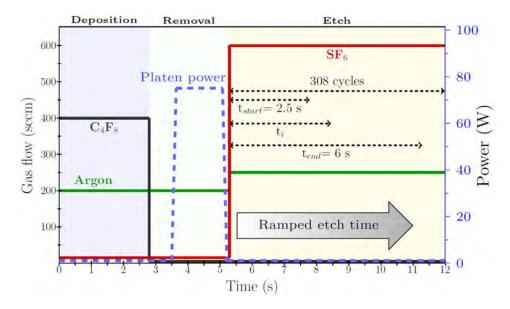

Chapter 4 presents the process development performed to allow for transducer integration from the backside. This includes the optimization of a deep silicon etching technique in combination with uniform trench filling. The second part of the chapter describes the mechanical substrate thinning technique, called lapping.

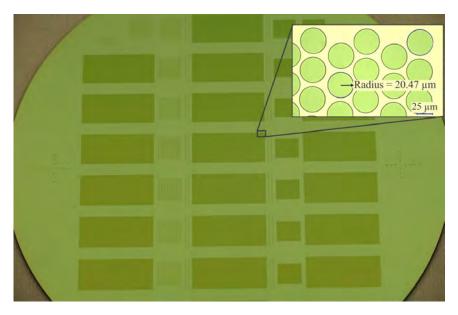

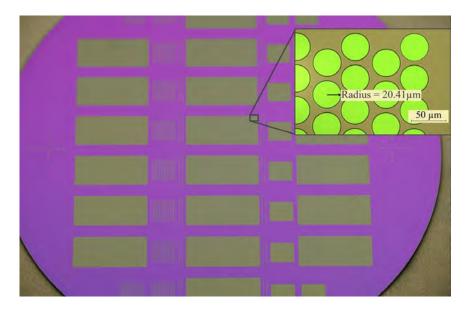

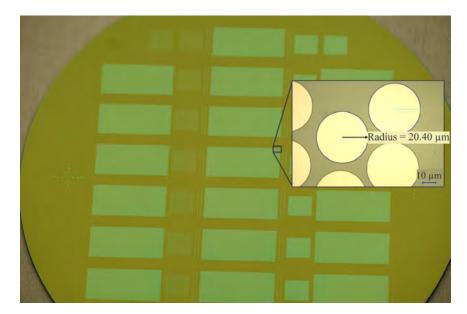

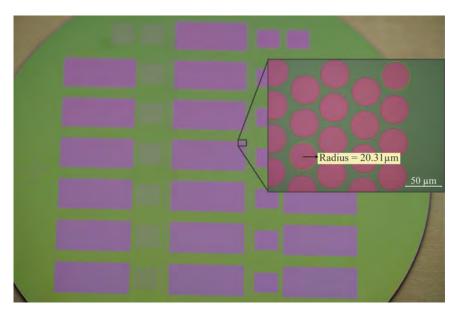

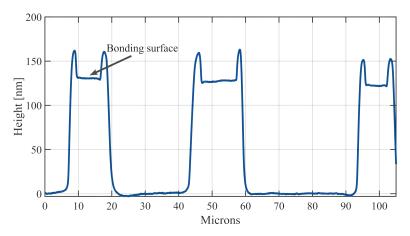

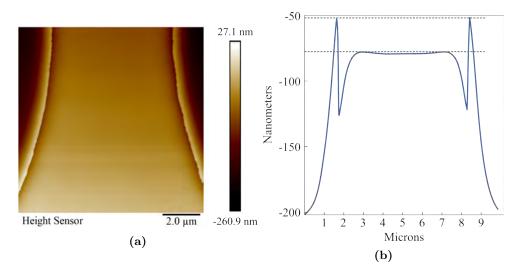

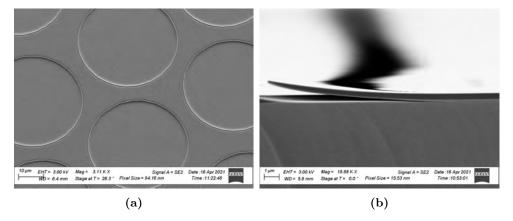

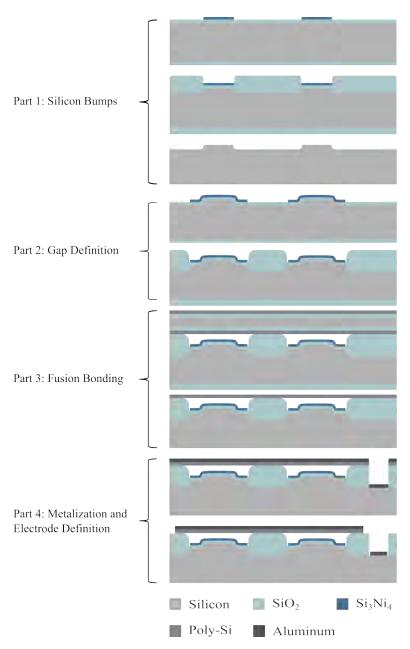

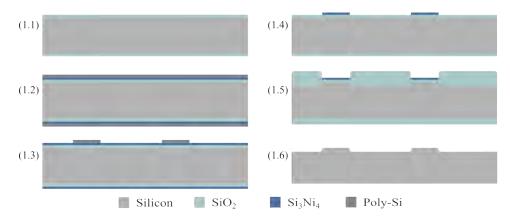

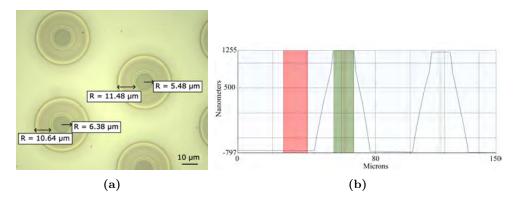

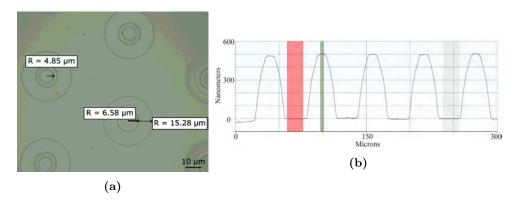

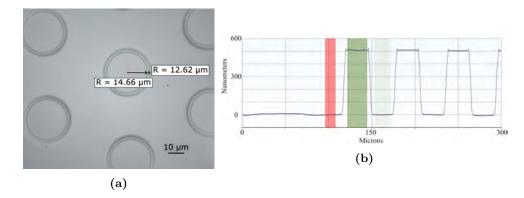

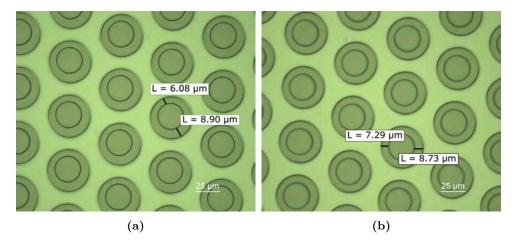

Chapter 5 is concerned with the fabrication of a linear array employing a combination of LOCOS and fusion bonding processes. Three different methods are tested for fabrication of the silicon bumps on the substrate

wafer: one based on a conventional LOCOS process, one based on a dry etching RIE process, and one based on a maskless LOCOS process. These methods are explained in detail and compared after the bump fabrication and the cavity definition.

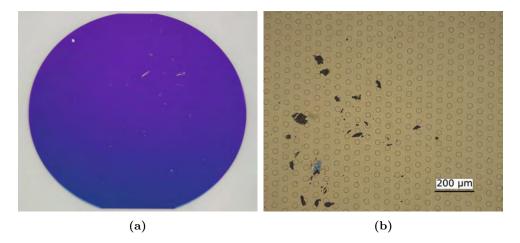

Chapter 6 introduces a novel wafer-level characterization method utilizing visual inspection followed by unbiased impedance measurements. The chapter establishes some selection criteria and highlights potential errors, associated with either measurement technicalities or fabrication errors.

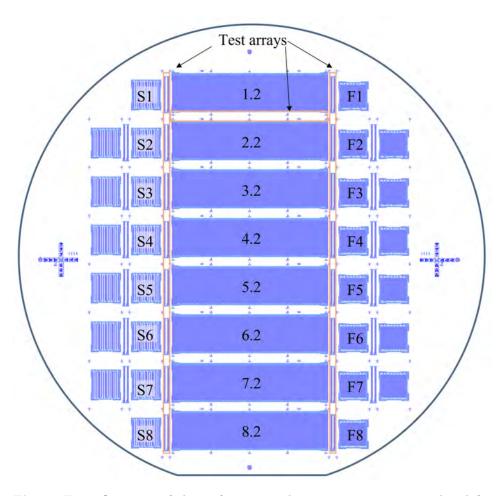

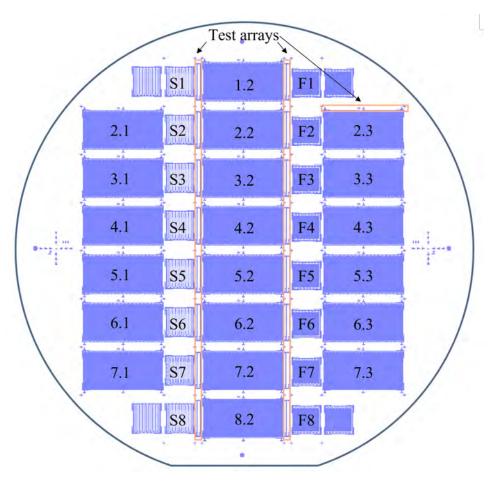

Chapter 7 presents the characterization results obtained from the wafer-level characterization method. Two wafers underwent characterization, one fabricated using two consecutive LOCOS processes and one using the mask-less LOCOS process. Based on the criteria defined in Chapter 6, few arrays underwent a full characterization before potential probe integration.

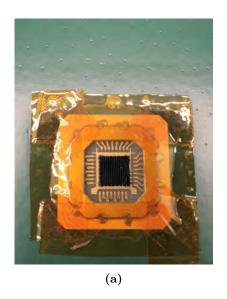

Chapter 8 describes the probe integration process, including the chip mounting, wire bonding, and casting process. The second part of the chapter describes impedance measurements performed subsequent to integration, together with the acoustical measurements performed on the assembled arrays.

Chapter 9 concludes the thesis and discusses future investigations.

# CHAPTER 2

# Transducer Modeling

The ultrasound transducer is an essential part within an ultrasound system as it is responsible for emitting and receiving the ultrasound waves, which are utilized for image formation. Therefore, understanding and accurately predicting the behavior of the CMUTs is crucial for the advancement of transducer technology. This chapter addresses the transducer modeling from a theoretical and simulation based perspective. The top plate is a central component of the CMUT structure and its geometry significantly affects several key parameters of the ultrasound transducer, including the plate deflection, the resonance frequency, and the pull-in voltage.

Often complicated FEM simulations are employed to predict the transducer behavior, which has the advantage of being reasonable precise. However, such simulations are often both time consuming and do not reveal any scaling relations. For this reason, it is desired to establish a simpler starting point for the design phase by deriving analytic expression for some of the key parameters. Furthermore, the aspect ratio of the plate, denoted a/h, influences the behavior and transducer parameters. Here a denotes the radius and h represents plate thickness, respectively. Based on the plate aspect ratio, plates can be categorized as either thin or thick plates. Since no exact definition exists, this can vary in literature. However, thin plates are often (as well as in this thesis) defined as plates with aspect ratios larger than 10, while thick plates have aspect ratios below 10.

The first section of this chapter describes some of the essential parameters for the CMUT employing classical plate theory. The second section covers analytical modeling of the resonance frequency in immersion, attempting to expand the geometric validity of the expression derived by Lamb in 1920 [49]. The derivation is accomplished through the use of a Padé expansion

**Figure 2.1:** Cross-sectional view of a simple CMUT cell. Geometric parameters are defined in the figure. Note, the illustration is not to scale.

of the radiation impedance. FEM simulations were performed to verify the analytical findings.

In the third section, the influence of the clamping conditions is investigated. This is done through FEM simulations, and the findings are subsequently incorporated into the derived classical analytical expressions.

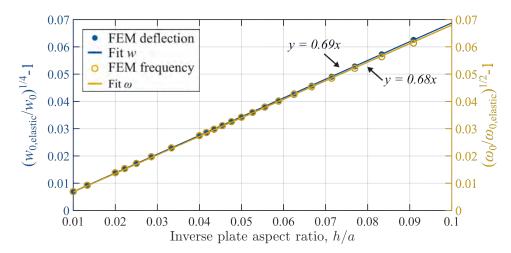

Finally, the last section studies the shear effects on both thick and thin plate geometries, analyzing the impact on transducer key parameters such as the plate deflection, pull-in voltage, capacitance, and resonance frequency in water.

# 2.1 Classical Plate Theory

Classical plate theory is applicable to plates with large aspect ratios, typically defined as a/h > 10. Thin plates have been widely investigated over time and enable many different Micro Electro-Mechanical Systems (MEMS) based devices, such as piezoresistive pressure sensors [50], and capacitive pressure sensors [51], as well as optical pressure sensors [52,53]. Since the working principle of CMUTs also relates to the top plate behavior, classical plate theory are commonly employed for initial design and analysis of CMUTs. Fig. 2.1 provides an overview of a simplified CMUT structure, including the definition of its geometric parameters.

#### 2.1.1 Plate Deflection

The plate deflection is fundamental for the behavior of the CMUT and influences both the capacitance and the pull-in voltage. The static deflection of an isotropic thin plate is found by solving the isotropic plate equation initially derived by Kirchhoff-Love [54]

$$\frac{\partial^4 w}{\partial x^4} + 2 \frac{\partial^4 w}{\partial x^2 \partial y^2} + \frac{\partial^4 w}{\partial y^4} = \frac{p}{D_i}.$$

(2.1)

Here w is the plate deflection, p is the applied pressure and  $D_i$  is the plate stiffness, which is also referred to at the isotropic flexural rigidity

$$D_{\rm i} = \frac{Y}{12(1-\nu^2)}h^3. \tag{2.2}$$

Y and  $\nu$  are material parameters known as Young's modulus and Poisson's ratio, respectively. For a thin circular plate clamped at the periphery, the static solution to Eq. (2.1) yields [55]

$$w_{\text{thin}}(r) = w_{0,\text{thin}} \left( 1 - \left( \frac{r}{a} \right)^2 \right)^2, r \le a, \tag{2.3}$$

where  $w_{0,\text{thin}}$  is the center deflection of the plate and r is the position along the radius. Applying the boundary conditions  $\partial w(0)/\partial r = 0$ ,  $\partial w(a)/\partial r = 0$ , w(a) = 0 and  $w(0) < \infty$  the center deflection of the plate results in

$$w_{0,\text{thin}} = \frac{pa^4}{64D_{i}}. (2.4)$$

#### 2.1.2 Eigenfrequency

From the field of mechanical engineering the angular resonance frequency of a plate in vacuum can be expressed in terms of the plate dimensions and material properties. The frequency is often calculated using the Raleigh-Ritz approximation method. However, the exact first resonance frequency in vacuum for a clamped circular plate with no applied potential is calculated by Bessel functions [55]. The result is

$$\omega_0 = 10.2158 \sqrt{\frac{D_{\rm i}}{a^4 h \rho_{\rm p}}},$$

(2.5)

where  $\rho_{\rm p}$  is the density of the plate.

Combining Eq. (2.5) and Eq. (2.2) the full expression becomes

$$\omega_0 = 10.2158 \sqrt{\frac{Y}{12(1-\nu^2)\rho_p}} \frac{h}{a^2},$$

(2.6)

which shows that the angular frequency in vacuum scales with  $h/a^2$  and  $\sqrt{Y/\rho_p}$ . For silicon the mean value of  $\nu$  is 0.177, which results in  $(1-\nu^2) = 0.97$ , illustrating that the influence of Poisson's ratio is very small.

#### 2.1.3 Electrostatic Analysis

Two other important parameters for the CMUT performance are the capacitance and the pull-in voltage. Both depending on the deflection profile of the plate.

#### Capacitance

First, the capacitance is derived, which is a measure of stored electrical charge, Q, relative to the applied voltage, V. The unit for the capacitance is Farad. The capacitor consists of two conducting plates and, in this case, two intermediate insulating layers, one of oxide and one of nitride (see Fig. 2.1).

The simplest model to describe this system is the parallel plate capacitor model, which has a capacitance of

$$C = \frac{\epsilon_0 \epsilon_r A}{g_{\text{eff}}}. (2.7)$$

$\epsilon_0$  and  $\epsilon_r$  are the vacuum permittivity and relative permittivity of the insulating material, respectively. A is the area of the plate and  $g_{\text{eff}}$  is the effective gap between the electrodes. The effective gap can be expressed as a sum over the stack of materials in the active region of the cell

$$g_{\text{eff}} = g + \sum_{n=1}^{N} \frac{h_n}{\epsilon_{\text{r},n}},\tag{2.8}$$

where g is the vacuum gap and N is the total number of insulting layers.  $h_n$  and  $\epsilon_{r,n}$  denote the thickness and the relative permittivity of the nth dielectric layer, respectively. For the material stack present in Fig. 2.1 the effective gap becomes

$$g_{\text{eff}} = g + \frac{h_{\text{ox}}}{\epsilon_{\text{ox}}} + \frac{h_{\text{ni}}}{\epsilon_{\text{ni}}}.$$

(2.9)

As a result, the total capacitance for zero deflection can be written as

$$C_0 = \left(\frac{1}{C_{\text{vac}}} + \frac{1}{C_{\text{ox}}} + \frac{1}{C_{\text{ni}}}\right)^{-1} = \frac{\epsilon_0 A}{g_{\text{eff}}}.$$

(2.10)

If the plate deflection is taken into account the general expression for the capacitance becomes [56]

$$C = \frac{1}{g_{\text{eff}}} \int \int \frac{\epsilon_0}{1 - \eta f(x, y)} dx dy.$$

(2.11)

Here  $\eta = w_0/g_{\text{eff}}$  is the normalized center deflection and f(x, y) is a function describing the shape of the plate deflection. For a parallel capacitor f(x, y) = 1, while for a clamped circular plate the function is given by Eq. (2.3). The capacitance of the parallel plate capacitor then yields

$$C_{\text{parallel}} = C_0 \frac{1}{1 - \eta},\tag{2.12}$$

while for the circular plate the capacitance is calculated in [57] to be

$$C_{\text{circular}} = C_0 \sqrt{\frac{1}{\eta}} \operatorname{arctanh} \sqrt{\eta}.$$

(2.13)

By utilizing the derived capacitance, it is possible to determine the pull-in voltage and distance through energy considerations.

#### Pull-in Voltage and Distance

To derive the pull-in voltage and distance for the CMUT, the stored energy in transducer is considered. The following derivation will be based on lumped parameters.

Initially, the total energy is defined for the three domains of interest: the mechanical, the electrical and the acoustical domain. The system is assumed to be loss-less, and the energy is composed of four terms [56]. The total stored energy for the mechanical domain is defined as

$$U_{\rm t.m} = U_{\rm s} + U_{\rm kin} - U_{\rm e} - U_{\rm p},$$

(2.14)

where  $U_{\rm s}$  represents the stored potential energy,  $U_{\rm kin}$  is the kinetic energy,  $U_{\rm e}$  denotes the electrical energy stored in the capacitor and  $U_{\rm p}$  represents the work done on the system by the external pressure. Inserting the lumped parameters  $K_0$  and  $m_0$ , denoting the spring constant and the geometrical mass, respectively, leads to a total stored mechanical energy of

$$U_{t,m} = \frac{1}{2}K_0w_0^2 + \frac{1}{2}m_0\left(\frac{\partial w_0}{\partial t}\right)^2 - \frac{1}{2}V^2C(w_0) - pw_0A.$$

(2.15)

V defines the voltage applied to the system. To determine the stored energy in both the electrical and acoustical domains, it is necessary to adjust the signs to accommodate the altered definition of the work and internal energy [56]. The total stored energies yields

$$U_{\rm t,e} = -\frac{1}{2}K_0w_0^2 - \frac{1}{2}m_0\left(\frac{\partial w_0}{\partial t}\right)^2 + \frac{1}{2}V^2C(w_0) - pw_0A,\tag{2.16}$$

$$U_{t,a} = -\frac{1}{2}K_0w_0^2 - \frac{1}{2}m_0\left(\frac{\partial w_0}{\partial t}\right)^2 - \frac{1}{2}V^2C(w_0) + pw_0A.$$

(2.17)

Differentiating Eq. (2.15), Eq. (2.16) and Eq. (2.17) with respect to equivalent variable, the governing equations can be derived for the three domain. The equivalent variable for the mechanical domain is the plate deflection,  $w_0$  resulting in a force F. For the electrical domain the equivalent variable is the voltage V resulting in an expression for the system charge Q, and finally, for the acoustical domain the equivalent variable is the pressure p, resulting in the volume displacement W. The three derived equations are

$$F = \frac{\partial U_{t,m}}{\partial w_0} = K_0 w_0 + m_0 \frac{\partial^2 w_0}{\partial t^2} - \frac{1}{2} V^2 \frac{\partial C(w_0)}{\partial w_0} - pA, \tag{2.18}$$

$$Q = \frac{\partial U_{t,e}}{\partial V} = VC(w_0), \qquad (2.19)$$

$$W = \frac{\partial U_{t,a}}{\partial p} = w_0 A. \tag{2.20}$$

In combination these three equations provides a nonlinear description of the behavior of the transducer, which will be used in the following to derive the pull-in voltage and the pull-in distance [56]. Notice, that the partial derivative of the capacitance with respect to  $w_0$  will be denoted  $C'(w_0)$ .

Based on the energy considerations above, the stable position of the capacitor plate can be found, hence the pull-in voltage and distance is derived. The stable position occurs when the spring force of the plate is balanced by the electrostatic force and the pressure applied to the plate. Considering the mechanical force acting on the CMUT the static case becomes

$$F_{\rm s} = K_0 w_0 - \frac{1}{2} V^2 C'(w_0) - pA. \tag{2.21}$$

The stable position is found for a given potential when the total force is zero by solving

$$K_0 w_0 = \frac{1}{2} V^2 C'(w_0) + pA. \tag{2.22}$$

By differentiating the total force with respect to the center deflection,  $w_0$ , the effective spring constant is found to be

$$K_{\text{eff}} = \frac{\partial F_{\text{s}}}{\partial w_0} = K_0 - \frac{1}{2} V^2 C''(w_0).$$

(2.23)

This expression shows the "spring softening" effect of the plate, namely the reduction in the spring constant caused by an applied voltage, which is subtracted from the isolated spring constant of the plate,  $K_0$ .

The pull-in voltage defines the point where the effective spring constant is zero, hence

$$V_{\rm pi} = \sqrt{\frac{2K_0}{C''(w_0)}}. (2.24)$$

Combining Eq. (2.22) and Eq. (2.24), the center deflection when applying the pull-in voltage, known as the pull-in distance, can be calculated by solving

$$K_0 w_{0,\text{pi}} = K_0 \frac{C'(w_{0,\text{pi}})}{C''(w_{0,\text{pi}})} + pA.$$

(2.25)

For the circular plate with no applied pressure the relative pull-in distance becomes  $\eta_{\rm pi,p0,circ}=0.463$ , hence the pull-in potential at this distance is found by combining the value  $\eta_{\rm pi,p0,circ}$  and Eq. (2.22) leading to

$$V_{\text{pi,p0,circ}} = \sqrt{\frac{89.4459D_{i}g_{\text{eff}}^{2}}{a^{2}C_{0}}},$$

(2.26)

which is equivalent to

$$V_{\rm pi,p0,circ} = \sqrt{89.4459 \frac{Y g_{\rm eff}^3}{12\pi (1 - \nu^2)\epsilon_0}} \frac{h^{3/2}}{a^2}.$$

(2.27)

It the observed that the pull-in voltage depends on the plate geometry and scales with  $h^{3/2}/a^2$ .

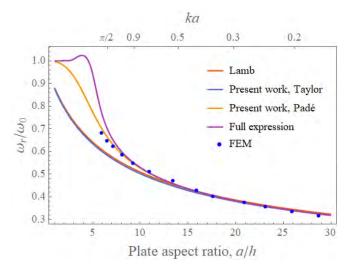

# 2.2 Resonance Frequency in Immersion

Since the application of the CMUTs developed during this Ph.D. project are intended for providing ultrasound imaging of the body's internal structures, the resonance frequency of the transducer in immersion is of great interest. However, the expression derived by Lamb [49] has limited validity for the plate aspect ratios required for high-resolution imaging demands.

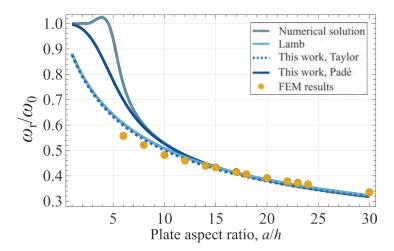

Therefore, the objective of this section is to provide a more accurate analytic expression for the resonance frequency in immersion, covering small plate aspect ratios relevant for medical CMUTs employed for high-resolution imaging. Based on the equation of motion a novel expression for the resonance frequency in immersion is derived. The interaction between the plate and the surrounding medium is modeled using the radiation impedance. Due to the complexity of the complete radiation impedance expression, the resonance frequency can only be solved numerically. To overcome this challenge the radiation impedance is approximated using a Taylor expansion to validate the derivation method against Lamb's expression. Additionally, a Padé approximation is employed to extend the model towards small aspect ratios.

The study presented in this section is based on the research presented at the International Ultrasound Symposium (IUS) 2022 conference, which was subsequently published in a conference proceeding appended in Paper A. This section is extended new FEM data.

The resonance frequency for a single CMUT cell in vacuum without applied potential can simplest be described as a harmonic oscillator by

$$\omega_0 = \sqrt{\frac{K_0}{m_0}}. (2.28)$$

From experiments it is know that the resonance frequency of a device decreases when submerged in water compared to the vacuum frequency. In relation to Eq. (2.28) this decrease can be though of as an added mass from the surrounding medium, which will move together with the vibrating plate. The sum of the geometric mass and the extra mass added by the medium is defined as the effective mass  $m_{\rm eff} = m_0 + \Delta m$ .

The resonance frequency in water can then be written as

$$\omega_{\rm r} = \sqrt{\frac{K_0}{m_0 + \Delta m}}. (2.29)$$

Combining Eq. (2.28) and Eq. (2.29) provides the ratio between the resonance frequency in immersion and in vacuum, which results in

$$\frac{\omega_{\rm r}}{\omega_0} = \frac{\sqrt{\frac{K_0}{m_0 + \Delta m}}}{\sqrt{\frac{K_0}{m_0}}} = \sqrt{\frac{m_0 + \Delta m}{m_0}} = \frac{1}{\sqrt{1 + \frac{\Delta m}{m_0}}}.$$

(2.30)

The geometric mass of the plate is defined as  $m_0 = \pi a^2 h \rho_p$ . The added mass from the medium is simplest though of as a column of water on top of the plate having the same radius as the plate and is thus written as

$$\Delta m = \pi a^2 h_{\rm w} \rho_{\rm m},\tag{2.31}$$

where  $\rho_{\rm m}$  is the density of the medium and  $h_{\rm w}$  is the unknown height on the water column. Combining this with Eq. (2.30) leads to

$$\frac{\omega_{\rm r}}{\omega_0} = \frac{1}{\sqrt{1 + \frac{\pi a^2 h_{\rm w} \rho_{\rm m}}{\pi a^2 h \rho_{\rm p}}}} = \frac{1}{\sqrt{1 + \frac{h_{\rm w}}{h} \frac{\rho_{\rm m}}{\rho_{\rm p}}}}.$$

(2.32)

A heuristic way to define  $h_{\rm w}$  is implemented as  $h_{\rm w}=\Gamma a$ , where  $\Gamma$  is a proportionality factor. The argument is that the added mass differs between different plate geometries, thus depends on one of the geometric parameters. However, the molecules of the medium is not expected to experience the thickness of the plate, but rather to be influenced by the radius of the plate. The ratio between the frequency in immersion and vacuum can then be written as

$$\frac{\omega_{\rm r}}{\omega_0} = \frac{1}{\sqrt{1 + \Gamma \frac{a}{h} \frac{\rho_{\rm m}}{\rho_{\rm p}}}}.$$

(2.33)

This expression takes on the same form as derived by Lamb for the center frequency of a clamped circular thin plate in immersion [49]. Lamb's expression is established as

$$\frac{\omega_{\rm r}}{\omega_0} = \frac{1}{\sqrt{1 + \Gamma_{\rm Lamb} \frac{a}{h} \frac{\rho_{\rm m}}{\rho_{\rm p}}}},\tag{2.34}$$

where  $\Gamma_{\text{Lamb}}$  is known as the Non-dimensionalized Added Virtual Mass Incremental (NAVMI) factor [58]. The NAVMI factor is a dimensionless constant, which depends on the boundary conditions of the plate. For a clamped circular plate Lamb states a NAVMI value of  $\Gamma_{\text{Lamb}} = 0.6689$ . However, the

|             | Lamb   | Powell | Kwak           |

|-------------|--------|--------|----------------|

| NAVMI value | 0.6689 | 0.546  | 0.4667/0.65381 |

| Reference   | [49]   | [59]   | [58]/[60]      |

**Table 2.1:** Various NAVMI factors found in the literature.

resonance frequency of a circular plate has been investigated by several researchers and even though the final expression has the same form, the value of the NAVMI factor varies dependent on the scientist. A few examples are provided with references in Table 2.1.

The model by Lamb assumes that the diameter of the plate is much smaller than the wavelength in the medium, corresponding to  $ka \ll 2\pi$ , with k being the wavenumber and a the radius of the plate. The expression in Eq. (2.34) is implicitly valid for  $ka \leq 0.5$  since the expression is based on some simplification, that will be apparent later in this section. In literature the ka values for CMUTs ranges from 0.3 to 0.6 [16,33] and with recent interest of  $\lambda/2$ -pitch designed CMUTs [22], the ka product increases up to 1.35 [61]. This reveals the demand for a more accurate analytical solution valid for larger ka, hence for smaller aspect ratios.

### 2.2.1 The Harmonic Oscillator Model

To derive an expression for the resonance frequency in immersion valid for devices with large ka, the clamped circular plate is mapped onto a concentrated element harmonic oscillator, which has the equation of motion

$$F_{\text{ext}} = m_0 \frac{d^2 x}{dt^2} + K_0 x + F_{\text{w}}.$$

(2.35)

$F_{\rm ext}$  is the total external force on the plate, x the deflection and  $d^2x/dt^2$  the acceleration.  $K_0$  is given by Eq. (2.28) and  $F_{\rm w}$  is the force from the fluid acting on the CMUT. This force can most simple be described in the frequency domain by introducing the radiation impedance, Z. The force can be expressed as  $\hat{F}_{\rm w} = Z\hat{v}_{\rm a}$ , where  $\hat{v}_{\rm a}$  is the plate velocity. Combining this with Eq. (2.35), the equation of motion becomes

$$\hat{F}_{\text{ext}} = -m_0 \omega^2 \hat{x}_{\text{m}} + K_0 \hat{x}_{\text{m}} + iZ \omega \hat{x}_{\text{a}}.$$

(2.36)

$\hat{F}_{\rm ext}$  and  $\hat{x}$  refers to the force and position in the frequency domain, respectively, which are both complex numbers. The subscripts, m and a, refer to the mechanical and acoustical domain, respectively. In order to couple between the two domains a scaling factor  $\Lambda = \hat{x}_{\rm a}/\hat{x}_{\rm m}$  is required. This is introduced through a lumped model. Rewriting the equation of motion in

Eq. (2.36) leads to an equation of motion in the mechanical domain, which yields

$$\hat{F}_{\text{ext}} = -m_0 \omega^2 \hat{x}_{\text{m}} + K_0 \hat{x}_{\text{m}} + iZ\omega \Lambda \hat{x}_{\text{m}}. \tag{2.37}$$

From this expression the resonance frequency in immersion can be calculated, since resonance occurs when the real part of Eq. (2.37) equals zero, hence

$$0 = m_0(\omega_0^2 - \omega_r^2) - \Im(Z)\Lambda\omega_r. \tag{2.38}$$

This equation reveals the need to determine the radiation impedance of the clamped circular plate, which will be further described in the following subsection.

In order to couple between the mechanical and the acoustical domain a lumped model is now introduced. Recall, the static deflection curve for a circular clamped plate is defined by Eq. (2.3).

Considering the mechanical domain, the kinetic energy for a harmonic vibrating top plate is found by integration. The dynamic velocity at distance r is defined as

$$\hat{v}(r,t) = i\omega w(r)e^{i\omega t}. (2.39)$$

The peak kinetic energy is

$$U_{\rm kin} = \int_0^a \frac{1}{2} \omega^2 w^2(r) \rho_{\rm p} h \, 2\pi r dr = \frac{1}{2} m_0 \left( \frac{\omega w_0}{\sqrt{5}} \right)^2. \tag{2.40}$$

The lumped velocity amplitude can subsequently be identified as  $v_{\rm m} = \omega w_0/\sqrt{5}$ , which corresponds to a lumped position amplitude of  $x_{\rm m} = w_0/\sqrt{5}$ . At the same lumped position the elastic potential peak energy can be identified as

$$U_{\rm ela} = \frac{1}{2}K_0x_{\rm m}^2 = \frac{1}{2}m_0\omega_0^2x_{\rm m}^2$$

(2.41)

such that  $K_0 = m_0 \omega_0^2$  by definition.

When submerged in a medium the CMUT radiates sound and the radiation impedance is defined as a complex number Z = R + iX, where the real part describes the radiated power, while the imaginary part describes the "back action" on the transducer. The radiation impedance is calculated based on the volume velocity, V, of the radiating CMUT plate. The volume velocity is given by

$$V = \int_0^a \omega w(r) \, 2\pi r dr = \pi a^2 \omega \, \frac{w_0}{3}. \tag{2.42}$$

The harmonic position relevant in the acoustical domain is therefore defined as  $\hat{x}_a = (w_0/3)e^{i\omega t}$ .

In summary, the lumped position amplitudes are  $x_{\rm m}=w_0/\sqrt{5}$  and  $x_{\rm a}=w_0/3$  for the mechanical and acoustical domains, respectively. The scaling

factor linking the mechanical and acoustical domain becomes

$$\Lambda = \frac{x_{\rm a}}{x_{\rm m}} = \frac{\sqrt{5}}{3} = 0.745,\tag{2.43}$$

which can be used for both the position and the velocity based on the harmonic assumption. Using this scaling parameter, the resonance frequency can be calculated from Eq. (2.38), when the radiation impedance is known.

## 2.2.2 Radiation Impedance

As previously stated, the radiation impedance is a complex number that characterizes both the radiated power and the "back action" on the transducer. For a clamped circular plate the radiation impedance is derived in [62] and expressed in terms of a hypergeometric function,  ${}_2F_3$ , the expression is

$$Z_{\text{plate}} = \left(\frac{1}{(ka)^5} \left(12(-3+2(ka)^2)J_1(2ka) + ka(36+(ka)^4 - 84J_2(2ka))\right) + i\frac{512ka}{175\pi} {}_2F_3\left(2,\frac{5}{2};\frac{3}{2},\frac{7}{2},\frac{9}{2};-(ka)^2\right)\right)\rho_{\text{m}}c_{\text{m}}\pi a^2,$$

(2.44)

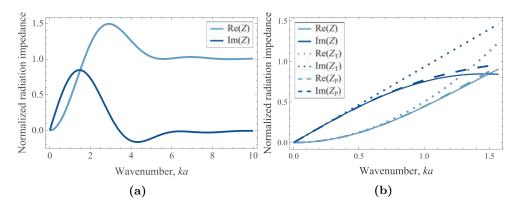

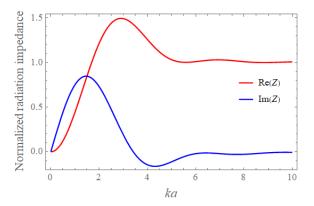

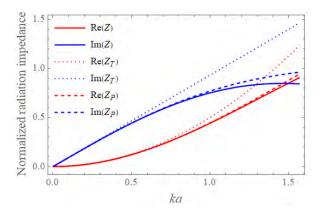

where  $J_1$  and  $J_2$  are Bessel functions of first and second order. The exact normalized radiation impedance is shown in Fig. 2.2a for the real and the imaginary part. The normalized radiation impedance is plotted as function of ka, which is the wavenumber-radius product. For large ka values the radiation resistance approaches the constant used for normalization;  $\rho_{\rm m} c_{\rm m} \pi a^2$ , while the radiation reactance asymptotic approaches zero.

Combining Eq. (2.38) and Eq. (2.44) the resonance frequency can be solved numerically for any CMUT design. However, to obtain an analytical expression for the resonance frequency in immersion an approximation for the radiation impedance is required. For small ka products the Taylor expansion of Eq. (2.44) can be used. The real part then results in

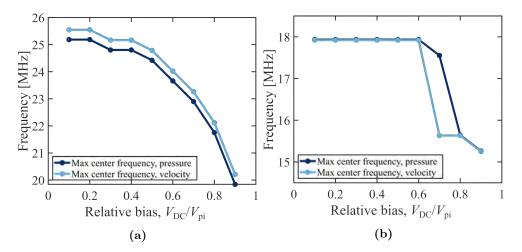

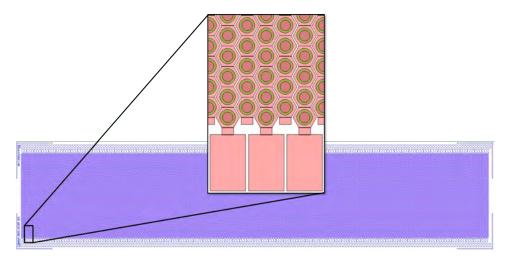

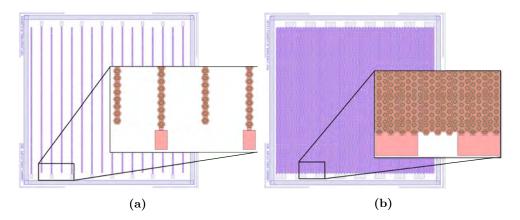

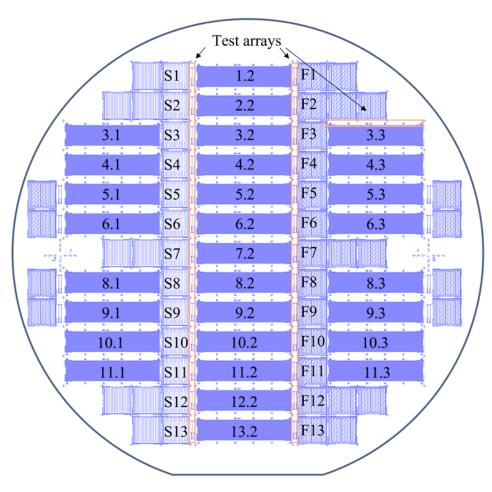

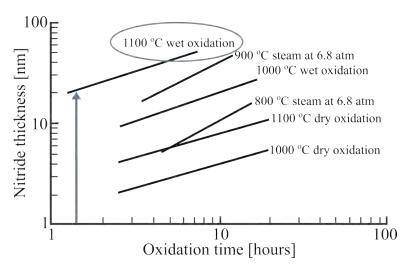

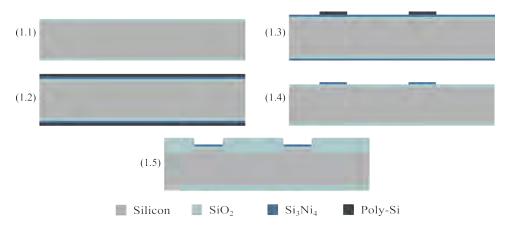

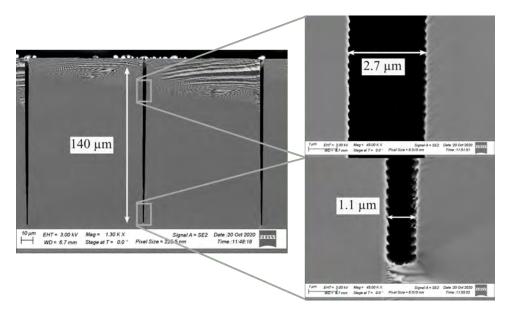

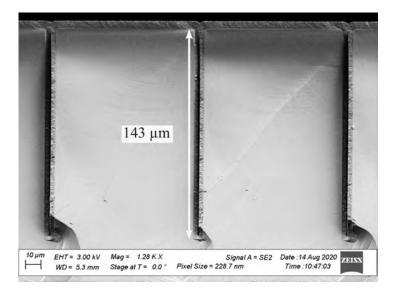

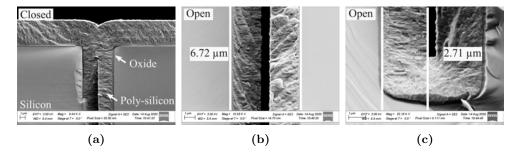

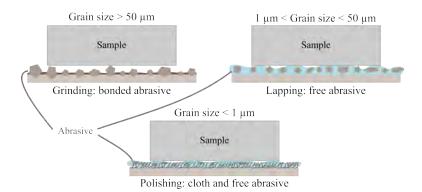

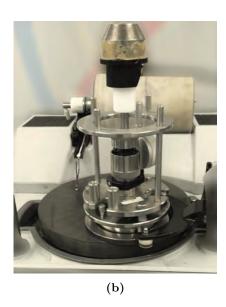

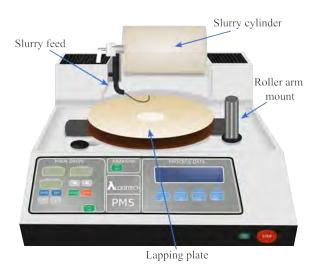

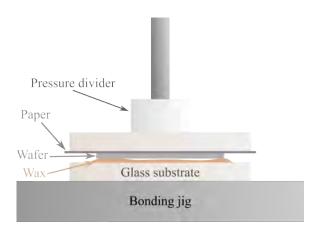

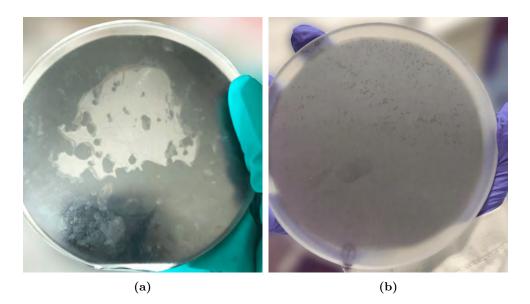

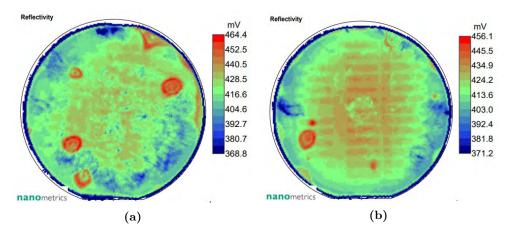

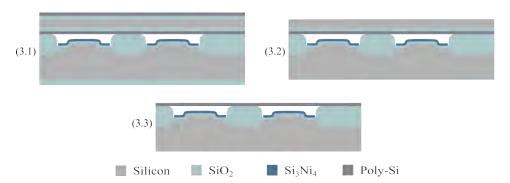

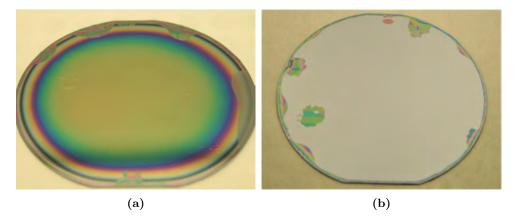

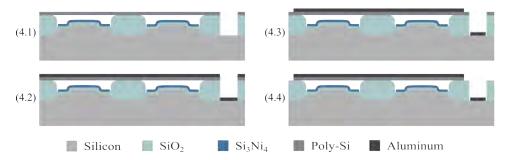

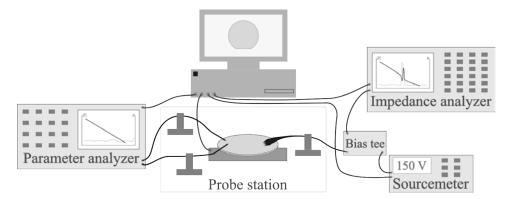

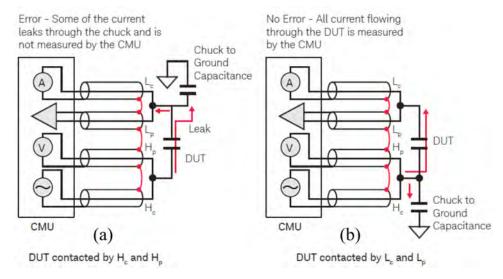

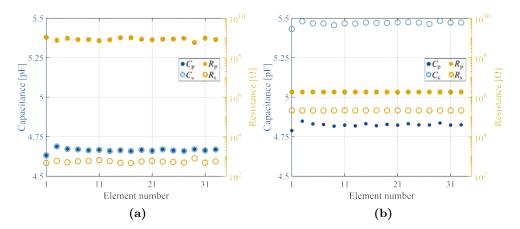

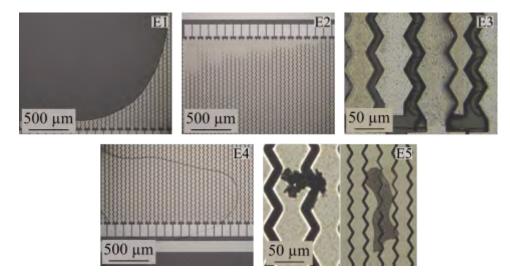

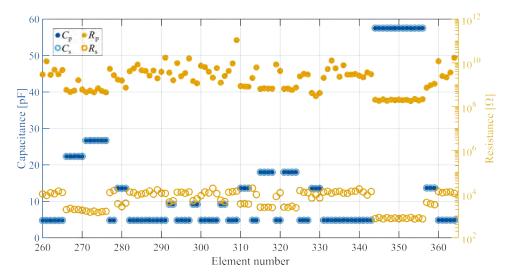

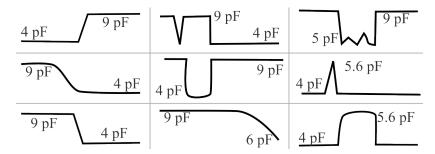

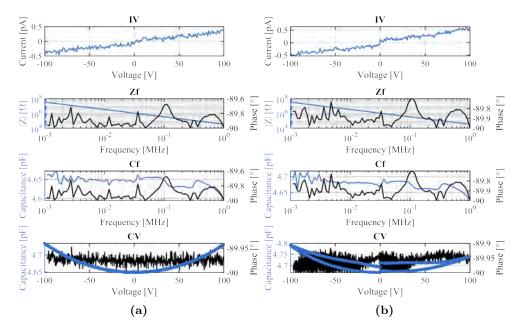

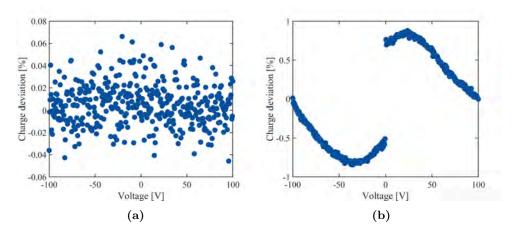

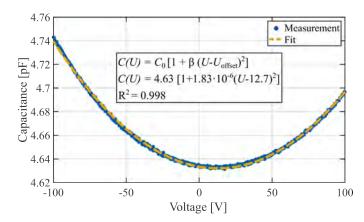

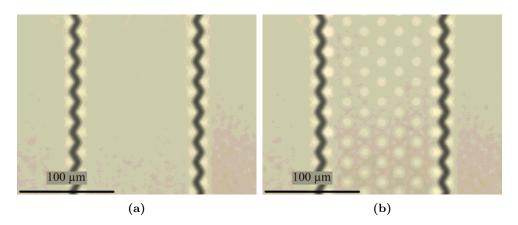

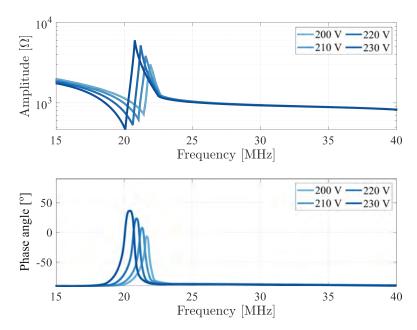

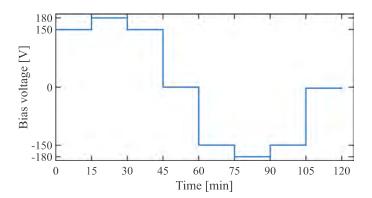

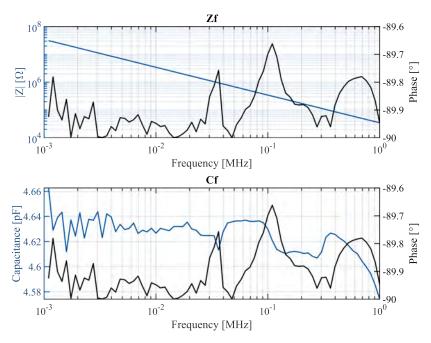

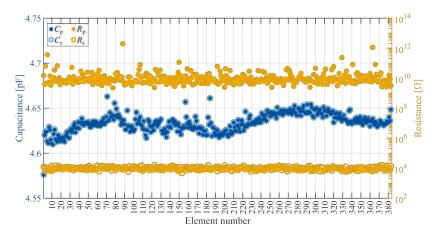

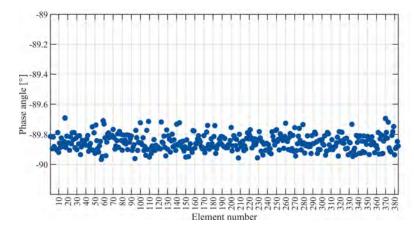

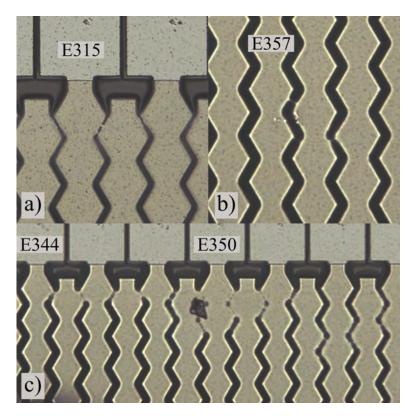

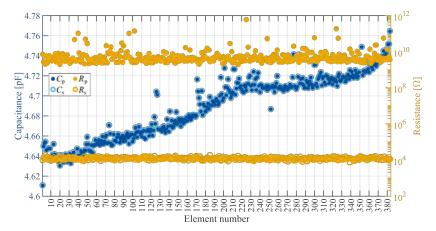

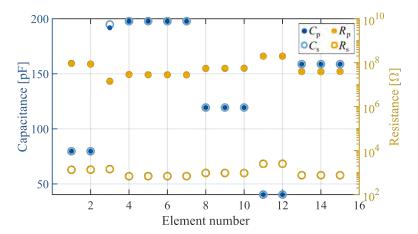

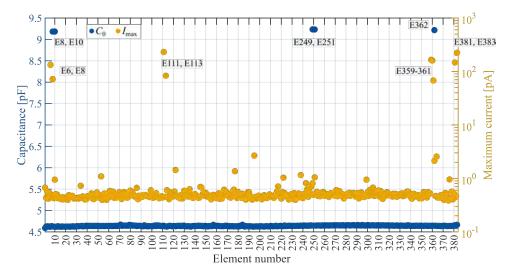

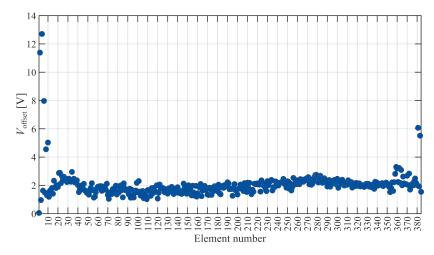

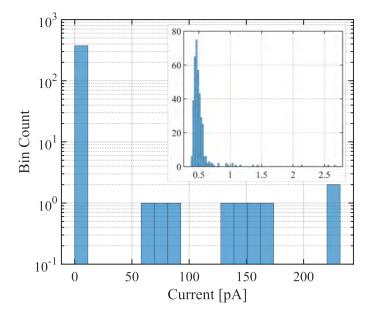

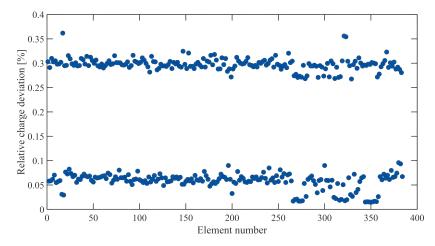

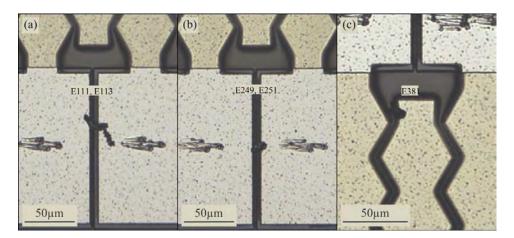

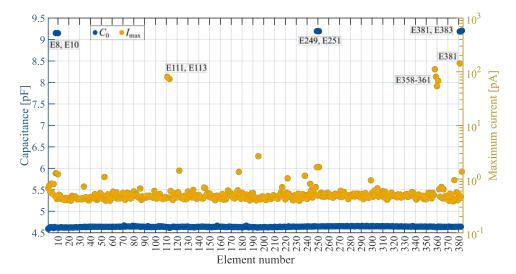

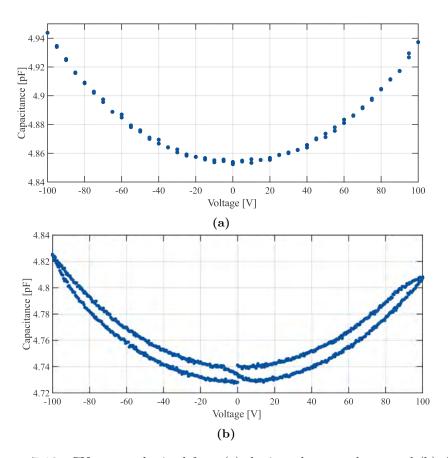

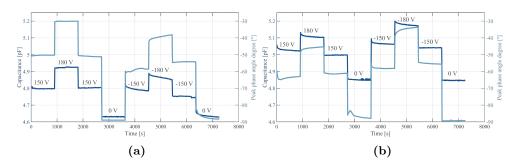

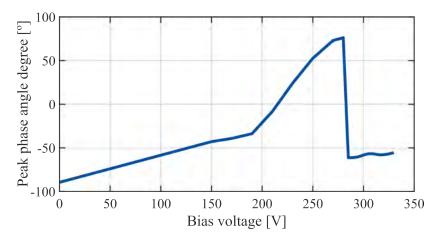

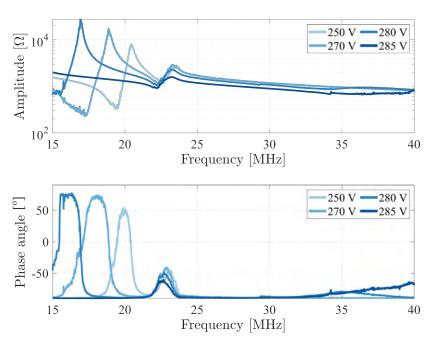

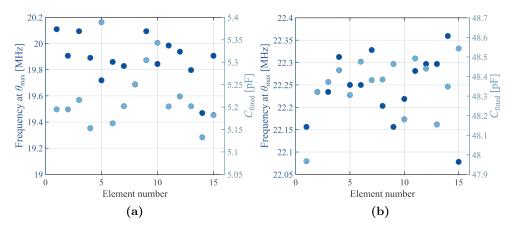

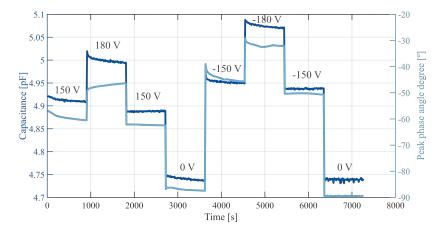

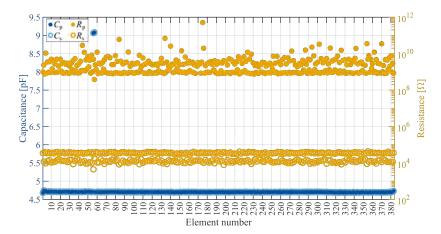

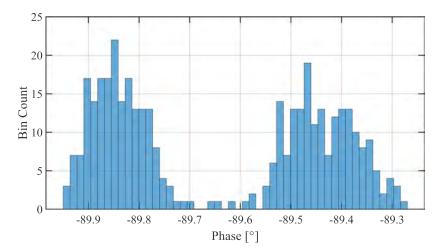

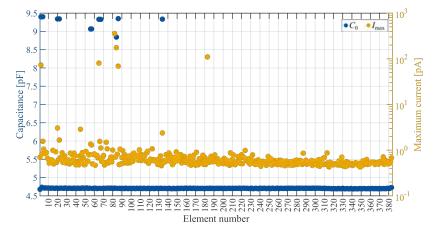

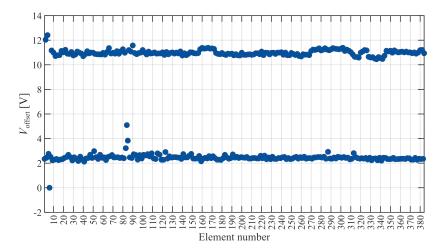

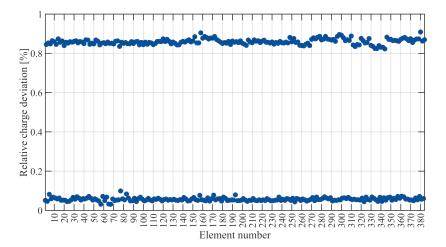

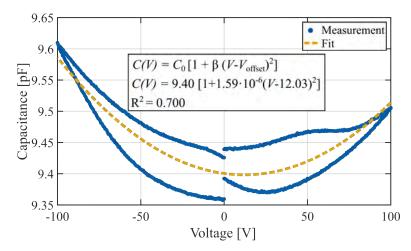

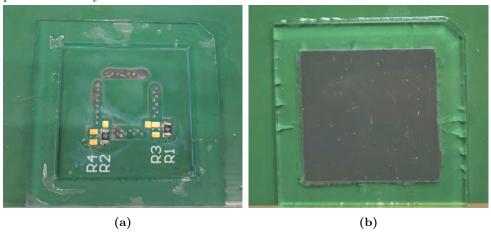

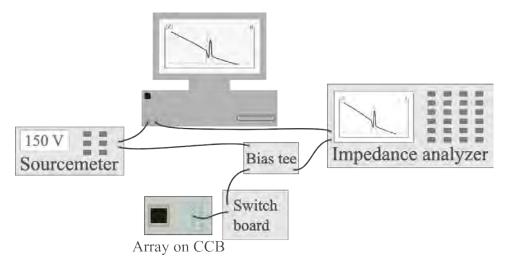

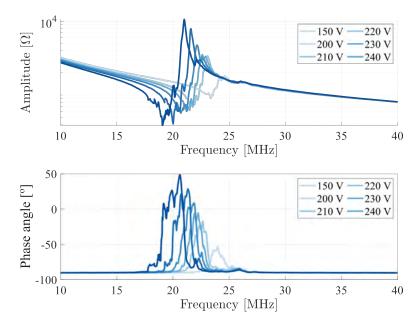

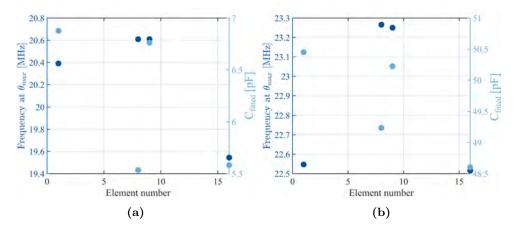

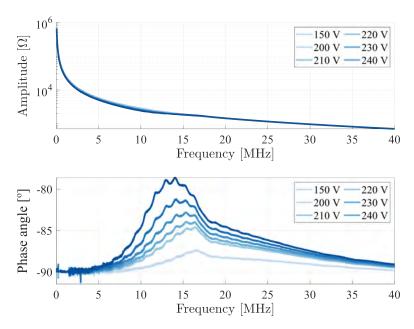

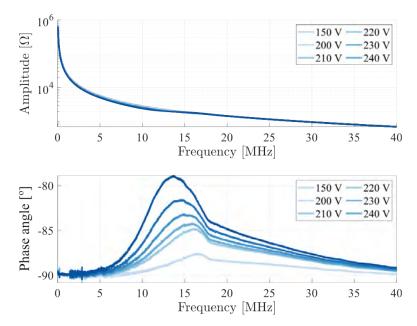

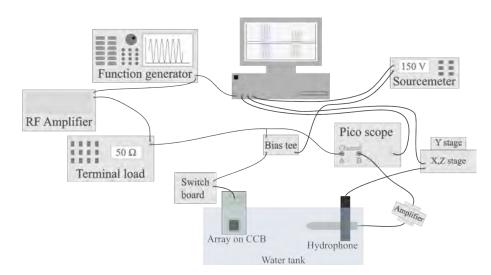

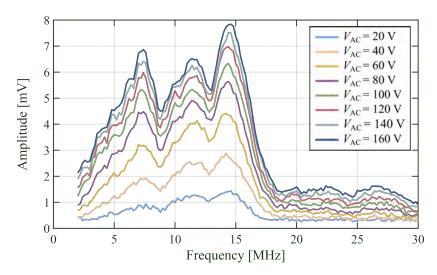

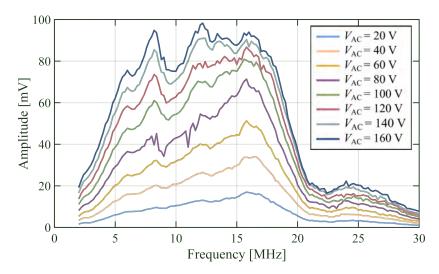

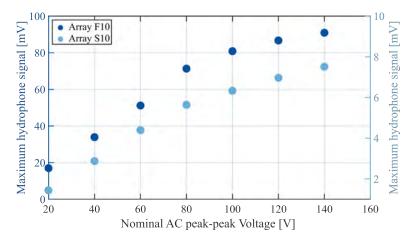

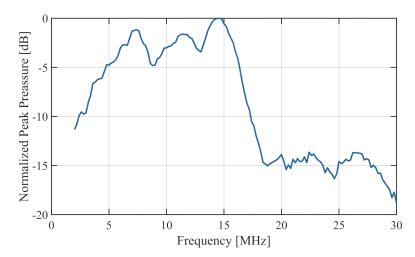

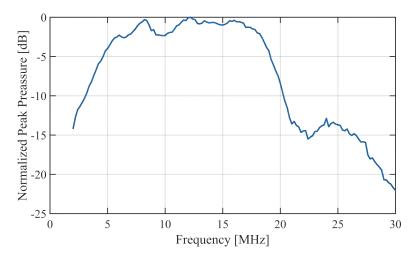

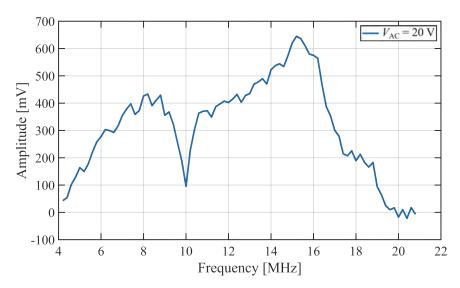

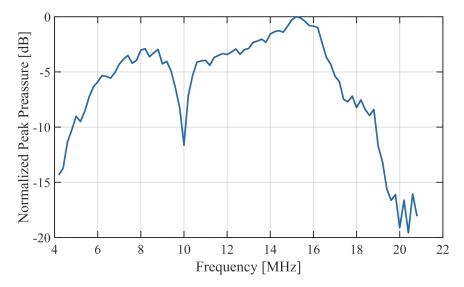

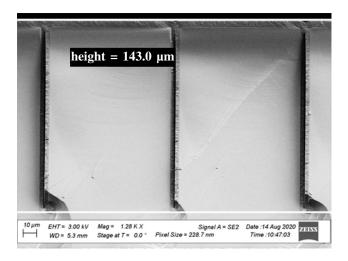

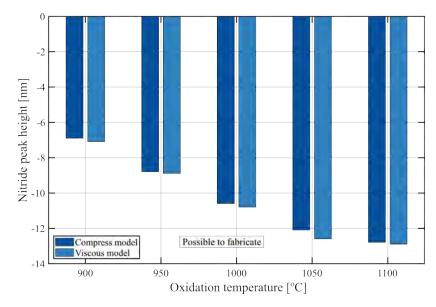

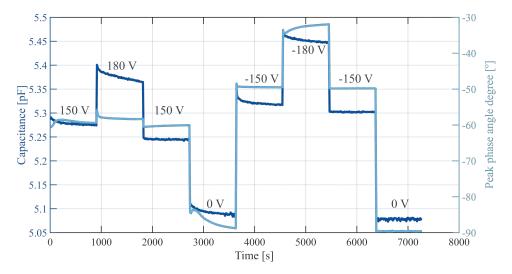

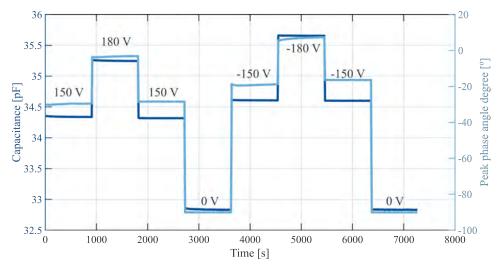

$$\Re(Z_{\text{Taylor}}) = \frac{1}{2}a^2 c_{\text{m}}(ka)^2 \pi \rho_{\text{m}} + O(ka)^3, \tag{2.45}$$