**DTU Library**

## Carrier Distortion in Hysteretic Self-Oscillating Class-D Audio Power

Amplifiers: Analysis and Optimization

Høyerby, Mikkel Christian Kofod; Andersen, Michael A. E.

Published in: **IEEE Transactions on Power Electronics**

Link to article, DOI: 10.1109/TPEL.2008.2007956

Publication date: 2009

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA): Høyerby, M. C. K., & Andersen, M. A. E. (2009). Carrier Distortion in Hysteretic Self-Oscillating Class-D Audio Power: Amplifiers: Analysis and Optimization. *IEEE Transactions on Power Electronics*, 24(3-4), 714-729. https://doi.org/10.1109/TPEL.2008.2007956

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Carrier Distortion in Hysteretic Self-Oscillating Class-D Audio Power Amplifiers: Analysis and Optimization

Mikkel C. W. Høyerby, Member, IEEE, and Michael A. E. Andersen, Member, IEEE

Abstract—An important distortion mechanism in hysteretic selfoscillating (SO) class-D (switch mode) power amplifiers--carrier distortion--is analyzed and an optimization method is proposed. This mechanism is an issue in any power amplifier application where a high degree of proportionality between input and output is required, such as in audio power amplifiers or xDSL drivers. From an average-mode point of view, carrier distortion is shown to be caused by nonlinear variation of the hysteretic comparator input average voltage with the output average voltage. This easily causes total harmonic distortion figures in excess of 0.1-0.2\%, inadequate for high-quality audio applications. Carrier distortion is shown to be minimized when the feedback system is designed to provide a triangular carrier (sliding) signal at the input of a hysteretic comparator. The proposed optimization method is experimentally proven in an audio power amplifier leading to THD figures that are comparable to the state of the art. Experimental hardware is a hysteretic SO bandpass current-mode-controlled single-ended audio power amplifier capable of 45 W into 8  $\Omega$  or 80 W into 4  $\Omega$ from a  $\pm 34$  V supply with less than 0.03% THD from 100 Hz to 6.7 kHz. Carrier distortion is shown to account for this limitation in THD performance.

Index Terms—Audio, class-D, hysteretic, power amplifier, sliding.

#### I. INTRODUCTION

WITCH-MODE (class D) audio power amplifiers have been a commercial success over the past decade, replacing traditional linear (class A/AB/B) amplifiers in many applications. The main driver has been the reduction in physical size resulting from the increased efficiency [1].

It is generally well understood that errors in the switching stage of the class-D amplifier can introduce significant harmonic distortion to the amplifier output [1]–[3]. However, with the ever-increasing performance of modern power MOSFETs, the significance of switching stage errors diminishes [4], [5]. As a result, the distortion generated by the pulsewidth modulation (PWM) and control process itself becomes visible. An excellent illustration of this is given in [5], where the distortion generated by the injection of switching ripple components from the feedback circuitry into the PWM is analyzed by the use of discrete-time system theory. As presented, this analysis is

Manuscript received March 17, 2008; revised September 12, 2008. First published March 10, 2009; current version published April 8, 2009. Recommended for publication by Associate Editor P. Jain.

M. C. W. Høyerby is with Motorola Denmark, DK-2600 Glostrup, Denmark (e-mail: mikkel.hoyerby@motorola.com).

M. A. E. Andersen is with the Department of Electrical Engineering, Technical University of Denmark, DK-2800 Lyngby, Denmark (e-mail: ma@elektro.dtu.dk).

Digital Object Identifier 10.1109/TPEL.2008.2007956

only applicable to clocked/driven control systems, such as those based on the traditional triangle-and-comparator PWM.

For self-oscillating (SO) control systems, which have been successfully commercialized [6] for class-D audio, details on the distortion generated by the modulation and control process are more scarce, although a very good example is given in [7] for SO systems without comparator hysteresis. However, design suggestions on how to affect the amount of distortion generated by the modulation process are not offered, nor does the analysis directly apply to SO systems with comparator hysteresis. For these systems, only a few hints on optimizing modulation linearity are offered [8]–[10].

This paper examines distortion generated by the modulation process in the hysteretic SO class of control systems, a class that has yielded some of the most impressive [9], [11] THD figures published for switch-mode audio power amplifiers. The analysis is carried out using the well-established average modeling approach, leading to an optimization method proposal that is consistent with prior art findings, and complemented by experimental results on a representative, nontrivial, hysteretic SO class-D audio power amplifier. Although this paper is focused on audio power amplification, other applications exist where accurate amplification of ac signals is required. One example is various digital subscriber line (xDSL) drivers [7], where high output spectral purity is required. Another example is tracking power supplies in high-efficiency RF power amplification systems [12]. Here, the tracking power supply in some schemes directly modulates the output of an RF power amplifier, adding any distortion introduced by the tracking power supply to the RF power amplifier output. A final example is ac transmission systems [13], [14].

#### II. HYSTERESIS-BASED SO CONTROLLERS

The hysteresis-based SO controllers reviewed in this paper can be considered a small, low-complexity subset of the very large set of sliding-mode control (SMC) systems. For audio power amplification using a single-phase buck-type power stage, the hysteretic SO control system will generally contain one comparator with hysteresis, which, based on a linear combination of system states and the audio input, selects one of the two possible switching states (high/low) for the power stage.

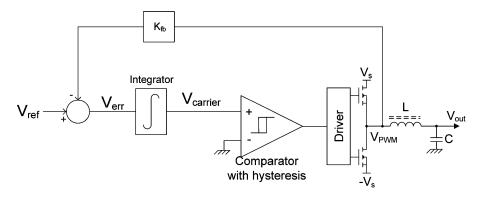

A very simple but applicable example of such a control system is the astable integrating multivibrator (AIM) [8], [15] shown in Fig. 1. Capable of good results [8] in practice, it has the

Fig. 1. Simple hysteretic SO audio power amplifier example—the AIM [8], [15].

disadvantage of not having feedback around the output filter, increasing the impact of the output filter design on amplifier distortion levels, output impedance, and frequency response [6], [9], [11]. Several alternative hysteretic SO controller implementations have been proposed in the context of audio power amplification, where the main difference lies in the way in which the output inductor current is effectively fed back, since this is the most difficult system state to measure. Some solutions opt for feeding back the output capacitor current instead, since this is the same as the inductor current with output current feedforward added [16]. The capacitor current can either be estimated by differentiation of the capacitor voltage [9], [17] and added to the raw capacitor voltage as done by proportional-derivative (PD) feedback, or measured directly with a current sense transformer [11], [18]. Alternatively, the inductor current can be estimated by low-pass filtering of the inductor voltage [10], effectively leading to bandpass current control [19]. In all cases, the use of postfilter feedback generally serves to lessen the negative effects of the output filter. Many very similar solutions have appeared in the somewhat wider context of single-phase buck dc/dc converters, where PD-based capacitor voltage feedback is richly represented [20]–[23] along with capacitor current feedback [24], [25] and direct inductor current feedback [26]. It has also been shown that the equivalent series resistance of the output capacitor can be usefully incorporated into the capacitor current estimation system [27], relaxing the demands on the differentiation circuitry.

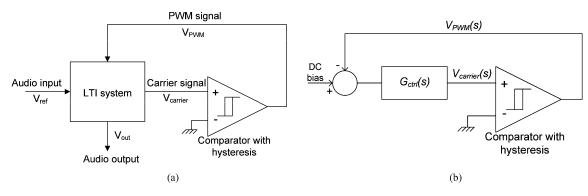

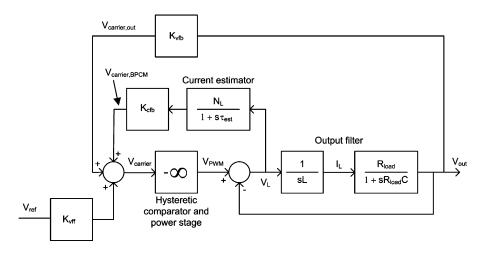

At this time, it is useful to formally define the class of systems studied as any system with a hysteretic comparator driving a linear time-invariant system with relevant feedback and reference inputs added, as shown in Fig. 2. Of particular interest, it turns out, is the generation of the carrier signal  $(V_{\rm carrier})$ , which is described by the effective controller transfer function (a.k.a. "loop filter" [5]),  $G_{\rm ctrl}(s)$ :

$$G_{\rm ctrl}(s) \equiv rac{V_{

m carrier}(s)}{V_{

m PWM}(s)}$$

(1)

These generalizations allow all of the aforementioned systems to be represented, and are often adopted in prior art [28]–[30].

As sliding mode controllers, extensive theory [31] exists for dealing with the stability and dynamics of hysteretic SO controllers. In the application of controlling simple switch-mode power converters, classical sliding mode theory is based on the assumption

$$V_{\text{carrier}} = 0$$

(2)

where  $V_{\rm carrier}$  is the input to the hysteretic comparator, generally known as the "sliding variable" in SMC context or the "carrier signal" in SO control context. This approximation can be very useful [32], but also has its shortcomings [16]. For the presented study of linearity and distortion in sliding mode controllers, it is absolutely essential to depart from this basic assumption. The carrier voltage is still usefully described as *almost* zero, but the implications of "almost" need to be considered

$$V_{\text{carrier}} \approx 0$$

(3)

Prior art has demonstrated several examples of this; a nonzero carrier average was used in [33] to assign a low-frequency gain to the hysteretic comparator, and it is well known [34] that a describing function can be used to find its gain at the switching/oscillation frequency of the control loop. These two methods can even be combined to yield an estimated, but still quite accurate, transfer function for the hysteretic comparator [35]. A nonzero carrier average caused by delays in the comparator and power stage is shown in [36] to lead to inaccuracy in the average output current of a hysteretic current control loop. In the following, the effects of nonzero carrier average caused by the properties of  $G_{\rm ctrl}(s)$  are examined.

#### III. CARRIER DISTORTION

The carrier distortion [8] mechanism in hysteretic SO controllers is claimed [8]–[10] to be a function of the shape of the carrier signal waveform, with a triangular waveform being the optimum. In order to properly explain this proposed distortion mechanism, it is useful to examine the simplest conceivable hysteretic SO control system: the AIM. The approach adopted is to analyze the average (dc) carrier voltage variation with the amplifier dc operating point, expressed as a steady-state duty cycle *D* for different degrees of integrator ideality. Under the assumption of quasi-stationary behavior, the dc characteristics of the loop will also apply at audio frequencies [5]. Practically, the integrator in the AIM is replaced with a pole and a gain to provide variable carrier signal "straightness" in a way that is simple enough to allow exact analysis. With this imperfect

Fig. 2. Generalized views of hysteretic SO control systems for audio applications. (a) Overall system. (b) Carrier generation process.

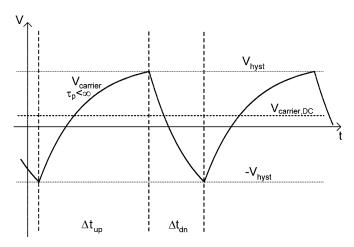

Fig. 3. AIM carrier waveform (D=1/3) with single-pole  $G_{\rm ctrl}(s)$  as considered for carrier distortion analysis.  $V_{\rm carrier,dc}$  is the average of the carrier waveform, which evidently can be nonzero in spite of a symmetrical hysteresis window  $\pm V_{\rm hyst}$  and zero delay.

integrator, a representative example of the carrier signal in the AIM is shown in Fig. 3. Note that zero time delay in the comparator and power stage has been assumed for the analysis performed hereafter.  $\pm V_{\rm hyst}$  denotes the hysteresis window. Likewise, it has been assumed that  $V_s=1$  and  $K_{fb}=1$  in order to clarify the analysis.

The AIM loop integrator is replaced with the transfer function G(s), which also becomes the  $G_{\rm ctrl}(s)$  of the system

$$G(s) = G_{\text{ctrl}}(s) = \frac{G_p}{1 + s\tau_p} \tag{4}$$

Note that  $G_p$  is a gain that numerically equals  $\tau_p$ , a distinction made to avoid unit confusion in the following analysis. The purpose of this particular choice of  $G_p$  is to ensure that  $G_{\rm ctrl}(s)$  converges toward the ideal integrator when  $\tau_p$  is made large

$$\lim_{\tau_p \to \infty} G_{\text{ctrl}}(s) = \frac{1}{s} \tag{5}$$

The step response of  $G_{\text{ctrl}}(s)$  is given by

step

$$\{G_{\text{ctrl}}(s)\} = G_p(1 - e^{-(t/\tau_p)})$$

(6)

Assuming that the feedback system has high loop gain, the steady-state PWM voltage per-cycle average will represent the

TABLE I CARRIER SIGNAL INITIAL/FINAL CONDITIONS IN AIM WITH IMPERFECT INTEGRATOR

| PWM level      | Initial $(t=0)$ value         | Final $(t=\infty)$ value  |

|----------------|-------------------------------|---------------------------|

| $V_{PWM} = -1$ | $-V_{\mathit{hyst}}$          | $2 \cdot D \cdot G_p$     |

| $V_{PWM} = 1$  | $V_{\scriptscriptstyle hyst}$ | $2 \cdot (D-1) \cdot G_p$ |

reference voltage exactly

$$\langle V_{\rm PWM} \rangle_{T_{\rm crit}} = V_{\rm ref}$$

(7)

This allows the reference voltage to be expressed by the PWM signal steady-state duty cycle D

$$\langle V_{\text{PWM}} \rangle_{T_{\text{em}}} = 2(D-1) \Rightarrow V_{\text{ref}} = 2(D-1)$$

(8)

The input to the loop filter is given by

$$V_{\text{err}} = V_{\text{ref}} - V_{\text{PWM}} = \begin{cases} V_{\text{ref}} + 1, & V_{\text{PWM}} = -1 \\ V_{\text{ref}} - 1, & V_{\text{PWM}} = 1 \end{cases}$$

(9)

This can be rewritten as

$$V_{\rm err} = \begin{cases} 2D, & V_{\rm PWM} = -1\\ 2(D-1), & V_{\rm PWM} = 1 \end{cases}$$

(10)

In this case, D and (D-1) both stringently have the unit of V. Since the PWM signal can be considered as a series of step functions, a segment of the carrier voltage can be found by using the step response of  $G_{\rm ctrl}(s)$  and observing that an initial value has to be added to reflect the presence of the hysteresis window  $\pm V_{\rm hyst}$ . The carrier voltage will change exponentially with time constant  $\tau_p$  and initial and final values as given in Table I.

The carrier voltage can thus be described as

$V_{\text{corrior}}(t)$

$$= \begin{cases} -V_{\text{hyst}} + (2DG_p + V_{\text{hyst}}) \left(1 - e^{-(t/\tau_p)}\right), & V_{\text{PWM}} = -1\\ V_{\text{hyst}} + (2(D-1)G_p - V_{\text{hyst}}) \left(1 - e^{-(t/\tau_p)}\right), & V_{\text{PWM}} = 1 \end{cases}$$

(11)

The up/down-slope periods  $\Delta t_{\rm up}$  and  $\Delta t_{\rm dn}$  can now be found by adding the boundary condition of the carrier signal hitting the hysteresis window, leading to the equations

$$-V_{\text{hyst}} + (2DG_p + V_{\text{hyst}}) \left(1 - e^{-(\Delta t_{\text{up}}/\tau_p)}\right) = V_{\text{hyst}} \wedge V_{\text{hyst}} + (2(D-1)G_p - V_{\text{hyst}}) \left(1 - e^{-(\Delta t_{\text{dn}}/\tau_p)}\right) = -V_{\text{hyst}}$$

(12)

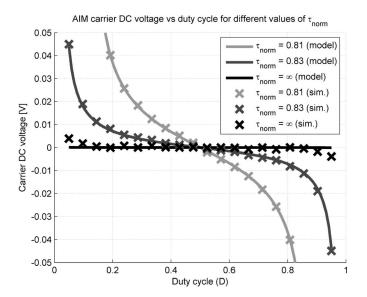

Fig. 4. Modeled (16) and simulated carrier dc voltages plotted for variable duty cycle. Modeled results match simulated results very well.

These equations can be solved easily, leading to

$$\Delta t_{\rm up} = -\tau_p \ln \left( 1 - \frac{2V_{\rm hyst}}{2DG_p + V_{\rm hyst}} \right) \wedge \Delta t_{\rm dn}$$

$$= -\tau_p \ln \left( 1 - \frac{2V_{\rm hyst}}{2(1-D)G_p + V_{\rm hyst}} \right) \tag{13}$$

In order to provide a more general view of the influence of  $\tau_p$  on system behavior,  $\tau_p$  can be normalized to the nominal (D=0.5) switching period  $(T_{\rm sw,nom})$  of the loop

$$\tau_{\text{norm}} = \frac{\tau_p}{T_{\text{sw,nom}}} = \frac{\tau_p}{\Delta t_{\text{up}} + \Delta t_{\text{dn}}} \bigg|_{D=0.5}$$

(14)

Now, the only problem is to find the average (dc) value of the carrier voltage with the given variables. This is done by calculating the per-cycle average of the carrier by integrating the carrier voltage over one switching period

$$V_{\text{carrier,dc}}(D) = \frac{1}{\Delta t_{\text{up}} + \Delta t_{\text{dn}}} \int_{0}^{\Delta t_{\text{up}} + \Delta t_{\text{dn}}} V_{\text{carrier}}(t) dt$$

(15)

Solving this integral (Mathematica was used for symbolic solution) results in (16) as shown at the bottom of this page.

This expression is best analyzed by plotting the expression output for different parameter inputs as in Fig. 4. It is obvious that the carrier dc voltage varies with D in a nonlinear manner when the loop filter is not an integrator. If  $\tau_p$  approaches infinity, this expression can be shown to converge toward zero. Since the

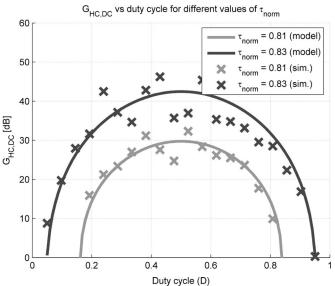

Fig. 5. Modeled [using numerical evaluation of (17)] and simulated hysteretic comparator dc gain  $G_{\rm HC,dc}$ . Deviation from the ideal loop filter ( $\tau_p=\infty$ ) causes reduction and nonlinearity in  $G_{\rm HC,dc}$ . Results for  $\tau_p=\infty$  would be a horizontal line at  $G_{\rm HC,dc}=\infty$ . The nonlinearity is symmetrical around D=0.5, so only odd harmonic distortion is produced.

gain of the hysteretic comparator can be defined as

$$G_{\rm HC,dc}(D) \equiv \frac{((\partial \langle V_{\rm PWM} \rangle_{T_{\rm sw}})/\partial D)}{((\partial V_{\rm carrier,dc}(D))/\partial D)}$$

$$= \frac{2}{((\partial V_{\rm carrier,dc}(D))/\partial D)}$$

(17)

it is also obvious that the hysteretic comparator exhibits a non-constant gain at dc. In other words, a nonlinear element has been introduced into the loop, leading to harmonic distortion. This distortion generated by the nonlinear variation of  $V_{\rm carrier,dc}$  with D is exactly what has previously been named *carrier distortion*.

For the AIM with the considered, imperfect loop filter, even with all the simplifications made (zero time delay, only dc considered), the analytical expression for  $G_{\rm HC,dc}$  gets too complicated to be of real value, so numerical differentiation was used for finding the carrier dc voltage derivative. Analytical and simulated values of  $G_{\rm HC,dc}$  are shown in Fig. 5. Since  $V_{\rm carrier,dc}(D)$  is generally larger and more variable for smaller values of  $\tau_{\rm norm}$ , the dc gain of the hysteretic comparator also decreases with  $\tau_{\rm norm}$ . Since the average of a perfectly triangular carrier oscillating within  $\pm V_{\rm hyst}$  is zero, the dc gain of the hysteretic comparator could theoretically be infinite. In practice, time delay in the comparator (and power stage) ensures that this never happens [33], [35].

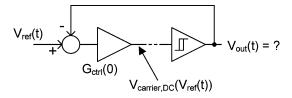

In order to evaluate the effect of the found variation of  $V_{\rm carrier,dc}$  with D on amplifier distortion, the system is modeled as shown in Fig. 6.

$$V_{\text{carrier,dc}}(D) = -2G_p \frac{(1-D)\ln(1 - (2V_{\text{hyst}}/(2G_p(1-D) + V_{\text{hyst}}))) - D\ln(1 - (2V_{\text{hyst}}/(2G_pD + V_{\text{hyst}})))}{\ln(1 - (2V_{\text{hyst}}/(2G_p(1-D) + V_{\text{hyst}}))) + \ln(1 - (2V_{\text{hyst}}/(2G_pD + V_{\text{hyst}})))}$$

(16)

Fig. 6. Model of the AIM loop used for determination of output voltage waveform when taking carrier distortion into consideration. Reference signal  $V_{\rm ref}(t)$  is assumed to be dc or "almost dc."

The output of the AIM model in Fig. 6 is given by

$$V_{\text{out}}\left(t\right) = V_{\text{ref}}\left(t\right) - \frac{V_{\text{carrier,dc}}\left(V_{\text{ref}}\left(t\right)\right)}{G_{\text{ctrl}}\left(0\right)} \tag{18}$$

The output,  $V_{\rm out}$  is here formally defined as the per-(switch)-cycle average PWM voltage

$$V_{\rm out} \equiv \langle V_{\rm PWM} \rangle_{T_{\rm out}}$$

(19)

Assuming that the output voltage has relatively low distortion, the D of the AIM will be determined almost exclusively by  $V_{\rm ref}$ . Thus, for a given  $V_{\rm ref}$ , D is approximated as

$$D = \frac{1}{2} \left( V_{\text{ref}} + 1 \right) \tag{20}$$

For a sinusoidal input

$$V_{\rm ref}(t) = M \sin\left(2\pi f_{\rm ref}t\right) \tag{21}$$

the duty cycle is therefore approximated as

$$D(t) = \frac{1}{2} [M \sin(2\pi f_{\text{ref}} t) + 1]$$

(22)

Note that since the studied AIM has a reference-to-output gain of unity and conceptually operates from 1 V supplies, the amplitude M of the sine wave corresponds to the modulation index of the PWM signal. The peak duty cycle  $D_{\rm max}$  and the modulation index M are generally related as follows:

$$D_{\max} = \frac{1}{2} (1 + M) \tag{23}$$

Thus, the output of the AIM is

$$V_{\text{out}}(t) = \frac{1}{2} \left[ M \sin \left( 2\pi f_{\text{ref}} t \right) + 1 \right] - \frac{V_{\text{carrier,dc}} \left( \frac{1}{2} \left[ M \sin \left( 2\pi f_{\text{ref}} t \right) + 1 \right] \right)}{G_{\text{ctrl}}(0)}$$

(24)

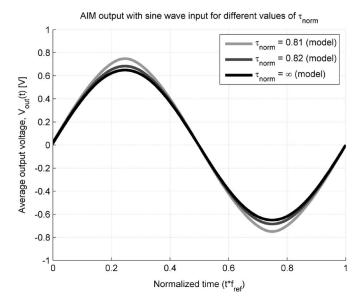

This expression is best evaluated numerically, yielding the averaged output of the AIM, complete with carrier distortion. As shown in the calculated example waveforms in Fig. 7, the distortion generated by using a pole as a loop filter in the AIM is of expansive character, causing the peaks of the reference signal to come out at a higher level than desired. This is perhaps surprising, since  $G_{\rm HC,dc}$  is reduced at high D. However, this compressive action is more than counteracted by the requirement for a specific carrier dc voltage  $V_{\rm carrier,dc}$  to be present for a given D. As an example, assume that the reference is +0.5. The loop will attempt to establish a D of 0.75, but looking at Fig. 4, the carrier voltage must contain a small,

Fig. 7. Calculated AIM output with values of  $\tau_{\rm norm}(M=0.65)$ . Carrier distortion caused by small time constants causes signal expansion at high output levels

negative dc component. Looking at Fig. 6, this can only be produced by an output dc voltage that is slightly higher than prescribed by the reference, causing the expansion effect apparent in Fig. 7.

From the AIM output, harmonic distortion products are found by Fourier analysis. The output waveform is expressed by the Fourier series (with complex coefficients) given by

$$c_{\text{out},n} = f_{\text{ref}} \int_{t=0}^{t=(1/f_{\text{ref}})} V_{\text{out}}(t) e^{-j2\pi f_{\text{ref}}n} dt$$

(25)

where  $|c_{\text{out},1}|$  corresponds to the fundamental amplitude,  $|c_{\text{out},3}|$  corresponds to the third-harmonic distortion product, etc. The THD generated by carrier distortion can be calculated from these numbers by evaluating the following expression:

THD =

$$\frac{\sqrt{|c_{\text{out},2}|^2 + |c_{\text{out},3}|^2 + \dots + |c_{\text{out},n}|^2}}{|c_{\text{out},1}|}$$

(26)

In practice, the following expression is a good approximation since there are no even harmonics:

THD

$$\approx \frac{\sqrt{|c_{\text{out,3}}|^2 + |c_{\text{out,5}}|^2 + \dots + |c_{\text{out,n}}|^2}}{|c_{\text{out,1}}|}$$

(27)

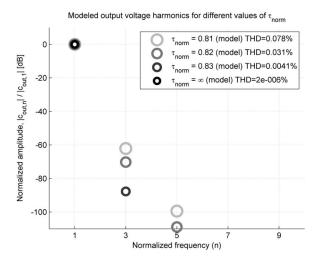

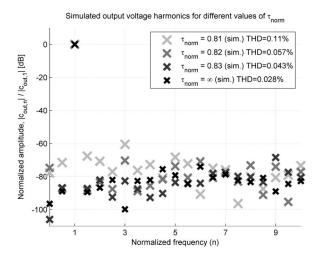

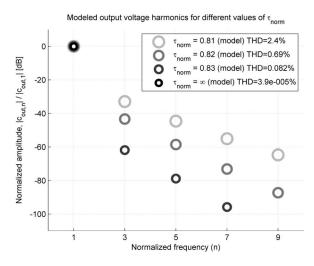

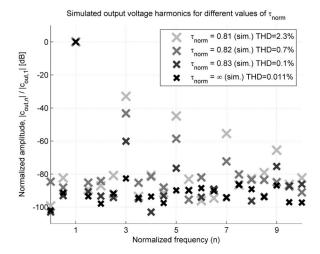

In the studied AIM example, we numerically evaluate harmonics and THD from the derived analytical expressions and compare them with simulations results in the numbers shown in Figs. 8–11. It is evident that the analysis approach shown is capable of describing the carrier distortion mechanism very well. It is also evident that this mechanism can easily produce significant harmonic distortion in an amplifier with a perfect power stage with stiff supply voltage, and no delay and no dead-time distortion, justifying the analysis performed. Finally, the generated distortion exhibits strong variation with  $\tau_{\rm norm}$  in the area of 0.80–0.85. This simply reflects that the first segment (well

Fig. 8. Output harmonics from AIM found by calculation; M = 0.2.

Fig. 9. Output harmonics from AIM found by simulation; M = 0.2.

below  $t = \tau_p$ ) of an exponentially shaped carrier has almost-constant slope, with curvature becoming significantly closer to  $\tau_p$ .

Several implications result from this analysis. First, it allows for proper explanation of the carrier distortion phenomenon by reference to the average modeling technique used. The explanation offered is that a nontriangular carrier signal (the result of not having an integrator-type  $G_{\text{ctrl}}(s)$ ) requires voltages that are a nonlinear function of the reference voltage to be present at the hysteretic comparator input, directly causing distortion, and in the process causing the hysteretic comparator to exhibit a nonconstant small-signal dc gain. Second, it allows the amount of carrier distortion in a class-D audio amplifier design to be predicted analytically from data on the carrier signal dc voltage. This is useful information in that it provides a designer with a tool for determining just how "perfect" the carrier signal should be to meet a target THD specification without time-consuming, repetitive simulations of multiple reference signal periods. Finally, the analysis supports statements in prior art [8] claiming that the carrier signal should be triangular (resulting from the use of an integrator as loop filter in the AIM), arguing from the

Fig. 10. Output harmonics from AIM found by calculation; M = 0.65.

Fig. 11. Output harmonics from AIM found by simulation;  $M=\ 0.65.$

point of view that the carrier voltage dc component should be a linear function of duty cycle to avoid causing nonlinearity. It is then taken as a trivial matter to show that a perfectly triangular carrier oscillating between  $\pm/-V_{\rm hyst}$  has to have an average of zero for any D.

#### IV. CARRIER DISTORTION OPTIMIZATION

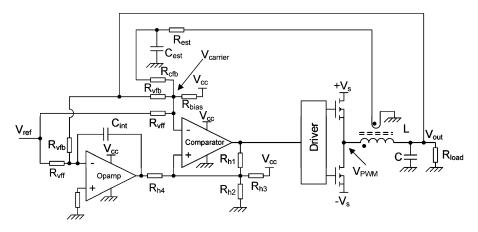

The previous section provided an analytical justification for pursuing a triangular carrier signal. In an AIM, this is easy; any practical operational amplifier has enough dc gain for realizing a loop filter that sufficiently resembles an integrator. In other feedback configurations, however, the problem is much more severe. For example, considering the hysteretic bandpass current-mode (BPCM) control topology demonstrated in [10] (and illustrated in Fig. 12), it is not obvious how to make the output of the combined voltage and current estimate feedbacks respond with a ramp to a step input, except perhaps by perfect estimation of the inductor current and removal of the output voltage feedback. This would make the amplifier a current source instead of the desired voltage source. The hysteretic BPCM topology has still been demonstrated to be capable of very good THD figures

Fig. 12. Simple single-ended BPCM amplifier implementation [10].

Fig. 13. Small-signal model of BPCM amplifier [10] using infinite-gain (equivalent to assuming sliding-mode operation [23], [31]) hysteretic comparator model.

(0.01%–0.03% range) with a modest control system complexity. It is a dual-loop feedback system, which incorporates the output filter dynamics, making the loop design nontrivial in comparison with the AIM. As such, it is an ideal test vehicle for the demonstration of a new analytical carrier distortion minimization technique based on the pursuit of a triangular carrier signal.

The carrier linearization approach that is proposed has the objective of shaping the step response of  $G_{\rm ctrl}(s)$  as a ramp. The proposed method for minimization and evaluation of carrier distortion is simply as follows.

- 1) Compute the step response of  $G_{\text{ctrl}}(s)$  analytically.

- 2) Compute second (time-) derivative of  $G_{\rm ctrl}(s)$  step response.

- 3) Use second derivative to find criteria for ensuring constantsloping step response.

- 4) Use found criteria to design control loop.

- 5) Optional: fine-tune design by iterative simulations.

- 6) Optional: Evaluate  $V_{\text{carrier,dc}}(D)$  of design and determine carrier distortion-caused THD.

Step 3 is the main part of the method—since a constantsloping (carrier) signal is characterized by its second derivative being zero, forcing the second derivative of the carrier signal response to a PWM step to be zero should lead to a constantsloping (linear) carrier signal. Step 5 is typically the only tool available. It has been included since a number of approximations must be made when computing the step response of  $G_{\rm ctrl}(s)$ , resulting in a design that may be slightly suboptimal. Still, the proposed method saves considerable design time by reducing the number of iterative simulations required or removing these completely. Step 6 allows for a prediction of the minimum level of THD that can be expected from the optimized design, providing a second-source reference for comparison with simulated THD. The remaining parts of this section illustrate the proposed approach with the BPCM-controlled amplifier. Fig. 13 shows how the BPCM amplifier may be broken down to block diagram form, with relevant parameters summarized in Table II.

For the carrier generation, the contributions from two feedback paths (current estimate and output voltage) can be expressed by the following transfer functions:

$$G_{\mathrm{BPCM}}\left(s\right) \equiv \frac{V_{\mathrm{carrier,BPCM}}\left(s\right)}{V_{\mathrm{PWM}}\left(s\right)} = K_{\mathrm{cfb}} \times \frac{N_{L}}{1 + s\tau_{\mathrm{est}}}$$

$$\times \frac{1}{s^{2}LC + (L/R_{\mathrm{load}})s + 1} \times sL \times \frac{1 + sR_{\mathrm{load}}C}{R_{\mathrm{load}}}$$

$$G_{\mathrm{out}}\left(s\right) \equiv \frac{V_{\mathrm{carrier,out}}\left(s\right)}{V_{\mathrm{PWM}}\left(s\right)} = K_{\mathrm{vfb}} \times \frac{1}{s^{2}LC + (L/R_{\mathrm{load}})s + 1}$$

$$C28$$

TABLE II

PARAMETERS IN HYSTERETIC BPCM AMPLIFIER MODEL

| Load resistance                    | $R_{load}$  |

|------------------------------------|-------------|

| Output filter capacitance          | C           |

| Output filter inductance           | L           |

| Inductor sense winding ratio       | $N_L$       |

| Current estimator time constant    | $	au_{est}$ |

| Current feedback coefficient       | $K_{cfb}$   |

| Voltage feedback coefficient       | $K_{vfb}$   |

| Reference feed-forward coefficient | $K_{vff}$   |

From these transfer functions,  $G_{\text{ctrl}}(s)$  is found to be

$$G_{\text{ctrl}}(s) = \frac{V_{\text{carrier,BPCM}}(s) + V_{\text{carrier,out}}(s)}{V_{\text{PWM}}(s)}$$

$$= \frac{1}{s^2 L C + s(L/R_{\text{load}}) + 1}$$

$$\times \left[ K_{\text{cfb}} \frac{N_L}{1 + s\tau_{\text{est}}} \frac{sL(sR_{\text{load}}C + 1)}{R_{\text{load}}} + K_{\text{vfb}} \right]$$

(29)

Obviously, this transfer function cannot be reduced to a simple integrator provided that the poles of the output filter are complex and that  $\tau_{\rm est}<\infty$ , thus making the carrier optimization nontrivial as previously stated. With the output filter transfer function  $G_{\rm filter}(s)$  as a factor in  $G_{\rm ctrl}(s)$ , it makes sense to start by computing the step response of the output filter transfer function,  $G_{\rm filter}(s)$ , given as

$$G_{\text{filter}}(s) = \frac{1}{s^2 L C + s(L/R_{\text{load}}) + 1}$$

(30)

Assuming  $R_{\text{load}}$  to be very high (a "high-Q" approximation), this simplifies to

$$G_{\text{filter}}(s) \approx \frac{1}{s^2 L C + 1} = \frac{\sqrt{(1/LC)}}{s^2 + \sqrt{(1/LC)}}$$

(31)

Combining this with the Laplace transform of a step function (1/s) results in an expression that can be easily reverse Laplace transformed. The response of the output voltage to a PWM voltage step is hereby found to be

$$V_{\text{out,step}}(t) = \ell^{-1} \left\{ \frac{1}{s} \times \frac{\sqrt{(1/LC)}}{s^2 + \sqrt{(1/LC)}} \right\}$$

$$= 1 - \cos\left(\frac{1}{\sqrt{LC}}t\right)$$

(32)

The output voltage feedback component of the carrier signal thus exhibits the following step response:

$$V_{\text{carrier,out,step}}(t) = K_{\text{vfb}} \left[ 1 - \cos \left( \frac{1}{\sqrt{LC}} t \right) \right]$$

(33)

The current estimator output can be usefully reexpressed as

$$V_{\text{carrier,BPCM}}\left(s\right) = V_{\text{PWM}}\left(s\right) \left[1 - G_{\text{filter}}\left(s\right)\right] \frac{K_{\text{cfb}} N_L}{1 + s \tau_{\text{est}}}$$

(34)

Note that at the frequencies of interest for carrier shaping (frequencies in the range around the switching frequency),  $G_{\rm filter}(s)$  is negligible compared to 1 (the filter cutoff can be more than a decade away from the switching frequency), allowing this contribution to be neglected. Practically, this corresponds to assuming the output voltage to be constant, i.e., free from switching ripple. This is also intuitively reasonable since the ac component in the PWM signal will be much larger than the ripple voltage in any practical design. Therefore

$$V_{\text{carrier,BPCM}}(s) \approx V_{\text{PWM}}(s) K_{\text{cfb}} \times \frac{N_L}{1 + s\tau_{\text{est}}}$$

(35)

The response of the BPCM component of the carrier to a PWM step is hereby

$$V_{\text{carrier,BPCM,step}}(t) = \ell^{-1} \left\{ \frac{1}{s} \times K_{\text{cfb}} \times \frac{N_L}{1 + s\tau_{\text{est}}} \right\}$$

(36)

Again, doing a reverse Laplace transformation, this can be reexpressed as

$$V_{\text{carrier,BPCM,step}}(t) = K_{\text{cfb}} \times N_L \times \left[1 - e^{-\tau_{\text{est}}t}\right]$$

(37)

Hereby, it has been found that the carrier response to a PWM voltage step is approximately

$$V_{\text{carrier,step}}(t) \equiv \text{step} \{G_{\text{ctrl}}(s)\}$$

$$\approx K_{\text{vfb}} \left[ 1 - \cos \left( \frac{1}{\sqrt{LC}} t \right) \right] + K_{\text{cfb}} N_L \left[ 1 - e^{-\tau_{\text{est}} t} \right]$$

(38)

Now, the carrier signal slope can expressed as

$$\dot{V}_{\text{carrier,step}}(t) = \frac{K_{\text{vfb}}}{\sqrt{LC}} \sin\left(\frac{1}{\sqrt{LC}}t\right) + \frac{K_{\text{cfb}}N_L}{\tau_{\text{est}}} \times e^{-\tau_{\text{est}}t}$$

(39)

To ensure that this signal has a constant slope (at least over a brief time horizon following the step), the following optimality criterion is applied as per step 3) in the optimization method:

$$\ddot{V}_{\text{carrier,step}}(0) = 0 \tag{40}$$

Of course, it would be preferable to demand this for all time instances—but this cannot be solved for the BPCM control system since only an integrator has an ideal, constant-sloping step response and  $G_{\rm ctrl}(s)$  of the BPCM amplifier is indeed not an integrator. It should also be noted that this criterion is only useful in a controller structure that is actually capable of producing a triangular carrier signal. This will be the case if the inductor current, or a high-frequency estimate of this is fed back, since the inductor current is (almost) triangular, especially at high switching frequencies. Differentiating the carrier slope leads to

$$\ddot{V}_{\text{carrier,step}}(t) = \frac{K_{\text{vfb}}}{LC} \cos\left(\frac{1}{\sqrt{LC}}t\right) - \frac{K_{\text{cfb}}N_L}{\tau_{\text{est}}^2} \times e^{-\tau_{\text{est}}t}$$

(41)

Applying the optimality criterion results in the following simple expression that should be satisfied for an optimal design of the considered BPCM controller:

$$\frac{K_{\text{vfb}}}{LC} = \frac{K_{\text{cfb}} \times N_L}{\tau_{\text{crt}}^2} \tag{42}$$

TABLE III

PROTOTYPE BPCM AMPLIFIER DESIGN CONSTANTS

| Component   | Value      |

|-------------|------------|

| L           | 20.25μΗ    |

| C           | $2\mu F$   |

| $N_L$       | 2μF<br>2:9 |

| $	au_{est}$ | 3.3 µs     |

#### V. EXAMPLE PROTOTYPE AMPLIFIER DESIGN

To demonstrate the usefulness of the proposed optimization method, a practical amplifier design is considered. Initial design constants are summed up in Table III. The design considered is single-ended and based on the use of 100-V switching components and a 20.25- $\mu$ H dual-winding power inductor on a gapped RM10 ferrite core, combined with 2  $\mu$ F of output capacitance. For the typical speaker load of 4–8  $\Omega$ , this leads to a minimum filter Q of 1.26, not exactly infinite as approximated, but still underdamped. The current estimator time constant ( $\tau_{\rm est}$ ) was set at 3.3  $\mu$ s, realized with  $R_{\rm est}=100~\Omega$  and  $C_{\rm est}=33~\rm nF$ .

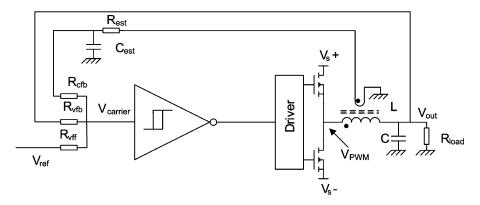

In order to increase the amplifier immunity to low-frequency supply voltage perturbations, as well as to help establish the carrier voltage dc operating point, the basic BPCM control system is augmented with a parallel integrating control loop as shown in Fig. 14. Equation (42) can still be used to predict the optimum feedback coefficients given that the integrator time constant is kept slow enough compared to the switching frequency, which ensures that the  $G_{\text{ctrl}}(s)$  step response is not significantly influenced within a time frame of one switching cycle. Note that the paralleling of proportional and integral output voltage feedback effectively provides PI output voltage feedback, hence the term BPCM + PI used for describing this topology. In the implementation shown, the comparator and the operational amplifier run off a single +5 V supply  $(V_{cc})$  generated from  $+V_s(34 \text{ V.})$ This is permissible since the operational amplifier has rail-torail inputs and the comparator inputs have dc offsets added via resistors to  $V_{cc}$ .

Taking into account the carrier voltage dc bias resistor  $R_{\rm bias}$ , the BPCM controller gain constants are given as

$$K_{\text{cfb}} = \frac{R_{\text{vfb}} ||R_{\text{vff}}||R_{\text{bias}}}{(R_{\text{vfb}}||R_{\text{vff}}||R_{\text{bias}}) + R_{\text{cfb}}}$$

$$K_{\text{vfb}} = \frac{R_{\text{cfb}} ||R_{\text{vff}}||R_{\text{bias}}}{(R_{\text{cfb}}||R_{\text{vff}}||R_{\text{bias}}) + R_{\text{vfb}}}$$

$$K_{\text{vff}} = \frac{R_{\text{vfb}} ||R_{\text{cfb}}||R_{\text{bias}}}{(R_{\text{vfb}}||R_{\text{cfb}}||R_{\text{bias}}) + R_{\text{vff}}}$$

(43)

From these expressions, the ratio  $K_{\rm vfb}/K_{\rm efb}$  can be derived as

$$\frac{K_{\rm vfb}}{K_{\rm cfb}} = \frac{R_{\rm cfb}}{R_{\rm vfb}} \tag{44}$$

Setting  $R_{\rm vfb}=10~{\rm k}\Omega$ , the analytically predicted optimal  $R_{\rm cfb}$  is 8.264 k $\Omega$ , which was rounded off to 8.2 k $\Omega$  in the prototype design. In order to get a closed-loop gain of 20 dB,  $R_{\rm vff}$  was set to 1 k $\Omega$ . The carrier dc bias point  $V_{\rm carrier,bias}$  was

set using  $R_{\rm bias}$  from the following expression:

$$V_{\text{carrier,bias}} = V_{\text{cc}} \times \frac{R_{\text{vfb}}||R_{\text{cfb}}||R_{\text{vff}}}{R_{\text{vfb}}||R_{\text{cfb}}||R_{\text{vff}} + R_{\text{bias}}}$$

(45)

The choice of  $R_{\rm bias}=3.3~{\rm k}\Omega$  thus lifts the carrier dc operating point to 1 V, to ensure that the carrier stays within the common-mode input range of the comparator. The prototype design gain coefficients are summed up in Table IV along with the true optimum coefficients and two sets of suboptimal coefficients. The suboptimal designs represent the lumped effect of component tolerances that are likely to be significant in the output filter components. Although  $K_{\rm cfb}$  is physically determined only by resistors, deviations in L and C require proportional changes in  $K_{\rm cfb}$  for optimality to be preserved, so tolerances on L and C can be directly mapped to a tolerance on  $K_{\rm cfb}$  as far as carrier distortion is concerned. Practically, the suboptimal designs were implemented by changing  $R_{\rm cfb}$  to  $10~{\rm k}\Omega$  and  $6.2~{\rm k}\Omega$ , respectively.

With the prototype design gain coefficients, the carrier signal unity-step response slope is found to be

$$\dot{V}_{\rm carrier, step} \left( 0 \right) = \frac{K_{\rm cfb} \times N_L}{\tau_{\rm est}} \approx 5.39 \,\mathrm{mV}/\mu\mathrm{s}$$

(46)

With a nominal supply voltage  $V_s$  of 34 V, this means that a 34 V step is applied to  $G_{\rm ctrl}(s)$  for D=0.5, leading to a carrier signal slope of 183 mV/ $\mu$ s. This means that the K [23] of the design is

$$K \equiv 2 \times \frac{dV_{\text{carrier}}}{dt} \bigg|_{D=0.5} = 2V_s \times \frac{K_{\text{cfb}} N_L}{\tau_{\text{est}}} \approx 0.366 \,\text{V}/\mu\text{s}$$

(47)

where K can also be found as follows [23]:

$$K = 2V_s \times \text{step} \left\{ \lim_{s \to \infty} G_{\text{ctrl}}(s) \right\}$$

(48)

Since the switching frequency of a triangular-carrier hysteretic control system is a parabolic function of duty cycle [16], [33], [35], [37] given quite precisely by

$$f_{\rm sw}(D) = \frac{D(1-D)}{2(V_{\rm hyst}/K) + t_d}$$

(49)

then, for a nominal (D=0.5) switching frequency  $f_{\rm sw,nom}$  of 350 kHz, assuming 100 ns comparator/power stage delay  $t_d$ , the hysteresis level  $V_{\rm hvst}$  should be

$$V_{\rm hyst} = \frac{K}{2} \left[ \frac{1}{4f_{\rm sw,nom}} - t_d \right] \approx 110 \,\mathrm{mV}$$

(50)

Note that the hysteresis window of the comparator in this case is still defined as  $\pm V_{\rm hyst}$ . The desired hysteresis window is easily implemented by proper choice of the resistors  $(R_{h1}-R_{h4})$  attached to the noninverting comparator input. The prototype design used  $R_{h1}=33~{\rm k}\Omega,\,R_{h2}=3.3~{\rm k}\Omega,\,R_{h3}=22~{\rm k}\Omega,$  and  $R_{h4}=3.3~{\rm k}\Omega.$

#### VI. SIMULATED/CALCULATED RESULTS

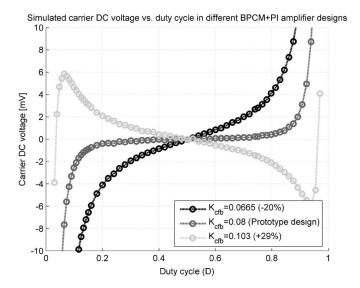

The accuracy of the proposed carrier distortion optimization method and the sensitivity of the optimum to parameter variations were examined by PSpice simulation and the results are

Fig. 14. Hysteretic SO BPCM + PI controlled single-ended amplifier with single-supply ( $V_{cc}$ ) control circuitry.

${\it TABLE\ IV}$  Optimal and Implemented BPCM Amplifier Design Gain Coefficients

| Parameter | Optimal | Prototype      | Sub-optimal design | Sub-optimal design |

|-----------|---------|----------------|--------------------|--------------------|

|           | design  | design         | I ("-20%")         | II ("+29%")        |

| $K_{cfb}$ | 0.0800  | 0.0800         | 0.0665 (-20%)      | 0.103 (+29%)       |

| $K_{vfb}$ | 0.0661  | 0.0656 (-0.7%) | 0.0665 (+0.7%)     | 0.0639 (-3.4%)     |

| $K_{vff}$ | 0.661   | 0.656          | 0.665              | 0.639              |

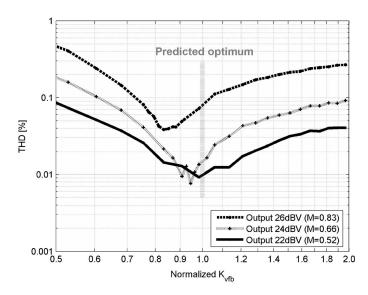

Fig. 15. Simulated THD (3rd + 5th harmonics only) with  $K_{\rm vfb}$  values around the predicted optimum.

shown in Fig. 15. A simulation model of the found optimum BPCM + PI design was implemented, with the switching components made ideal so that only carrier distortion was generated. The output THD of the BPCM + PI amplifier simulation model was evaluated for three different amplitudes of 5-kHz sine wave output. In each case, voltage feedback coefficient  $K_{\rm vfb}$  was varied from 0.5 to 2 times ( $\pm 6$  dB) its predicted optimum value. As can be seen, the proposed method succeeds in finding the  $K_{\rm vfb}$  that leads to minimal THD for low output levels. The optimal  $K_{\rm vfb}$  is seen to vary with output level, however, with a lower  $K_{\rm vfb}$  (or a higher  $K_{\rm cfb}$ ) being preferable at high output levels.

This suggests that a true global optimum feedback coefficient weighting does not exist and that each output level has its own optimum  $K_{\rm cfb}/K_{\rm vfb}$ . The amount of carrier distortion generated is seen to be relatively sensitive to component tolerances; optimizing the amplifier for 24 dBV output by choosing a  $K_{\text{vfb}}$ of 0.95,  $\pm 10\%$   $K_{\rm vfb}$  variation is enough to cause a THD increase from 0.01% to 0.02% at 24 dBV output. For  $\pm 20\%$ , the THD potentially increases to 0.03%. Still, these numbers are far lower than what would probably be obtained by not paying attention to carrier distortion; for all three output levels, THD varies by a factor of around 10 for relatively modest  $K_{\text{vfb}}$ variations of  $\pm 6$  dB around the predicted optimum. An interesting point to note is that even though the amplifier loop gain increases with  $K_{\rm vfb}$ , overall distortion also increases when  $K_{\rm vfb}$ is too high, showing that loop gain maximization alone is not necessarily the best strategy for linearizing SO class-D amplifiers. When combined with minimization of carrier distortion, however, maximized loop gain is still an advantage. This is because 1) high loop gain reduces the amplifier's sensitivity to other disturbances than carrier distortion and 2) loop gain still has an effect on carrier distortion. As seen from (24), designing for a high-gain  $G_{\text{ctrl}}(s)$  in the audio band directly reduces sensitivity to carrier distortion. There is a complication associated with this, however, since increasing the magnitude of  $G_{\rm ctrl}(s)$  also requires an increase in the amount of hysteresis needed for a given switching frequency thereby also increasing the amount of carrier dc variation by the same amount. To maximize loop gain while maintaining carrier distortion, it is therefore necessary to increase the low-frequency magnitude of  $G_{\text{ctrl}}(s)$  while still ensuring a linear step response and not increasing K as seen from (48) and (49). A difficult exercise, this is at least made somewhat easier by the avail-

Fig. 16. Simulated carrier dc voltage versus steady-state duty cycle for prototype and suboptimal BPCM + PI amplifier designs. Implemented design can be expected to be very linear for duty cycles from 0.2 to 0.8 (corresponding to an M < 0.6 or 23  ${\rm dBV_{rm\,s}}$  sine wave from  $V_s = 34~{\rm V}$ ).

ability of the proposed method for optimizing the  $G_{\mathrm{ctrl}}(s)$  step response.

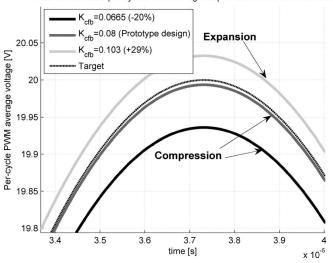

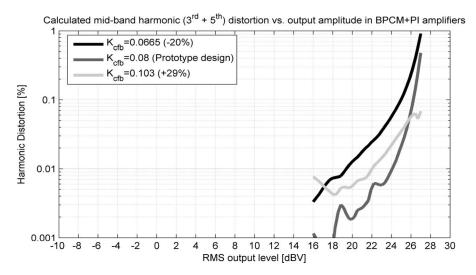

In order to further quantify the carrier distortion mechanism, the methodology already used for THD calculation on the simple AIM controller was adapted for the BPCM + PI system. Due to the complexity of  $G_{\text{ctrl}}(s)$  of the BPCM + PI controller, simulation, rather than analysis, was used to determine  $V_{\text{carrier,dc}}(D)$ . The control loop time delay  $t_d$  was set to zero to avoid masking of the nonlinear, dc variation caused by any nonintegrator  $G_{\rm ctrl}(s)$ , by the linear, delay-induced variation [21], [35]. The results are shown in Fig. 16 for the nearly-optimal implemented design as well as for the suboptimal designs. It is generally apparent that the relatively slight variation in  $K_{\rm cfb}$  causes the carrier average to exhibit significantly more nonlinear variation with duty cycle; hence, the THD can also be expected to increase. As shown in Fig. 17, the generated carrier distortion is expansive (like in the AIM) when the current feedback component is too high since this leads to an overemphasis of the exponential carrier component. Conversely, the carrier distortion instead becomes compressive when the output feedback component is too high.

For THD calculations, the data from Fig. 16 was used (interpolating between data points) to calculate the amplifier response to a sine wave. The sine wave was assumed to have a frequency above the PI corner frequency (i.e., integral output voltage feedback is assumed negligible compared to proportional feedback), allowing (29) to be used for  $G_{\rm ctrl}(s)$ , which was then assumed to be flat within the audio band. This is justified by the fact that the inductor current signal is effectively high-pass filtered (see (29)) by the current estimator, so that the output voltage feedback via  $K_{\rm vfb}$  dominates at low frequencies. With the low-frequency approximation  $G_{\rm ctrl}(s) = K_{\rm vfb}$ , the method used for the THD calculation in the AIM was applicable. Results for the prototype and suboptimal designs are

Peak of calculated per-cycle PWM average response to sine wave reference

Fig. 17. Calculated sine wave responses of optimal and suboptimal amplifier implementations at  $20\,V_{\rm peak}\,(23\,{\rm dBV_{rms}}$  or  $M=0.6, D_{\rm max}=0.8)$  output level. The optimized design is visibly more ideal than the suboptimal designs.

shown in Fig. 18, where it is confirmed that THD performance is quite sensitive to the carrier composition. For example, inspecting Fig. 18, an amplifier rated for 0.02% maximum THD would have its rated output power reduced by a factor of two (3 dB) with a  $K_{\rm cfb}$  tolerance of 20%. As will be demonstrated in the experimental section, this is a reasonable claim since carrier distortion is shown to be the dominant nonlinearity at high output levels. For the optimal design, THD is predicted to stay at a very low level (less than 0.01%) up to 24 dBV $_{\rm rms}$  output level, where a sharp increase is observed as the carrier average voltage deviates strongly from zero at the peaks of the sine wave.

#### VII. EXPERIMENTAL RESULTS

The BPCM + PI amplifier in Fig. 14 was implemented on a four-layer printed circuit board (PCB) with one-sided component placement as shown in Fig. 19. Small IRF6645 (28 m $\Omega$ , 100 V, 14 nC gate charge) MOSFETs were used together with ample dead time (around 15 ns) to allow cooling via the PCB. A standard HIP2100 with input-side residual current device networks for setting the dead time was used for the MOSFET driver along with a discretely built phase-split/level-shift circuit for interfacing with the LMV7219 comparator.

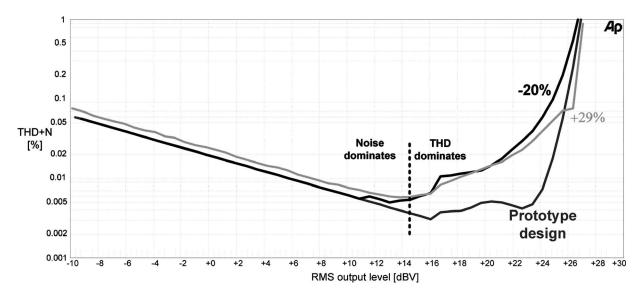

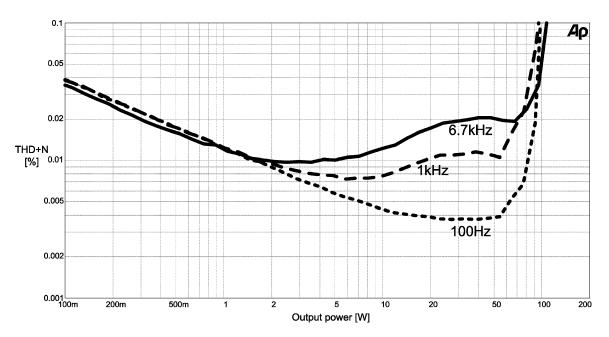

THD + N measurements were performed using an Audio Precision System 2 with 22 kHz bandwidth without the Aux-25 prefilter. The raw distortion and noise generated by the control system are assessable from the no-load THD + N versus output level measurements in Fig. 20. These measured results are directly comparable to the calculated ones in Fig. 18, since the third and fifth harmonics were found (via the fast fourier transform function) to dominate the generated THD. To ensure a flat  $G_{\rm ctrl}(s)$  as assumed for the calculations in Fig. 18,  $C_{PI}$  was temporarily doubled to 100 nF, effectively halving the integral feedback term. The measurements confirm

Fig. 18. Calculated THD (3rd + 5th harmonics only) caused by carrier distortion in optimum and implemented prototype BPCM + PI amplifier designs with variable  $K_{\rm cfb}$ . For the implemented design, no-load THD is expected to be less than 0.02% below  $25~{\rm dBV_{rms}}$  (M=0.74 or  $D_{\rm max}=0.87$  output level.

Fig. 19. Prototype hysteretic BPCM + PI amplifier PCB.

that even modest -20% or +29% deviation from the optimal carrier composition creates significant THD at high output levels. Some deviation is evident below 25 dBV (particularly in the "+29%" implementation), but agreement is very good above this level.

Given that the optimized prototype design produces higher THD at high levels than the "+29%" design, it is of course debatable whether or not it is in fact optimal. However, by defining the optimal design as the one that provides the lowest THD at low output levels, optimality has been achieved. As also predicted by simulations in Fig. 15, linearity can be increased at high output levels by increasing  $K_{\rm cfb}$  (or lowering  $K_{\rm vfb}$ ) thereby sacrificing low-level performance Such tradeoffs are best implemented following a precise specification of the desired THD and output power performance of the amplifier.

The noise generated by the BPCM + PI amplifier is 240  $\mu$ V since THD + N is 0.02% at 0 dBV<sub>rms</sub> output level where noise is dominant (as seen by the 6 dB/octave slope of the THD +

N curve). This is a rather high number that could probably be reduced by the use of a slower comparator. This is because [29] the comparator integrates the circuit noise (generated by resistors and active components) during the time when the switching decision is made, and slower comparators have a longer decision "window," effectively averaging the applied noise for a longer period.

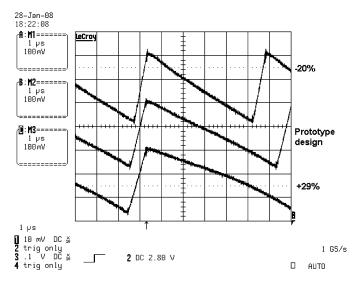

The triangularity of the carrier signal in the three different configurations is assessable from the measurements in Fig. 21. Visually, the optimized carrier signal appears the most triangular, as also expected for the design with the lowest THD.

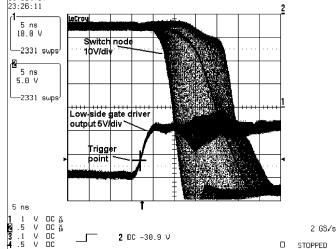

The performance of the implemented power switching stage was examined using the "analog persist" function on a Lecroy WaveRunner oscilloscope. This allowed observation of the total spread in variation of the switch node behavior with load current. For a sinusoidal output current of  $\pm 6.25 A$ , a 15 ns spread in transition delay time was observed as seen in Fig. 22. This is a result of the use of 15 ns dead time and a ripple current of 2.4  $A_{\rm pp}$ , leading to the power stage operating in both the zero current switching (ZCS) mode (for output currents less than  $\pm 1.2 A$ , given enough dead time) and hard-switched mode (for higher output currents).

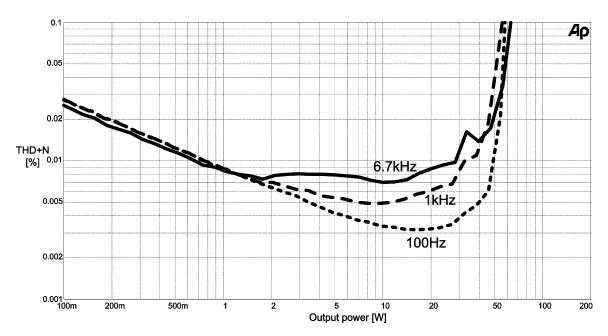

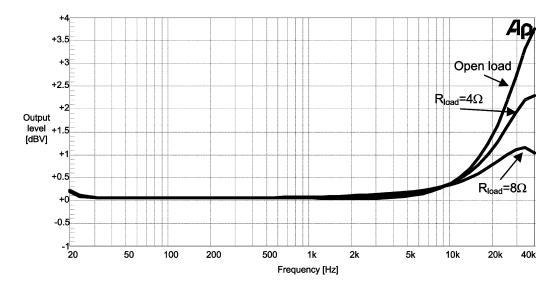

The THD + N performance of the prototype design with the usual 4  $\Omega$  and 8  $\Omega$  loads and three commonly used test frequencies (100 Hz, 1 kHz and 6.7 kHz) is indicated in the measurements in Figs. 23 and 24. The maximum frequency of 6.7 kHz is often used for switch-mode amplifiers since the third harmonic distortion of higher frequencies falls outside of the commonly used 20–22 kHz measurement bandwidths. Due to the dominance of the integral voltage feedback term at low frequencies, the 100 Hz THD figures are very low. The use of higher-order integral low-frequency feedback allows extremely low THD to be obtained at low frequencies [5], [6], [9], but usually does not help at higher frequencies since the loop gain inevitably has to roll off. Additionally, it is obvious that taking extra integral feedback too far will result in an increase in carrier

Fig. 20. Unloaded prototype amplifier THD + N versus output level (0  $dBV = 1~V_{rms}$ ) at 1 kHz with optimal and suboptimal  $K_{cfb}$ , for comparison with Fig. 18. THD of the optimized design is less than 0.02% up to 25  $dBV_{rms}$ . Suboptimal designs have higher THD as expected.

31-0ct-07

Fig. 21. Prototype carrier waveforms for D=0.88 (peak of M=0.76 sine wave.) Optimized design runs at 150 kHz, indicating an idle switching frequency of 350 kHz. The optimized carrier visually appears to be the most triangular, as also targeted by the proposed optimization method.

Fig. 22. Variation of switching behavior of prototype, measured using the "analog persist" function. Output is an 80 W (25  $V_{\rm peak}$ ) sine wave into 4  $\Omega$  and there is evidently a switching transition point variation of around 15 ns due to the combination of dead time and variation in load current.

distortion, since a higher-than-first-order integral of a PWM signal is not triangular.

Overall, the presented design can be rated at 80/45 W with less than 0.03% THD + N for 4/8  $\Omega$ , which is a very decent result for a design done purely by analysis. As indicated by Fig. 20 and the analysis performed, it would in fact be quite difficult to come up with a significantly better design given the BPCM feedback topology and the power stage used. This statement is backed up by results from prior art, which are summarized in Table V. Control schemes, power stage configurations, and switching frequencies are also listed for reference. BTL refers to "Bridge Tied Load," i.e., the full-bridge configuration while SE refers to "single-ended." Other very noteworthy results exist [6], [11], but details are inadequate for comparative purposes. It should of course be noted that the power stage components

used in the presented paper are nearly state of the art with discrete components and that this of course impacts the results positively. However, it was shown in Figs. 18 and 20 that carrier distortion generates exactly 0.02-0.03% THD for M=0.75, so it is the carrier distortion that dictates the final THD specification of the design. Hence, the presented optimization method has been shown to be instrumental in obtaining the THD results in Figs. 23 and 24. This was indeed also the conclusion in [5] for the discrete-time-based optimization method for fixed-frequency PWM-based amplifiers. It is expected by the authors that future publications will demonstrate a clear link between the proposed averaging and time-domain-based view of "carrier distortion" and the discrete-time and frequency-domain-based view of "aliasing distortion" [5]. The presented averaging approach is principally also applicable for THD prediction in phase-shift

Fig. 23. Optimized prototype amplifier THD + N versus output power with a 4  $\Omega$  load. Worst case (below 80 W or M=0.75) THD + N is very respectable at 0.03% at 6.7 kHz.

Fig. 24. Optimized prototype amplifier THD + N versus output power with an 8  $\Omega$  load. Distortion stays below 4.5 W, corresponding to M=0.79.

SO control systems [6]–[8], where the carrier signal is sinusoidal and oscillation is induced by raw phase shift in the loop filter  $G_{\rm ctrl}(s)$  rather than by comparator hysteresis. The carrier average in these systems will also potentially exhibit nonlinear variation with duty cycle. However, averaging the carrier signal in such systems is nontrivial since oscillation is only possible if the loop filters are second-order or higher [7] or comparator time delay is added to the analysis.

Finally, one important amplifier parameter that has not yet been considered, namely the frequency response, is examined in Fig. 25. For the typical 4–8  $\Omega$  load, the frequency response is fortunately flat within 1.2 dB below 20 kHz. Prefiltering could be used to straighten this out if desired. Computation of the frequency response for verification is easily done using the classical sliding mode approximation, but falls outside the scope of this paper.

| Reference | THD+N, $4\Omega$ , | THD+N, 8Ω,     | Control topology | Power stage,             |

|-----------|--------------------|----------------|------------------|--------------------------|

|           | M=0.75, 6.7kHz     | M=0.75, 6.7kHz |                  | supply voltage, $f_{sw}$ |

| [5]       | ?                  | 0.018%         | Fixed-freq. PWM  | BTL, 55V, 350kHz         |

|           |                    |                | + "MAE filter"   |                          |

| [9]       | 0.04%              | ?              | Hysteretic SO,   | SE, +/-40V,              |

|           |                    |                | "GLIM"           | 350kHz                   |

| [38]      | ?                  | 0.05%          | One-cycle        | BTL, 54V, 250kHz         |

| This work | 0.03%              | 0.02%          | Hysteretic SO,   | SE, +/-34V,              |

|           |                    |                | BPCM+PI          | 350kHz                   |

TABLE V REPRESENTATIVE PRIOR ART THD + N RESULTS FOR COMPARISON WITH PRESENTED STUDY

Fig. 25. Measured frequency responses of prototype amplifier. With a typical speaker load (4–8  $\Omega$ ), response is flat within 1.2 dB over the audio band (20 Hz to 20 kHz.).

#### VIII. CONCLUSION

An approach for understanding, evaluating, and minimizing the intrinsic distortion generated by hysteretic SO controllers applied to buck-type power converters has been presented. The term "carrier distortion" has been used for this intrinsic distortion phenomenon, referring to prior art. Carrier distortion is mainly an issue of concern in switch-mode ac power amplifiers where the signal bandwidth is high compared to the switching frequency and where fast, high-quality switching components are used. In such cases, distortion generated by imperfect switching is low while loop gain of the control system is limited at high signal frequencies, making carrier distortion the dominant nonlinearity in the power amplifier at high output levels. Class-D audio power amplifiers are an obvious application for the presented analysis, but reducing harmonic distortion of switchmode power amplifiers is also of interest in a variety of other niche applications. Examples include xDSL drivers, envelopetracking power supplies, and ac transmission line filters.

In agreement with prior art statements, it has been found that the carrier signal (a.k.a. sliding variable) should be made triangular by proper design of the control loop(s) to minimize this distortion. This directly resulted from an averaging analysis of the steady-state hysteretic comparator input/output waveforms. It was shown that even an amplifier with a perfect power stage supplied with a perfect dc supply voltage can in fact pro-

duce significant harmonic distortion due to the carrier distortion mechanism. Based on the desire for a triangular carrier signal for minimizing carrier distortion, a simple s-domain analytical approach was proposed and demonstrated on a nontrivial control topology. An optimized prototype amplifier design was implemented and verified against modeled results. The generated harmonic distortion was found to be well described by the proposed methodology as well as quite sensitive to parameter variation. The harmonic distortion results achieved with the prototype design were at state-of-the-art level, verifying the validity and usefulness of the presented approach.

#### REFERENCES

- [1] B. Putzeys, "Digital audio's final frontier," *IEEE Spectr.*, vol. 40, no. 3, pp. 34–41, Mar. 2003.

- [2] I. D. Mosely, P. H. Mellor, and C. M. Bingham, "Effect of dead time on harmonic distortion in class-D audio power amplifiers," *Electron. Lett.*, vol. 35, no. 5, pp. 950–952, Jun. 1999.

- [3] F. Koeslag, H. du T. Mouton, H. J. Beukes, and P. Midya, "A detailed analysis of the effect of dead time on harmonic distortion in a class D audio power amplifier," in *Proc. IEEE AFRICON 2007*, Oct., pp. 1–7.

- [4] F. Nyboe, C. Kaya, L. Risbo, and P. Andreani, "A 240 W monolithic class-D audio amplifier output stage," in *Proc. IEEE Int. Solid State Circuits Conf. 2006*, Feb., pp. 1346–1355.

- [5] L. Risbo and C. Neesgaard, "PWM amplifier control loops with minimum aliasing distortion," presented at the AES 120th Conv., Paris, France, May 2006, no. 6693.

- [6] B. Putzeys, "Simple self oscillating class D amplifier with full output filter control," presented at the AES 118th Conv., Barcelona, Spain, May 2005, pp. 6453.

- [7] T. Piessens and M. S. J. Steyaert, "Behavioral analysis of self-oscillating class D line drivers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 4, pp. 706–714, Apr. 2005.

- [8] S. Poulsen and M. A. E. Andersen, "Self oscillating PWM modulators, a topological comparison," presented at the IEEE Power Modulator Conf., San Francisco, CA, 2004, Jul., pp. 403–407.

- [9] S. Poulsen and M. A. E. Andersen, "Simple PWM modulator with excellent dynamic behaviour," in *Proc. Appl. Power Electron. Conf.* 2004, Anaheim, CA, Feb., pp. 486–492.

- [10] M. C. W. Høyerby and M. A. E. Andersen, "Derivation and analysis of a low-cost, high-performance BPCM control scheme for class-D audio power amplifiers," in *Proc.27th AES Conf.*, Hillerød, Denmark, Sep. 2005, pp. 101–107.

- [11] P. Van Der Hulst, A. Veltman, and R. Groenberg, "An asynchronous switching high-end power amplifier," presented at the 112th AES Conv., Munich. Germany. May 2002.

- [12] P. Midya et al., "Tracking power converter for supply modulation of RF power amplifiers," in Proc. Power Electron. Spec. Conf. 2001, Jun., vol. 3, pp. 1540–1545.

- [13] J. Matas, L.-G. de Vicuña, J. Miret, J. M. Guerro, and M. Castilla, "Feed-back linearization of a single-phase active power filter via sliding mode control," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 116–125, Jan. 2008

- [14] B. Mwinyiwiwa, Z. Wolanski, and B.-T. Ooi, "High power switch mode linear amplifiers for flexible AC transmission system," *IEEE Trans. Power Del.*, vol. 11, no. 4, pp. 1993–1998, Oct. 1996.

- [15] Elbo GmbH; "Self-oscillating digital amplifier with delay-free digital negative feedback, without push-pull distortions," German Patent DE19838765, May 2000.

- [16] M. C. W. Høyerby and M. A. E. Andersen, "Accurate sliding-mode control system modeling for buck converters," in *Proc. Eur. Conf. Power Electron. Appl. (EPE 2007)*, Aalborg, Denmark, Sep., pp. 1–10.

- [17] M. A. Rojas-Gonzales and E. Sanchez-Sinencio, "Design of a class D audio amplifier IC using sliding mode control and negative feedback," *IEEE Trans. Consum. Electron.*, vol. 53, no. 2, pp. 609–617, May 2007.

- [18] A. Veltmann and H. J. Jacobus, "Amplifier circuit having output filter capacitance current feedback," US patent 6 552 606, Apr. 2003.

- [19] A. F. Rozman and J. J. Boylan, "Band pass current control," in *Proc. Appl. Power Electron. Conf. 1994*, Orlando, FL, Feb., pp. 631–637.

- [20] M. Castilla, G. de Vicuna, J. M. Guerrero, J. Miret, and N. Berbel, "Simple low-cost hysteretic controller for single-phase synchronous buck converters," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1232–1241, Jul. 2007.

- [21] K. D. T. Ngo, S. K. Mishra, and M. Walters, "Synthetic-ripple modulator for synchronous buck converter," *IEEE Power Electron. Lett.*, vol. 3, no. 4, pp. 148–151, Dec. 2005.

- [22] C.-H. Tso and J.-C. Wu, "A ripple controlled buck regulator with fixed output frequency," *IEEE Power Electron. Lett.*, vol. 1, no. 3, pp. 61–63, Sep. 2003.

- [23] M. C. W. Høyerby and M. A. E. Andersen, "Ultrafast tracking power supply with fourth-order output filter and fixed-frequency hysteretic control," *IEEE Trans. Power Electron.*, vol. 23, no. 5, pp. 2387–2398, 2008.

- [24] S.-C. Tan, Y. M. Lai, C. K. Tse, and M. K. H. Cheung, "Adaptive feed-forward and feedback control schemes for sliding mode controlled power converters," *IEEE Trans. Power Electron.*, vol. 21, no. 1, pp. 182–192, Jan. 2006.

- [25] L. G. Shiau and J. L. Lin, "Direct and indirect SMC control schemes for DC–DC switching converters," in *Proc. SICE* 1997, Jul., pp. 1289–1294

- [26] M. Ahmed, M. Kuisna, K. Tolsa, and P. Silventoinen, "Implementing sliding mode control for buck converter," in *Proc. IEEE Power Electron.* Spec. Conf. 2003, Jun., vol. 2, no. 3, pp. 634–637.

- [27] G. Eirea and S. R. Sanders, "Phase current unbalance estimation in multiphase buck converters," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 137–143, Jan. 2008.

- [28] F. F. Judd and H. Wilhart, "Self-oscillating regulated DC-to-DC converter," *IEEE Trans. Ind. Appl.*, vol. IA-8, no. 6, pp. 684–689, Dec. 1972.

- [29] L. Risbo, "Discrete-time modeling of continuous-time pulse-width modulator loops," in *Proc. 27th AES Conf.*, Hillerød, Denmark, Sep. 2005, pp. 108–117.

- [30] J. Olivier, J. Le Claire, and L. Loron, "An efficient switching frequency limitation process applied to a hugh dynamic voltage supply," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 153–162, Jan. 2008.

- [31] V. Utkin, J. Guldner, and J. Shi, Sliding Model Control in Electromechanical Systems. Boca Raton, FL: CRC, Apr. 1999.

- [32] P. Mattavelli, L. Rossetto, and G. Spiazzi, "Small-signal analysis of DC–DC converters with sliding mode control," *IEEE Trans. Power Electron.*, vol. 12, no. 1, pp. 96–102, Jan. 1997.

- [33] G. W. Wester, "Describing-function analysis of a ripple regulator with slew-rate limits and time delays," in *Proc. Power Electron. Spec. Conf.* 1990, Jun., pp. 341–346.

- [34] T. H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, 2nd ed. Cambridge, MA: Cambridge Univ. Press, Mar. 2004.

- [35] M. C. W. Høyerby and M. A. E. Andersen, "A small-signal model of the hysteretic comparator in linear-carrier self-oscillating switch-mode controllers," presented at the Nordic Workshop Power Ind. Electron. (ORPIE 2006), Lund, Sweden, Jun.

- [36] C. Song and J. L. Niles, "Accuracy analysis of multiple-phase hysteretic current-mode DC–DC converters," in *Proc. IEEE Power Electron. Spec. Conf. 2007*, Jul., pp. 396–400.

- [37] M. Castilla, G. de Vicuna, J. M. Guerrero, J. Matas, and J. Miret, "Design of voltage-mode hysteretic controllers for synchronous buck converters supplying microprocessor loads," in *Proc. Inst. Electr. Eng. Proc. Electr. Power Appl.*, Sep. 2005, vol. 152, no. 5, pp. 1171–1178.

- [38] K. M. Smith, Z. Lai, and K. M. Smedley, "A new PWM controller with one-cycle response," *IEEE Trans. Power Electron.*, vol. 14, no. 1, pp. 142– 150, Jan. 1999.

Mikkel C. W. Høyerby (M'06) recieved the Master's degree in electrical engineering from the Technical University of Denmark, Lyngby, Denmark, in 2004. He is currently working toward the Ph.D. degree at Motorola Denmark, Glostrup, Denmark.

From 2004 to 2005, he was a Research Assistant at the Technical University of Denmark, working on high-bandwidth dc-dc converters, class-D audio power amplifiers, and control IC design. Since the start of 2006, he has been engaged in research on envelope-tracking power supplies for RF power am-

plifiers. He is the holder of three pending patents in the field of self-oscillating control of dc-dc converters.

Michael A. E. Andersen (S'88–M'91) was born in Aalborg, Denmark. He received the M.Sc.E.E. and Ph.D. degrees from the Technical University of Denmark, Lyngby, Denmark, in 1987 and 1990, respectively, both in power electronics.

Since 1990, he has been with the Department of Electrical Engineering, Technical University of Denmark, initially as an Assistant Professor, Associate Professor in 1994, and since 2003, a Professor in power electronics. He is the Head of the Danish Ph.D. Research School in Electrical Energy Systems

"EnergyLabDK" since 2006. He is the author or coauthor of more than 70 papers. His current research interests include switch-mode power supplies, piezoelectric transformers, power factor correction, and switch-mode audio power amplifiers.

Prof. Andersen is a member of Audio Engineering Society (AES) and European Power Electronics and Drives Association (EPE). He was the recipient of numerous awards including the A. R. Angelo's Grant in 1990, the P. Gorm Petersen's Memorial Grant in 1991, the Best Poster Prize at UPEC 1991, the Danish AEG Elektronprisen in 2004, and the Technical University of Denmark Innovation Prize in 2006.