Downloaded from orbit.dtu.dk on: Apr 29, 2024

**DTU Library**

#### **4G Mobile Networks**

An Analysis of Spectrum Allocation, Software Radio Architectures and Interfacing Technology

Lanzani, Christian Fabio Alessandro

Publication date:

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Lanzani, C. F. A. (2011). 4G Mobile Networks: An Analysis of Spectrum Allocation, Software Radio Architectures and Interfacing Technology. Technical University of Denmark.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## 4G Mobile Networks:

# An Analysis of Spectrum Allocation, Software Radio Architectures and Interfacing Technology

Christian F. A. Lanzani

Industrial Ph. D. Thesis

A thesis submitted for the degree of

Industrial Doctor of Philosophy of the Technical University of Denmark,

Department of Photonics Engineering, Kgs. Lyngby, Denmark

in collaboration with the Ministry of Technology of Denmark and

in collaboration with Radiocomp ApS, Hilleroed Denmark.

Lanzani, Christian F. A.

DTU Student number: s042920 (chrla)

Industrial Ph. D. Thesis

KaleidaGraph version 4.1.1.

4G Mobile Networks: An Analysis of Spectrum Allocation, Software Radio Architectures and Interfacing

Technology. Includes bibliographical references.

Copyright © 2010 of Christian F. A. Lanzani, except where otherwise stated. All rights reserved. No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without permission in writing from the Author. Printed and bound in DTU, Kgs. Lyngby. This thesis was written with PDFTEX on an Apple MacBook Pro 13" running Mac OS X version 10.6.4. The LATEX editor is Textmate 1.5.9. All figures were made by the Author using OmniGraffle version 5.2.2 Professional and printed as high quality PDF vector images. All plots and graphs were made by the Author using

I hereby declare that this submission is my own work and that, to the best of my knowledge and belief, it contains no material previously published or written by another person nor material which to a substantial extent has been accepted for the award of any other degree or diploma of the university or other institute of higher learning, except where due acknowledgment has been made in the text.

Christian F. A. Lanzani

Hilleroed, Denmark

October 31<sup>th</sup>, 2010

Coursein ft.

| Dedicato | alla mia spi | lendida nonna . | Lina ci sara | $i\ sempre$ |

|----------|--------------|-----------------|--------------|-------------|

|          |              |                 |              |             |

|          |              |                 |              |             |

|          |              |                 |              |             |

|          |              |                 |              |             |

## Acknowledgements

I would like to take this opportunity to thank all the people who have been supporting me in various ways along this path. My gratitude goes firstly to my academic supervisors in DTU Fotonik, Prof. Lars Dittmann and Prof. Michael Berger. Secondly I would like to thank my supervisors in Radiocomp Aps, Dr. Morten Hoegdal and Mr. Thomas Noergaard for their patience, support and indeed for the invaluable opportunity given. Secondly I would like to express sincere appreciation and gratitude to Dr. Soren Danielsen for the great support and experience of working together with. Thanks to Dr. Matteo R. Bosisio for the ride, and what a ride.

I owe great thanks to Altera Corporation, and especially to Mrs. Lena Engdahl for her precious and invaluable support to the University with free components, licenses and exceptional support that cannot be matched elsewhere. I wish to thank the industry forum of OBSAI for allowing me actively contributing to the standardization activities in the past 4 years. In particular I would like to thank Mr. Tero Mustala, Dr. Peter Kenington and Dr. Timo Viero for their support. In addition many thanks to Mr. Gerry Leavey and Mr. Pertti Krans for their tips and valuable technical insights. My appreciation goes to all Radiocomp staff for their's experience and system level support, especially Dr. Nastaran Bejhou, Mr. Kim Soerensen and Mr. Georgios Kardaras. Thanks to Mr. Claus Hetting and Dr. Marco Carbone for the support in the final stage of this project.

Thanks to my family, my brother Marco and all my close friends that have been supporting and tolerating me during all these years. I owe them a lot. Finally, thanks to my fiancee' Mari for her patience, love and support over the years.

Christian F. A. Lanzani

Nouver ft.

Hilleroed, Denmark October  $31^{th}$ , 2010

## Abstract

This thesis has investigated 4G radio access networks covering spectrum allocation methodologies, eNB software radios and architectures including interfacing performance aspects relevant for IMT-Advanced requirements.

Dynamic spectrum allocation is an alternative to fixed allocation methodologies. Although 100 MHz of spectrum per antenna will require frequencies re-allocation - initial rollouts with bandwidths of 40 MHz leveraging Carrier Aggregation and MIMO antenna techniques are foreseen within a 3-years time horizon. MultiRAN and high-power eNB configurations are expected to operate in the 1.7-2.6 GHz bands. Likewise, SingleRAN low-power configurations will operate in the 2.6-3.8 GHz bands allowing equipment manufactures to focus on a limited number of systems and configurations. An SCR architecture is proposed based on SoC integration of both digital and analog functions allowing modularity and flexibility with a reduced footprint and equipment cost reduction.

Baseband to radio interfaces were analyzed representing the future of open and distributed eNB architectures. A contribution on carrier grade capacity analysis and interface interoperability enhancements was presented. Likewise, system synchronization and delay management - relevant because of the remote nature of OBSAI/CPRI equipment supporting reliable multi-hop applications - were thoroughly analyzed. A new architecture for a serial receiver circuitry - the main source of interface delay measurement inaccuracy - is presented enabling 100 ps of theoretical resolution for delay variance.

# Resume (in Danish)

Denne afhandling omhandler 4G radio access-netværk og dækker frekvenstildelingsmetoder, eNB softwaredefinerede radioer og arkitekturer, herunder signaleringsaspekter relevante for IMT-Advanced.

Dynamisk frekvensallokering er et alternativ til faste tildelingsmetoder. Selv ved 100 MHz spektrum per antenne vil det kræve frekvensomfordeling - færste rollouts med båndbredder på 40-MHz udnytter sammenlægning af bærebælger, og MIMO-antenneteknikker, og er planlagt inden for en 3-årig tidshorisont. MultiRAN og høj-effekts eNB konfigurationer forventes at operere i 1.7 - 2.6 GHz-båndet. Ligeledes vil SingleRANs energibesparende konfigurationer opererende i 2.6-3.8 GHz-båndet give udstyrsfabrikanterne mulighed for at fokusere på et begrænset antal af systemer og konfigurationer. En SCR arkitektur er foreslet på grundlag af SoC integration af bde digitale og analoge funktioner, og den giver modularitet og fleksibilitet med et reduceret fodspor og reduktion af udstyrsomkostninger.

Basisbndsfrekvens- til radiofrekvensens-grænseflader blev analyseret, og de reprsenterer fremtiden for åbne og distribuerede eNB arkitekturer. Der bliver tillige præsenteret et forslag til Carrier Grade kapacitetsanalyser og interface interoperabilitets-forbedringer. Ligeledes bliver systemsynkronisering og forvaltning af forsinkelse til understøttelse af pålidelige multi-hop-applikationer (der er relevant på grund af, at OBSAI / CPRI udstyr står fjernt fra hinanden) grundigt analyseret. En ny arkitektur for et serielt modtagerkredsløb med 100 ps teoretisk opløsning af forsinkelsesvarians prsenteres.

## **Publications**

#### Peer Reviewed Journal Papers

C. Lanzani, G. Bergamo, and M. Hoegdal, "Analysis of clock distribution and delay management for IMT-Advanced distributed wireless base station systems," Frequenz: Journal of RF-Engineering and Telecommunications, December 2010 [1]

#### Peer Reviewed Conference Proceedings

- C. Lanzani, G. Bergamo, and M. Hoegdal, "Analysis of clock distribution and delay measurements for multi-hop remote radio applications," in 6th Karlsruhe Workshop on Software Radios (I. K. I. of Technology Communications Engineering Lab, ed.), (Karlsruhe, Germany), pp. 146–152, March 3/4 2010 [2]

- G. Kardaras and C. Lanzani, "Advanced multimode radio for wireless and mobile broadband communication," in *Wireless Technology Conference*, 2009. EuWIT 2009. European, pp. 132–135, IEEE Computer Society, sept. 2009 [3]

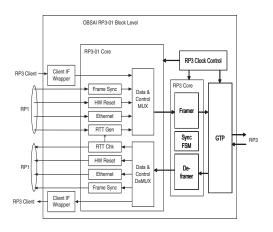

- C. Lanzani, "OBSAI RP3-01 6.144 Gbps Implementation," in 4th FPGAworld Conference Proceedings 2007 (L. Lindh and V. Mooney, eds.), pp. 10–15, FPGA World, October 2007 [4]

#### Committee Approved Standardization Bodies Contributions

RP3-TWG, OBSAI RP3 Specification v.4.2. OBSAI, www.obsai.com, v.4.2 ed., March 2010 [5]

C. Lanzani and et al., RP3 / RP3-01 Interface Profile Document. OBSAI, www.obsai.com, May 2009 [6]

#### Refereed Conference Presentations

- C. Lanzani, "Open base station architecture: Can standardization enable true innovation?," in *PCIA 2008*, (www.pcia.com), 2008 [7]

- C. Lanzani, "A path toward unified remote radio interface," in *IWPC Workshop on Flexible 4G Base Station Architectures*, (www.iwpc.org), 2008 [8]

#### **Company Internal Publications**

- C. Lanzani, M. Hoegdal, and N. Behjou, "Analysis of multi-mode transmission RF IC for base stations," tech. rep., Radiocomp ApS, 2010 [9]

- C. Lanzani, Base Station Management Procedures for OBSAI RP3-01 and CPRI Interfaces. Radiocomp ApS, www.radiocomp.com, January 2010 [10]

- C. Lanzani, Single and Multi Hop CPRI Interface Applications using Radiocomp's CPRI v.4.1 IP Core. Radiocomp ApS, www.radiocomp.com, v.1.4 ed., May 2009 [11]

- C. Lanzani and et al., *CPRI v.4.1 IP Core User Manual.* Radiocomp, www.radiocomp.com, v.2.3 ed., September 2010 [12]

- C. Lanzani and et al, *OBSAI RP3-01 IP Core User Manual*. Radiocomp, www.radiocomp.com, v.2.0 ed., August 2010 [13]

# Abbreviations and Acronyms

Α

${f ADC}$  Analog-to-Digital Converter

AGC Automatic Gain Control

**AL** Application Layer

**ASIC** Application Specific Integrated Circuit

ATM Asynchronous Transfer Mode

AWS Advanced Wireless Services

В

**BBM** Base-Band Module

**BER** Bit Error Rate

**BF** Basic Frame

**BOM** Bill Of Materials

**BTS** Base Transceiver Station

${\bf BW}$ BandWidth

$\mathbb{C}$

CA Carrier Aggregation

**CC** Component Carrier

**CAPEX** Capital Expenses

**CCM** Clock and Control Module

**CDR** Clock Data Recovery

CN Core Network

**CoMP** Coordinated Multi Point transmission

COTS Common off the Shelf

C-Plane Control Plane

CPRI Common Public Radio Interface

CLK Clock

CPU Control Processing Unit

CR Cognitive Radio

CRC Cyclic Redundancy Check

**C&M** Control and Management

D

${\bf DAC}$  Digital-to-Analog Converter

**DCF** Digital Communication FPGA

DCU Digital Communication Unit

**DDC** Digital Down Converter

**DSA** Dynamic Spectrum Allocation

**DSL** Digital Subscriber Line

**DSP** Digital Signal Processing

**DUC** Digital Up Converter

**DL** DownLink

**DPC** Discrete Processing Core

$\mathbf{DPD}$  Digital Pre Distortion

Е

$\mathbf{eNB}$  Evolved NodeB

**EPC** Evolved Packet Core

F

FCB Frame Clock Burst

FCS Frame Check Sequence

FDD Frequency Division Duplexing

FSA Fixed Spectrum Allocation

FS Frequency Synthesizer

FSM Finite State Machine

FPGA Field Programmable Gate Array

G

Gbps Giga bits per second

**GPP** General Purpose Processor

**GPS** Global Positioning System

**GSM** Global System/Standard Mobile

Н

HARQ Hybrid Automated Repeat Request

**HSEVB** High Speed Evaluation Board

**HDS** Hardware Defined Sub-system

**HSDU** High Speed Digital Unit

**HW** Hardware

I

IEEE-SA Institute of Electrical and Electron-

ics Engineers - Standards Association

IC Integrated Circuit

IF Intermediate Frequency

IMT International Mobile Telecommunications

IP Internet Protocol

IPR Intellectual Property Right

IQ In-phase and Quadrature

ITU International Telecommunication Union

$\mathbf{L}$

L1 Layer 1

**L2** Layer 2

**L3** Layer 3

${f LC}$  Local Converter

LNA Low Noise Amplifier

LO Local Oscillator

LSB Least Significant Bit

LTE Long Term Evolution

LVDS Low Voltage Differential Signaling

LU Local Unit

Μ

MAC Media Access Control

Mbps Mega bits per second

MCU Micro Controller Unit

ME Mobile Equipment

MF Master Frame

MSB Most Significant Bit

MG Message Group

MGT Multi Gigabit Transceiver

MIMO Multiple In Multiple Out

MIPS Million Instructions Per Second

MC Multi Carrier

$\mathbf{MSR}$  Multi Standard Radio

MUX Multiplexer

O

**OAM&P** Operation Administration Maintenance & Provisioning

OCXO Owen Controller Crystal Oscillator

**OEM** Original Equipment Manufacturer

**OBSAI** Open Base Station Architecture Ini-

tiative

**OPEX** Operating Expenses

**ORI** Open Radio Interface

**OS** Operating System

**OSI** Open Systems Interconnection

Р

PA Power Amplifier

PAR Peak to Average Ratio

PCB Printed Circuit Board

PCS Physical Coding Sub Layer

PLL Phase-Locked Loop

**PRC** Primary Reference Clock

PRBS Pseudo Random Bit Sequence

Q

**QAM** Quadrature Amplitude Modulation

**QoS** Quality of Service

R

RAN Radio Access Network

RAM Read Access Memory

RAT Radio Access Technology

RATG Radio Access Technology Group

**RF** Radio Frequency

**RFM** Radio Frequency Module

**RFT** Radio Frequency Transceiver

RNC Radio Network Controller

**RNS** Radio Network Subsystem

**RMS** Root Mean Square

**ROM** Read Only Memory

RTL Register Transfer Logic

RTT Round Trip Time

**RP** Reference Point

RoF Radio over Fiber

**RRH** Remote Radio Head unit.

S

**SAP** Service Access Point

SCR Software Configurable Radio

SDH Synchronous Digital Hierarchy

SDR Software Defined Radio

**SERDES** SERializer DESerializer

**SEM** Spectral Emission Mask

SF System Frame

SFN System Frame Number

SFP Small Factor Pluggable

**SOAP** Simple Object Access Protocol

SoC System on a Chip

**SPC** Soft Processing Core

SPI Serial Peripheral Interface

S-Plane Synchronization Plane

**SR** Software Radio

SSC Spectrum sharing and Co-existence

SYNC Synchronization signal

## Τ

TBTS Traditional Base Station System

**TDD** Time Division Duplexing

**TDM** Time Division Multiplexing

TMA Tower Mounted Amplifier

TMB Tower Mounted Booster

TM Transport Module

TRX Transceiver

TTR Time To Repair

$\mathbf{TWG}$  Technical Work Group

**2G** Second Generation GSM Mobile Networks

**3G** Third Generation UMTS Mobile Networks

4G Fourth Generation LTE Mobile Networks

### IJ

**UMTS** Universal Mobile Telecommunication

Standard

$\mathbf{UL}$  UpLink

**U-Plane** User Plane

UTRAN Universal Terrestrial Radio Access

Network

## V

VCO Voltage Controlled Oscillator

VHDL Very High Speed Hardware Descrip-

tion Language

VCXO Voltage Controlled Crystal Oscillator

## W

WINNER European Wireless World Initia-

tive New Radio

WiMAX Worldwide Interoperability Multiple

Access

WCDMA WideBand Code Division Multiple

Access

WRC Worldwide Radio Conference

# Contents

| A                | bstra | act          |                                                                 | i   |

|------------------|-------|--------------|-----------------------------------------------------------------|-----|

| $\mathbf{R}$     | esum  | ne (in 1     | Danish)                                                         | iv  |

| P                | ublic | ${f ations}$ |                                                                 | vi  |

| $\mathbf{A}$     | bbre  | viatior      | ns and Acronyms                                                 | vii |

| $\mathbf{P}_{1}$ | refac | $\mathbf{e}$ |                                                                 | xix |

| 1                | Inti  | roduct       | ion                                                             | 5   |

| <b>2</b>         | 4G    | Netwo        | orks: Spectrum and Radio Access Requirements                    | 11  |

|                  | 2.1   | Overv        | riew of Bandwidth Demand                                        | 11  |

|                  | 2.2   | Spect        | rum Allocation Methodologies                                    | 16  |

|                  |       | 2.2.1        | Fixed Spectrum Allocation Limitations                           | 16  |

|                  |       | 2.2.2        | Dynamic Spectrum Allocation Principles                          | 20  |

|                  |       | 2.2.3        | Considerations on Short-Term Spectrum and Coverage Requirements | 22  |

|                  | 2.3   | Metho        | ods for Increasing the Capacity of 4G Networks                  | 24  |

|                  |       | 2.3.1        | Multi-Antenna Techniques                                        | 26  |

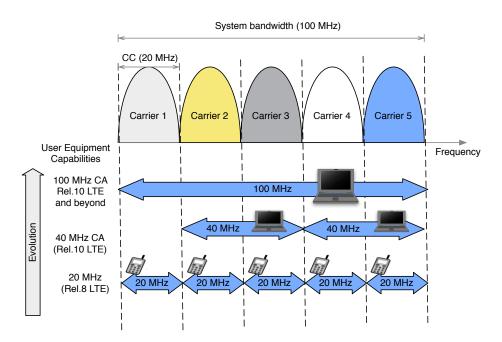

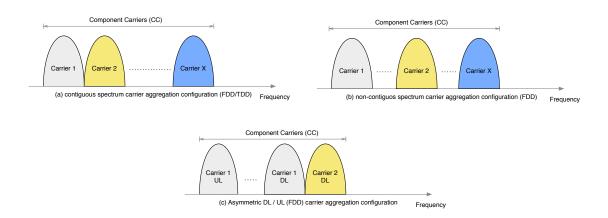

|                  |       | 2.3.2        | Carrier Aggregation Techniques                                  | 29  |

|                  |       | 2.3.3        | Discussion on Bandwidth Demand                                  | 35  |

|                  | 2.4   | Softwa       | are Radio Architecture                                          | 36  |

|                  |       | 2.4.1        | Software Defined Radios                                         | 36  |

|                  |       | 2.4.2        | Limitations of Software Configurable Radios                     | 41  |

|                  |       | 2.4.3        | A Multi-RAN Remote Radio Architecture                           | 44  |

|                  | 2.5   | Sumn         | nary                                                            | 46  |

| 3                | Bas   | se Ban       | d to Radio Interface Analysis                                   | 47  |

|                  | 3.1   | Overv        | view of open eNB interfacing standards                          | 48  |

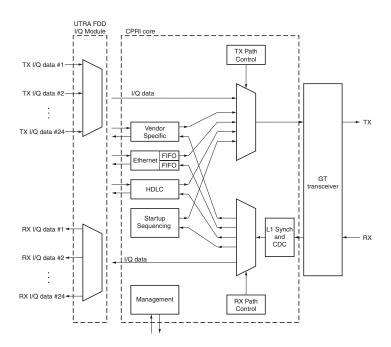

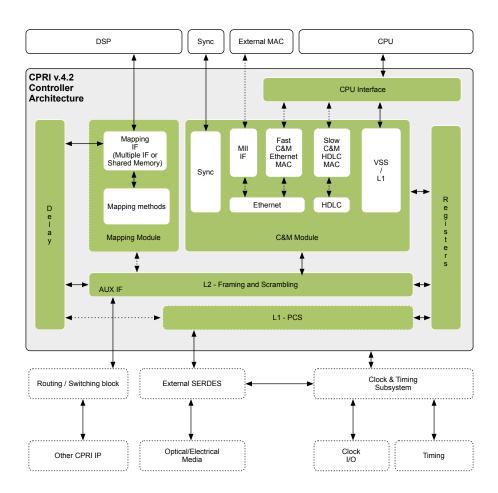

|                  |       | 3.1.1        | CPRI Protocol Structure                                         | 50  |

|                  |       | 3.1.2        | RP3-01 Protocol Structure                                       | 51  |

|                  |       | 3.1.3        | Digitized Baseband Signals Representation                       | 52  |

|                  | 3.2   | CPRI         | / RP3-01 Framing Structures Comparison                          | 54  |

|                  |       | 3.2.1        | Interface Capacity Comparison: RP3-01 vs. CPRI                  | 57  |

#### Contents

|              | 3.3       | Study on Protocol Interoperability                                                       | 62          |

|--------------|-----------|------------------------------------------------------------------------------------------|-------------|

|              |           | 3.3.1 Limitations of Equipment Interoperability                                          | 63          |

|              |           | 3.3.2 Methodology for Interoperability                                                   | 66          |

|              |           | 3.3.3 Results on Interoperability Enhancement Study                                      | 66          |

|              | 3.4       | Interface Start-up Sequencing                                                            | 72          |

|              |           | 3.4.1 System Synchronization Overview                                                    | 73          |

|              |           | 3.4.2 Start-Up Sequencing and Delay Measurements                                         | 77          |

|              |           | 3.4.3 A Link Start-Up Sequence with Deterministic Delay                                  | 80          |

|              | 3.5       | Summary                                                                                  | 84          |

| 4            | An        | Advanced Interface Protocol Stack Architecture Design                                    | 85          |

|              | 4.1       | Overview of a Generic Interface Architecture                                             | 86          |

|              | 4.2       | State-of-the-Art Interfaces Implementations                                              | 87          |

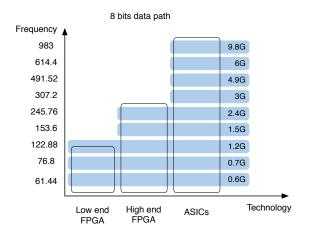

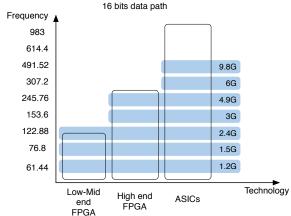

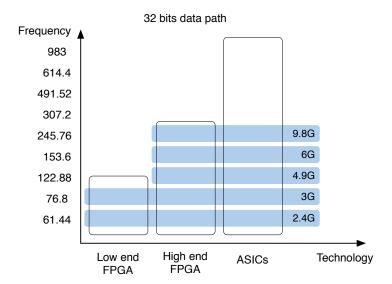

|              |           | 4.2.1 Data Path Dimensioning                                                             | 87          |

|              |           | 4.2.2 Functional Block Architecture                                                      | 89          |

|              | 4.3       | An Advanced Interface Controller Architecture                                            | 91          |

|              |           | 4.3.1 10-Gigabit Line Rates and Beyond                                                   | 92          |

|              |           | 4.3.2 A Highly Parallel Data Path Design Proposal                                        | 93          |

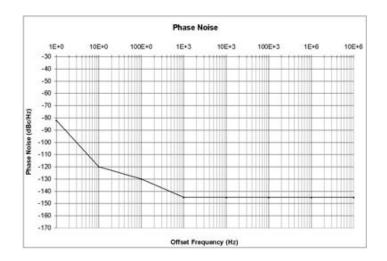

|              |           | 4.3.3 Measurements Results of 6.144 Gbps RP3-01 Signal                                   | 95          |

|              | 4.4       | A Novel Physical Layer Receiver Circuitry with Deterministic Latency                     | 99          |

|              |           | 4.4.1 Physical Layer Receiver and Data Path Delays                                       | 99          |

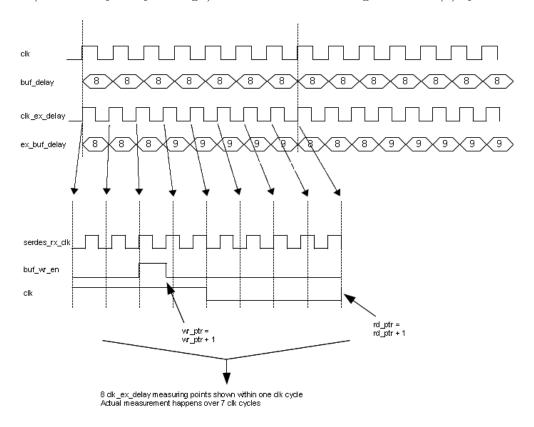

|              |           | 4.4.2  Design of a High-Precision Receiver Digital Delay Measurement Circuit  .  .  .  . | 102         |

|              | 4.5       | Summary                                                                                  | 106         |

| 5            | Dis       | cussion and Conclusions                                                                  | 107         |

|              | 5.1       | Summary of Contributions                                                                 | 109         |

|              | 5.2       | Future Research                                                                          | 111         |

| Re           | efere     | ences                                                                                    | 112         |

|              | 01010     |                                                                                          |             |

| A            | ppen      | adices                                                                                   | <b>12</b> 0 |

| $\mathbf{A}$ | <b>4G</b> | networks overview                                                                        | <b>12</b> 0 |

| В            | 3GI       | PP Frequency Bands                                                                       | <b>12</b> 9 |

| C            | One       | en Base Station Interface Standards                                                      | 132         |

|              | _         |                                                                                          |             |

| D            | Exa       | ample of RP3-01 System Start-up Sequence Diagrams                                        | 140         |

| $\mathbf{E}$ | Clo       | ck Distribution in Multi-Hop Radio Applications                                          | 143         |

| F            | CP        | RI and RP3-01 Synchronization and Delay Background                                       | 152         |

# List of Figures

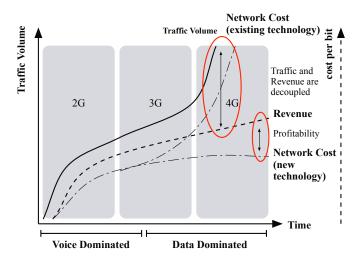

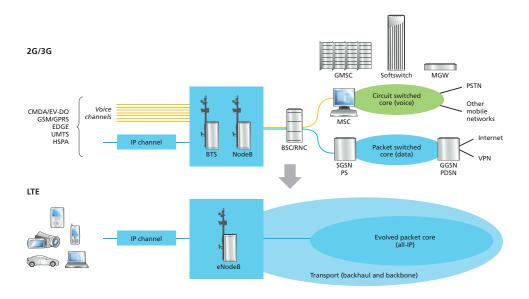

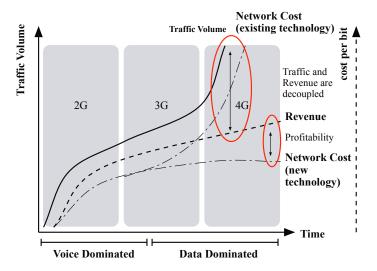

| 1    | Trends in network traffic, revenues and cost per bit.                                           | 2  |

|------|-------------------------------------------------------------------------------------------------|----|

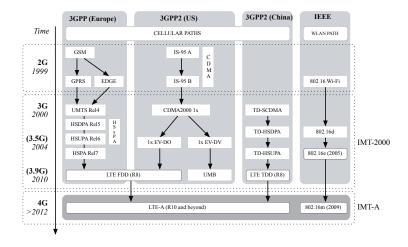

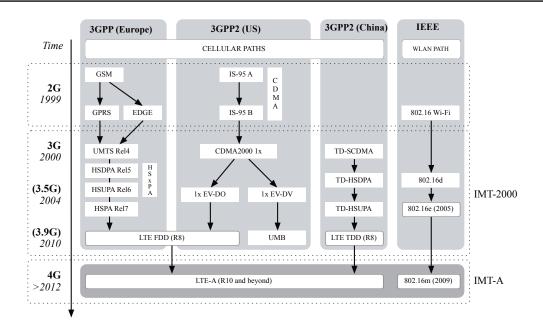

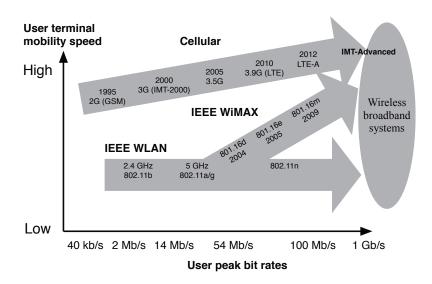

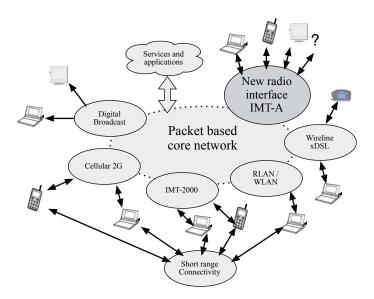

| 2    | Mobile and WLAN technologies evolution paths toward 4G mobile wireless networks                 | 3  |

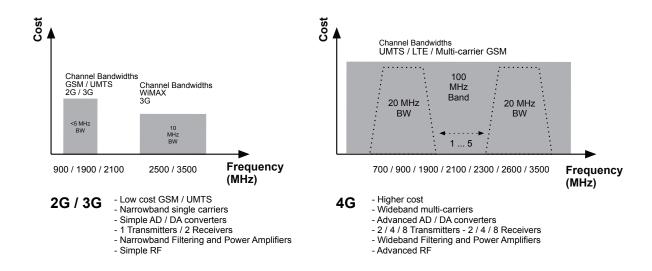

| 1.1  | Radio Access Spectrum and Configuration Cost Trend Comparison between $2\mathrm{G}/3\mathrm{G}$ |    |

|      | and 4G                                                                                          | 6  |

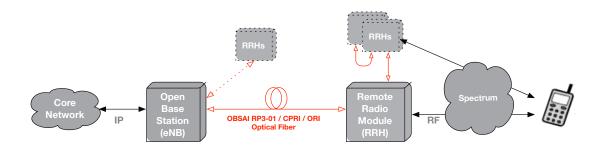

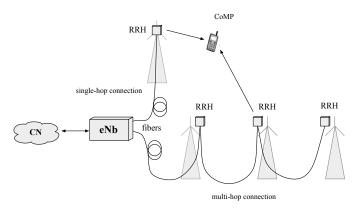

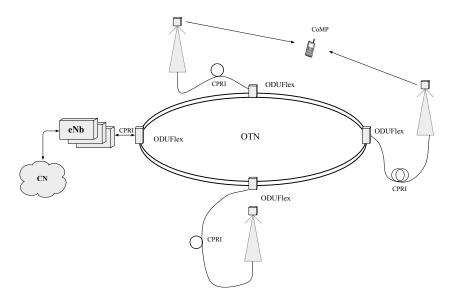

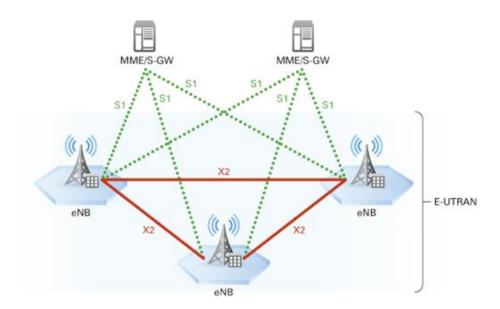

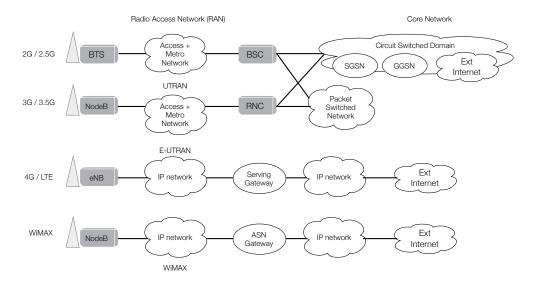

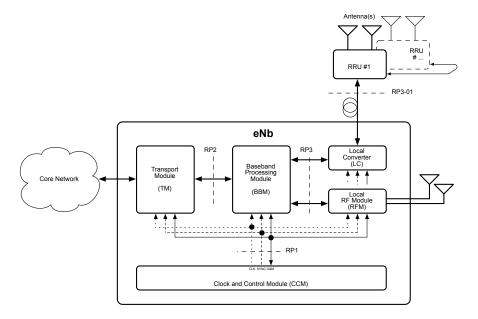

| 1.2  | Network Architecture Overview of Open eNB with Remote Radio Heads. $\ \ldots \ \ldots$          | 7  |

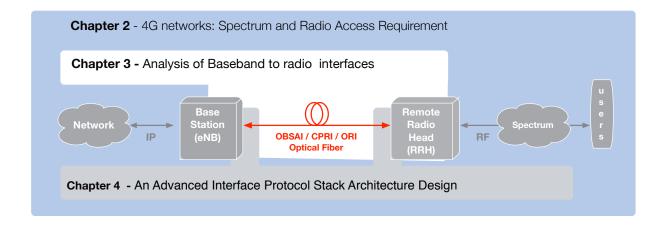

| 1.3  | Report Structure                                                                                | 9  |

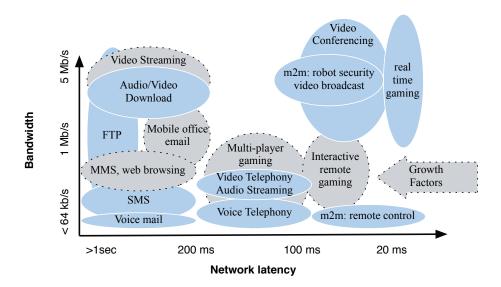

| 2.1  | Internet services throughputs and latencies                                                     | 13 |

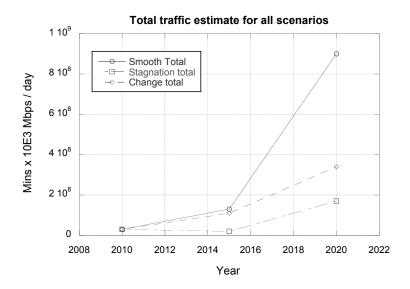

| 2.2  | Total wireless mobile traffic volume estimates for 4G                                           | 13 |

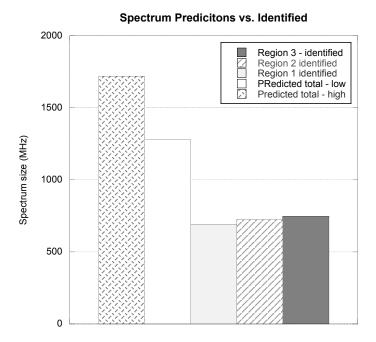

| 2.3  | Predicted 4G networks spectrum                                                                  | 15 |

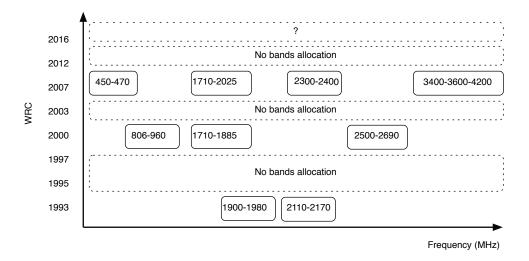

| 2.4  | Worldwide Radio Conferences and frequency bands identifications                                 | 17 |

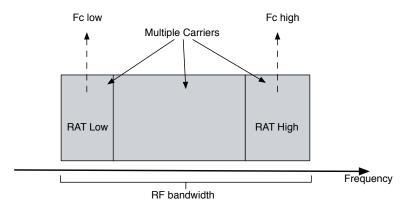

| 2.5  | Radio Frequency definitions for Multi-standard usage of spectrum                                | 19 |

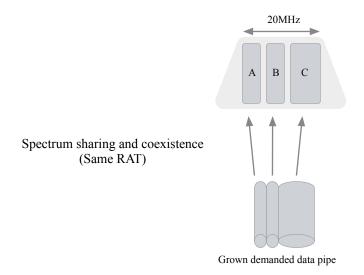

| 2.6  | Spectrum Sharing and Coexistence (SSC)                                                          | 20 |

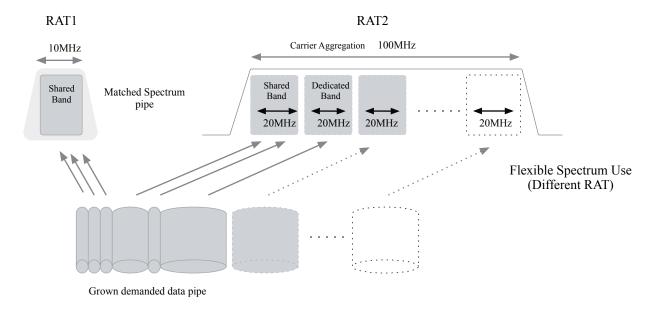

| 2.7  | Flexible Spectrum Utilization (FSU)                                                             | 21 |

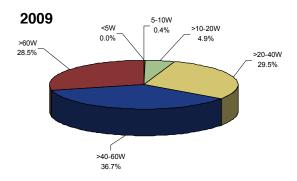

| 2.8  | Base station deployments forecast in 2009                                                       | 24 |

| 2.9  | Base station deployments forecast in 2014                                                       | 24 |

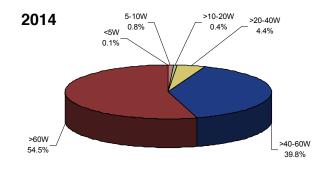

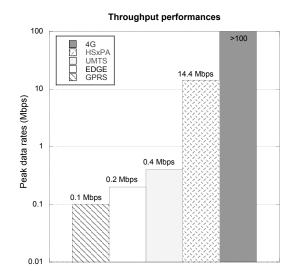

| 2.10 | Throughput performance evolution path                                                           | 25 |

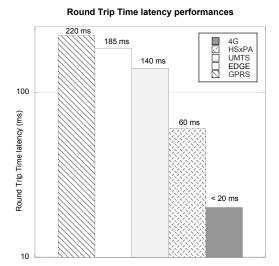

| 2.11 | Latency performance evolution path                                                              | 25 |

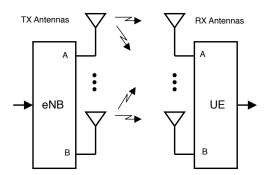

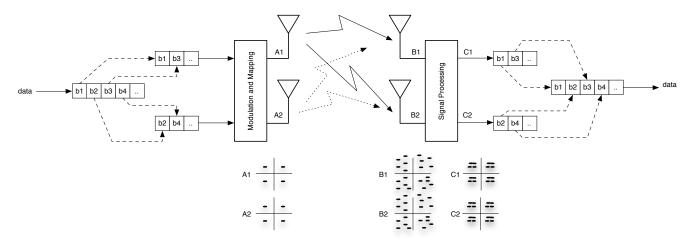

| 2.12 | MIMO Transmitter and Receiver Concept                                                           | 27 |

| 2.13 | 2x2 MIMO Communication System                                                                   | 28 |

| 2.14 | Carrier Aggregation concept and usage scenario                                                  | 30 |

| 2.15 | Carrier Aggregation Types at Physical Layer                                                     | 31 |

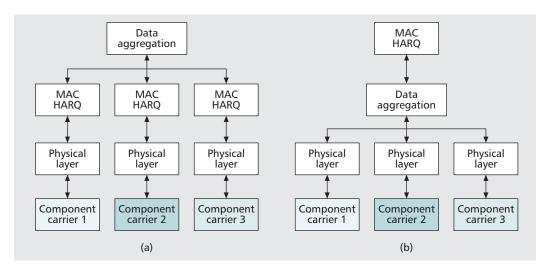

| 2.16 | Carrier Aggregation Types at MAC Layer                                                          | 33 |

| 2.17 | Evolution phases for SDR systems                                                                | 37 |

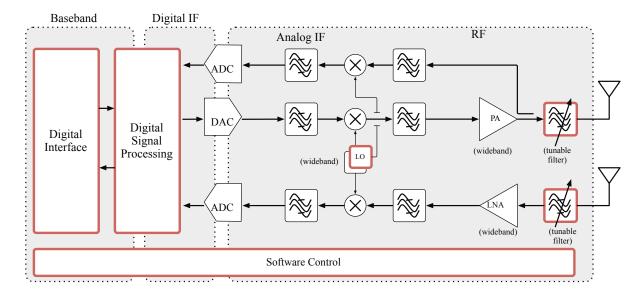

| 2.18 | Typical Hardware Reference Design for SDR                                                       | 39 |

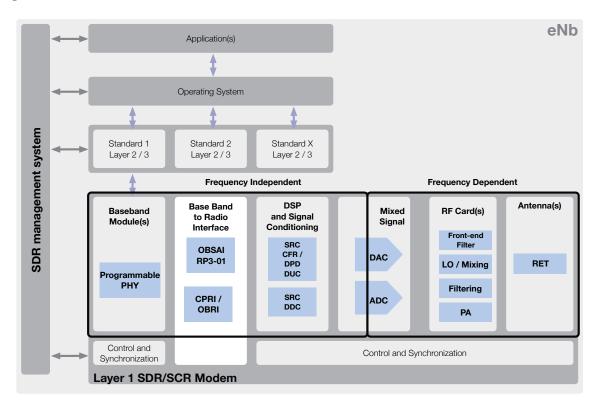

| 2.19 | Software Defined / Configurable Multi-RAN eNB architecture                                      | 40 |

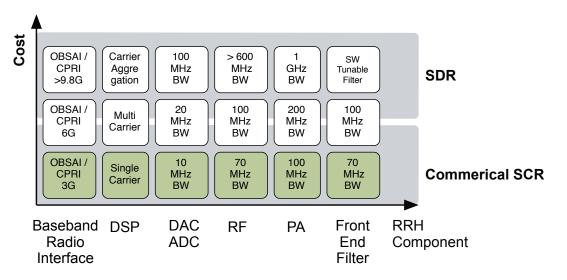

| 2.20 | Overview of commercial SCR $/$ SDR radio components vs cost of the technology                   | 42 |

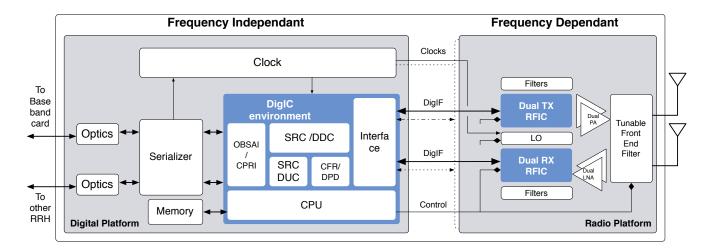

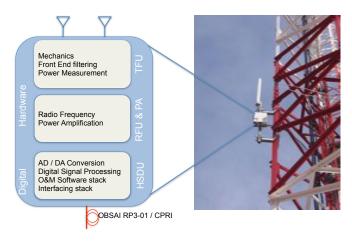

| 2.21 | Architecture for a flexible and integrated remote radio head environment                        | 45 |

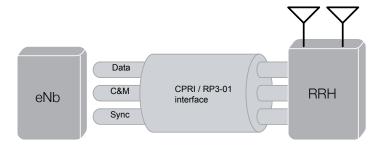

| 3.1  | Base band to radio interface concept                                                            | 48 |

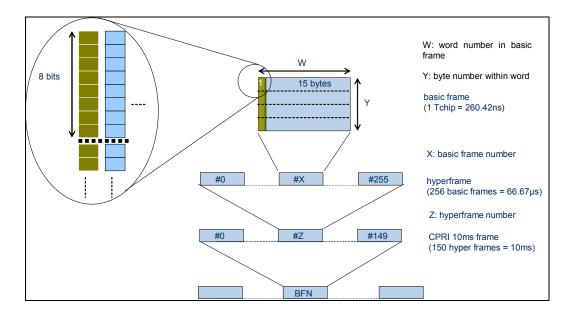

| 3.2  | CPRI Basic Frame Definition                                                                     | 50 |

| 3.3  | CPRI Basic Frame Definition                                                                     | 51 |

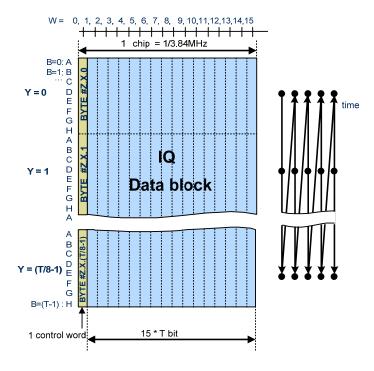

| 3.4  | RP3 / RP3-01 Frame Structure Definition                                                         | 52 |

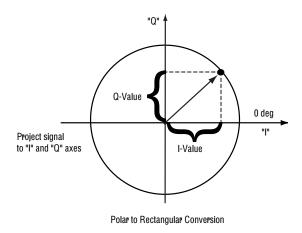

| 3.5        | Polar to rectangular conversion concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

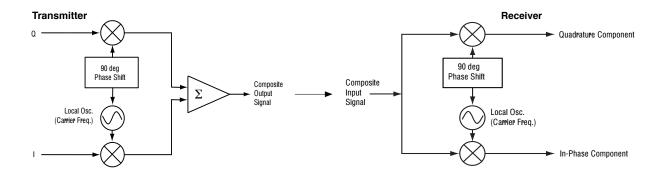

| 3.6        | In-phase and Quadrature digital radio Transmitter and Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54  |

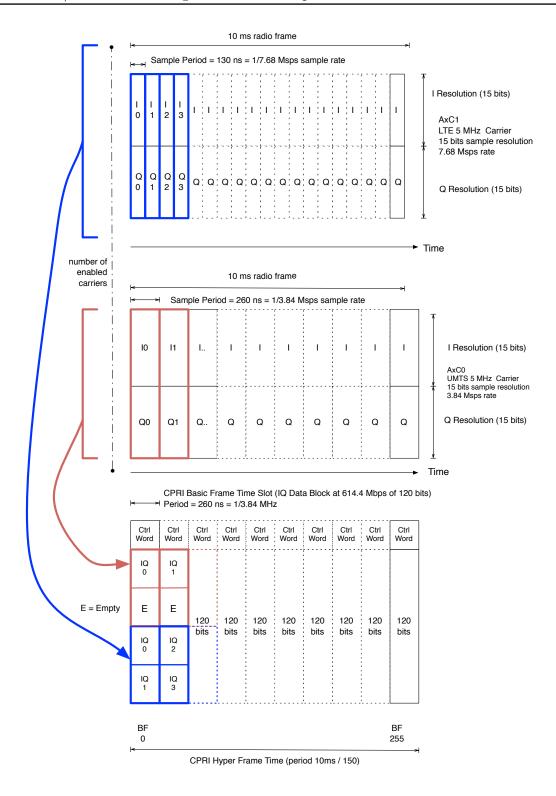

| 3.7        | Example of configuration parameters with two I/Q carriers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55  |

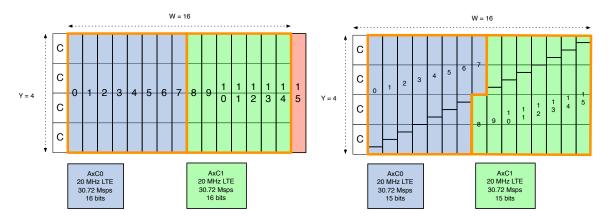

| 3.8        | CPRI 20 MHz LTE Mapping with 2.4576 Gbps line rate and 16 bits sample size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58  |

| 3.9        | CPRI 20 MHz LTE Mapping with 2.4576 Gbps line rate and 15 bits sample size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58  |

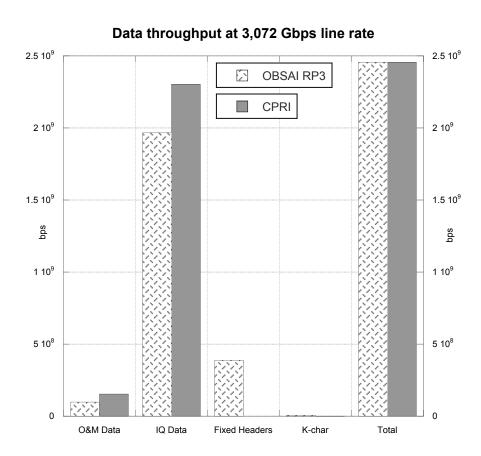

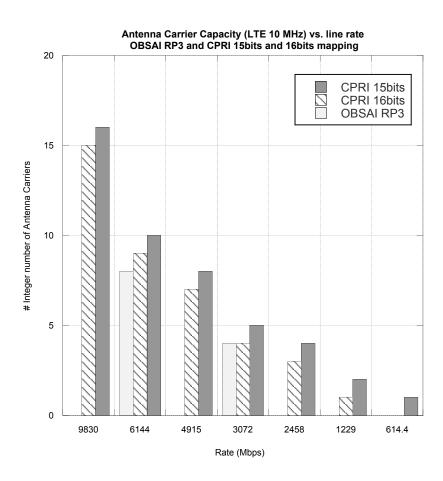

| 3.10       | OBSAI RP3-01 and CPRI Data Flows Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59  |

| 3.11       | OBSAI RP3-01 and CPRI Carrier Grade Capacity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60  |

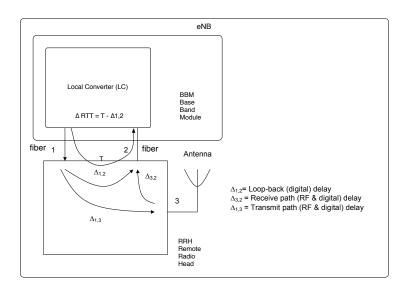

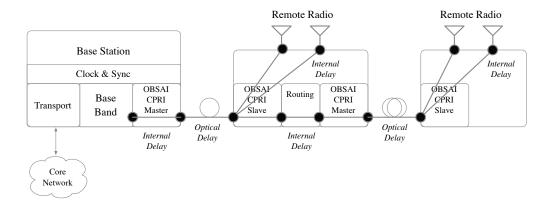

| 3.12       | Delays in an eNB between a BBM/LC and a RRH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63  |

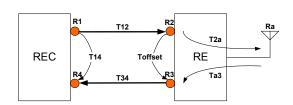

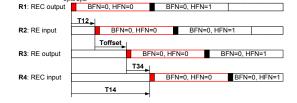

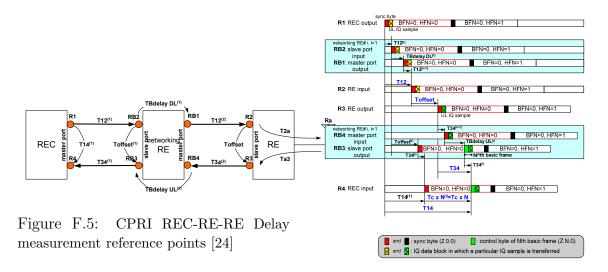

| 3.13       | Reference points for delay measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64  |

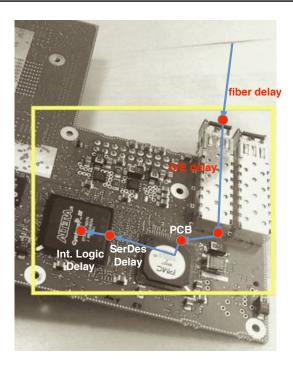

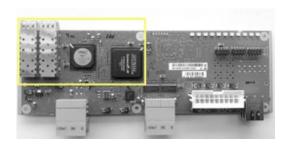

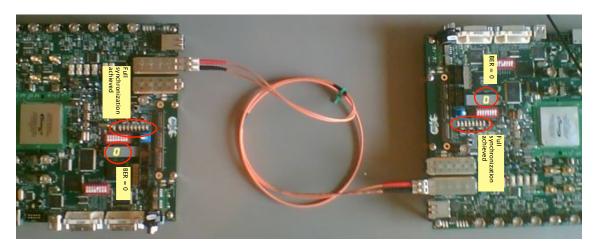

| 3.14       | Reference points for delay measurement on the Radiocomp HSDU RRH Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|            | card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65  |

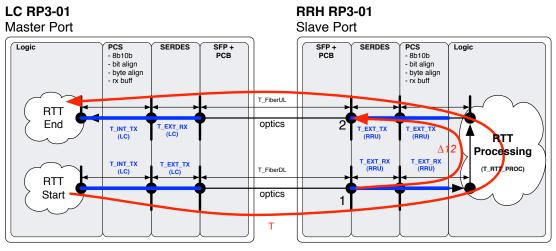

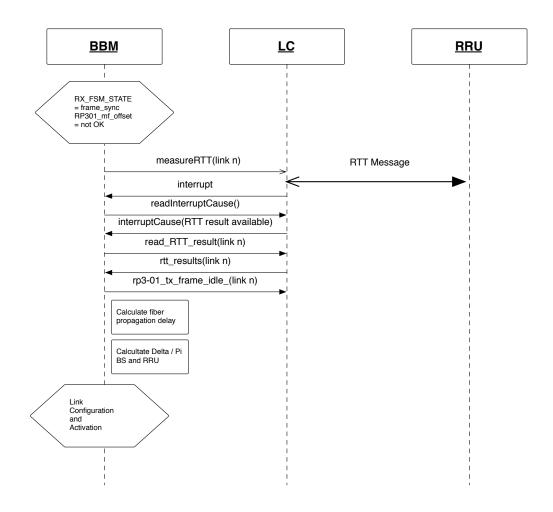

| 3.15       | Round Trip Time in RP3-01 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67  |

| 3.16       | OBSAI RP3-01 Air-Interface profile application layer parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70  |

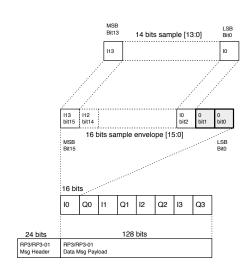

| 3.17       | Illustration of sample payload mapping proposal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70  |

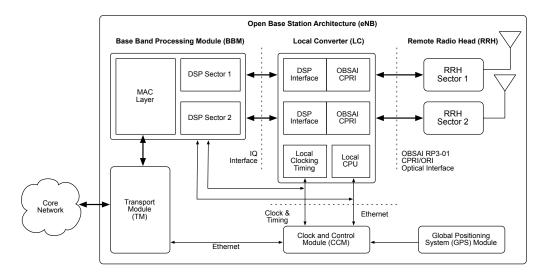

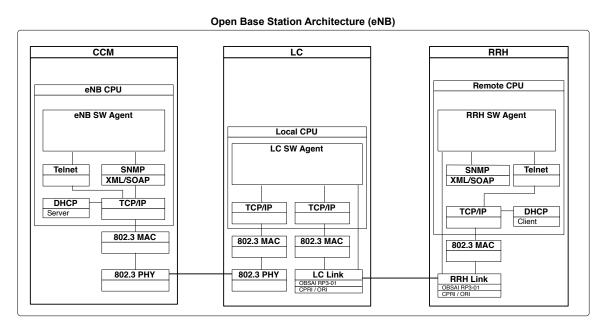

| 3.18       | Generic and open eNB modular architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 73  |

| 3.19       | Common software protocol communications between internal eNB modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74  |

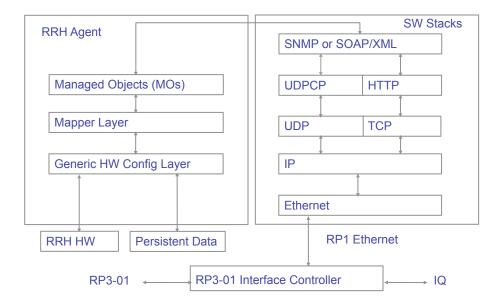

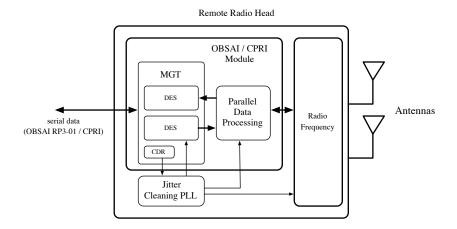

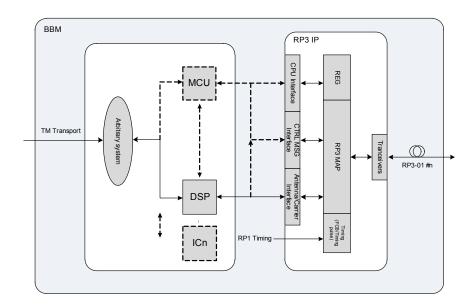

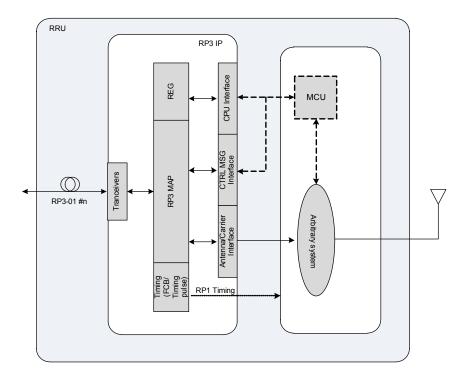

| 3.20       | Example of detailed software architecture in a remote radio head unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75  |

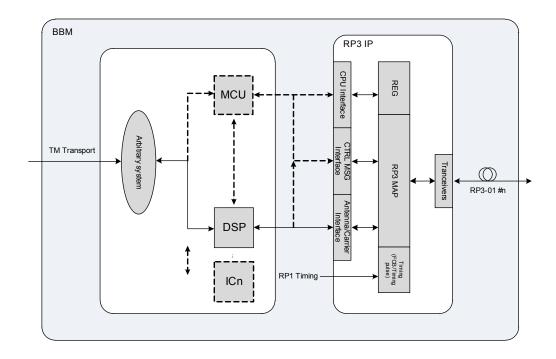

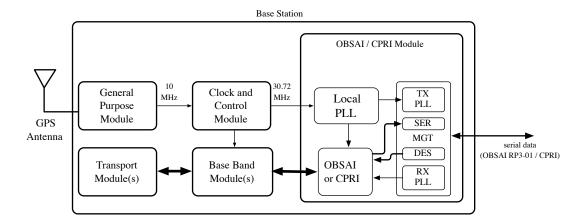

| 3.21       | Conceptual BBM internal synchronization architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76  |

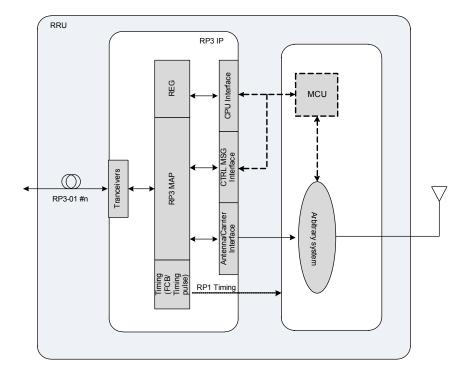

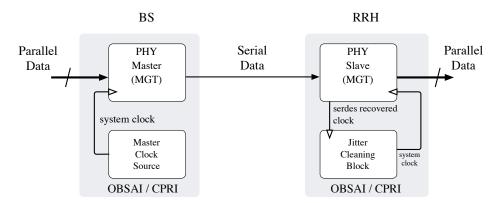

| 3.22       | Conceptual RRH internal synchronization architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76  |

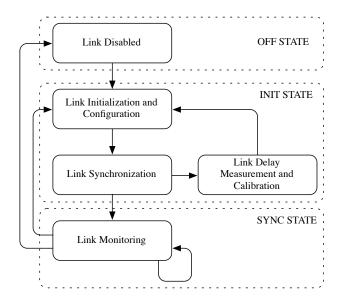

| 3.23       | RP3-01 Link Start-up FSM sequence phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77  |

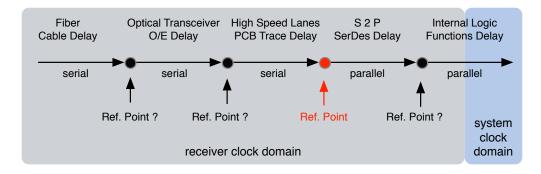

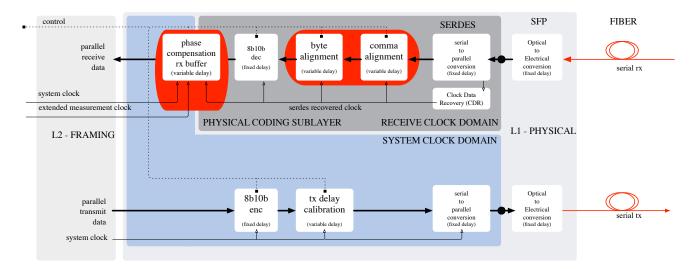

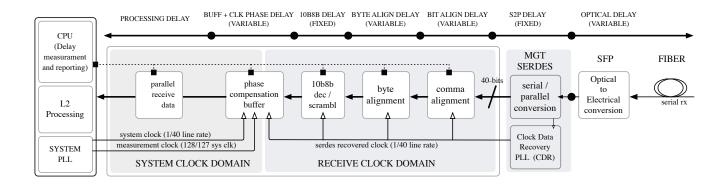

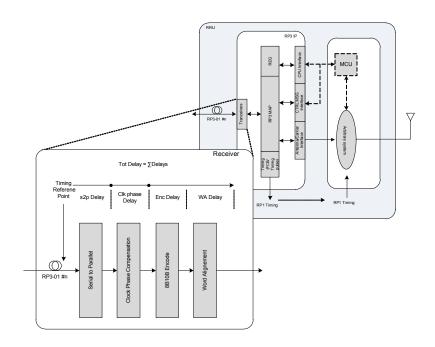

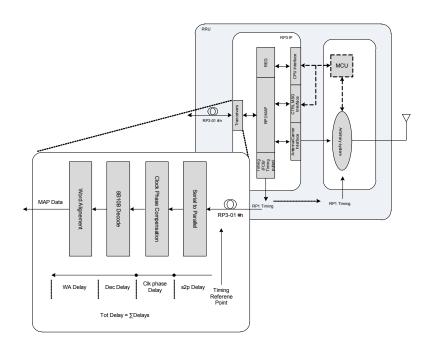

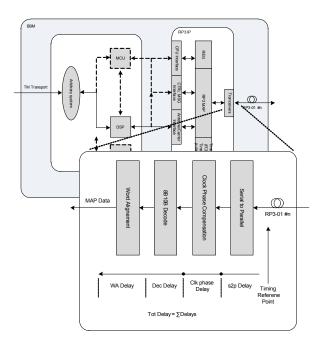

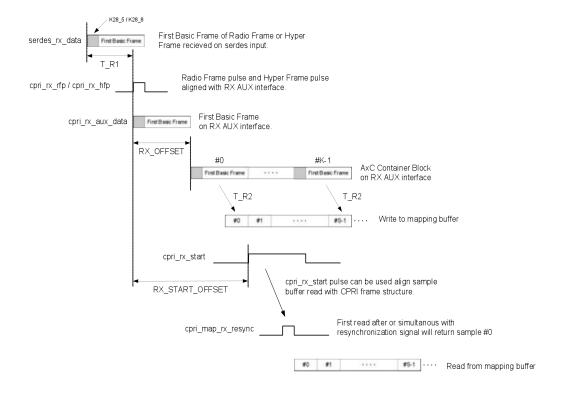

| 3.24       | Block diagram architecture of a serial to parallel physical layer receiver chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 78  |

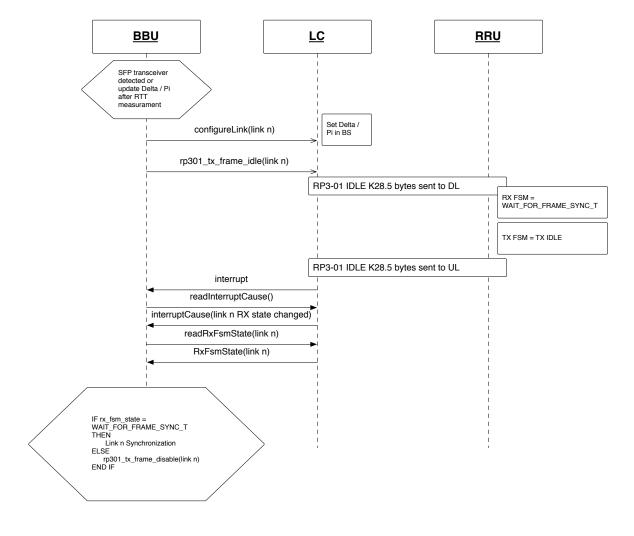

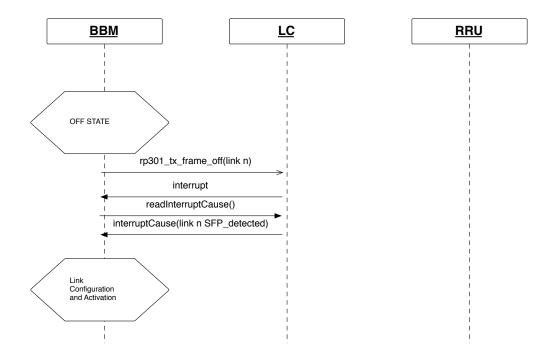

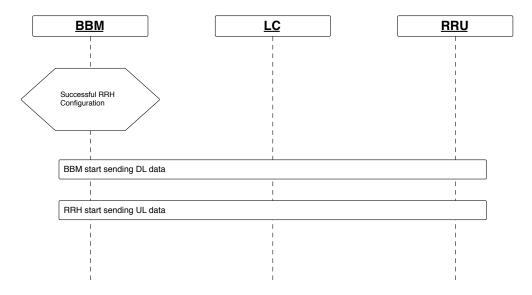

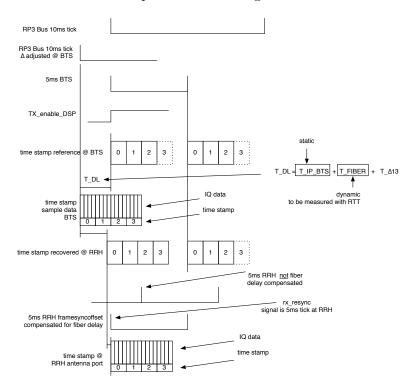

| 3.25       | RP3-01 Link Configuration and Activation phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81  |

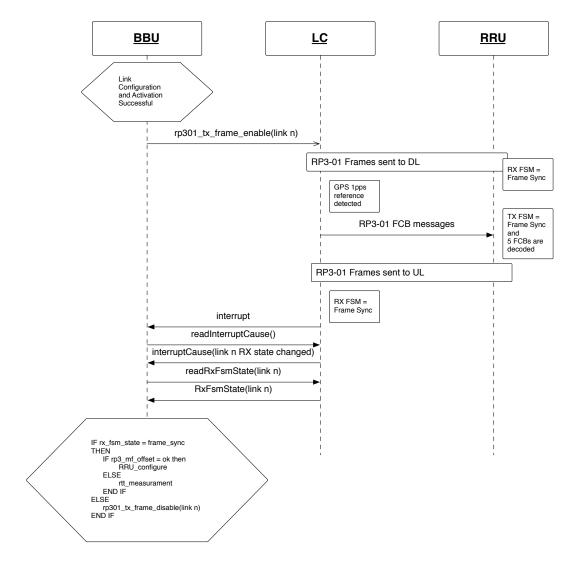

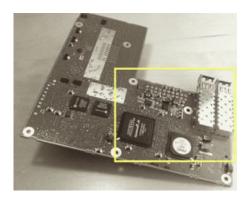

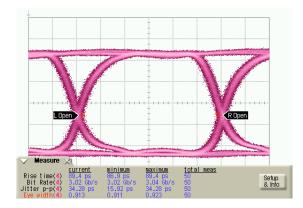

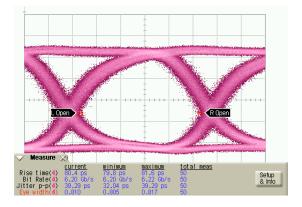

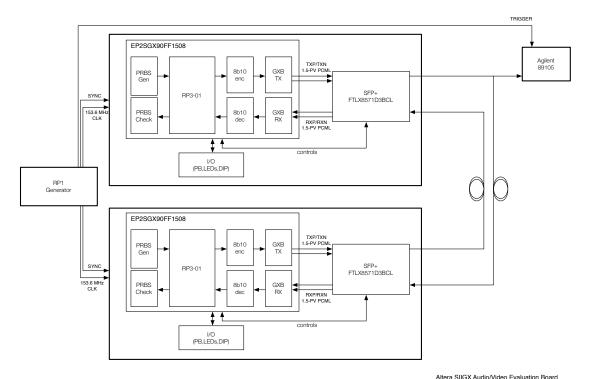

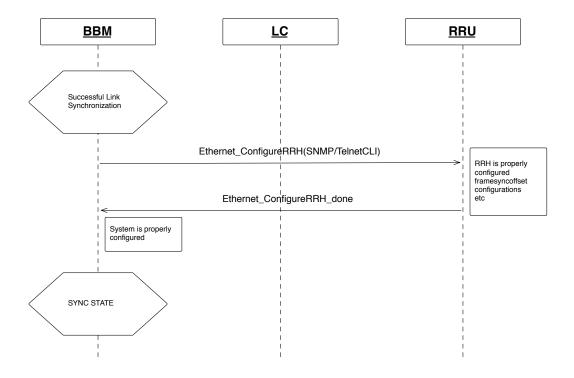

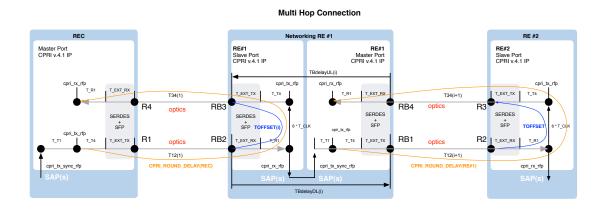

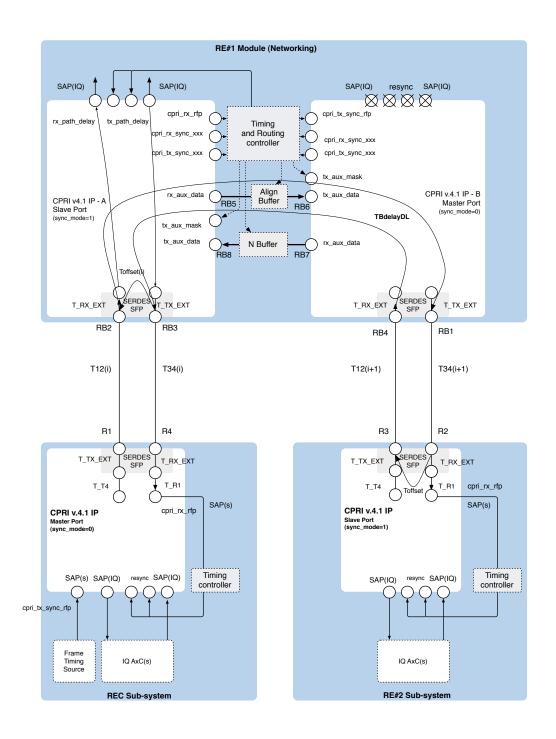

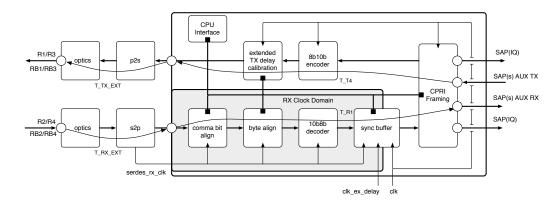

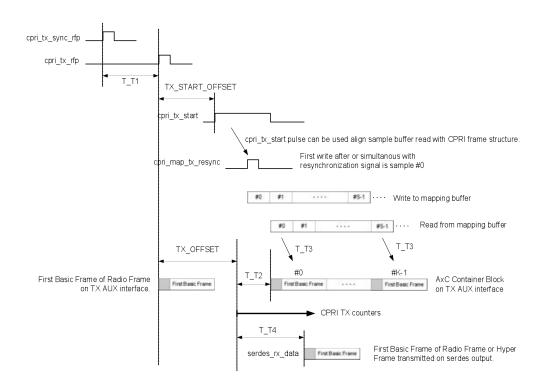

| 3.26       | RP3-01 Link Synchronization phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82  |