## Tradeoff analysis for Dependable Real-Time Embedded Systems during the Early Design Phases

Gan, Junhe

Publication date: 2014

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA): Gan, J. (2014). Tradeoff analysis for Dependable Real-Time Embedded Systems during the Early Design Phases. Technical University of Denmark. DTU Compute PHD-2014 No. 330

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Tradeoff Analysis for Dependable Real-Time Embedded Systems during the Early Design Phases

Junhe Gan

Kongens Lyngby 2014 PhD-2014-330

Technical University of Denmark Department of Applied Mathematics and Computer Science Building 303B, DK-2800 Kongens Lyngby, Denmark Phone +45 45253031, Fax +45 45881399 compute@compute.dtu.dk www.compute.dtu.dk PhD-2014-330

To My Family

### Summary

Embedded systems are becoming increasingly complex and have tight competing constraints in terms of performance, cost, energy consumption, dependability, flexibility, security, etc. The objective of this thesis is to propose design methods and tools for supporting the tradeoff analysis of competing design objectives during the early design phases, which are characterized by uncertainties. We consider safety-critical real-time applications modeled as task graphs, to be implemented on distributed heterogeneous architectures consisting of processing elements (PEs), interconnected by a shared communication channel. Tasks are scheduled using fixed-priority preemptive scheduling, and we use non-preemptive scheduling for messages.

As a first step, we address the problem of function-to-task decomposition. In this context we have assumed that the application functionality is captured by a set of functional blocks, with different safety requirements. We propose a Genetic Algorithm-based metaheuristic to solve the function-to-task decomposition problem. Our algorithm also decides the mapping of tasks to the PEs of a distributed architecture and the reliability of each PE in the architecture, such that the safety and integrity constraints are satisfied, the schedulability of the real-time application is guaranteed and the overall development and product unit costs are minimized.

Next, we investigate tradeoffs between performance, energy and reliability. Addressing energy and reliability simultaneously is especially challenging, since lowering the voltage to reduce the energy consumption has been shown to increase the transient fault rate. We are interested to tolerate transient faults and we use task replication for recovery. We propose a Tabu Search-based approach, which decides the mapping of tasks to processing elements, as well as the processor voltage and frequency levels for executing each task, such that transient faults are tolerated, the real-time constraints of the application are satisfied, and the energy consumed is minimized. In this thesis, we target the early design phases, when decisions have a high impact on the subsequent implementation choices. However, due to a lack of information, the early design phases are characterized by uncertainties, e.g., in the worst-case execution times (WCETs), in the functionality requirements, or in the hardware component costs. In this context, we select the hardware components for the architecture and derive a mapping of tasks in the application, such that the resulted implementation is both robust and flexible. The architecture also has a high chance to have its unit cost within the cost budget. Robust means that the application has a high chance of being schedulable, considering the WCET uncertainties, whereas a flexible mapping has a high chance to successfully accommodate future functionality changes. We propose a Genetic Algorithm-based approach to solve this optimization problem. The proposed tradeoff analysis methods have been evaluated using several synthetic and real-life benchmarks.

# Summary (Danish)

Indlejrede systemer bliver stadig mere komplekse og har stramme, konkurrerende begrænsninger med hensyn til ydelse, pris, energiforbrug, pålidelighed, fleksibilitet, sikkerhed osv. Formålet med denne afhandling er at foreslå metoder og redskaber til at støtte en afvejningsanalyse af konkurrerende design mål i de tidlige design faser, som er karakteriseret af usikkerhed. Vi berører sikkerhedskritiske realtidsapplikationer modelleret som opgave grafer, der skal implementeres på distribuerede heterogene arkitekturer bestående af beregningsselementer (PE'er), sammenkoblet med en delt kommunikationskanal. Opgaver planlægges ved hjælp af fast prioritet afbrydende (preemptive) planlægning, og vi bruger ikke- afbrydende (non-preemptive) planlægning for meddelelser.

Som et første skridt, vi tager fat på problemet med funktion-til-opgave nedbrydning. I denne sammenhæng har vi antaget, at applikationens funktionalitet er beskrevet ved et sæt af funktionelle blokke, med forskellige sikkerhedskrav. Vi foreslår en metaheuristik baseret på en genetisk algoritme til at løse problemet med funktion-til-opgave nedbrydningen. Vores algoritme afgører også fordelingen af opgaver til PE'en i en distribueret arkitektur og pålideligheden af de enkelte PE'er i arkitekturen, således at sikkerhedskravene er opfyldt, skedulerbarheden af realtids-applikationen er garanteret og de overordnede udviklings og produkt omkostninger minimeres.

Dernæst undersøger vi afvejninger mellem ydeevne, energi og pålidelighed. Håndtering af energi og pålidelighed samtidig er særligt udfordrende, fordi at sænke spændingen til at reducere energiforbruget har vist sig at øge hyppigheden af midlertidige fejl. Vi er interesseret i at tolerere forbigående fejl og vi bruger opgave replikering til fejlhåndtering. Vi foreslår metoden "Tabu Searc", som beslutter fordeling af opgaver til PE'er, samt processor spænding og frekvens niveauer for udførelse af hver enkelt opgave således at: forbigående fejl tolereres, realtids kriterier i applikationen er opfyldt og energiforbruget minimeres.

I denne afhandling fokuserer vi på de tidlige design faser, hvor beslutninger har en stor indvirkning på de efterfølgende implementeringsvalg. Dog er de tidlige design faser karakteriseret ved et højt niveau af usikkerhed på grund af manglende information. F.eks. i de værst tænkelige eksekveringstider (WCET'er), i de funktionelle krav, eller i de hardware komponenten omkostninger. I denne sammenhæng, vi vælge de hardware komponenter til arkitektur og udleder en fordeling af opgaver i applikationen, således at den endelige implementeringen er både robust og fleksibel. Arkitekturen også har en høj chance for at få sin enhedsomkostninger inden omkostningerne budget. Robust betyder, at programmet har en høj chance for at være skedulerbar, taget WCET usikkerheder i betragtning, mens en fleksibel fordeling har en høj chance for succesfuldt at rumme fremtidige funktionelle ændringer. Vi foreslår en genetisk algoritme metodik til at løse dette optimeringsproblem. De foreslåede afvejnings-analyse metoder er blevet evalueret ved hjælp af flere syntetiske og real-life benchmarks.

## Preface

This thesis was prepared at the Department of Applied Mathematics and Computer Science, the Technical University of Denmark in fulfillment of the requirements for acquiring the Ph.D. degree in computer engineering.

In this thesis, we propose methods and tools to support automatic design space exploration for the design of embedded systems in the early design phases. The thesis consists of an introductory chapter and three papers.

The work has been supervised by Associate Professor Paul Pop and co-supervised by Professor Jan Madsen.

甘君荷

Junhe Gan

## Acknowledgements

I would like to express my sincere respect and heartfelt thanks towards Paul Pop and Jan Madsen, for their professional supervision. I feel it is my great honor to be their PhD student. During these years of my PhD, they were always there, providing me all the help I need.

My greatest appreciation to Paul Pop, for two things. Firstly, I appreciated he selected me to be his PhD student, which gave me a chance to improve my skills and knowledge, which has proved to be a very rewarding experience. Secondly, I appreciated his patience towards me during these years. I learned a lot from his feedback, and improved, not only the ability to get things done, but also the manner and enthusiasm of my work.

I would also like to express a big thank you to Jan Madsen and Flavius Gruian. They gave me a lot of inspiring advice and patient reviews on our joint papers.

I have to mention that, close to half of my PhD time has been done at the Royal Institute of Technology (KTH), Sweden. I would especially like to thank Axel Jantsch and Ingo Sander for providing me an office and all the other help, which enabled me to finish my PhD. I enjoyed so much the various conversations with them and the time at KTH.

During my Master study in Lund University and Carnegie Mellon University, I had been working under the guidance of Claus Führer and Fernando De la Torre. They encouraged me and provided inspiration, from where the idea of pursuing a PhD grew in me. I would also like to thank all my friends and all the fellow students for their support and help in different aspects through the years when I was working in Sweden, USA and Denmark.

In particular, I want to give my special thanks to my husband, Hao Wang, for his understanding and support over the years. He always encourages me not to give up, when I feel discouraged.

Finally, I take this opportunity to express my deep gratitude to my parents, Yang Gan and Yiqiu Liao, for their endless love and support.

Junhe Gan

February 2014, Stockholm

### Contents

| Summary          |       |                                                           |     |     |    |     | i   |

|------------------|-------|-----------------------------------------------------------|-----|-----|----|-----|-----|

| Summary (Danish) |       |                                                           |     |     |    |     | iii |

| Pr               | eface |                                                           |     |     |    |     | v   |

| Ac               | know  | vledgements                                               |     |     |    |     | vii |

| 1                | Intr  | oduction                                                  |     |     |    |     | 1   |

|                  | 1.1   | Design Metrics                                            |     |     |    |     | 2   |

|                  |       | 1.1.1 Energy Consumption                                  |     |     |    |     | 3   |

|                  |       | 1.1.2 Cost                                                |     |     |    |     | 3   |

|                  |       | 1.1.3 Performance and Predictability                      |     |     |    |     | 4   |

|                  |       | 1.1.4 Dependability                                       |     |     |    |     | 5   |

|                  |       | 1.1.5 Robustness and Flexibility                          |     |     |    |     | 7   |

|                  | 1.2   | Design of Embedded Systems                                |     |     |    |     | 7   |

|                  |       | 1.2.1 Systems Engineering Stages                          |     |     |    |     | 8   |

|                  |       | 1.2.2 Early Decisions                                     |     |     |    |     | 9   |

|                  |       | 1.2.3 System-Level Design                                 |     |     |    |     | 10  |

|                  |       | 1.2.4 Design Challenges                                   |     |     |    |     | 12  |

|                  |       | 1.2.5 Design Space Exploration                            |     |     |    |     | 14  |

|                  | 1.3   | Thesis Objective and Contribution                         |     |     |    |     | 15  |

| 2                | Pap   | er A: Criticality-Aware Function-to-Task Allocation for D | lis | tri | bu | ted |     |

|                  | Real  | I-Time Embedded Systems                                   |     |     |    |     | 19  |

|                  | 2.1   | Introduction                                              |     |     | •  |     | 20  |

|                  |       | 2.1.1 Related Work                                        |     |     |    |     | 22  |

|                  | 2.2   | System Model                                              |     |     |    |     | 24  |

|                  |       | 2.2.1 Application Model                                   |     |     |    |     | 24  |

|   |           | 2.2.2 Platform Model                                                                                                            |      |     |    |      | 29       |

|---|-----------|---------------------------------------------------------------------------------------------------------------------------------|------|-----|----|------|----------|

|   | 2.3       | Problem Formulation                                                                                                             |      |     |    |      | 32       |

|   |           | 2.3.1 Motivational Example                                                                                                      |      |     |    |      | 32       |

|   | 2.4       | Optimization Strategy                                                                                                           |      |     |    |      | 35       |

|   |           | 2.4.1 Objective Functions                                                                                                       |      |     |    |      | 35       |

|   |           | 2.4.2 Genetic Algorithm                                                                                                         |      |     |    |      | 37       |

|   | 2.5       | Evaluation                                                                                                                      |      |     |    |      | 39       |

|   | 2.6       | Conclusion                                                                                                                      |      |     |    |      | 44       |

|   | 2.0       |                                                                                                                                 | • •  | •   | •  | •    |          |

| 3 | Pape      | er B: Reliability-Aware Dynamic Energy Management for Fa                                                                        | ult  | t-T | ol | lera | ant      |

|   | -         | ributed Embedded Systems                                                                                                        |      |     |    |      | 45       |

|   | 3.1       | Introduction                                                                                                                    |      |     |    |      | 46       |

|   | 3.2       | System Model                                                                                                                    |      |     |    |      | 48       |

|   | 3.3       | Reliability Model                                                                                                               |      |     |    |      | 51       |

|   |           | 3.3.1 Energy/Reliability Trade-off Model                                                                                        |      |     |    |      | 53       |

|   | 3.4       | Problem Formulation                                                                                                             |      |     |    |      | 55       |

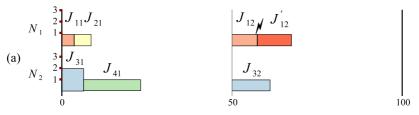

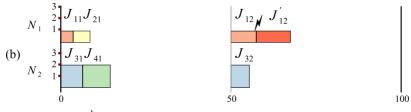

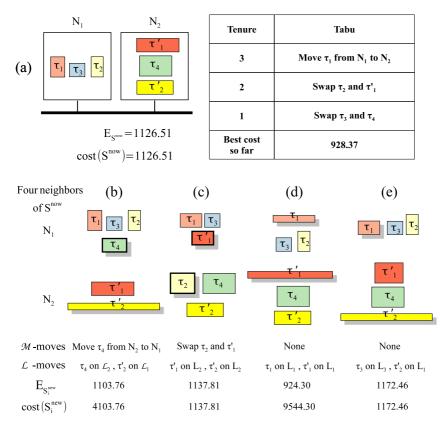

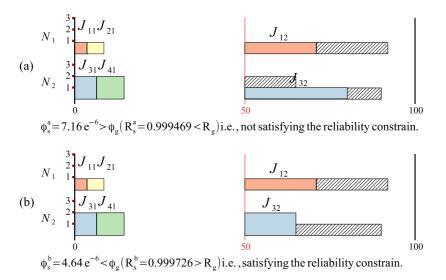

|   |           | 3.4.1 Motivational Example                                                                                                      | •••  | •   | •  | •    | 55       |

|   | 3.5       | Offline Synthesis                                                                                                               |      |     |    |      | 59       |

|   | 3.6       | Online Scheduling                                                                                                               |      |     |    |      | 63       |

|   | 3.7       | Experimental Results                                                                                                            |      |     |    |      | 67       |

|   | 5.7       | 3.7.1 Offline Synthesis Evaluation                                                                                              |      |     |    |      | 67       |

|   |           | 3.7.2 Online Scheduling Evaluation                                                                                              |      |     |    |      | 69       |

|   | 3.8       | Conclusions                                                                                                                     |      |     |    |      | 71       |

|   | 5.0       |                                                                                                                                 | •••  | •   | ·  | ·    | /1       |

| 4 | Pape      | er C: Design for Robustness and Flexibility of Real-time D                                                                      | Dist | ril | bu | ted  | ł        |

|   | -         | lications during the Early Design Phases                                                                                        |      |     |    |      | 73       |

|   | 4.1       | Introduction                                                                                                                    |      |     |    |      | 74       |

|   | 4.2       | System Model                                                                                                                    |      |     |    |      | 76       |

|   |           | 4.2.1 Early Design Stages                                                                                                       |      |     |    |      | 76       |

|   |           | 4.2.2 Modeling WCET Uncertainties                                                                                               |      |     |    |      | 78       |

|   |           | 4.2.3 Modeling Functionality Uncertainties                                                                                      |      |     |    |      | 79       |

|   | 4.3       | Problem Formulation                                                                                                             |      |     |    |      | 80       |

|   | 1.5       | 4.3.1 Robustness and Flexibility                                                                                                |      |     |    |      | 80       |

|   | 4.4       | Schedulability Analysis                                                                                                         |      |     |    |      | 81       |

|   | 4.5       | Motivational Example                                                                                                            |      |     |    |      | 84       |

|   | 4.6       | Mapping Optimization                                                                                                            |      |     |    |      | 85       |

|   | <b></b> 0 | 4.6.1 NSGA-II for Multiobjectives Optimization                                                                                  |      |     |    |      | 86       |

|   |           | 4.6.2 Determining the Mapping of Future Scenarios                                                                               |      |     |    |      | 88       |

|   | 4.7       |                                                                                                                                 |      |     |    |      | 89       |

|   |           | Experimental Results                                                                                                            |      |     |    |      |          |

|   | 4.8       |                                                                                                                                 |      |     |    |      | 92       |

|   |           | 4.8.1 Modeling Cost Uncertainty in Architecture Selection                                                                       |      |     |    |      | 93<br>04 |

|   |           | 4.8.2 Architecture Selection Problem                                                                                            |      |     |    |      | 94       |

|   |           | <ul><li>4.8.3 Architecture Selection: Motivational Example</li><li>4.8.4 GA-based Approach for Architecture Selection</li></ul> |      |     |    |      | 94<br>97 |

|   |           | A V A I - A based Approach for Architecture Valuation                                                                           |      |     |    |      | - ur/    |

#### Contents

|     | 4.9          | Conclusion       | 99  |  |  |  |

|-----|--------------|------------------|-----|--|--|--|

| A   | List         | of Abbreviations | 101 |  |  |  |

| B   | List         | of Notations     | 103 |  |  |  |

| Bil | Bibliography |                  |     |  |  |  |

### CHAPTER 1

## Introduction

We are living in a time of great change, with rapid development of science and technology. High-tech products are greatly improving our quality of life and work efficiency. Most of the products we use today are controlled by digital computer systems. When talking about digital computers, we may immediately think of the general purpose computer systems, such as laptops, desktops or servers. However, the computers inside most of the devices we used are a special type of computer systems, called *embedded systems*. Over 98% of the microprocessors produced are used in embedded systems [EJ09].

Compared to the general purpose computer systems, embedded systems are usually used in a specialized application domain, performing a specific set of functions, repeatedly. Embedded systems are controlled and operated by a predetermined program, and thus the expected operations of the embedded system interacting to the external environment should have been considered and captured in the program.

It is difficult to give a precise definition of an embedded system. Their most important characteristic is that they are built for performing a specific set of functions, and thus are not general purpose computers. Another characteristic is that they are tightly constrained, i.e., embedded systems have requirements such as high performance, low energy consumption, low cost, small size and short time-to-market. Most of embedded systems should be also continually reactive and perform the functions in real-time, with high predictability. A mobile phone is an example of am embedded system, which is designed and used for making telephone calls, sending messages, and some entertainment activities for the leisure time. With smartphones, the distinction between general purpose computers and embedded systems becomes less obvious.

Other examples of embedded systems are the automotive electronic functions inside a vehicle, such as Anti-lock Braking Systems (ABS), engine control, airbags. A modern high-end vehicle can have more than 100 microprocessors implementing various functionalities [Cha09].

Embedded systems are everywhere. People in their daily life and work use more than 30 embedded systems [EJ09], such as, cars, cameras, televisions, printers, traffic light systems, etc. Embedded systems can be large, for example, airplanes and ships, or can be very small, such as hearing aids or smart sensors. The growth rate in the number of embedded devices is more than 10% per year and it is estimated the number of embedded devices may reach 40 billion by 2020 [Res12]. According to statistics [Res12], the market of embedded systems was valued at 121 billion dollars in 2011, and this number is expected to grow by 6.8%, i.e., 194.27 billion dollars, in 2018.

The complexity of embedded systems is increasing very rapidly. For instance, more than 100 million object code instructions (totaling close to 1 Gbyte of software) are embedded in about 70 chips (electronic control units) in a currently new car [HS06, EJ09], in order to perform the required functions.

The size of embedded software is increasing with 10% to 20% per year, depending on the application area [EJ09]. Embedded software is more challenging to develop than traditional desktop software, e.g., Microsoft Word, because embedded systems have very tight constraints on the requirements that they have to fulfill. For example, the embedded software of controlling a car should react the operations from the driver quickly enough and provide a dependable service even in the worst-case scenarios.

Developing embedded software is expensive. According to  $[BCC^+05]$ , non safetycritical embedded software normally costs to develop between 15-30 dollars per line of code, while for highly critical applications, such as the space shuttle, the cost per line of code increases to 1,000 dollars.

#### 1.1 Design Metrics

As mentioned, embedded systems have very tight constraints on the requirements that they have to fulfill. Those requirements are divided into functional requirements and non-functional requirements. The desired functionality depends on the particular application that is implemented by the embedded system. Typical non-functional requirements can be expressed in terms of design metrics, such as, time-to-market, size, energy consumption, cost, performance, predictability, robustness, flexibility, and dependability attributes of reliability, safety, security, maintainability and availability. Time-tomarket is the time needed to build a working version of the system. Size means the physical space required by the system. Other design metrics are considered in our thesis and introduced in this section. The formal definition of these design metrics is given in the included papers: Paper A, Paper B and Paper C.

#### **1.1.1 Energy Consumption**

Energy-efficiency is one of the most important metrics for embedded systems, since many are battery-powered mobile devices. For example, mobile phones have stringent low power requirements, e.g., about two Watts [Mar11], limited by the available battery technology, so the battery lasts for a couple of days. The development of battery technology is far from satisfactory, and does not support the need of rapidly increasing computational requirements and the complexity of embedded applications [Roa09].

Process technology is targeted towards increased density, to support higher operating frequency, resulting not only in higher power density but also in thermal problems. Energy-efficiency aims to keep the embedded systems meeting other requirements such as size, weight, and performance, at the same time saving the power dissipation as much as possible, which can keep the temperature of embedded devices under desirable levels, such that the processors are not burned and the battery-life is extended.

In our thesis, we are interested in reducing the energy consumption without negatively impacting reliability and schedulability. These two design metrics of reliability and schedulability and their tradeoffs will be introduced later. We measure the *energy consumption* of an embedded system in *Processing Elements (PEs)*, which are a major component of the system-level energy consumption. We use the power model from [BBL09], as it is able to capture a set of realistic assumptions, such as discrete operating modes of PEs, the energy and delay due to mode switches, and takes I/O operations into account. The detailed definition of energy consumption for a specific embedded system is presented in Section 3.2, Paper B.

#### 1.1.2 Cost

Cost is always a key decision factor in most industries. The cost of a system could be measured in many ways, for example, as the sum of all component costs integrated in the system, or capturing the design, development and/or manufacturing costs. We define the *Non-Recurring Engineering cost (NRE)* as the one-time monetary cost of designing the system, and we define the *unit cost* as the monetary cost of manufacturing each copy of the system, excluding NRE cost. The NRE cost is fixed once the design of an system has been done, regardless of how many units are going to be manufactured.

Jokob Axelsson [Axe06] proposed a cost model to estimate the *per-product cost*, i.e., the cost of each copy of the system up to delivery, for a distributed real-time embedded system. In our thesis, we have adapted the cost model from [Axe06], considering the cost of an architecture solution in Section 4.8, Paper C, and considering the total cost of a design alternative that includes the unit cost of hardware components and the development and certification costs of software tasks in Section 2.4.1, Paper A.

#### 1.1.3 Performance and Predictability

Performance typically is captured by the execution time of computations and communications. Taking two mobile phones as an example, iPhone 5 has better performance than iPhone 4, since iPhone 5 can finish a same task much faster with its dual core running at 1,300 MHz, than the single core at 1,000 MHz of iPhone 4.

There are two main measures of performance, depending on what is of concern. One is the *latency* or *response time*, which is the duration of a task's execution. Another is the *throughput*, that is the number of tasks a system executes per unit time. For example, let us assume that, a camera takes 0.25 second to process an image. The latency of that camera is 0.25 seconds, while the throughput of that camera is 4 images per second [Vah06].

These measures of performance are not useful for real-time systems. A *real-time system* is an embedded system where the correctness of the result depends also on the time-instant when it has been produced [Kop11b]. In this context, other performance measures, related to predictability are more appropriate. *Predictability* is a key property of any real-time system that the timing requirements must be met. Before we discuss the timing requirements, some basic terms used in real-time systems are introduced.

There are many models of computation used to capture the functionality of an embedded system [ELLSV97]. In this thesis we have used the *task graph* model of computation, see the details in the attached papers. A *task* is defined as a sequence of instructions, and it is ready to be executed at any time after its *release time*. The *execution time* of the task may be different between task invocations, and this variability of task execution time is typically due to, for example, the variations in the input data of tasks or the speculative features of modern processors. In real-time systems, to be able to provide guarantees, engineers use the *Worst-Case Execution Time* (WCET). The WCET is an analytical bound on the execution time of a task (the execution time is surely not larger than this WCET bound) and can be determined using tools such as *aiT* from AbsInt [FH04]. Note that a WCET is a bound, i.e., a task may never execute for such a long period of time, and we are interested having as low as possible values for WCET (i.e., less pessimistic). Similarly, we can define the *Best-Case Execution time* (BCET) of a task. The length of time between the release time of a task and the time it finished executing is named as *response time*. A task is required to complete before its *deadline*.

Real-time embedded systems can have two types of timing requirements: hard and soft. In *hard* real-time embedded systems, each task must be completed before its deadline. Otherwise it may lead to catastrophic results. For example, the airbag in a car must be inflated within 10-20 milliseconds (ms), after a collision is detected. Any delay might be too late to save the life of the passenger.

In contrast, *soft* real-time embedded systems accept occasional timing failures, which will not result in disastrous consequences, but can lead to a certain performance degradation. For example, it is likely you are not aware that the DVD player failed to decode some frames of the video source, when you watch a movie.

In our thesis work, we target on hard real-time embedded systems. The metrics used for predictability are defined in Section 2.4.1 of Papers A, Section 3.5 of Paper B and Section 4.4 of Paper C.

#### 1.1.4 Dependability

Some of embedded systems, such as cars, airplanes, or medical equipment, nuclear power plants, are *safety-critical*, since any deviation from the specified functionality can have catastrophic consequences to the people or environment. *Fault-tolerance* means the safety device is still under the control and provides alternative functionality, although an internal fault occurred and was detected. Such faults might be permanent (e.g., damaged microcontrollers or communication links), transient (e.g., caused by electromagnetic interference), or intermittent (appear and disappear repeatedly). The transient faults are the most common [Con03], and their number is increasing due to the rising level of integration in semiconductors.

The *failure rate* of a system is the number of failures within a given period of time, which depends on the technology and age of the system, the voltage or physical shocks that the system suffers, and the ambient temperature that the system works on. The typical permanent fault rate has been reported [ZMM04] in the range of  $10^{-8}$  to  $10^{-6}$  faults per hour for a chip. However, the fault rate increases dramatically while the system

tem runs in some harsh environments. For example, for an orbiting satellite is reported that up to 35 errors are found in a 15-minutes interval [CMR92], which equals to 140 faults/hour.

Software faults (bugs) are permanent, i.e., they are due to specification, design or implementation mistakes. Software does not experience transient faults similar to hardware, since it is not aging, for example. A software bug disappears only if the software is updated with a new version, where the bug has been removed. We have considered to tolerate hardware transient faults which manifest themselves at the task-level.

*Dependability* is the system property that integrates such attributes as reliability, availability, safety, security, maintainability and availability [ALR<sup>+</sup>01]. *Reliability* is defined as the probability of successful execution over a period of time under a given set of operating conditions. We modeled the reliability for fault-tolerant distributed embedded systems in Section 3.3, Paper B.

*Safety* describes the property that a system will not endanger human life or the environment. A *Hazard* is a situation in which there is active or potential danger to people or the environment. *Risk* is a combination of the probability of a hazardous event and its consequence. If, after performing an initial hazard and risk analysis, a system is considered safety-critical, it has to be certified [KK10]. Certification is a "conformity of assessment" performed by a third party, e.g, an independent organization or a national authority, namely a "certification authority".

The current certification practice is "standards-based" [Rus07], and requires that the product and the development processes fulfill the requirements and satisfy the objectives of a certain certification standard, depending on the application area. For example, [IEC10] is used in industrial applications, [ISO09] is for the automotive area, whereas [RTC92] refers to software for airborne systems.

During the engineering of a safety-critical system, the hazards are identified and their severity is analyzed, the risks are assessed and the appropriate risk control measures are introduced to reduce the risk to an acceptable level. A *Safety-Integrity Level* (SIL) is allocated to each safety function and captures the required level of risk reduction. SIL allocation is typically a manual process, which is done after performing hazard and risk analysis [Sto96], although a few researchers have proposed automatic approaches for SIL allocation [PWR<sup>+</sup>10b]. SILs differ slightly among areas. For example, the avionics area uses five "Design Assurance Levels" (DALs), from DAL E (lest critical) to DAL A (most critical), while ISO 26262 specifies for the automotive area four "Automotive Safety Integrity Levels" (ASILs), from ASIL A (least critical) to ASIL D (most critical). However, the approach presented in this thesis is applicable to all safety-critical areas, regardless of the standard. SILs are assigned to functional blocks, from SIL 4 (most critical) to SIL 0 (non-critical).

*Security* concerns the property that a system is able to protect the confidentiality, integrity, and availability of data and guarantee their authenticated communication. Certification standards require that tasks of different SILs are separated. In addition, they also impose constraints on the communication to ensure data integrity. These constraints are similar to the Bell-LaPadula [BL73] and Biba [Bib77] data integrity models from the security domain. In our thesis, we have modeled the safety and integrity requirements for criticality-aware functionality allocation and information communication in Section 2.2, Paper A.

#### 1.1.5 Robustness and Flexibility

Design metrics are often difficult to quantify exactly due to, for example, uncertainties, as discussed about variability of task execution time in Section 1.1.3, hence there can be variations in their values. Also, the requirements of a system can change, especially in the early design phases. In addition, the environment where an embedded system operates will undergo changes. In this context, the issues of robustness and flexibility are of utmost importance.

*Robustness* is generally defined as the ability of a system to resist change without altering its implementation. In our thesis, robustness means that the application has a high chance of being schedulable, considering uncertainties (variations) in WCETs. For a formal definition, see Section 4.3.1, Paper C.

*Flexibility* is generally defined as the ability to adapt to change. Many things can change during the engineering of an embedded system, e.g., the initial requirements, the functionality. Also, new functions are always added in subsequent product versions. Performing changes is often very costly and requires extensive validation. For example, the time-to-market of a power-train unit in automotive industry is 24-months. Five months out of the time is used for the validation, which the percentage of validation time is more than 20% of its time-to-market [PEPP04].

In our thesis work, flexibility is defined as the likelihood of successfully implementing the future functionality changes, which have been modeled as "future scenarios" [BE06]. The detailed definition of flexibility is presented in Section 4.3.1, Paper C.

#### **1.2 Design of Embedded Systems**

The design of embedded systems is facing ever-increasing demands from the rapidly growing complexity of embedded systems and the competing constraints. The con-

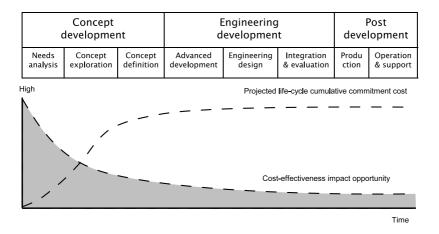

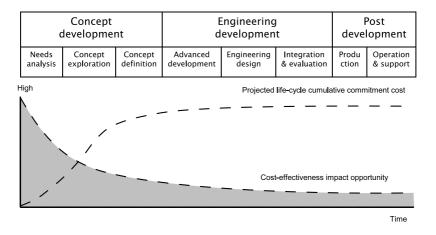

Figure 1.1: Life Cycle of Systems Engineering

straints that embedded systems should meet are measured by design metrics such as, energy consumption, cost, predictability, robustness, flexibility, reliability, which are described in the previous section,. The design methodology used in many organizations follows some versions of the "waterfall" model [Est07]. Such a methodology is inadequate for complex systems, and many other methodologies have been proposed, such as the V-model of system development [Est07].

In the following subsections, firstly we introduce the different stages of systems engineering life cycle, and then present the system-level design methodology. We continue to talk about the main challenges in designing embedded systems, which is to determine an implementation that simultaneously optimizes the competing design metrics. In the end, methods and tool for automatic design space exploration are also discussed.

#### **1.2.1** Systems Engineering Stages

There are many life cycle models used in the industry [Est07], such as waterfall models [Boe88] and V-models [FHKS09], but in principle they all have the following main stages: concept development, engineering development and post-development, see the top part of Fig. 1.1 [KSSB11]. During concept development, system engineers perform a needs analysis, do concept exploration and definition. Engineering development consists of advanced development, engineering design, integration and evaluation. Then, in post-development, the mass-production from the prototype starts, followed by the operation and maintenance of the system. In this thesis, we focus on the early design stages, see the following subsection.

#### **1.2.2 Early Decisions**

Experience from completed system design and development projects has indicated that, the cost spent for the concept development stage accounts for about 20% of the total cost. However, 80% of the cumulative cost of the system is committed already in this stage [Bue11]. Decisions made in the early design stages not only have a high impact on the subsequent implementation choices, but also have substantially negative impacts on the total cost of the system, since it is costly and time-consuming to modify and correct a decided design to other alternative designs in the engineering development stage. i.e., early decisions have a high cost-effectiveness impact opportunity.

For example [Tas02], in the context of testing the software of a system, reports that, 70% of faults are introduced in the concept development stage, while 30% are found in the engineering development stage. However, the cost for removing faults in the engineering development stage is much more expensive (5-10 times) than the case we fix them in the early design stages of concept development.

The bottom part Fig. 1.1 [SR11] shows the projected committed cumulative cost, and the impact opportunity of a design decision over time. The conclusion is that we should spent more effort on the early decisions, in order to increase the chance of completing the projects on time and successfully.

There is a lot of research on embedded systems design [Mar11,GAGS09], but very few researchers have addressed the early design stages. The challenge is that early design stages are characterized by many uncertainties.

*Uncertainty* in the context of systems engineering refers to the inability to determine precisely the state or attributes of a system. It can be caused by incomplete knowledge or by stochastic variability. A detailed discussion on the taxonomy of uncertainty is available in [Hai11].

Uncertainties in the early design stages need to be quantified, such that *risks*, defined here as the probability of not reaching design targets, of different design alternatives can be estimated for making early design decisions. In Paper C, we have modeled the uncertainties of task WCETs (Section 4.2.2), functionality requirements (Section 4.2.3), and hardware component costs (Section 4.8.1) in the early design stages, and considered them in evaluating the design metrics of robustness, flexibility and cost.

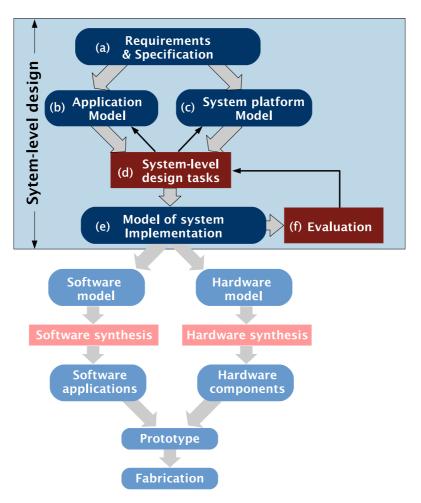

Figure 1.2: System-level Design

#### 1.2.3 System-Level Design

The aim of any design methodology is to minimize the time-to-market, and coordinate the design tasks such that design metrics are simultaneously optimized. In the embedded systems area, the design methodology is typically organized as in the Fig. 1.2. We use boxes with rounded corners for input and output information, and rectangles for design tasks. Our thesis work includes the steps which are inside the blue box. The low-level development, i.e., a full synthesis of the design solution, whose steps are under the blue box of Fig. 1.2, is outside the scope of our thesis work. In the following, we explain the system-level design process (a) - (f). (a) Besides demanding requirements on functionality, embedded systems have to meet also non-functional requirements, which are captured by the "design metrics" presented in Section 1.1.

(b) The applications are typically modeled with formalism from the particular domain. For example, the functionality of a vehicle can be described in terms of control algorithms using differential equations to model the behavior of the vehicle and its environment. Researchers have used many Models of Computation (MoC) [ELLSV97], such as *task graphs* or *synchronous data flow networks* for the modeling of embedded systems. In our thesis work, the detailed application models are presented in Sections 2.2.1 of Paper A, Sections 3.2 of Paper B and Sections 4.2 of Paper C.

(c) In our thesis work, the system platform is modeled at system level, which is viewed as a set of heterogeneous processing elements interconnected by a shared communication channel. We consider two cases for determining the system platform. One is given a fixed system platform that no modification is allowed, such a case is considered in Section 3.2, Paper B. Another is considering a system platform that can be parametrized, e.g., the number of components, the type of components, and the performance of components. We consider parametrized architectures in Section 2.2.2, Paper A and Section 4.8, Paper C.

(d) Once the application functionality and system platform have been modeled, several system-level design tasks are performed. The design tasks are typically performed automatically with the help of tools.

In our thesis work, we have considered the following system-level design tasks.

- *Function-to-task allocation* determines the decomposition options for implementing functions to tasks. In Fig. 1.2(b), an application is composed of several functionalities with safety requirements. In the early design stages, such functionalities are captured using functional blocks of different SILs. At the implementation level, the functional blocks from the design level have to be transformed into software or hardware tasks, or a combination of both. The certification standards allow several decomposition options. The function-to-task allocation problem is addressed in Paper A.

- Architecture selection determines the system platform. In Fig. 1.2(c), when the given system platform can be parametrized (in Paper A and Paper C), we may decide the number of components interconnected in the system platform, and choose the components from different types, performance and other features to build the system platform.

- *Mapping* decides the assignment of tasks to PEs and of messages to buses. The mapping problem has been tackled in all our papers included in the thesis.

- *Voltage scaling* refers to the assignment of processor operating modes (consisting of voltage/frequency pairs) to each mapped task. We consider each PE is characterized by a set of operating modes. Voltage scaling is the focus of Paper B, together with mapping.

- *Scheduling* decides the execution order of the mapped tasks on the PE or messages on the bus. In all our papers included in the thesis, tasks are scheduled using a fixed-priority preemptive scheduling, and messages are scheduled using fixed-priority non-preemptive scheduling.

(e) the outcome of Fig. 1.2(d) box is a "model of system implementation". A huge number of alternative implementation solutions will be visited during the design space explorations. Each such alternative implementation is evaluated in terms of the design metrics, captured in (f) box of Fig. 1.2.

(f) The evaluation can be done analytically or using simulation. In our thesis work, we used analytical models for evaluating a wide range of design metrics, and those models are presented in each included paper in details.

We can perform the modeling, design and evaluation of embedded systems at several abstraction levels [GK83]. From the lowest level to the highest level, there are circuit level, logic level, register-transfer level and system level. System-level design, by means of highly abstraction of modeling, is able to investigate the many alternative implementations of the system, and allows fast evaluation of each alternative, such that the exploration of a huge design space is possible.

#### **1.2.4 Design Challenges**

It is challenging to design embedded systems with complex functionality and simultaneously optimize multiple design metrics, especially when the design metrics compete with one another. Approaches used for improving a certain design metric can worsen another one. Tradeoffs must be analyzed in order to determine the best solutions that meet such an optimization challenge. In our thesis work, we have measured six design metrics, i.e., energy consumption, cost, schedulability, robustness, flexibility and reliability. Their tradeoffs are listed as follows.

• Tradeoffs between schedulability and cost, within the safety requirements.

The system-wide safety requirement is maintained if each component has been developed and operated under the given safety target. It is a common practice to decompose the system-wide safety requirements and allocate per-component safety requirement to hardware and software components, separately. However, the decomposition of function-to-task with safety requirements are not trivial. For each function with a given criticality level, there are several decomposition options, with varying impact on total cost (including the development cost of software tasks and the unit cost of hardware components) and schedulability of the implementation.

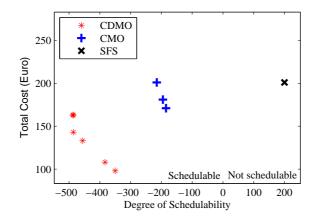

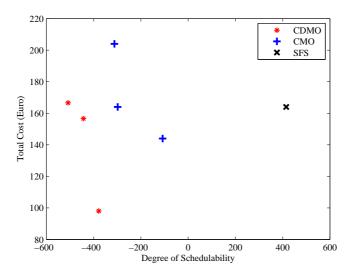

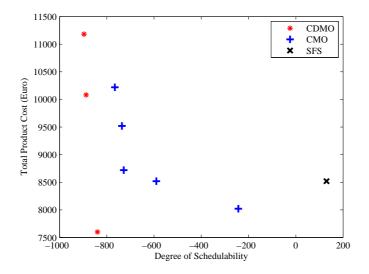

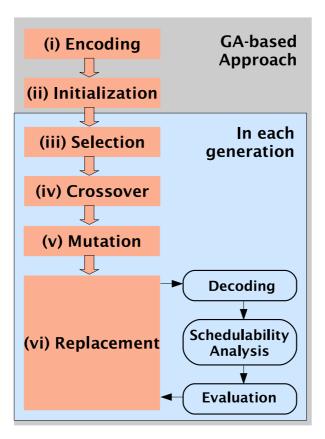

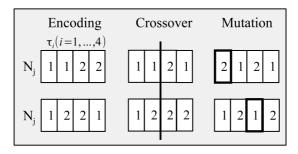

In Paper A, we have considered mixed-criticality applications to be implemented on distributed architectures. We have proposed a GA-based approach to decide the function-to-task allocation, the mapping of tasks to PEs and the reliability of each PE, such that the safety requirements are preserved, the development and unit costs are minimized, and the schedulability is maximized.

• Tradeoffs between energy consumption and schedulability, within the reliability requirements.

The most common approach for energy minimization that allows energy and performance trade-offs during run-time of the application is *Dynamic Voltage Scaling (DVS)* [SAHE03]. DVS aims at reducing the dynamic power consumption by scaling down operational frequency and circuit supply voltage, while adapting the component (PE or communication link) performance to the actual requirement of the system. A considerable amount of work has been done on DVS, see [SAHE03] for a survey.

However, lowering the operating voltage and frequency not only decreases the performance, but also increases the number of transient faults exponentially. The main reason for such an increase is that, with lower voltages, even very low energy particles are likely to create a critical charge that leads to a transient fault. Moreover, the redundancy-based fault-tolerance techniques (such as replication) and DVS-based low-power techniques compete for the available slack.

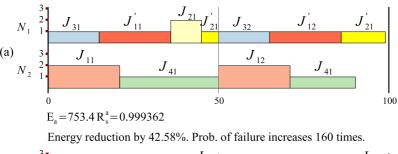

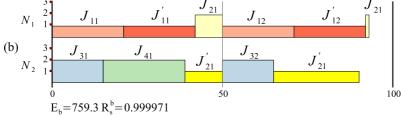

In Paper B, we addressed the mapping, voltage and frequency scaling for faulttolerant hard real-time applications mapped on distributed embedded systems. We captured the effect of voltage and frequency scaling on system reliability, and we showed that if the supply voltage and the operating frequency are lowered to reduce energy consumption, reliability is significantly reduced. We have prepared an offline synthesis approach, based on a Tabu Search metaheuristic, which decides the mapping and operating mode for each task such that the energy is reduced and the schedulability and reliability constraints are satisfied. We have also proposed an online scheduling approach, which considers the mapping determined by offline synthesis approach and decides at runtime the operating mode for each job such that the energy is further reduced, while guaranteeing the timing and reliability constraints.

• Tradeoffs among robustness, flexibility, and cost.

In the early design stages of building a new system version, the choice of reusing legacy architecture components, using or upgrading to new components has a

significant impact on the robustness, flexibility and architecture cost of the new system version. In the case we choose to use new hardware components, with improved metrics such as better performance, or lower power dissipation, we may need to redevelop and validate the system platform which results in high costs for this new architecture solution and high uncertainties in evaluating the WCET of tasks. In case we migrate the legacy hardware components from the previous products, the cost of such an architecture solution should be much less than that in the former case, and the task WCET are more certain as well, but we may not benefit from the improved metrics of the new architecture.

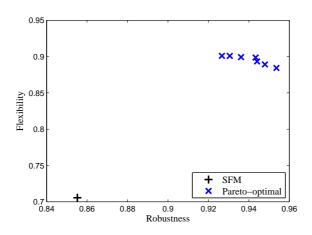

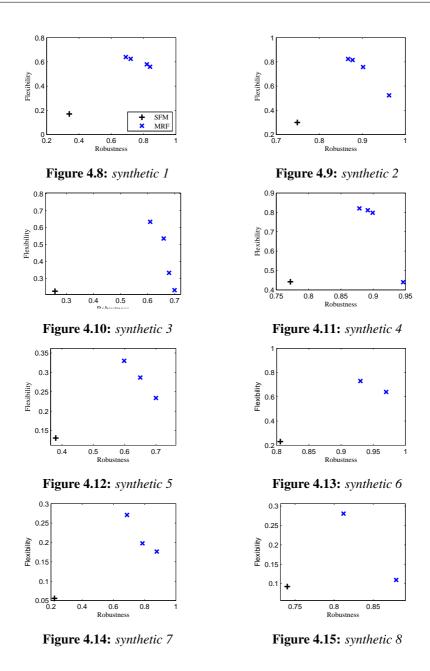

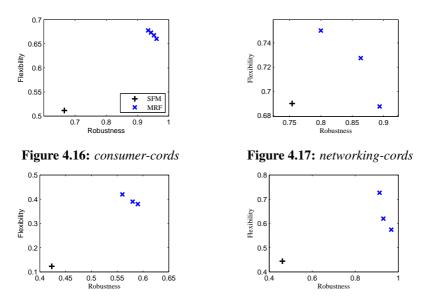

In Paper C, we have addressed the architecture selection and the mapping of hard real-time applications on distributed heterogeneous architectures, during the early design phases. We have proposed a GA-based optimization for architecture selection and task mapping, targeting robustness, flexibility, and cost, which takes into account the uncertainties in WCETs, functionality requirements, and hardware component costs respectively. The proposed model allows the system designer to make the early design decisions after considering the tradeoff among robustness, flexibility, and cost.

#### **1.2.5 Design Space Exploration**

*Design space exploration (DSE)* is the process of visiting and analyzing the design alternatives to identify good quality solutions. The search in design space is presented in the three arrows which repeatedly visits new design alternatives in (b), (c) and (d) in Fig. 1.2. The design alternative are created by performing design tasks presented in Section 1.2.3.

DSE can be done manually, which is often the case in practice, but this is very inefficient for designing complex systems. In our thesis, we do automatic DSE supported by tools, and the search in the automatic DSE tool is implemented using optimization algorithms, in order to determine the good quality solutions in a reasonable time.

We consider m-dimensional space X of possible design alternatives, and F is the n-dimensional space of values for each objectives, i.e., design metrics.

$$F(x) = opt(f_1(x), \cdots, f_n(x)) \tag{1.1}$$

where  $x \in X$ , *opt* could be minimize or maximize the objectives, e.g., minimizing  $f_1(x)$  and maximize  $f_2(x), \dots, f_n(x)$ .

A design solution  $x \in X$  is called *Pareto-optimal* with respect to X iff there is no design  $y \in X$  such that u = F(x) is dominated by v = F(y).

In our thesis work, we consider simultaneously optimizing multiple competing design metrics. In Paper B, we merge all design metrics into a single objective function by using a weighted average, and determine one optimized solution, while in Paper A and Paper C, we perform multiobjective optimization, which aims to determine Pareto-front of solutions.

In general, there are exact methods, such as integer/mixed linear program formulation, and heuristics, such as Tabu Search (TS) or Genetic Algorithm (GA), for solving the multiobjective optimization problems. In our thesis work, the optimization problems we addressed (in Paper A, Paper B and Paper C) are NP-hard. In order to find high quality solutions in a reasonable time, we proposed a TS-based heuristics in Paper B, and used a GA-based heuristics for multiobjective optimization in Paper C.

#### **1.3** Thesis Objective and Contribution

The objective of this thesis is to propose design methods and tools for the design of embedded systems. We are interested in addressing competing design metrics such as energy consumption, cost, schedulability, reliability, robustness and flexibility, and to support the designer making early design decisions during the early design phases, which are characterized by uncertainties. The proposed methods have been implemented in optimization tools which use advanced optimization techniques to determine good quality solutions in a reasonable time.

The following papers and contributions have been included in the thesis:

• Paper A: Gan, Junhe, Paul Pop, Domitian Tamas-Selicean and Jan Madsen. "Criticality-Aware Functionality Allocation for Distributed Real-Time Embedded Systems." To be submitted to International Journal of Reliability, Quality and Safety Engineering (IJRQSE). A preliminary version of this paper has been accepted to the Design, Automation and Test in Europe (DATE) conference workshop: Performance, Power and Predictability of Many-Core Embedded Systems (3PMCES), 2014.

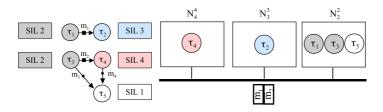

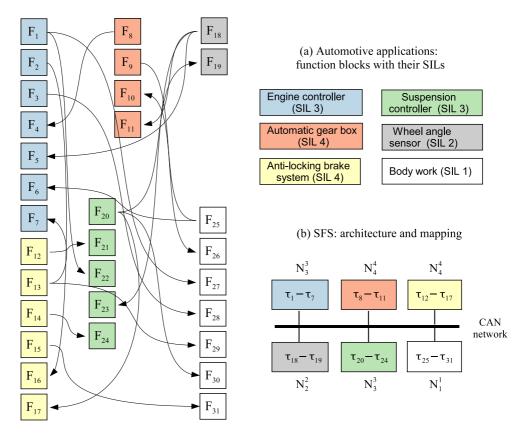

Gan, Junhe, Paul Pop and Jan Madsen. "Criticality-Aware Functionality Allocation for Distributed Multicore Real-Time Systems." In the Design, Automation and Test in Europe (DATE) conference workshop: Performance, Power and Predictability of Many-Core Embedded Systems (3PMCES), 2014. In this paper, we are interested in implementing mixed-criticality hard real-time applications on a distributed heterogeneous hardware architecture, consisting of a set of processing elements (PEs) interconnected by a shared bus. We assume that the architecture provides the required separation mechanisms for mixed-criticality applications. An application is modeled as a set of functional blocks, with different Safety-Integrity levels (SILs), which dictate the development processes and certification procedures that have to be followed. Before the applications are implemented, the functional blocks have to be decomposed into software tasks. There are several decomposition options, which use redundancy and diversity to achieve the desired SIL. We are interested to determine (1) the function-to-task allocation, (2) the mapping of tasks to PEs, and (3) the reliability of each PE, such that the total cost is minimized, the application is schedulable and the safety and integrity constraints are satisfied. The proposed algorithm has been evaluated using a synthetic benchmark and a real-life benchmark.

• Paper B: Gan, Junhe, Paul Pop, Flavius Gruian and Jan Madsen. "Reliability-Aware Dynamic Energy Management for Fault-Tolerant Distributed Embedded Systems." To be submitted to ACM Transactions on Design Automation of Electronic Systems (TODAES). A preliminary version of this paper has been published at the Asia and South Pacific Design Automation Conference (ASP-DAC), 2011.

Junhe Gan, Flavius Gruian, Paul Pop and Jan Madsen. "Energy/Reliability Trade-Offs in Fault-Tolerant Event-Triggered Distributed Embedded Systems" In Proceedings of the 16th Asia and South Pacific Design Automation Conference, pp. 731 - 736. IEEE Press, 2011.

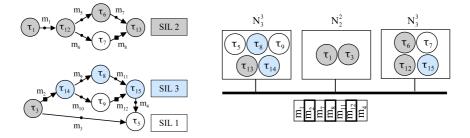

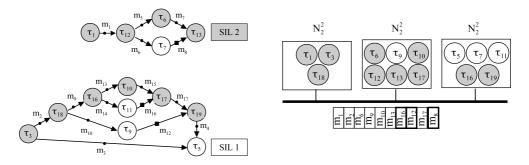

This paper presents an approach to the synthesis of low-power fault-tolerant hard real-time applications mapped on distributed heterogeneous embedded systems. We first propose a design-time (offline) synthesis approach which decides the mapping of tasks to processing elements, as well as the voltage and frequency levels for executing each task, such that transient faults are tolerated, the timing constraints of the application are satisfied, and the energy consumed is minimized. Tasks are scheduled using fixed-priority preemptive scheduling, while replication is used for recovery from multiple transient faults. Addressing energy and reliability simultaneously is especially challenging, since lowering the voltage to reduce the energy consumption has been shown to increase the transient fault rate. We present a Tabu Search-based approach which uses an energy/reliability trade-off model to find reliable and schedulable implementations which minimizes the energy consumption. We also propose a runtime (online) synthesis algorithm, which changes dynamically the voltage and frequency levels of running tasks to reduce further the energy consumption, while guaranteeing the schedulability of the application and its fault-tolerance to transient faults. To provide such guarantees, the offline synthesis has to assume the worst-case, i.e., that tasks will execute up to their worst-case execution times, and the maximum faults will occur. The online scheduling will know at runtime the actual

execution times of tasks and the fault occurrences. We evaluated the proposed synthesis approaches using several synthetic and real-life benchmarks.

• Paper C: Gan, Junhe, Paul Pop and Jan Madsen. "Design for Robustness and Flexibility of Real-time Distributed Applications during the Early Design Phases." To be submitted to Journal of Systems and Software (JSS). A preliminary version of this paper has been published at the Design, Automation and Test in Europe (DATE) conference, 2012.

Gan, Junhe, Paul Pop, Flavius Gruian and Jan Madsen. **Robust and Flexible Mapping for Real-Time Distributed Applications during the Early Design Phases.**" In Proceedings of the Conference on Design, Automation and Test in Europe, pp. 935 – 940. EDA Consortium, 2012.

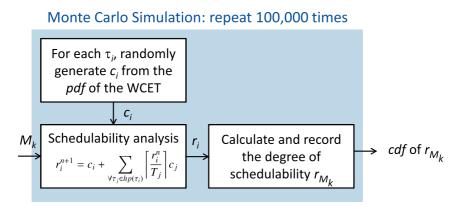

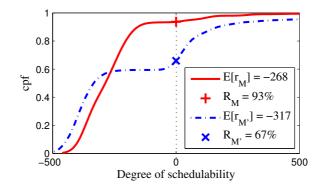

We are interested in mapping hard real-time applications on distributed heterogeneous architectures. An application is modeled as a set of tasks, and we consider a fixed-priority preemptive scheduling policy. We target the early design phases, when decisions have a high impact on the subsequent implementation choices. However, due to a lack of information, the early design phases are characterized by uncertainties, e.g., in the Worst-Case Execution Times (WCETs) or in the functionality requirements. We model uncertainties in the WCETs using the "percentile method". The uncertainties in the functionality requirements are captured using "future scenarios", which are task sets that model functionality likely to be added in the future. In this context, we derive a mapping of tasks in the application, such that the resulted implementation is both robust and flexible. Robust means that the application has a high chance of being schedulable, considering the WCET uncertainties, whereas a flexible mapping has a high chance to successfully accommodate the future scenarios. We propose a Genetic Algorithm-based approach to solve this optimization problem. We also show how this problem can be extended to consider the architecture selection: deciding what hardware components to use in the architecture. In this context, we consider the uncertainties related to hardware component costs. Extensive experiments show the importance of taking into account the uncertainties during the early design phases.

### CHAPTER 2

# Paper A: Criticality-Aware Function-to-Task Allocation for Distributed Real-Time Embedded Systems

In this paper, we are interested in implementing mixed-criticality hard real-time applications on a distributed heterogeneous hardware architecture, consisting of a set of processing elements (PEs) interconnected by a shared bus. We assume that the architecture provides the required separation mechanisms for mixed-criticality applications. An application is modeled as a set of functional blocks, with different Safety-Integrity levels (SILs), which dictate the development processes and certification procedures that have to be followed. Before the applications are implemented, the functional blocks have to be decomposed into software tasks. There are several decomposition options, which use redundancy and diversity to achieve the desired SIL. We are interested to determine (1) the function-to-task allocation, (2) the mapping of tasks to PEs, and (3) the reliability of each PE, such that the total cost is minimized, the application is schedulable and the safety and integrity constraints are satisfied. The proposed algorithm has been evaluated using a synthetic benchmark and a real-life benchmark.

# 2.1 Introduction

*Safety* is a property of a system that will not endanger human life or the environment. *Safety-Integrity Levels* (SILs) are assigned to safety-related functions to capture the required level of risk reduction, and will dictate the development processes and certification procedures that have to be followed [IEC10], [ISO09], [RTC92]. There are four SIL levels, ranging from SIL 4 (most critical) to SIL 1 (least critical). Certification standards require that safety functions of different criticality levels are *protected* (or, *isolated*), so they cannot influence each other. For example, without protection, a lower-criticality task could corrupt the memory of a higher-criticality task.

The "Research Agenda for Mixed-Criticality Systems" [BBB<sup>+</sup>09] defines a *mixed*criticality system as "an integrated suite of hardware, operating system and middleware services and application software that supports the execution of safety-critical, mission-critical, and non-critical software within a single, secure computing platform". Many such applications, following physical, modularity or safety constraints, are implemented using distributed architectures, composed of several different types of hardware components (called *nodes*), interconnected in a network. Initially, each function was implemented in a separate node, which has led to a large increase in the number of nodes.

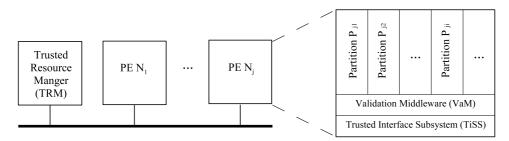

The current trends are towards "integrated architectures", where several functions are integrated onto the same node. In this context, designers are relying on partitioning mechanisms at the platform level. For example, in the avionics area, the partitioned architecture is called "Integrated Modular Avionics" (IMA) [Ari97], and the platform-level separation mechanisms are provided by implementations of the ARINC 653 standard [Ari13]. ARINC 653 consists of hardware-mediated operating system-level *spatial* and *temporal* partitioning mechanisms [Rus99]. Similar platform-level separation mechanisms are available in other industries [Ern10,LSOH07, PTV<sup>+</sup>13].

In this paper we are interested in the implementation of mixed-criticality hard real-time applications on integrated distributed architectures. The functionality of such applications is captured in the early design stages using functional blocks of different SILs. Before the applications are implemented, the functional blocks have to be decomposed into software tasks. For example, in the automotive area [CGL+07], the functionality is captured at the "Vehicle" and "Analysis" levels using functional blocks. During the "Design" level these functions are decomposed into tasks, which are implemented on the target architecture in the "implementation" level.

SIL allocation of functional blocks is typically a manual process, which is done after performing hazard and risk analysis, but researchers have proposed automatic approaches for SIL allocation [PWR<sup>+</sup>10a]. However, no automatic approaches have been proposed for the function-to-task allocation.

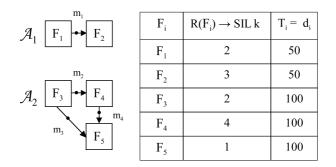

The function-to-task allocation problem is not trivial, since, for each function with a given SIL k, there are several decomposition options. For example, for a SIL 3 function, the automotive certification standard ISO 26262 [ISO11] allows several possible decompositions: a SIL 3 task; a SIL 2 task and a SIL 1 task; further, the SIL 2 task from the previous decomposition can be further decomposed into two SIL 1 tasks. Decomposing a SIL 3 function into two or even more tasks of lower SILs may reduce the development and certification costs. Such decompositions rely on redundancy and software diversity to achieve the desired SIL level using lower SIL tasks.

The decomposition will have an impact on the total cost and the schedulability of the implementation. The development and certification costs of a software task grow exponentially with each SIL [IBM10]. We assume that for each SIL k we have a corresponding required reliability  $R_k$  of processing element (PE). That is, high-criticality tasks are only allowed to be mapped on a correspondingly high reliability PE. Our optimization approach decides the type of PEs to be used in the architecture, and high-reliability PEs are more expensive, which impacts the total cost. In addiction, the function-to-task decomposition will affect schedulability, because it may introduce additional tasks to be scheduled and because it may require message validation for communication integrity, which introduces additional overheads.

We consider heterogeneous distributed platforms, consisting of several PEs interconnected using a broadcast bus. We assume that the platform provides both spatial and temporal partitioning, thus enforcing enough separation for the mixed-criticality applications. The separation among mixed-criticality tasks also affects the communication. For example, integrity models require that a task can only receive an input from a task of the same criticality level or higher than its own. In this paper we consider that ACROSS integrity model [Was14], which allows lower-criticality tasks to send messages to higher-criticality tasks if they pass first through a validation middleware. We assume that the platform provides such a validation middleware to be used for communication integrity.

Each partition can have its own scheduling policy. However, to simplify the discussion, in this paper, we assume that all applications are scheduled using Fixed-Priority Preemptive Scheduling (FPPS). Although we address hard real-time applications, (non-critical) soft real-time applications can also be handled using a technique such as the Constant Bandwidth Server [AB98], where the server is seen as a hard task providing a desired level of service to soft tasks.

We assume that the communication protocol has mechanisms to enforce partitioning at the bus level. For example, space partitioning is attained in SAFEbus [HD93] by mapping the messages to unique locations in the inter-module memory, protected by a memory-mapping hardware in the host, and temporal partitioning is achieved in TTP [Kop11a] by enforcing a Time-Division Multiple Access scheme. TTEthernet [AS 11] offers spatial separation for mixed-criticality messages through the concept of virtual links, and temporal separation, enforced through schedule tables for time-triggered messages and bandwidth allocation for rate constrained messages. Researchers have shown how realistic bus protocols such as TTP [PEP04], FlexRay [PPE<sup>+</sup>08] and TTEthernet [TSPS12b] can be taken into account during the design. However, in this paper we consider a simple bus where messages are transmitted using a fixed-priority non-preemptive policy.

Given a mixed-criticality application modeled as a set of safety functions to be implemented on such a distributed architecture, we are interested to determine the functionto-task decomposition, the type of PEs in the architecture and the mapping of tasks to the PEs, such that the total cost is minimized, the application is schedulable and the safety and integrity constraints are satisfied.

## 2.1.1 Related Work

There is a large amount of research on hard real-time systems [Kop11a, But97], including task mapping to heterogeneous architectures [BSB<sup>+</sup>01]. Researchers have also started to address the mapping problem in the context of mixed-criticality systems [TSP11a], where the problem is to decide the assignment of tasks to partitions and the mapping to PEs such that the applications are schedulable. The work in [TSP11a] can also decide to "elevate" a task, i.e., raise its SIL, if this is needed to improve the schedulability, and uses a SIL-related development cost model to support the reduction of the overall cost.

The problem of deciding the SIL of a safety function is typically a manual process, which is done after performing hazard and risk analysis. in this context, researchers have started to propose automatic approaches to this problem, which is called "SIL allocation" [PWR<sup>+</sup>10b]. A more broader view is taken by [SBK], which propose a method for the propagation, transformation and refinement of safety requirements in general.

Some of the work on SIL allocation addresses also SIL decomposition (which they call "SIL algebra"), but in the context of safety functions implemented using hardware architectures [PWA<sup>+</sup>13, APW<sup>+</sup>13, BDS11]. [PWA<sup>+</sup>13] have proposed a Genetic Algorithm for SIL decomposition and [APW<sup>+</sup>13] have proposed a Tabu Search metaheuristic. Both works aim at a SIL decomposition which reduces the development costs, and are interested in deriving a fault-tolerant architecture. The safety of the resulted architecture is evaluated using Fault-Tree Analysis.

Researchers have proposed [BDS11] a tool called DALculus for the automatic allocation of SILs (which in the avionics area are called "Design Assurance Levels" or DAL) such that the smallest DAL possible is allocated to a function in order to minimize costs, while following the recommended practices in the avionics area. The rules from [ARP10] and the architecture constraints are formulated as a constraint satisfaction problem and solved with an existing solver.

However, when preforming SIL allocation and decomposition at the level of safety function, special case has to be taken not to abuse the SIL concept, which is not a measure of safety, but a way to dictate the development process rigor, and which cannot be decomposed unless "sufficient independence" can be shown between the requested functionalities [WC12].

Other related works are in the context of the automatic transformation of structural models to runtime models. For example, [KWS03] have proposed an automatic transformation of structural models (components and their interaction) to runtime models (tasks that communicate via message), taking into account real-time constraints. Their method also does priority assignment and thread mapping. The transformation of component models to tasks is also addressed in [FÅS04]. Thus, real-time components which model the desired functionality at "design time" are transformed into tasks at the "runtime" level. The authors propose a Genetic Algorithm-based approach to solve this transformation problem. Their work is limited to single-processor systems.

[FDT05] have looked at transforming functional blocks at the level of the "functional architecture" to Timed Petri Nets (TPNs) at the "runtime platform" level, deciding at the same time the links between the functions and resources, which from the "operational architecture". None of these works address safety-critical systems and the SIL decomposition.

We have proposed a Genetic Algorithm-based optimization approach, which decides the decomposition of functions to tasks, the mapping of tasks to PEs and the type of PEs to be used in the architecture, such that the costs are minimized, the safety and integrity constraints are satisfied and the schedulability of the applications is guaranteed.

The paper is organized as follows. The next section present the system models considered. We formulate the problem and illustrate a motivational example in Section 2.3. The proposed a Genetic Algorithm-based approach is presented in Section 2.4, and is evaluated using a synthetic and a real-life benchmarks in Section 2.5. We draw the conclusion in the last section.

# 2.2 System Model

#### 2.2.1 Application Model

The set of all applications in the system is denoted with  $\Gamma$ . At the design level, we model an application as *functional blocks*. Functional blocks have input and output ports and communicate with each other with directional links, which connect the output port of a functional block to the input port of another functional block. We assume that there are no loops in this communication (if loops are present, they can be unrolled).

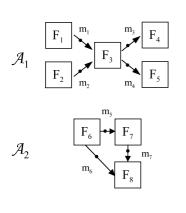

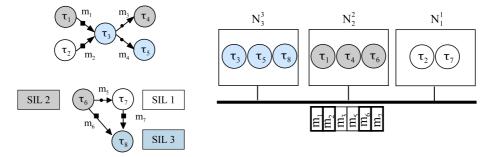

All the functional blocks in the system are modeled as a graph  $\mathcal{G}(\mathcal{F}, \mathcal{E})$ , where each node  $F_i \in \mathcal{F}$  is a functional block, and an edge  $e_{ij} \in \mathcal{E}$  from  $F_i$  to  $F_j$  denotes a data dependency between an output port of  $F_i$  and an input port of  $F_j$ . We use fixed-priority preemptive scheduling at the PE-level, hence we assume that we know the period  $t_i$  and deadline  $d_i$  of each functional block  $F_i$ . If dependent functional blocks have different periods, they are combined into a merged graph capturing all activations for the hyperperiod (least common multiple of all periods).

As mentioned, a *safety-critical* system should not endanger human life or the environment. A *hazard* is a situation in which there is actual or potential danger to people or to the environment. *Risk* is a combination of the frequency or probability of a specified hazardous event, and its consequence. If, after performing an initial hazard and risk analysis, a system is deemed safety-related, it has to be certified [Sto96]. Certification is a "conformity of assessment" performed by a third party, e.g, an independent organization or a national authority, namely a "certification authority".

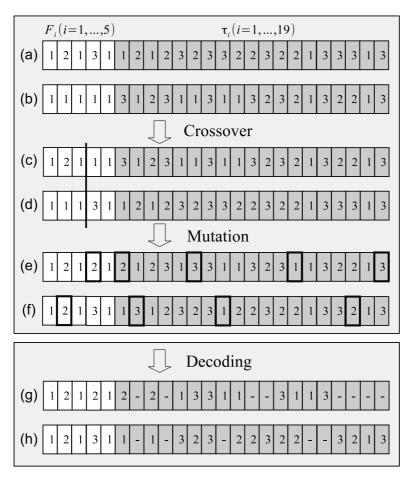

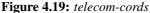

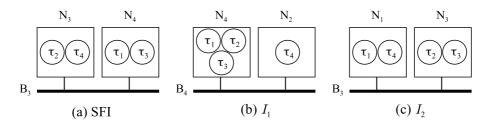

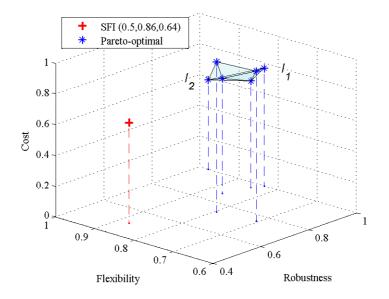

The current certification practice is "standards-based" [Rus07], and requires that the product and the development processes fulfill the requirements and satisfy the objectives of a certain certification standard, depending on the application area. For example, [IEC10] is used in industrial applications, [ISO09] is for the automotive area, whereas [RTC92] refers to software for airborne systems.