#### Micromachined Integrated 2D Transducers for Ultrasound Imaging

Havreland, Andreas S.

Publication date: 2019

Document Version Publisher's PDF, also known as Version of record

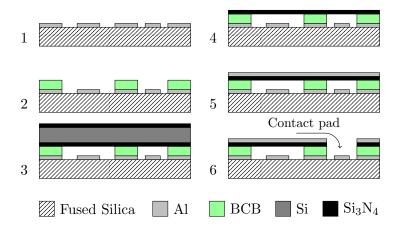

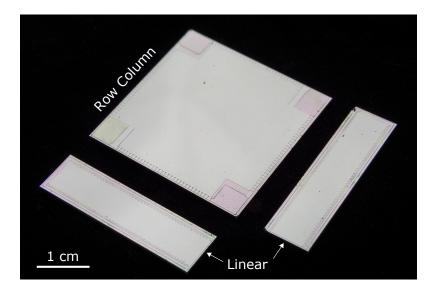

Link back to DTU Orbit

*Citation (APA):* Havreland, A. S. (2019). *Micromachined Integrated 2D Transducers for Ultrasound Imaging*. DTU Health Technology.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## TECHNICAL UNIVERSITY OF DENMARK

## Ph.D. Thesis

# MICROMACHINED INTEGRATED 2D TRANSDUCERS FOR ULTRASOUND IMAGING

Author: Andreas S. Havreland Supervisors: Prof. Erik V. Thomsen Prof. Jørgen A. Jensen

$14^{st}$  September 2019

Kgs. Lyngby, Denmark

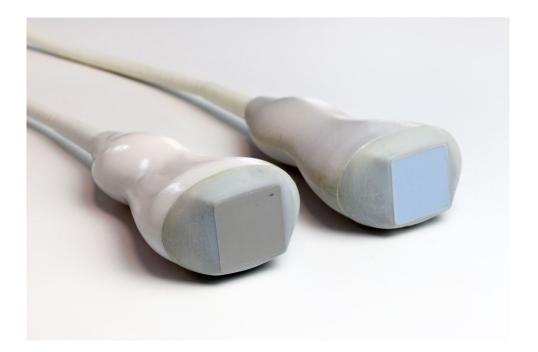

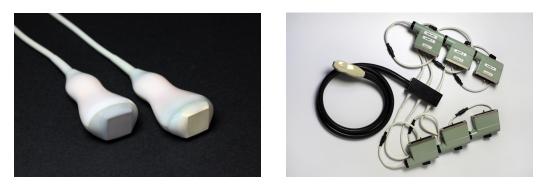

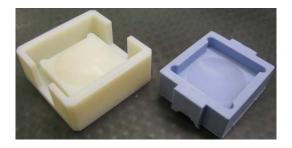

**Cover image:** Two row-column addressed ultrasound probes developed in this work. Photo by Jesper Scheel.

Technical University of Denmark Department of Health Technology Ørsteds Plads 345C 2800 Kgs. Lyngby DENMARK Tel: (+45) 4525 5700 Fax: (+45) 4588 7762 Web: www.healthtech.dtu.dk Author e-mail: ahav@dtu.dk

## Preface

This PhD thesis has been submitted to the Technical University of Denmark, in partial fulfillment of the requirements for the degree of Doctor of Philosophy. The work has been supervised by Professor Erik Vilain Thomsen and Professor Jørgen Arendt Jensen. This thesis consists of a recapitulation of the research work carried out from September 2016 to September 2019 at DTU Health Tech, Technical University of Denmark.

The MEMS group has conducted research within the field of Capacitive Micromachined Ultrasonic Transducer (CMUT) for several years, and profound knowledge of the CMUT technology was therefore already established before my project.

Andrews Harmland

Andreas Havreland Kgs. Lyngby, September 2019

PREFACE

iv

## Summary

Conventional ultrasound imaging produces 2D images of the human body, and these images are today routinely used for diagnostics purposes. The twodimensi images can efficiently be displayed on a computer screen and are easy to interpret, whereas 3D images are more difficult to interpret but provide additional information about the imaged objects. The added dimension in a 3D image can provide vital information and can be used for new innovative imaging techniques. However, the complexity of the underlying transducer technology increases enormously when the imaging capabilities go from 2D to 3D. New advances in the transducer technology, such as row-column addressed arrays, drastically reduce the complexity of ultrasound systems capable of 3D imaging. The row-column technology reduces the required number of electrical interconnection from  $N^2$  to 2N, where N is the number of channels in the ultrasound system. The main goal of this thesis is to develop the row-column addressed transducer array. The technology of capacitive Micromachined Ultrasound Transducers (CMUT) is used for the development platform for the row-column arrays due to the high flexibility and desired imaging properties offered by this technology.

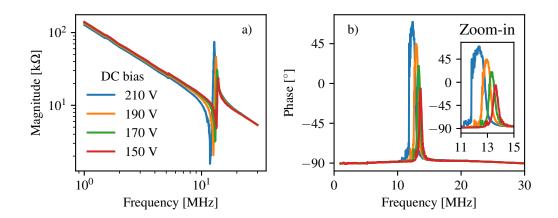

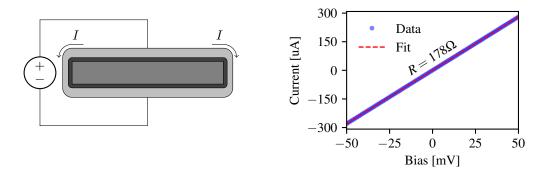

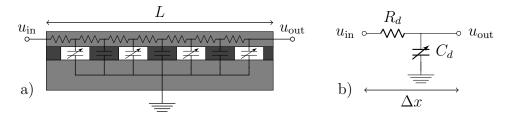

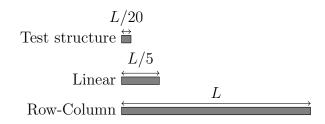

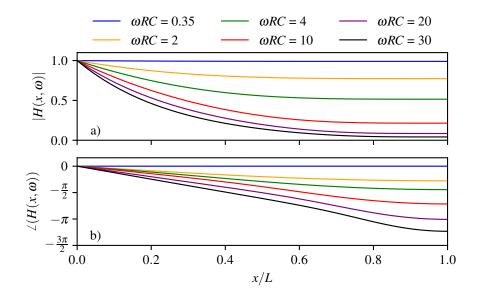

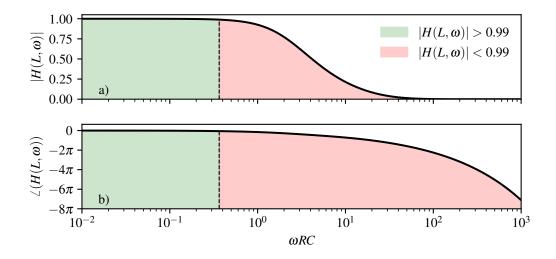

Theoretical analysis of a CMUT is presented in the first part of thesis, including investigation of the static and dynamic properties. Multiple CMUT fabrication methods are developed, demonstrated, and used to fabricate various row-column arrays of different sizes. The area of row-column addressed arrays can be larger than conventional ultrasound transducers which introduces new challenges that has to be addressed. These challenges included increased resistance in the electrodes, and a design criterion for sufficient resistance of long row-column elements is derived and experimentally documented.

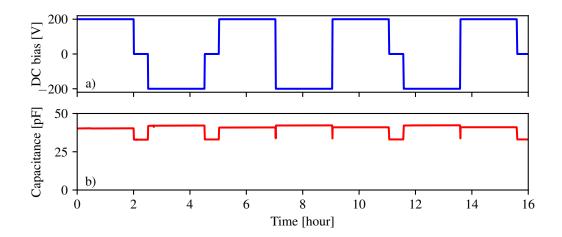

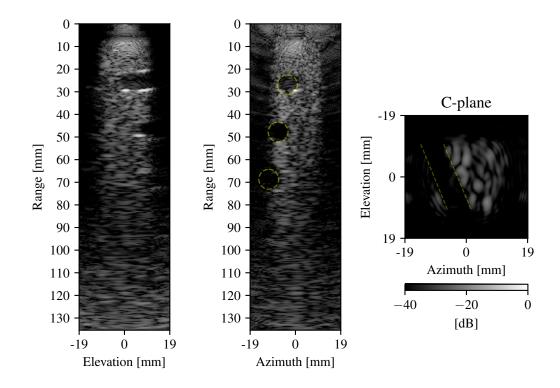

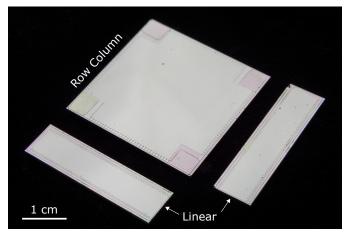

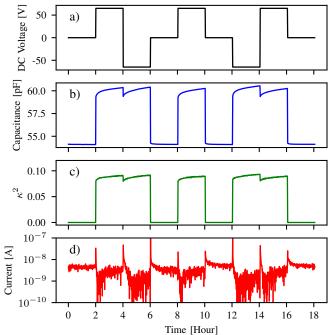

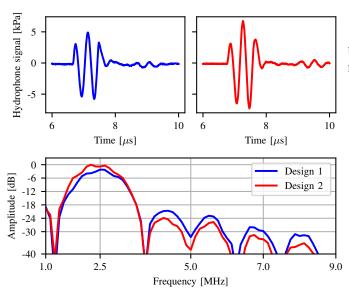

Two 92+92 4.5 MHz row-column addressed CMUT arrays are assembled into ultrasound probes. The CMUT probes are electrically characterized, long term stability test during 16 h showed no sign of dielectric charging and the electromechanical coupling coefficient is estimated to be 18.3%. The acoustical performance of the probes are characterized and 3D imaging capabilities are demonstrated at a depth of 7 cm in a cyst phantom.

vi

#### Resumé

Ultralydsbilleddannelse bliver rutinemæssigt brugt til diagnosticering i medicinsk sammenhæng. Konventionelt er ultralydsbilleder i 2D, hvilket både gør det nemt at fortolke og afbillede på en computerskærm, hvorimod 3D-billeder er sværere at fortolke men indeholder mere information om det afbillede objekt. Den ekstra dimension i 3D- billede kan give livsvigtig information og bane vejen for nye billedeteknikker. Men kompleksiteten af den bagvedliggende transducerteknologi stiger voldsomt når man går fra 2D til 3D. Den nyeste udvikling af transducerkoncepter, såsom række-søjle adressering, reducerer denne kompleksitet drastisk. Række-søjle-adressering reducerer antallet individuelle elektriske forbindelse fra  $N^2$  til 2N, hvor N er antallet af kanaler i ultralydssystemet. Hovedfokuset i denne afhandling er at udvikle transducere på teknologien bag rækkesøjle-adressering. Til at facilitere denne udvikling er teknologien baseret på kapacitive mikrofremstillet ultalydstransducer (CMUT) valgt som platform. Dette valg er grundet fleksibilitet og den øget billedkvalitet som CMUT teknologien tilbyder.

Den første del af afhandlingen indeholder en teoretisk analyse af en CMUT, som inkluderer en gennemgang af de statiske og dynamiske egenskaber. Derudover bliver flere forskellige CMUT fabrikationsmetoder gennemgået, demonstreret, og brugt til at fabrikere række-søjle adresseret CMUT transducere i forskellige størrelser. Arealet af en række-søjle adresset CMUT kan blive betydlig større end konventionelle ultralyds transducere hvilket medfører nogle problemstilling, der skal håndteres i CMUT design processen. Et af disse problemer er øget elektrisk modstand, og et kriterium for den højeste tilladte modstand i elektroderne er udledt og eksperimentelt demonstreret i denne afhandling. To 92+92 4.5 MHz MHz række-søjle adresseret CMUT transducere er blevet samlet til en ultralydsprobe, og disse prober er akustisk karakteriseret og har demonstreret 3D ultralydsbilleddannelse ned til 7 cm dybde på et cystefantom.

RESUMÉ

viii

## Acknowledgements

First of all I would like to thank my supervisor Prof. Erik V. Thomsen and my co-supervisor Prof. Jøregn Arendt Jensen. I have learned many things from both of you during the past three years on a personal and professional level. It has been a great experience for me to participate in the important research you are conducting.

Then I would like thank my colleagues at DTU Health Tech. Thank you for making my time as a PhD student very joyful. A special thank you goes to my office mate Martin Lind Ommen for always providing a friendly atmosphere at our office and equally important thank you for all the constructive professional debates we have had on various subjects. Thanks to all the students that I have supervised, you have been an important part of the CMUT development in the MEMS group.

I would also like to thank our partners at BK Medical and DTU Nanolab for facilitating the research conducted in this thesis. A proper thank you should also be given to Jan Bagge for his lessons regarding CMUT electronics.

Last, but not least, a huge thanks goes to my family for the continuous support. First and foremost to you Mathilde. Thank you for the endless support and love you have provided.

## Acronyms

${\bf AFM}\,$  Atomic Force Microscope

ASIC Application Specific Integrated Circuit

BCB BenzoCycloButene

BHF Buffed HydroFluoric acid

BOX Burried OXide

**CMP** Chemical Mechanical Polishing

CMUT Capacitive Micromachined Ultrasonic Transducer

**CT** Computed Tomography

${\bf CV}$  Capacitance-Voltage

**DREM** Deposit, Remove, Etch, Mask

$\mathbf{DTU}~$  The Technical University of Denmark

${\bf EFE}$  EigenFunction Expansion

${\bf FBW}\,$  Fractional BandWidth

FORCES Fast Orthogonal Row–Column Electronic Scanning

${\bf FPM}\,$  Fully Populated Matrix

#### Acronyms

#### **FWHM** Full Width Half Max

**IUS** International Ultrasound Symposium

**IV** Current-Voltage

KOH potassium hydroxide

LOCOS Local oxidation of silicon

**LPCVD** Low Pressure Chemical Vapour Deposition

**MMS** Method of Multiple Scales

${\bf MR}\,$  Magnetic Resonance

PCB Printed Circuit Board

**PDMS** polydimethylsiloxane

**PECVD** Plasma Enhanced Chemical Vapour Deposition

**PMUT** Piezoelectric Micromachined Ultrasonic Transducers

**PSOI** Poly-Silicon-On-Insulator

**PZT** ceramic material with piezoelectric properties

- $\mathbf{RCA}$  Row-Column-Addressed

- $\mathbf{RMS}$  Root mean square

- **SEM** Scanning Electron Microscope

${\bf SNR}\,$  Signal to Noise Ratio

${f SOI}$  Silicon-On-Insulator

**SPM** Sparsely Populated Matrix

**TOBE** Top-Orthogonal-to-Bottom-Electrode

## Nomenclature

## CMUT array

| $A_{\rm trans}$ | Area of transducer surface                       | $[m^2]$       |

|-----------------|--------------------------------------------------|---------------|

| $f_0$           | Center frequency                                 | [Hz]          |

| L               | Length of an element                             | [m]           |

| N               | Number of channels                               | [#]           |

| W               | Width of an element                              | [m]           |

| Singl           | e CMUT cell                                      |               |

| A               | Area of a single CMUT cell                       | $[m^2]$       |

| a               | Radius of a single CMUT cell                     | [m]           |

| F               | Force (frequency domain)                         | $[N \cdot s]$ |

| $f_{RI}$        | Force from the radiation impedance (time domain) | [N]           |

| g               | Gap height in CMUT cavity                        | [m]           |

| h               | Thickness of the CMUT plate                      | [m]           |

| $k_s$           | Linear spring constant of CMUT                   | [N/m]         |

| m               | Mass of a single CMUT cell                       | [kg]          |

| U               | Applied DC bias                                  | [V]           |

#### A cronyms

| $U_{pi}$ | Pull-in voltage                               | [V]                        |

|----------|-----------------------------------------------|----------------------------|

| V        | Velocity of the CMUT plate (frequency domain) | [m]                        |

| v        | Velocity of the CMUT plate (time domain)      | [m/s]                      |

| x        | Displacement of the CMUT plate                | [m]                        |

| Ζ        | Radiation impedance (frequency domain)        | [kg/s]                     |

| z        | Radiation impedance (time domain)             | $[kg/s^2]$                 |

| Mat      | erial properties                              |                            |

| $ ho_m$  | Density of medium                             | $[\mathrm{kg/m^3}]$        |

| $ ho_p$  | Density of plate                              | $[kg/m^3]$                 |

| ρ        | Resistivity                                   | $[\Omega\cdot\mathrm{cm}]$ |

| $c_m$    | Speed of sound                                | [m/s]                      |

| Oth      | er                                            |                            |

| λ        | Wavelength                                    | [m]                        |

| ω        | Angular frequency                             | [rad]                      |

| ε        | Permittivity                                  | [F/m]                      |

| $A_c$    | Cross-sectional area                          | $[m^2]$                    |

| C        | Capacitance                                   | [F]                        |

| $F_e$    | Electrostatic force                           | [N]                        |

| $F_s$    | Spring force                                  | [N]                        |

| k        | Wave number                                   | $[\mathrm{m}^{-1}]$        |

| R        | Resistance                                    | $[\Omega]$                 |

| t        | Time                                          | [s]                        |

xiv

## Contents

| Pı           | refac           | e                           | iii            |

|--------------|-----------------|-----------------------------|----------------|

| Sι           | ımm             | ary                         | v              |

| R            | $\mathbf{esum}$ | é                           | vii            |

| A            | ckno            | wledgements                 | ix             |

| $\mathbf{A}$ | crony           | yms                         | xii            |

| N            | omer            | nclature                    | xii            |

| 1            | Intr            | oduction                    | 1              |

|              | 1.1             | CMUT                        | 2              |

|              |                 | 1.1.1 CMUT outlook          | 5              |

|              | 1.2             | 2D ultrasound imaging       | 5              |

|              | 1.3             | 3D ultrasound imaging       | $\overline{7}$ |

|              | 1.4             | Thesis outline              | 8              |

|              | 1.5             | Publications                | 9              |

| <b>2</b>     | The             | eory                        | 11             |

|              | 2.1             | Static model                | 12             |

|              |                 | 2.1.1 Lumped model          | 12             |

|              |                 | 2.1.2 Clamped plate         | 13             |

|              |                 | 2.1.3 Approximate solutions | 14             |

|              | 2.2             | Dynamic model               | 16             |

|              |       | 2.2.1 Small $ka$ limit                                                                      | 18        |

|--------------|-------|---------------------------------------------------------------------------------------------|-----------|

|              |       | 2.2.2 Large $ka$ limit                                                                      | 23        |

|              |       | 2.2.3 Full description                                                                      | 26        |

|              | 2.3   | Chapter summery                                                                             | 27        |

| 3            | Rov   | v-Column-Addressed Arrays                                                                   | 29        |

|              | 3.1   | Scaling laws                                                                                | 30        |

|              | 3.2   | Geometry                                                                                    | 35        |

|              | 3.3   | Edge waves                                                                                  | 37        |

|              | 3.4   | Silicon substrates for row-column CMUT fabrication                                          | 39        |

|              | 3.5   | Chapter summery                                                                             | 41        |

| 4            | CM    | UT fabrication                                                                              | 43        |

|              | 4.1   | Fusion bonding                                                                              | 44        |

|              |       | 4.1.1 Characterization                                                                      | 47        |

|              | 4.2   | Polymer bonding                                                                             | 52        |

|              |       | 4.2.1 Characterization                                                                      | 54        |

|              | 4.3   | Anodic bonding                                                                              | 57        |

|              |       | 4.3.1 Characterization                                                                      | 58        |

|              | 4.4   | Combined anodic and fusion bonding                                                          | 62        |

|              |       | $4.4.1  \text{Rodent one}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 63        |

|              |       | 4.4.2 Mask layout                                                                           | 67        |

|              |       | 4.4.3 Characterization                                                                      | 67        |

|              | 4.5   | Poly-Silicon-On-Insulator wafer                                                             | 70        |

|              | 4.6   | Chapter summery                                                                             | 76        |

| <b>5</b>     | CM    | UT characterization                                                                         | 79        |

|              | 5.1   | Acoustic characterization                                                                   | 79        |

|              | 5.2   | Electrode resistance                                                                        | 87        |

|              | 5.3   | Ultrasound imaging results                                                                  | 101       |

|              | 5.4   | Chapter summery                                                                             |           |

| 6            | Con   | nclusion 1                                                                                  | <b>05</b> |

| Bi           | bliog | graphy 1                                                                                    | 18        |

|              |       |                                                                                             |           |

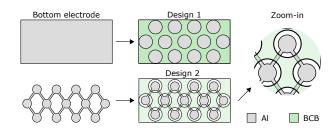

| A            | гар   | er A - BCB polymer based row-column addressed CMUT1                                         | 119       |

| $\mathbf{B}$ | Pap   | er B - Design of a novel zig-zag 192+192 Row Column                                         |           |

Addressed Array Transducer: A simulation study. 125

xvi

#### CONTENTS

| $\mathbf{C}$ | Paper C - CMUT Electrode Resistance Design: Modeling  |     |

|--------------|-------------------------------------------------------|-----|

|              | and Experimental Verification by a Row-Column Array   | 131 |

| D            | Paper D - Wafer bonded CMUT technology utilizing Poly | -   |

|              | Silicon-on-Insulator wafers                           | 141 |

| $\mathbf{E}$ | Paper E - A Row-Column-Addressed 2D Probe with and    | ł   |

|              | Integrated Compound Diverging Lens                    | 147 |

| $\mathbf{F}$ | Fabrication processes                                 | 153 |

|              | F.1 LOCOS                                             | 153 |

|              | F.2 BCB                                               | 160 |

|              | F.3 Anodic bond                                       | 165 |

|              |                                                       | 100 |

CONTENTS

xviii

## CHAPTER 1

### Introduction

Medical applications of ultrasound dates back to 1950 [1], and have since grown to be a conventional tool for diagnostic purposes. Ultrasound is additionally routinely used in multiple other applications ranging from park assist, non destructive testing, fingerprint sensing, gas sensing among other. Ultrasound imaging is like X-ray, Computed Tomography (CT), and Magnetic Resonance (MR) used to examine the internal part of the human body, and ultrasound imaging has the advantages of offering real time imaging opposite to the other modalities and additionally at a low cost. However, the resolution of ultrasound imaging is in general inferior compared to the three other imaging modalities, and ultrasound is limited to predominantly visualization of tissue. Imaging of bone structures is challenging for ultrasound, the reason being bone structures reflect the majority of generated pressure from an ultrasound transducer while tissue allows penetration of the ultrasound waves. This is in technical terms explained by acoustic impedance mismatch between two mediums. The interface between two adjacent mediums acts as a reflector if the acoustic impedance mismatch is large, which prohibits imaging beyond the interface. Medical imaging of bone structures is therefore commonly acquired using imaging modalities such as X-ray, CT, and MR.

Today, nearly all commercial ultrasound transducers for medical imaging are made by a ceramic material with piezoelectric properties (PZT).  $Pb[Zr_xTi_{1-x}]O_3$  is the chemical composition of these types of ceramics, and the abbreviation PZT is used as a generic term for the entire class of piezoelectric ceramics. Other chemical compositions can also be used, but the

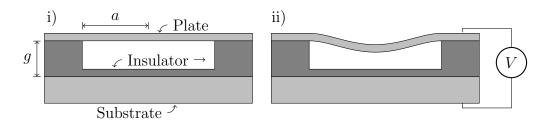

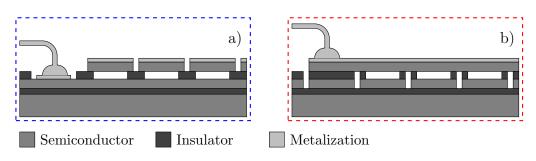

Figure 1.1: Cross-section sketch of a single CMUT. i) Geometrical CMUT parameters are indicated as well as definitions of the different layers. a is the CMUT radius and g is the gap height. ii) The working principle of a CMUT. An electrical field is created by applying a voltage between the plate and the substrate that forces the plate towards to substrate. The deflection of the CMUT plate can thereby be controlled by applying a voltage, and ultrasonic pressure waves can be generated by applying a time varying pulse.

terminology PZT will be used throughout this thesis for all piezoelectric ceramics. Modern ultrasound transducers are fabricated by dicing pieces of PZT into small adjacent elements next to each other. The geometry of the diced PZT elements as well as the quality of the PZT crystallinity determine the performance of the transducer, and notably advances in the PZT crystallinity have significantly increased the performance of the transducers used for medical imaging over the years [2]. But, new semiconductor based technologies have begun to compete with the conventional PZT technology. These new promising technologies are the Piezoelectric Micromachined Ultrasonic Transducers (PMUT) and Capacitive Micromachined Ultrasonic Transducer (CMUT) technology that both have been used to demonstrate medical ultrasound images, and the CMUT technology is already being sold commercially for medical imaging applications.

The PZT and PMUT are both interesting technologies, however, the focus of this thesis is exclusively development of the CMUT technology, and in particular for 3D ultrasound imaging.

### 1.1 CMUT

A CMUT is a micro sized device that consists of a substrate and a vibrating plate (or membrane) separated by an electrically insulating material. A cross sectional sketch of a single CMUT is shown on Fig 1.1 i). The horizontal dimension of a typical CMUT ranges between 5 and 100 µm whereas the common vertical dimension is in the sub micron regime. The high aspect ratio geometry of a single CMUT makes it impractical to draw sketches to

#### 1.1. CMUT

scale, and all sketches of CMUTs are therefore not drawn to scale for visual purposes. The semiconductor technology is the obvious choice for fabricating devices on this length scale. Conventional semiconductor fabrication techniques provide a large degree of freedom in design process of CMUTs, which is one of the main selling points for the CMUT technology.

The geometry of a CMUT is defined by conventional UV lithography and the most common shapes for the individual CMUTs are either circles or squares in which case the parameter a becomes either the radius or half side length and q is in both cases the gap height. CMUTs are operated by applying a voltage between a top and a bottom electrode that are designed into the CMUT structure, see Fig. 1.1 ii). The applied voltage creates an electric field that forces the plate towards to substrate due to the electrostatic force. The CMUT is a high field device, meaning the applied voltage does not necessarily has to be high, but the electric field between top and bottom electrode is in many applications required to be on the order of  $0.5 \,\mathrm{V/nm}$ , which is high compared to other MEMS devices. The electromechanical coupling between the electrostatic and mechanical domain makes a CMUT inherently non-linear. It should, however, be emphasized that the structural deformation of the plate caused by an applied bias can in most cases be described by a linear deformation theory. The DC bias is required for CMUT applications within the field of medical imaging, since the generated pressure and the receive sensitivity both increases as function of the applied bias. Acoustic signals are generated by imposing a voltage pulse on top of the DC bias which effectively forces the plate to oscillate. In transmit situation, the kinetic energy of the plate couples into the medium as propagating pressure waves. The mechanism is opposite in receive, where an external pressure wave couples into kinetic energy of the plate, that can be measured and converted into an ultrasound image.

The non-linearity of the CMUT is in many cases used advantageously, since, the Signal to Noise Ratio (SNR) has a non-linear increase with the applied bias. The plate is forced towards the substrate due to the electrostatic force as the DC bias is increased. The mechanical stiffness of plate gets reduced as the applied DC-bias increases, a phenomenon called the spring softening effect. The non-linear effects become more and more dominant as the bias voltage is increased until a point where the spring force from the plate no longer can counter the electrostatic force. It results in an unstable state where the plate is forced to the bottom of the cavity. This is a nonlinear phenomenon that occurs at a specific voltage known as pull-in voltage or collapse voltage. The gap height, the plate thickness, and the radius or side length of a CMUT determine the pull-in voltage, and other parameters such as resonance frequency, bandwidth, and output pressure. The top plate and the substrate of a CMUT are separated by an electrical insulator in the CMUT literature commonly denoted the post region, or in short just post. Excellent insulating properties are essential for functional CMUTs, since the insulator has to be able to withstand the high electrical field. The purity of the insulator also of crucial importance, even a tiny amount of mobile impurities in the insulator can give rise to dielectric charging during operation, which greatly reduces the functionality of the CMUT.

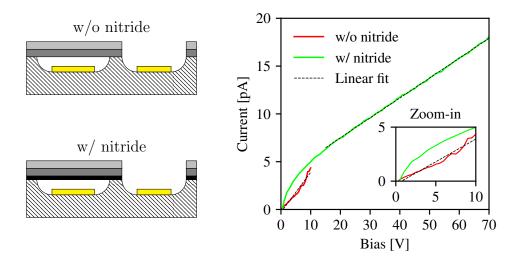

To achieve high quality insulation properties layers of silicon oxide or silicon nitride are commonly used for CMUT fabrication. An insulating layer in the bottom of the cavity is often used to prevent the CMUT from short circuiting if the pull-in voltage is applied. The same effect can be obtained by having an insulating layer on the plate (on the side towards the cavity), both cases require high quality dielectric properties for a satisfying CMUT performance.

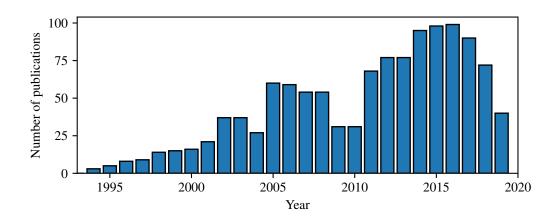

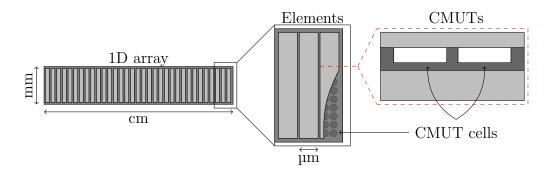

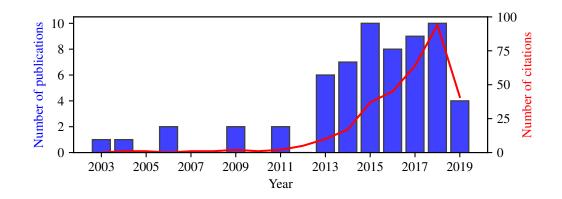

The CMUT technology was first proposed in the early 1990's by Khuri-Yakub from Stanford University. Two papers from 1994 and 1996 by the same name A Surface Micromachined Electrostatic Ultrasonic Air Transducer and both by Haller and Khuri-Yakub are the first and most influential CMUT papers [3,4]. The interest for the CMUT technology has after these papers grown steadily ever since and is still an expanding technological field, which can be seen in Fig. 1.2 where the number of publications is shown as function of time. The publication count from 2019 is prior the to large International Ultrasound Symposium (IUS) where a substantial amount of CMUT papers are published. Two of the many reasons behind the success of the CMUT technology are the design flexibility and the possibility of parallelism. The sketched CMUT in Fig. 1.1 ii) constitutes a single CMUT, which henceforth is called a CMUT cell, that by itself produces a small signal regardless of it being acoustically or electrically. But, by grouping hundreds or even thousands of individual CMUT cell together and operating all of them in parallel enhance the SNR to a level capable of competing at a commercially level within various applications.

Figure 1.2: Number of CMUT publications versus time. The data has been acquired from the Web of Science database using the keywords: CMUT or Capacitative Micromachined Ultrasound Transducer or Surface micromachined transducer.

#### 1.1.1 CMUT outlook

The first commercialization of a CMUT probe for medical imaging was back in 2009 where Hitachi released the *Mappie* probe. In the following years KOLO and Butterfly Network have released their respective CMUT probes, where especially the latter has gotten a lot of positive attention. The CMUT probe from Butterfly Network is portable and uses a smartphone or a tablet to display the acquired ultrasound image. Furthermore, the Butterfly iQ – Ultrasound app, used for visualization on the smart devices, was announced as one of the winners of the Apple design Awards in 2019.

The publicity, especially associated with the Butterfly Network, has boosted the confidence in the CMUT technology, that is predicted to have a significant increase during the next couple of years. The market share of CMUT transducers within the field of medical imaging was less than 1% back in 2017, but is according to a report from Yole Développement [5] predicted to occupy 30 % of the market in 2023 as illustrated in Fig. 1.3.

## 1.2 2D ultrasound imaging

Conventional ultrasound transducers produce two-dimensional images of the internal body and such transducers will henceforth be referred to as a linear arrays or 1D arrays. A Linear array can be further decomposed into N elements. Each of the N individual elements has to be electrically connected

Figure 1.3: Prediction of the medical ultrasound market distribution in 2023 compared with the numbers from 2017 [5].

Figure 1.4: Sketch of all the components in a 1D CMUT array. The 1D array consists of N individual elements. The end of the 1D array is magnified and the zoom-in shows the three last elements. The plate is partially removed from the last element to illustrate the positions of the CMUT cells. The red dashed line indicates the in-plane cross section in which CMUTs commonly are drawn.

while being insulated from all the other elements. Each element in a linear CMUT array consists of numerous CMUT cells, typically several hundreds of CMUT cells per element. All the components that make up a linear CMUT array are sketched together in Fig. 1.4. The number of elements should preferably be as high as possible, since the image quality improves with the number of elements. The surface area and the complexity of the probe assembly do also increase with number of element, hence, application specific trade-offs have to be considered for all ultrasound transducers. To put things in perspective, modern ultrasound images are typically acquired by transducers with more than 100 individual elements.

Multiple ultrasound images have been documented by CMUTs probes

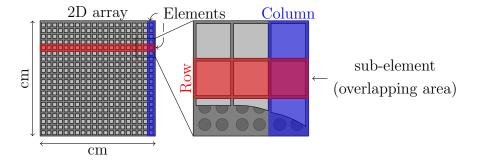

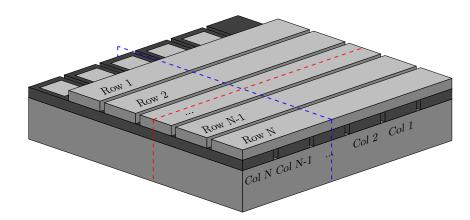

Figure 1.5: Sketch of all the components in a 2D CMUT array. The 2D array consists of N individual rows and N individual columns, highlighted in red and blue, respectively. The area where rows and columns overlap defines a sub-element. The zoom-in shows nine sub-elements where the plate is partially removed from three of them to illustrate the positions of the CMUT cells.

since the discovery back in the 1990s [6–8]. Notably, the presented probe in [8] was fully capable of producing commercially comparable B-modes images and doppler blood flow estimation of the carotid artery.

## 1.3 3D ultrasound imaging

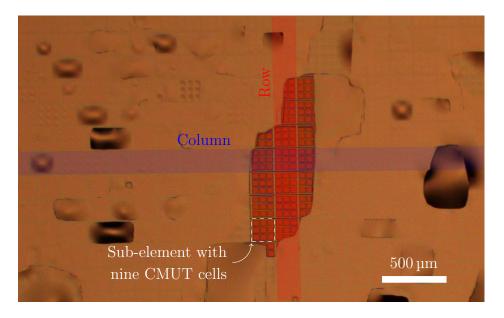

All objects inside the human body are three dimensional and information is inevitably lost by evaluating 2D images of the body. It is therefore naturally to think in terms of three dimensional imaging. The terminology for 2D transducers is not as well defined as the 1D counterpart, but the terminology used throughout this thesis is the following. 2D arrays can, equivalent to the 1D arrays, be divided into elements. A 2D transducer consists of 2Nelements, N rows and N columns as sketched in Fig. 1.5. The overlapping region of a row and a column is called a sub-element.

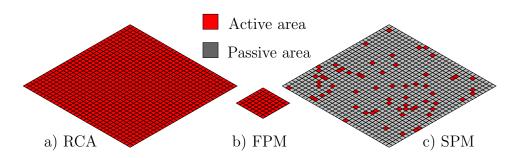

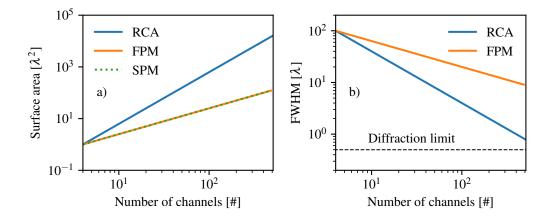

Fully Populated Matrix (FPM) arrays are the direct extension from 1D arrays to 2D arrays. These arrays require electrical interconnections to all the individual sub-elements and therefore defined by  $N \times N$  channels. This configuration is problematic due to a quadratic scaling law of electrical interconnections. Thus, more than 10000 electrical interconnections are required for a FPM transducer to obtain the same 3D image quality as a linear transducer with plus 100 elements. Multiple transducer architectures have been proposed in the literature to overcome the challenge with the enormous amount of electrical interconnections [9] associated with 3D imaging. One way of achieving 3D images is to use a conventional 1D transducer with an integrated accelerometer, capable of monitoring the relative position of the transducer. Three dimensional ultrasound images are reconstructed by combining the knowledge of the transducer position with multiple 2D images. This 3D transducer architecture does not provide real time 3D images and is also sensitive to movement of the imaged object between the first and last acquired image. A rather similar architecture, that also stitch multiple images together, is a motorized 1D transducer, where the transducer surface is steered periodically back and forth by a motor inside the probe handle. It has the advantage of being less operator dependent, and also provide a higher frame rate for the reconstructed 3D images. These two technologies can provide 3D images, but will inherently have difficulties with estimating blood flow in 3D, due to the time shift between images used for the reconstruction. The transducer design should be structured as a 2D array to efficiently perform 3D blood flow estimations. Either by the FPM configuration, at the expense of a high amount of interconnections, or by a sparse array configuration where a smaller percentage of the sub-elements are electrically connected. A third option is a Row-Column-Addressed (RCA) array, this configuration utilizes the fact that the rows and columns make up two orthogonal linear arrays on top of each other. The channel count is significantly reduced to 2N compared to the  $N^2$  dependency for the FPM array, and the RCA array configuration provides the opportunity of real time 3D images and flow estimation [10].

Development of RCA CMUT arrays with large surface area and a high channel count is the focus of this thesis. The different 2D transducer technologies are discussed in more detail in chapter 3, where a more technical and in depth analysis between the different 2D transducer technologies are given.

### 1.4 Thesis outline

The thesis is divided into six chapters. Theoretical modelling of a CMUT is discussed in chapter 2 where design parameters and scaling laws are derived and discussed. The chapter is divided into two parts. The first part addresses the static behaviour of a single CMUT cell, and the dynamics of a single CMUT cell is examined in the second part.

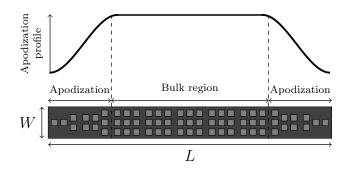

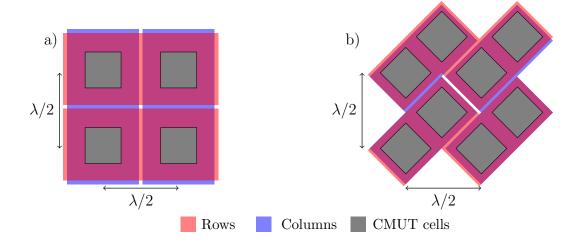

The row-column technology is discussed in chapter 3. After a brief literature review are relevant scaling laws for 2D arrays considered. The geometrical structure of a RCA CMUT array will be provided followed by an analysis of challenging phenomenons associated with the row-column geometry. It includes the issue of edge waves and problems with capacitive substrate coupling, the later is CMUT specific.

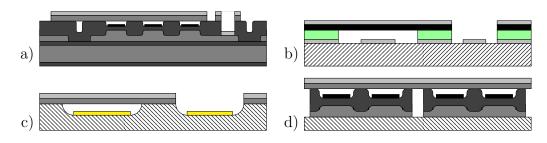

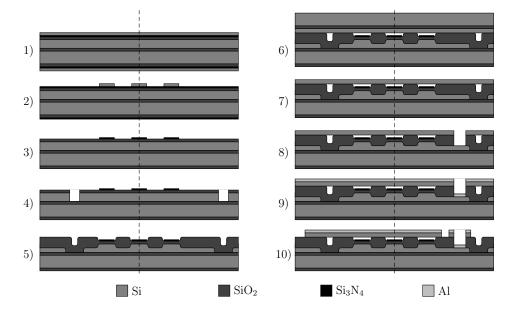

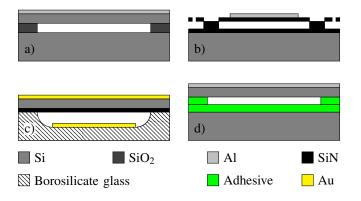

CMUT fabrication and process development are examined in chapter 4.

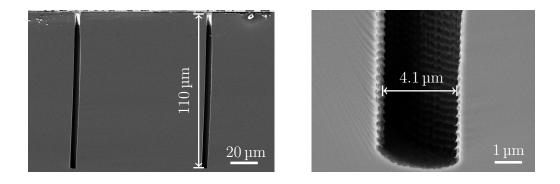

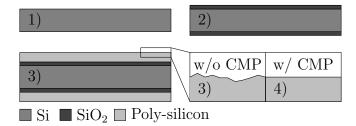

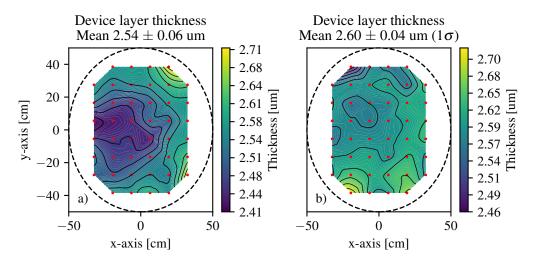

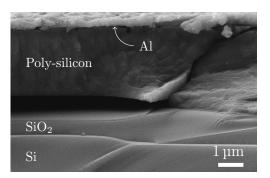

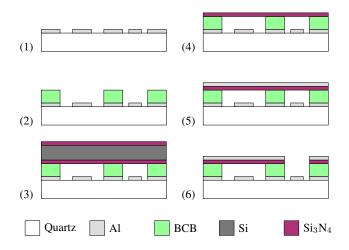

Three different fabrications methods are discussed with a special focus on RCA arrays. The first method utilizes fusion bonding, the second method is a polymer based CMUT fabrication, and an anodic bonded CMUT is the third and last process. An additional forth fabrication process is also presented, it combines the beneficial properties of the fusion bonding method and the anodic bonding method. Finally, a novel fabrication technique of Poly-Silicon-On-Insulator (PSOI) wafer is presented. PSOI wafers can be used for CMUT fabrication as a substitution of conventional Silicon-On-Insulator (SOI) wafers. A characterization of PSOI wafer are given and the PSOI technology is demonstrated for both fusion bonded and anodic bonded CMUTs.

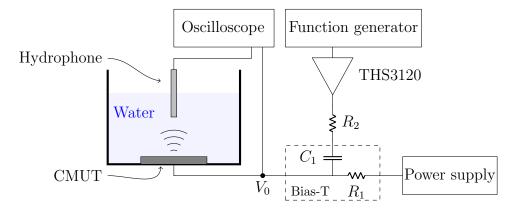

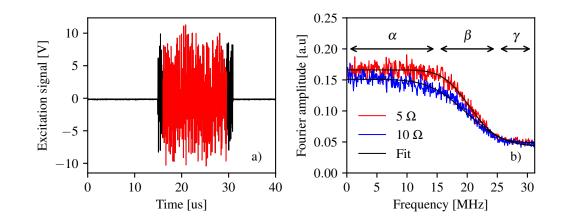

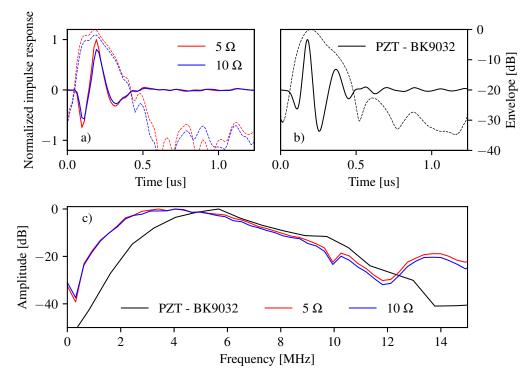

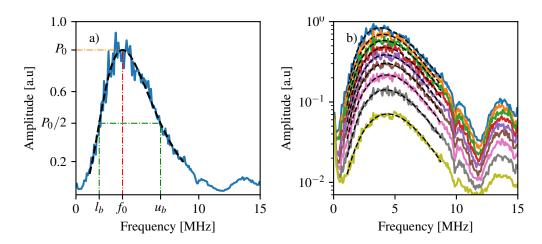

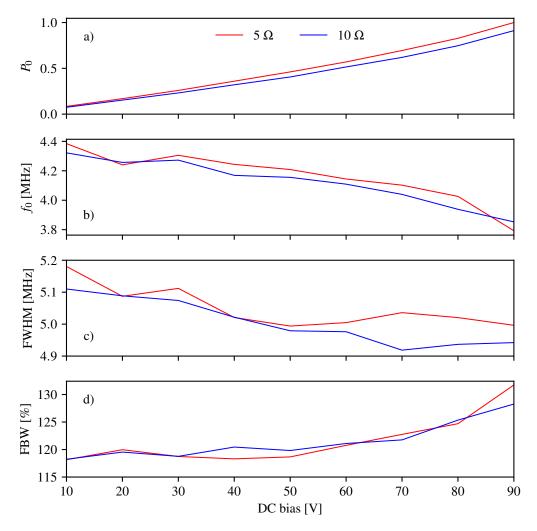

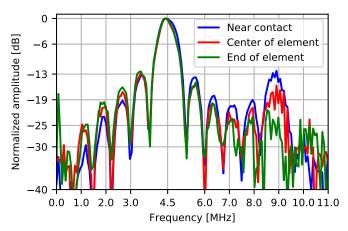

An acoustic characterization of the developed CMUTs are presented in chapter 5. This chapter is divided in two parts. A developed single channel acoustic set-up is considered in the first part. The frequency response from the instruments and electronics are optimized to provide optimal conditions for acoustic CMUT characterization. Acoustic measurements of a fabricated linear CMUT array is demonstrated with two different configurations in the electronics.

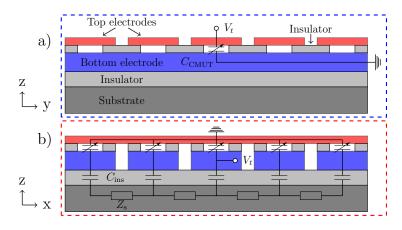

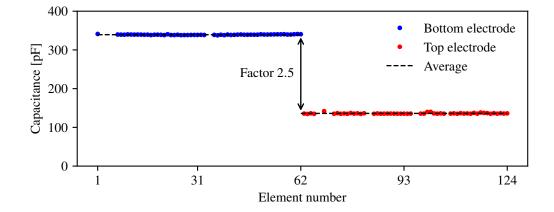

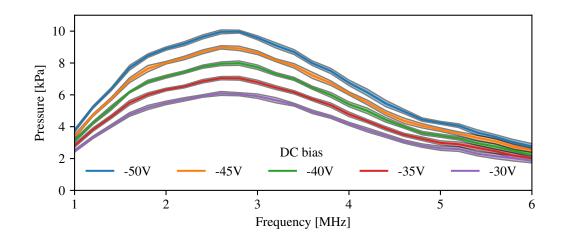

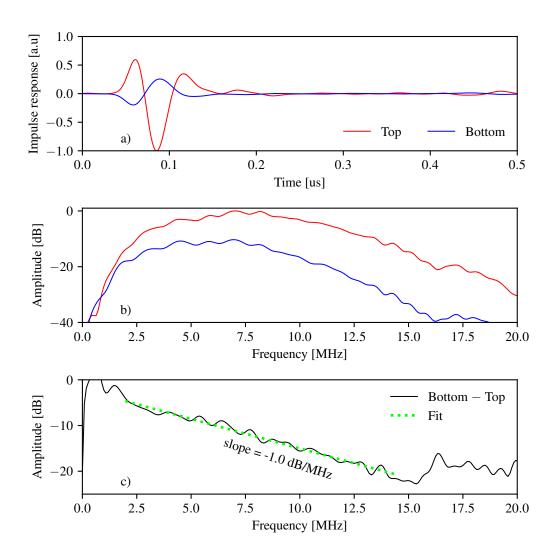

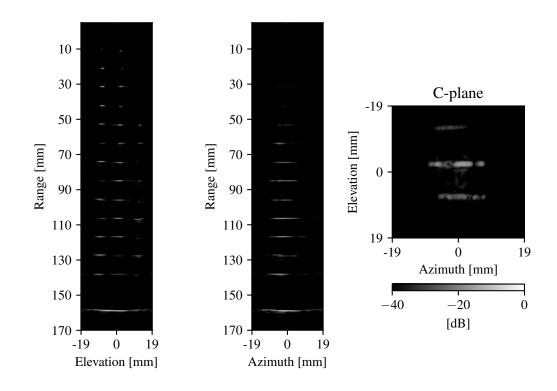

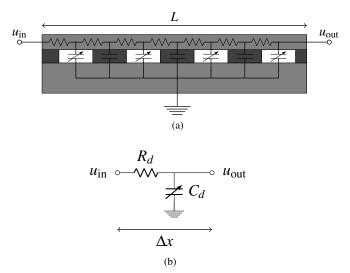

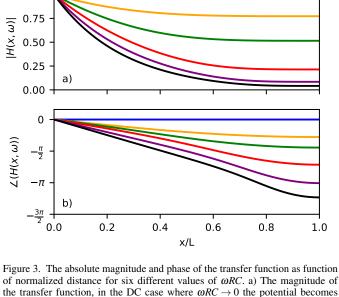

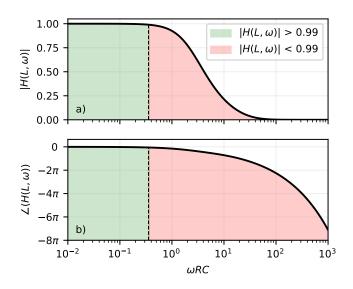

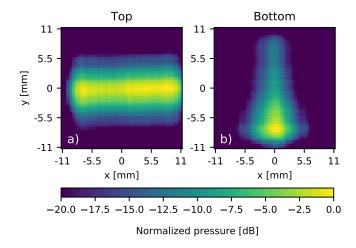

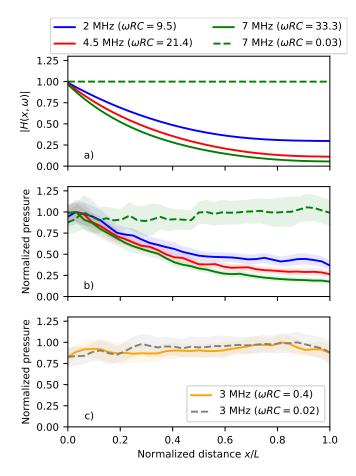

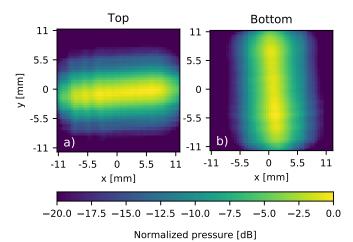

In the second part of the chapter is a fabricated 92+92 RCA CMUT probe acoustically characterized, where an attenuated pressure field was observed for the columns. A delay line model is derived and used to describe the observed attenuation for the columns. At the end of the chapter is 3D ultrasound row-column images presented.

The thesis is concluded in chapter 6.

### **1.5** Publications

The results from this thesis has been published in six IUS conference proceedings and one journal article.

Articles included in the thesis:

- Paper A A. S. Havreland, M. L. Ommen, C. Silvestre, M. Engholm, J. A. Jensen, and E. V. Thomsen, "BCB polymer based row-columnaddressed CMUT," in *Proc. IEEE Ultrason. Symp.*, 2017, pp. 1–4.

- Paper B M. Schou, A. S. Havreland , M. Engholm, M. B. Stuart, E. V. Thomsen and J. A. Jensen, "Design of a novel zig-zag 192+192 Row Column Addressed Array Transducer: A simulation study.," in *Proc. IEEE Ultrason. Symp.*, 2018, pp. 1–4.

- **Paper C** A. S. Havreland, M. Engholm, B. G. Tomov, J. A. Jensen, O. Hansen, and E. V. Thomsen, "CMUT Electrode resistance design:

Modeling and experimental verification by a row-column array" in *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol.66, no. 6, pp.1110-118, 2019.

- Paper D A. S. Havreland, M. Engholm, R. S. Grass, J. A. Jensen and E. V. Thomsen, "Wafer bonded CMUT technology utilizing a Poly-Siliconon-Insulator wafer," in *Proc. IEEE Ultrason. Symp.*, 2019, pp. 1–4.

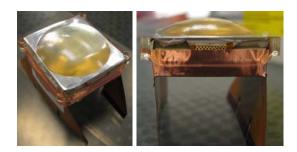

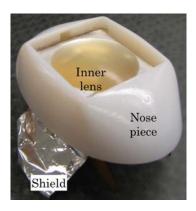

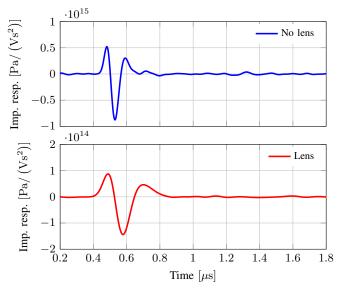

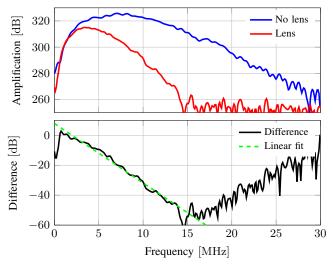

- Paper E M. Engholm, C. Beers, A. S. Havreland, B. G. Tomovz, J. A. Jensen, and E. V. Thomsen, "A Row–Column-Addressed 2D Probe with an Integrated Compound Diverging Lens," in *Proc. IEEE Ultrason. Symp.*, 2018, pp. 1–4.

#### Articles not included in the thesis:

- Paper F R. S. Grass, A. S. Havreland, M. Engholm, J. A. Jensen and E. V. Thomsen, "188+188 Row-Column Addressed CMUT Transducer for Super Resolution Imaging," in *Proc. IEEE Ultrason. Symp.*, 2019, pp. 1–4.

- Paper H E. V. Thomsen, M. Petersen, K. Steenberg, A. S. Havreland, R. S. Grass, M. L. Ommen and M. Engholm, "Wafer Level Characterization of Row-Column Addressed CMUT Arrays," in *Proc. IEEE Ultrason. Symp.*, 2019, pp. 1–4.

## CHAPTER 2

### Theory

In this chapter both the static and dynamic behavior of a CMUT is described through mathematical models. The CMUT is an inherently non-linear device and is therefore complicated to model, however, dimensionless parameters will be derived as they provide valuable insight in the scaling of different relevant CMUT parameters.

Multiple mathematical models for the static and dynamic behaviour of CMUTs can be found in the literature. The models include finite difference models [11], time domain FEM analysis [12], large lumped element models [13], simulink/BEM models [14] and harmonic oscillator models [15] among others. The dynamics of a single CMUT cell will in this chapter be modeled as a harmonic oscillator with a non-linear electrostatic force term. All the developed models in this theory chapter evaluates the behaviour of a single isolated CMUT cell, thus, effects from electronics, backing, array couplings are not included.

A hat notation will be used throughout the chapter and will be assigned to all non-dimensional variables. The same letter will be used for both physical and non-dimensional variables. For instance, the plate displacement is denoted x and has a length unit, whereas the  $\hat{x}$  is the normalized distance with respect to the gab height and is dimensionless.

The assumptions in for the modeling is as follows: A circular cell geometry is assumed for all models in this chapter, and a vertical electric field is assumed between the top and bottom electrode, hence, effects from fringing fields are not included. The dynamic CMUT models are applicable for both a transmit and a receive situation. However, displacement of the plate is small enough to justify linearization of the electrostatic force in a receive analysis. But, a transmit analysis has to include the non-linearity due to a large displacement of the plate. Finally, the models used for dynamical modeling do not include a time dependent driving term, but, focus solely on the dynamical properties of the CMUT itself.

### 2.1 Static model

Two static models are presented in this section. The first model is a lumped element model that is used to find a characteristic voltage for a CMUT system. The second model is perturbative solution used to estimate the deflection profile of a clamped CMUT plate applied to an electrostatic pressure.

#### 2.1.1 Lumped model

The most simple approach to model the static behavior of a CMUT is to consider a parallel plate capacitor, where one plate is fixed and the other plate is attached to a linear spring. When a DC bias is applied the system consists of two opposite forces i.e. a spring force  $F_s$  and an electrostatic force  $F_e$

$$\underbrace{k_s x}_{F_s} = \underbrace{\frac{\varepsilon A U^2}{2(g-x)^2}}_{F_s},\tag{2.1}$$

where x is the displacement of the plate,  $k_s$  is the spring constant,  $\varepsilon$  is the permittivity, U is the applied DC bias, g is the gab height, and A is the surface area of the CMUT cell. The solution to Eqn. 2.1 yields the stationary point of the displacement for a given applied voltage. The electrostatic force is non-linear and introduces an unstable regime where the spring force no longer can balance the electrostatic force. It leads to an unstable state where the plate gets pulled into the bottom of the cavity. The critical voltage at which this phenomenon occurs for a CMUT is denoted the pull-in voltage or the collapse voltage, which the parallel plate capacitor CMUT model is given by [16]

$$U_{pi} = \sqrt{\frac{8}{27} \frac{k_s g^3}{\varepsilon A}}.$$

(2.2)

This closed form solution can be difficult to directly apply to a real system, since precise estimates of the spring constant can be difficult to obtain. However, the scaling laws of the different parameters are very valuable in a design and fabrication process of CMUTs. A pull-in condition is a sign of non-linearity in any given system, since such instabilities never occurs in linear systems. Analysis of non-linear instabilities are widely documented in the literature of non-linear dynamics where the terminology for this kind of pull-in condition is called a saddle node bifurcation [17].

#### 2.1.2 Clamped plate

The lumped model assumes a uniform displacement of the plate, and this assumption will in many CMUT designs not be a realistic scenario. A more accurate description of a CMUT plate under an applied DC potential is mathematically formulated by the plate equation, given here in a coordinate free form

$$\nabla^2 \nabla^2 w = \frac{p}{D},\tag{2.3}$$

where w is the deflection profile of the plate, p is the electrostatic pressure and D is the flexural rigidity given by

$$p = \frac{\varepsilon U^2}{2(1-w)^2} \tag{2.4}$$

$$D = \frac{Yh^3}{12(1-\nu)},$$

(2.5)

where Y is Young's modulus, h is the plate thickness, and  $\nu$  is the Poisson's ratio. A polar coordinate system is introduced due to the assumed circular geometry. An axis symmetric argument can be used to conclude that the deflection profile, w, must to rotational symmetric and therefore depend entirely on the radial component, r. The radius of the CMUT cell will be denoted, a, and is used to define the horizontal non-dimensional parameter  $\hat{r} = r/a$ . The vertical displacement is normalized to the gab height,  $\hat{w} = w/g$ , and the non-dimensional version of Eqn. 2.3 can then be expressed as

$$\underbrace{\left[\frac{1}{\hat{r}}\frac{\mathrm{d}}{\mathrm{d}\hat{r}}\hat{r}\frac{\mathrm{d}}{\mathrm{d}\hat{r}}\right]}_{\nabla^2}\underbrace{\left[\frac{1}{\hat{r}}\frac{\mathrm{d}}{\mathrm{d}\hat{r}}\hat{r}\frac{\mathrm{d}\hat{w}}{\mathrm{d}\hat{r}}\right]}_{\nabla^2\hat{w}} = \frac{\varepsilon U^2 a^4}{2Dg^3(1-\hat{w})^2} = \frac{\hat{U}_r^2}{(1-\hat{w})^2},$$

(2.6)

where  $\hat{U}_r$  is a voltage ratio between between the applied voltage and a characteristic voltage,  $U_c$ , defined as

$$\hat{U}_r = \frac{U}{U_c}$$

where  $U_c = \sqrt{\frac{2Dg^3}{\varepsilon a^4}}$ . (2.7)

To find a unique solution to Eqn. 2.6 four imposed boundary conditions are required, and the used boundary conditions in this analysis are

$$\hat{w}(0) = \text{finite} \quad \hat{w}'(0) = 0 \quad \hat{w}(1) = 0 \quad \hat{w}'(1) = 0.$$

(2.8)

Equation 2.6 is a non-linear boundary value problem without any known closed form solution for the four imposed boundary conditions. However, the dimensionless form allows extraction of valuable information. The derived parameter,  $U_c$ , contains the scaling properties of the pull-in voltage and differs only by a numerical constant. The numerical constant has been determined by a FEM analysis in [18], and the relationship between  $U_c$  and  $U_{pi}$  is calculated to be

$$U_{pi} = 14.23U_c. (2.9)$$

#### 2.1.3 Approximate solutions

Equation 2.6 cannot be solved analytically, but, approximate solution can be found for small deflections. To do so the differential equation is linearized by taylor expanding the electrostatic pressure to first order

$$\nabla^2 \nabla^2 \hat{w} = \frac{\hat{U}_r^2}{(1-\hat{w})^2} \approx \hat{U}_r^2 (1+2\hat{w}).$$

(2.10)

Under the assumption of an infinite sum representation a pertubative solution can be defined as

$$\hat{w} = \sum_{n=0}^{\infty} \hat{U}_r^{2n} \hat{w}_n \approx \hat{w}_0 + \hat{U}_r^2 \hat{w}_1 + \hat{U}_r^4 \hat{w}_2 \quad \text{for} \quad U_r^2 \ll 1.$$

(2.11)

Here  $\hat{U}_r^2$  is used as the perturbation parameter, and the infinite sum is truncated and substituted into equation 2.10 to obtain a sequence of linear differential equations

order

$$\hat{U}_r^0 \quad \nabla^2 \nabla^2 \hat{w}_0 = 0$$

(2.12)

order

$$\hat{U}_r^2 \quad \nabla^2 \nabla^2 \hat{w}_1 = 1 + 2\hat{w}_0$$

(2.13)

order

$$\hat{U}_r^4 \quad \nabla^2 \nabla^2 \hat{w}_2 = 2\hat{w}_1$$

(2.14)

$\hat{w}_0$  is the solution to the plate equation when electrostatic pressure is zero and deflection is therefore completely flat or expressed mathematically  $w_0 = 0$ .

#### 2.1. STATIC MODEL

$w_1$  corresponds to a plate with a uniform applied pressure and has the forth order polynomial solution

$$\hat{w}_1 = \frac{\left(1 - \hat{r}^2\right)^2}{64}.$$

(2.15)

When the plate is forced downwards due to the electrostatic force the center of the plate will experience a larger force than the circumference of the CMUT.  $\hat{w}_2$  is the first correction term that incorporates the distance dependency in the applied electrostatic pressure and has the solution

$$\hat{w}_2 = \hat{w}_1 \frac{23 - 6\hat{r}^2 + \hat{r}^4}{1152} \tag{2.16}$$

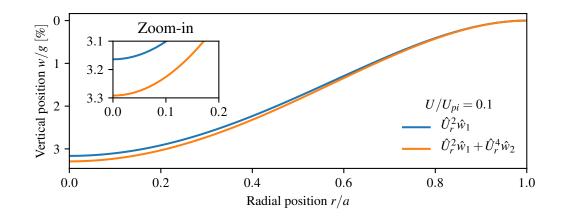

The largest deflection and numerical difference between  $w_1$  and  $w_2$  occur at the center, where  $\hat{r} = 0$ . The presented perturbative analysis predicts a slight overall increase of the deflection, with a maximum displacement at the center. The approximate solution to the problem is given by

$$\hat{w}(\hat{r}) \approx \hat{w}_1(\hat{r})\hat{U}_r^2 \left(1 + \frac{23 - 6\hat{r}^2 + \hat{r}^4}{1152}\hat{U}_r^2\right).$$

(2.17)

The correction term is positive for all values of  $\hat{r}$  and depends on the magnitude of the bias ratio. The derived approximate solution to Eqn. 2.10 is shown in Fig. 2.1 plotted together with the constant pressure solution  $\hat{U}_r^2 \hat{w}_1$ . Additional displacement is observed for the higher order model, although the overall shape of the deflection is preserved. The model predicts a maximum discrepancy of approximately 0.15% when the CMUT is biased with 10% of the pull-in voltage.

**Figure 2.1:** The deflection of a clamped plate with an electrostatic applied pressure.  $\hat{w}_1 \hat{U}_r^2$  corresponds to the deflection under a constant pressure assumption. The solution  $\hat{w}_1 \hat{U}_r^2 + \hat{w}_2 \hat{U}_r^4$  accounts for the distance dependency of the electrostatic pressure, and the larger displacement is therefore expected and observed.

### 2.2 Dynamic model

Dynamic modeling of CMUTs in immersed applications becomes rapidly complicated due to the intrinsic non-linear behavior of the CMUT itself and the fluid structure interaction between the vibrating plate and the surrounding medium. The equations of the CMUT dynamics will be governed by four force contributions in the following section. The contributions include an inertia term, a linear spring term, an electrostatic term, and a force term that describes the interacting between the plate and the surrounding medium. The four forces are assumed to be the dominant forces in this system, and are used to define the non-linear harmonic oscillator given by

$$\underbrace{m\frac{\mathrm{d}^2 x}{\mathrm{d}t}}_{\mathrm{Inertia}} + f_{RI} + \underbrace{kx}_{\mathrm{Spring}} = \underbrace{\frac{\varepsilon A U^2}{2(g-x)^2}}_{\mathrm{Electrostatic}},$$

(2.18)

where the assumed initial conditions are

$$x(0) = 0$$

and  $x'(0) = 0.$  (2.19)

Two additional terms have been added when compared to the static model in section 2.1, the force from the radiation impedance,  $f_{RI}$ , and the inertia term. The radiation impedance is used to model an interaction between the plate and the surrounding medium. The interacting mechanism of  $f_{RI}$  depends

on frequency and the size of the CMUT geometry, it will be introduced in different configurations depending regime of operation.

Radiation impedance is conventionally defined in the frequency domain, however, medical ultrasound is a time domain system. Thus, an inverse Fourier transform is required to proceed with a time domain analysis. The equations used to model the radiation impedance assumes a harmonically driven system, and is naturally still assumed in the time domain. But, this assumption will not be met in medical imaging applications, since pulses are used instead of continuous signals, though the scaling laws are assumed to be similar. Radiation impedance is defined as complex quantity in the frequency domain, where the real part is called radiation resistance and is measure of how much acoustic energy that radiates from the transducer surface. The imaginary part is called radiation reactance and can be interpreted as a mass loading of the medium in front of the transducer. The force acting on a transducer surface can, in the frequency domain, be expressed as

$$F(\omega) = Z(\omega)V(\omega) \tag{2.20}$$

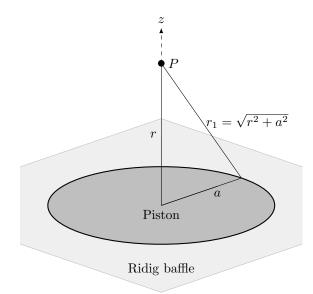

where Z is the radiation impedance, V is the velocity of the transducer surface, and  $\omega$  is the angular frequency. The radiation impedance for a circular piston in rigid baffle is given by [19]

$$Z(2ka) = \rho_m c_m A \left[ 1 - 2\frac{J_1(2ka)}{2ka} + i2\frac{H_1(2ka)}{2ka} \right]$$

(2.21)

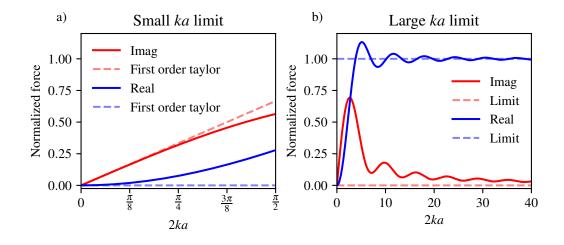

where  $\rho_m$  is the density of the medium,  $c_m$  is the speed of sound in the medium, A is the transducer area, k is the wave number, and  $J_1$  is the Bessel function of first kind and order one,  $H_1$  is the Struve function of order one. The two special functions,  $J_1$  and  $H_1$ , complicate analytical modeling, but simple approximations can be used in the two limiting cases where  $ka \ll 1$  or  $ka \gg 1$ . The real and the imaginary part of radiation impedance are plotted in Fig. 2.2 in both the low and high ka limits. The solid lines represent the exact expressions and dashed lines represent approximations.

In the following two sections 2.2.1 and 2.2.2 CMUT dynamics will be studied for small and large ka values, respectively. No damping mechanisms are initial included in Eqn. 2.18, thus, the radiation impedance is the only term that can introduce damping properties. However, CMUTs will experience multiple other damping mechanisms during operation. These damping mechanisms counts clamping losses, material damping, squeeze film damping, thermoelastic damping among other. The damping is heavily dependent on the medium in which the CMUT is operated. For instance is squeeze film damping more dominant for CMUT in airborne applications, whereas the

**Figure 2.2:** The radiation impedance normalized to  $\rho_m c_m A$  for both low and high ka values. First order Taylor expansions of the radiation impedance are plotted as dashed lines in the small ka limit a). The limiting value of the radiation impedance is plotted as dashed lines in the large ka limit b).

damping from the medium becomes more dominant for immersed applications, such as medical imaging.

#### 2.2.1 Small ka limit

A pitch of  $\lambda/2$  between two neighbouring elements is beneficial in medical imaging applications, since it minimizes the effect from grating lobes [20].  $\lambda$ is here the wavelength of the transmitted ultrasound. This design criterion constrains the possible values of 2ka between 0 and  $\pi/2$ , where the latter case corresponds to CMUT cell diameter equal to the width of the element. The small ka regime is modelled by a taylor expansion of Eqn. 2.21 and yields

$$Z \approx \rho_m c_m A \frac{8ika}{3\pi}$$

for  $ka \ll 1.$  (2.22)

This approximation will be used throughout the entire analysis for small ka values. Notice, the approximation is purely imaginary, and both real part (zero) and the imaginary part of the approximation are indicated in Fig. 2.2 a). The transformation of Eqn. 2.22 back to the time domain is done by first employing the substitution  $ka = \omega a/c_m$  followed by an inverse Fourier

transform

$$f_{RI} = \frac{8\rho_m Aa}{6\pi^2} \int_{-\infty}^{\infty} i\omega V(\omega) e^{i\omega t} \,\mathrm{d}\omega \qquad (2.23)$$

$$=\frac{8\rho_m a^3}{3}\frac{\mathrm{d}^2 x}{\mathrm{d}t^2},$$

(2.24)

where the following Fourier transform rule has been used

$$\frac{\mathrm{d}^n g}{\mathrm{d}t^n} = \frac{1}{2\pi} \int_{-\infty}^{\infty} (i\omega)^n G(\omega) e^{i\omega t} \,\mathrm{d}\omega.$$

(2.25)

This results implies that the system will experience an additional mass, and the equation of motion becomes

$$\left(m + \frac{8\rho_m a^3}{3}\right)\frac{\mathrm{d}^2 x}{\mathrm{d}t^2} + kx = \frac{\varepsilon A U^2}{2(g-x)^2}.$$

(2.26)

The non-dimensional version of this equation is obtained by defining the displacement relative to the gap height  $\hat{x} = x/g$ . The time is scaled with the unperturbed natural frequency  $\hat{t} = \omega_0 t$  where  $\omega_0^2 = k/m$  and the final non-dimensional equation can then be expressed as

$$\frac{\mathrm{d}^2 \hat{x}}{\mathrm{d}t^2} + \hat{\omega}_m^2 \hat{x} = \hat{\omega}_m^2 \frac{\hat{U}_r^2}{(1-\hat{x})^2}.$$

(2.27)

This equation shows the dynamics of a single CMUT cell, in the small ka regime, is fully described by two parameters,  $\hat{U}_r$  and  $\hat{\omega}_m$ . The bias ratio,  $\hat{U}_r$ , and a reduced resonance frequency parameter,  $\hat{\omega}_m$ , defined as

$$\hat{U}_r^2 = \frac{4}{27} \frac{U^2}{U_{pi}^2} \tag{2.28}$$

$$\hat{\omega}_m^2 = \left(1 + \frac{8\rho_m a^3}{3m}\right)^{-1} = \left(1 + \frac{8}{3\pi} \frac{\rho_m}{\rho_p} \frac{a}{h}\right)^{-1}, \qquad (2.29)$$

where  $\rho_p$  is the density of the plate, and h is the thickness of the plate. The constant 4/27 is merged into the bias voltage ratio,  $U_r$ , to reduced numerical constants in the following expressions and  $U_{pi}$  is defined in Eqn. 2.2. The reduced resonance frequency parameter predicts a significant frequency change between applications in air and water, simply caused by the ratio of the densities. This effect is validated experimentally where the center frequency of the same CMUT typically differs a factor of  $\approx 2$  between air and immersed applications. For a silicon plate the density ratio is on the order of  $5 \times 10^{-4}$  when operated in air, whereas the ratio is 0.43 between when operated in water. Additionally, the reduced frequency also depends on the plate aspect ratio, a/h, according to the model.

Eqn. 2.27 is a non-linear differential equation where the energy is conserved for all applied voltages smaller than the pull-in voltage. Physically it implies the CMUT does not radiate sound into the medium, which is a completely non-satisfying performance from a transducers point of view. However, to avoid or reduce low acoustic radiation, the CMUT plate should have a large radius, which is obtained by packing an the elements with few but large CMUT cells instead of many smaller CMUT cells.

A close form solution to Eqn. 2.27 is not known, but approximate solutions can be found by expanding the non-linear electrostatic term. The linear response is modeled by a first order expansion and non-linear corrections can be captured in higher order expansions. Equation 2.27 simplifies to

$$\frac{\mathrm{d}^2 \hat{x}}{\mathrm{d}\hat{t}^2} + \hat{\omega}_m^2 \hat{x} = \hat{\omega}_m^2 \hat{U}_r^2 \left[\underbrace{\underbrace{1+2\hat{x}}_{\text{linear}} + 3\hat{x}^2}_{\text{linear}}\right],\qquad(2.30)$$

after a taylor expanding. The linear and non-linear system are indicated in the equation. The exact solution to the linear problem is given by

$$\hat{x}_{lin} = \frac{\hat{U}_r^2}{1 - 2\hat{U}_r^2} \left[ 1 - \cos\left(\hat{\omega}_m \hat{t} \sqrt{1 - 2\hat{U}_r^2}\right) \right].$$

(2.31)

The linear solution predicts an increased amplitude and further reduction of the resonance frequency as the bias ratio increases. This additional reduction of the resonance frequency is the well known spring softening effect. A closed form solution does not exists for the non-linear approximation. Hence, at this point the original hard non-linear differential equation is converted into another hard non-linear differential equation. Fortunately, an approximate solution can be found to the non-linear problem on the form in Eqn. 2.30. The Method of Multiple Scales (MMS) is an efficient perturbative method suited for approximate solutions to non-linear problems such as this one. MMS has the advantage over regular perturbation methods that it is capable of canceling out secular terms in the expansion, that otherwise leads to unbounded solutions. The idea of MMS is to find an approximate solutions on the form

$$x = x_0(T_0, T_1, ...) + \epsilon x_1(T_0, T_1, ...) + ...$$

where  $T_n = \epsilon^n t$ , (2.32)

where  $\epsilon$  is the perturbation parameter,  $T_n$  represents different time scales,  $T_0$  is the fastest time scales and the times scales become progressively slower

#### 2.2. DYNAMIC MODEL

as n increases. The solution of interest is an extended version of the general linear solution,  $x_{lin}$ , where the amplitude and frequency varies on higher order time scales

$$x_0 = A(T_1)e^{-i\omega(T_1)T_0} + A^*(T_1)e^{i\omega(T_1)T_0}\hat{U}_r^2.$$

(2.33)

The solution provided by the MMS analysis yields

$$\hat{x}_{MMS} = \underbrace{\frac{\hat{U}_r^2}{1 - 2\hat{U}_r^2}}_{\text{amplitude}} \left[ 1 - \cos\left(\hat{\omega}_m t \underbrace{\sqrt{1 - \hat{U}_r^2}}_{\text{Linear}} \left[ 1 - \underbrace{\frac{3\hat{U}_r^4}{(1 - 2\hat{U}_r^2)^2}}_{\text{Non-linear}} \right] \right) \right]. \quad (2.34)$$

The same amplitude as the linear approximation is found by the MMS analysis, but the resonance frequency has a correction term.

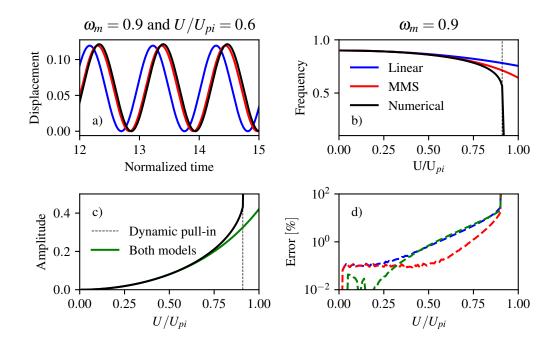

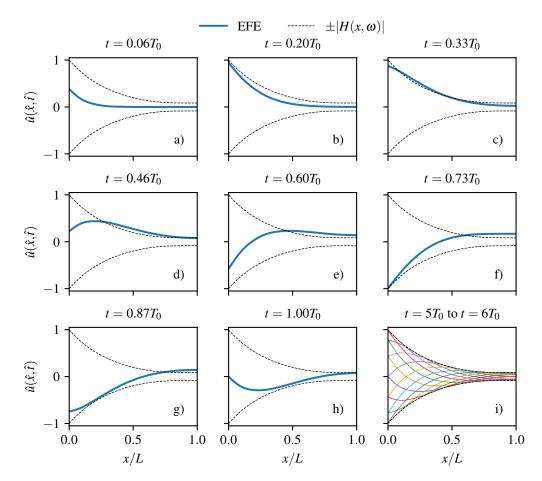

$U_r$  is a positive parameter ranging from zero to 4/27, consequently a subtraction of the positive non-linear correction term will always lead to a further reduction in frequency or from a physical point of view a larger degree of spring softening. Notice, the higher order frequency correction term equals to three times the amplitude squared. It indicates a direct coupling between the amplitude and the frequency, which is not predicted by the linear model. Equation 2.30 is a variation of the well known duffing equation, and MMS step by step derivations of similar problems can be found in [21]. The linear model and the MMS model have both been used to approximate the dynamics of Eqn. 2.27, and the two models are compared to numerical results in Fig. 2.3. The solution to Eqn. 2.27 is shown in a) for  $\hat{\omega}_m$  and  $U/U_{pi}$  equal to 0.9 and 0.6, respectively. The higher precision of the phase is clearly visible for the MMS model. It is the general case for all bias values as seen in b), where the resonance frequency is plotted as function of bias ratio. The displacement amplitude is plotted in c) where a good agreement between the models and the numerical solution is observed up to approximately 70 %of the pull-in voltage, above this point even higher order corrections will be required. Finally, the errors of the modelled parameters are compared to the numerical solution in d). The same color coding has been used, blue and red are used for the resonance frequency and green is used for the amplitude. The numerical resonance frequency is determined by Fourier transforming the displacement solution and then locating the position of the main peak. The plateau observed for the frequency estimates (blue and red) is due the precision of the numerical determination of the frequency.

The energy is conserved for the small ka models due to the absence of damping. Higher order expansions of the radiation impedance would be very interesting, since such models include a non-zero real part and allow the system

Figure 2.3: The linear and non-linear models are compared to a numerical solution to Eqn. 2.27 for various parameters. The solution to Eqn. 2.27 is plotted in figure a) for  $\omega_m$  and  $U/U_{pi}$  equal to 0.9 and 0.6, respectively. The resonance frequency versus applied DC bias is plotted in b), with  $\omega_m = 0.9$ . Figure c) shows amplitude versus applied DC bias. The amplitude is identical for both models and independent of  $\omega_m$ . Figure d) shows the error between the models and the numerical solution. The green dashed line is the amplitude error, and the error of the resonance frequency is shown by the blue and red dashed lines for the linear and the MMS model, respectively.

#### 2.2. DYNAMIC MODEL

to radiate energy into the medium. A higher order expansion of the radiation impedance is an effortless procedure which gives

$$Z \approx \rho_m c_m A \left[ \frac{(ka)^2}{2} + \frac{8ika}{3\pi} \right], \qquad (2.35)$$

but problems occur when this expression is transformed back to the time domain. By using Eqn. 2.25 to transform the second order approximation back to the time domain one gets

$$f_{RI} = -\underbrace{\frac{\pi\rho_m a^4}{2c_m} \frac{\mathrm{d}^3 x}{\mathrm{d}t^3}}_{\text{Jerk}} + \underbrace{\frac{8\rho_m a^3}{3} \frac{\mathrm{d}^2 x}{\mathrm{d}t^2}}_{\text{Inertia}}.$$

(2.36)

Multiple challenges arise from this expression. First and most important is the minus in front of the jerk term. A non-positive constant in front of a derivative in a linear  $n^{\text{th}}$ -order differential equation will have a positive eigenvalue that guarantees an unstable system. Though the CMUT equation is non-linear this unstably criterion still applies. A second challenge is the additional initial conditions. The order of the differential equation increases with the expansion order of the radiation impedance. The original equation is a second order differential equation, but, by introducing Eqn. 2.36 the approximate differential equation becomes of third order. The problem here is how to address the additional initial condition in a physical meaningful way. These challenges are not easy to overcome and illustrate the complexity of modelling the CMUT dynamics, which suggests advanced numerical methods to model the interaction with the CMUT and the medium.

#### 2.2.2 Large ka limit

All CMUT design in this thesis are designed by the  $\lambda/2$  pitch constraint, whih only allows 2ka values between 0 and  $\pi/2$ . Nevertheless, the large ka regime is still interesting as damping appears in this limit. An asymptotic expansion efficiently approximates the radiation impedance in the limit where  $ka \to \infty$

$$Z \sim \rho_m c_m A$$

as  $ka \to \infty$ . (2.37)

A constant radiation impedance transforms into a damping term, and now all the stored energy in the system will be converted into acoustic radiation. The rate at which the energy is converted is determined by a damping term, which is given by

$$f_{RI} = \rho_m c_m A \frac{\mathrm{d}x}{\mathrm{d}t} = \rho_m c_m \pi a^2 \frac{\mathrm{d}x}{\mathrm{d}t}$$

(2.38)

and the equation of motion in the large ka regimes can then be expressed as

$$m\frac{\mathrm{d}^2 x}{\mathrm{d}t^2} + \rho_m c_m A \frac{\mathrm{d}x}{\mathrm{d}t} + kx = \frac{\varepsilon A U^2}{2(g-x)^2}.$$

(2.39)

After nondimensionalization using the same dimensionless parameters as in section 2.2.1 the equation simplifies to

$$\frac{\mathrm{d}^2 \hat{x}}{\mathrm{d}\hat{t}^2} + \frac{1}{\hat{\tau}} \frac{\mathrm{d}\hat{x}}{\mathrm{d}\hat{t}} + \hat{x} = \frac{\hat{U}_r^2}{(1-\hat{x})^2} \quad \text{where} \quad \hat{\tau} = \frac{m\omega_0}{\rho_m c_m \pi a^2}.$$

(2.40)

The dynamics in both the small ka regime and the large ka regime is fully determined by two parameters, and both regimes share the electrostatic voltage ratio  $\hat{U}_r$ . The small ka regime has an added mass, whereas the large karegime has a damping term with a characteristic decay time  $\hat{\tau}$ . The characteristic decay time determines the bandwidth of the CMUT, large bandwidth corresponds to a small  $\hat{\tau}$  and narrow bandwidth corresponds to a large  $\hat{\tau}$ . Hence, from a medical imaging perspective a small  $\hat{\tau}$  is desired, since it improves the axial resolution in an ultrasound image. Equation 2.40 does, equivalent to the small ka model, not have any exact analytical solution due to the non-linear electrostatic term, and the options are therefore once again either approximate or numerical solutions. One approach is to use a phasespace analysis, it allows multiple solutions to be visualized at the same time and provides a quick overview of the dynamics. The phase phase is easily obtained by expressing Eqn. 2.40 as two coupled first order differential equations given by

$$\frac{\mathrm{d}\hat{x}}{\mathrm{d}\hat{t}} = \hat{v} \tag{2.41}$$

$$\frac{\mathrm{d}\hat{v}}{\mathrm{d}\hat{t}} = -\frac{1}{\hat{\tau}}\hat{v} - \hat{x} + \frac{\hat{U}_r^2}{(1-\hat{x})^2}.$$

(2.42)

The phase-space analysis describes the dynamics of a CMUT with a fixed DC bias subject to multiple initial conditions. For each set of initial conditions an ODE solver has been used to determine whether the CMUT spirals into a stable stationary point or if it collapses into the pull-in configuration. The stationary point (also called the operation point) can be found analytically for the non-linear CMUT parallel plate model as a solution to Eqn. 2.1. The phase-portrait analysis can be used to examine the concept of a dynamic pull-in voltage. When inertia and damping are included in CMUT modeling the pull-in condition becomes more involved than the static case and cannot no longer be expressed in simple terms. If the kinetic energy stored in the CMUT

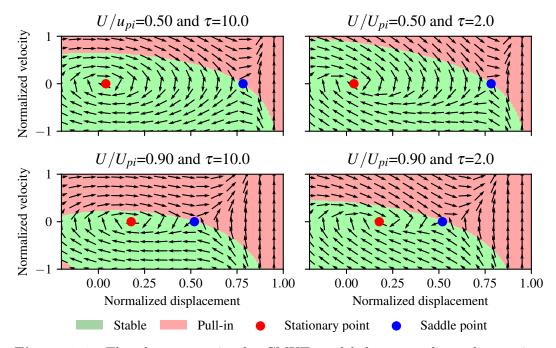

Figure 2.4: The phase portrait of a CMUT modeled as a nonlinear harmonic oscillator. The stationary point is marked with a red dot and the saddle point is marked with the blue dot. The green region indicates a stable state and the red region indicates an unstable state (dynamic pull-in).

plate is high enough, then ending up in the pull-in condition is inevitable even tough the applied bias is below the static pull-in voltage. The dynamic pullin condition depends on both the damping and the applied bias, and is not a one dimensional parameter as the static case, but should in the simplest possible way, be perceived as a two dimensional parameter space. A single point on the rim of the dynamic pull-in region can be found analytically by examining the additional two solutions of Eqn. 2.1, here denoted  $x_2$  and  $x_3$ . The second solution  $x_2$  is physical in the sense that  $x_2 < 1$ , meaning that it represents a point inside the CMUT cavity. One can show this solution is semi stable and therefore defines a saddle point in the phase portrait. This saddle point must lie on the rim of the dynamic pull-in region. The last solution  $x_3$  possesses no physical meaning since the  $x_1 > 1$  for all applied biases, and corresponds to a displacement below the CMUT. Four different CMUT phase portraits are shown in Fig. 2.4 for multiple values of  $U/U_{pi}$  and  $\hat{\tau}$ .

The direction of each arrow in the phase portrait is evaluated by inserting values of x and v into Eqn. 2.41 and 2.42. On top of the phase portraits are

a green and red color coding added to indicate stable and unstable states, respectively. The code used to determine the final state of the CMUT is verified by the analytic saddle point that lies on the rim of the stable region in all cases, as predicted. The stable dynamic region is reduced as the applied bias approaches the static pull-in condition. Likewise a reduction of the dynamic region is observed when the characteristic decay time is increased.

The large ka model radiates 100% of the stored energy into the medium, which is highly desired from a transducer point of view. Unfortunately, 2kahas an upper bound of  $\pi/2$  due to the  $\lambda/2$  pitch constraint used in medical imaging applications. The small ka models radiation 0% and the large kamodel radiates 100% and the true radiation is somewhere in between.

#### 2.2.3 Full description

In the previous sections the case of small and large ka values were examined. In this section the radiation impedance is transformed back to the time domain without any approximations. It leads to a complicated differential equation, and the aim is not to solve this equation but to determine dimensionless parameters. When the radiation impedance is known in the time domain, the force acting on the transducer surface can be found by applying a convolution integral

$$f(t) = \int_0^t z(t-\beta)v(\beta) \,\mathrm{d}\beta. \tag{2.43}$$

The exact radiation impedance in the time domain of a piston in a rigid baffle is derived in [19] and is given by

$$z(t) = \rho_m c_m \pi a^2 \left[ \delta \left( \frac{c_m t}{2a} \right) - \frac{4}{\pi} \left[ 1 - \left( \frac{c_m t}{2a} \right)^2 \right]^{1/2} \right]$$

(2.44)

with  $\delta$  being a delta function. The convolution of a delta yields a damping term, whereas the convolution of square root has to be expressed in terms of an integral. The physical interpretation of this integral is a memory term that depends on the dynamics from the past. The equation of motion after non-dimensionalization can be expressed as

$$\frac{\mathrm{d}^{2}\hat{x}}{\mathrm{d}\hat{t}^{2}} + \frac{1}{\hat{\tau}}\frac{\mathrm{d}\hat{x}}{\mathrm{d}\hat{t}} - \underbrace{2\hat{\eta}\int_{0}^{\hat{t}}\frac{\mathrm{d}\hat{x}}{\mathrm{d}\hat{\beta}}\sqrt{1 - \frac{4\hat{\eta}^{2}\hat{\tau}^{2}}{\pi}(\hat{t} - \hat{\beta})^{2}}_{\mathrm{Memory}}\mathrm{d}\hat{\beta} + \hat{x} = \frac{\hat{U}_{r}^{2}}{(1 - \hat{x})^{2}},\qquad(2.45)$$

#### 2.3. CHAPTER SUMMERY

where

$$\hat{\tau} = \frac{m\omega_0}{\rho_m c_m \pi a^2} \qquad \hat{\eta} = \frac{\rho_m c_m^2 a}{m\omega_0^2} \tag{2.46}$$

An analysis of the non-dimensional parameters can provide some quantitative information and scaling laws. The product of  $\hat{\tau}\hat{\eta}$  is a measure of the ratio between the damping and memory force. The square product is present inside the convolution integral, and will therefore directly influence the dynamics of the system.

$$\hat{\tau}\hat{\eta} = \frac{1}{\pi} \frac{c_m}{a\omega_0} \tag{2.47}$$

The product between the damping and the memory term contains three parameters,  $c_m$ , a, and  $\omega_0$ . From a medical imaging perspective the sound of speed is fixed and approximately 1540 m/s. The frequency and the radius are two coupled parameters, which can be chosen independently of each other by adjusting the plate thickness accordingly. As an example a 10 MHz CMUT transducer with a 25 µm cell radius would have a  $\hat{\tau}\hat{\eta}$ -product of 0.31 in immersion, whereas the ratio would be 0.07 for applications in air, assuming a sound of speed of 340 m/s. These simple calculations predict an increased influence of the memory term for immersion rapidly becomes complicated and not suited for analytic modeling. From this point advanced numerical methods such as FEM will be necessary in order to move forward, and these methods can include effects that has been neglected in this theory chapter, such as substrate/backing effects, array configuration, lens materials, electronics among other.

### 2.3 Chapter summery

A theoretical analysis of the a single CMUT cell was given in this chapter. A perturbative solution to the deflection of the clamped plate subject to an electrostatic pressure was derived. The dynamics of a single CMUT cell was analyzed using a non-linear model in the regime of small and large ka values. The small ka analysis demonstrated a reduction of the resonance frequency due to an additional mass loading and a damping mechanisum was inctroduced in the large ka regime. A phase portrait analysis was used to visualize the dynamics of the large ka regime. The dynamical parameter space was observed to depend on the applied bias and the damping of the CMUT plate.

# CHAPTER 3

### Row-Column-Addressed Arrays

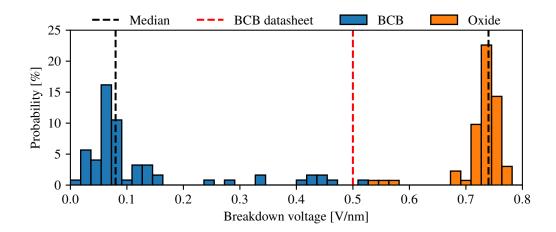

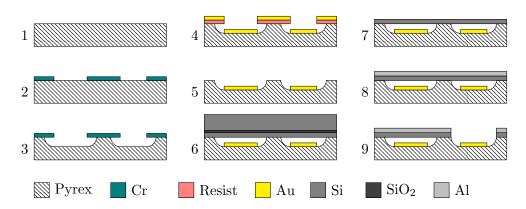

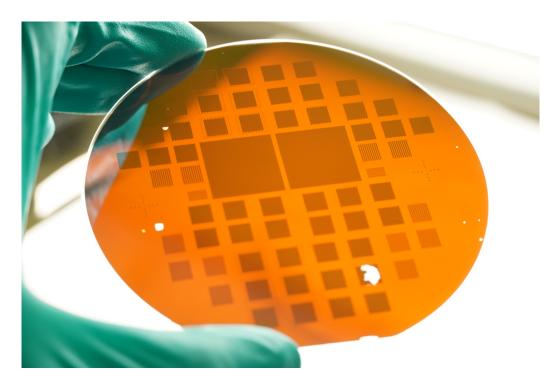

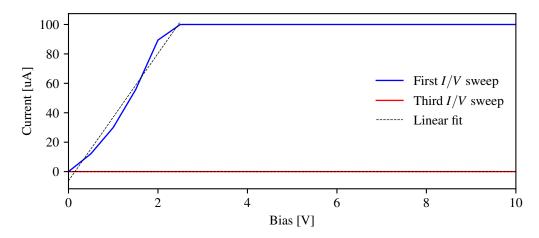

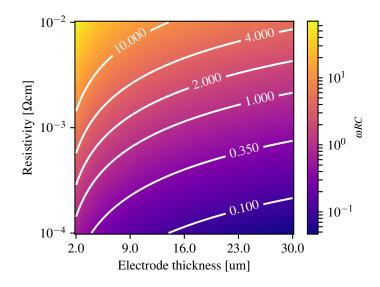

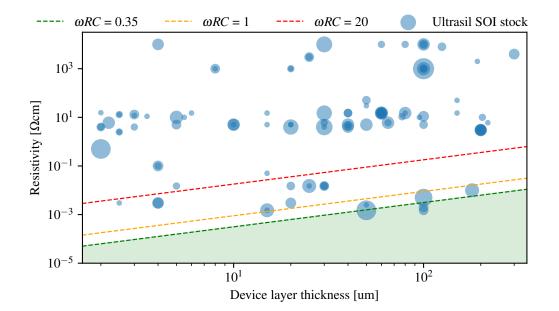

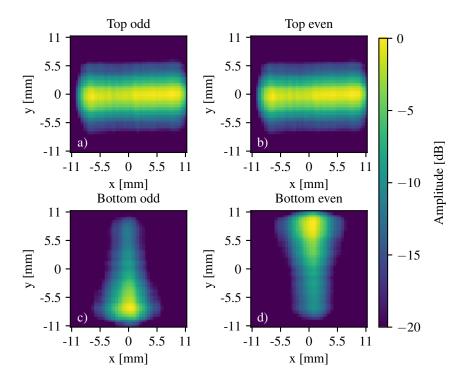

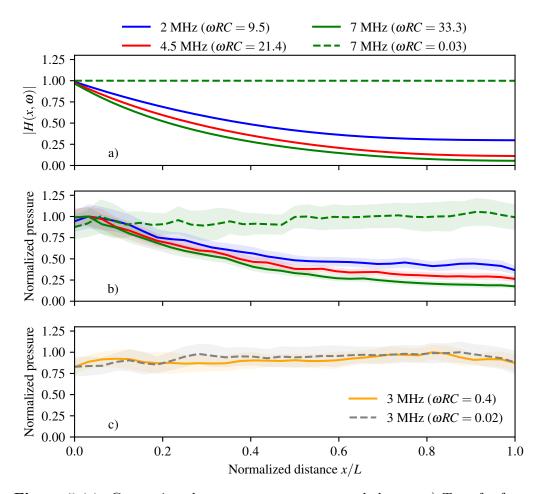

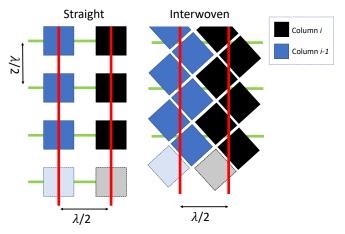

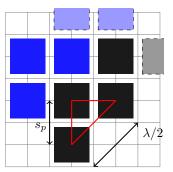

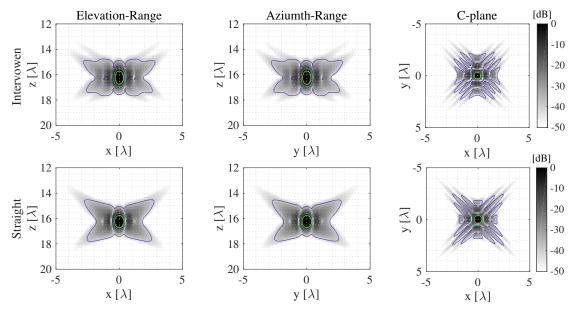

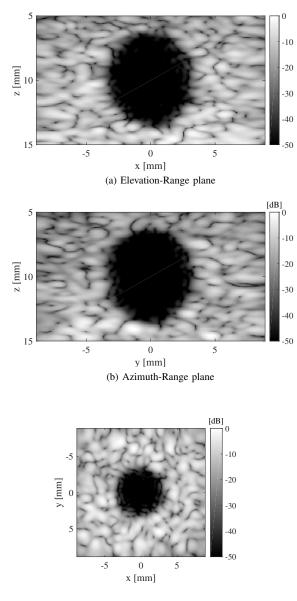

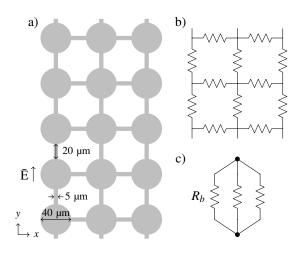

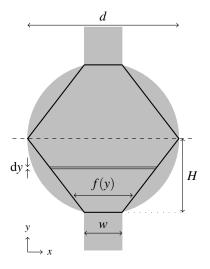

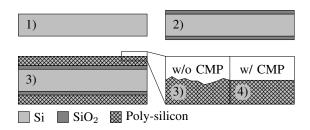

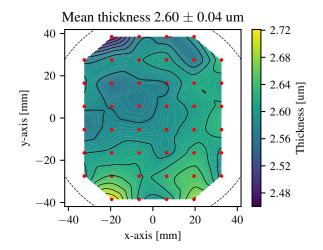

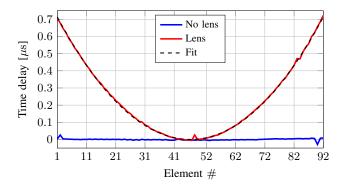

A generic examination of a Row-Column-Addressed (RCA) array will be presented in this chapter, the geometry, the advantageous properties, and challenges associated with such arrays are the main focus. A short literature review of the row-column technology will initially be given. Relevant scaling laws of RCA arrays are presented after the literature review, and then theoretical considerations regarding edge waves, and finally, a discussion of a substrate coupling phenomenon that can occur for specific CMUT row-column fabrication techniques.