# CMOS Analog IC Design: Fundamentals

Erik Bruun

# **ERIK BRUUN**

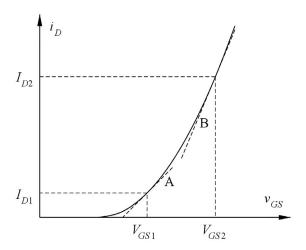

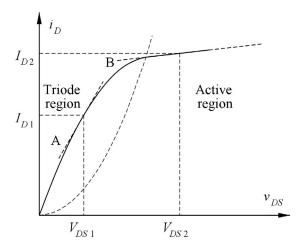

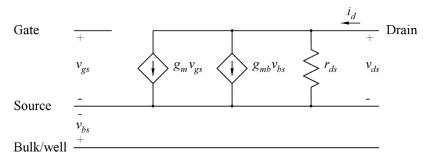

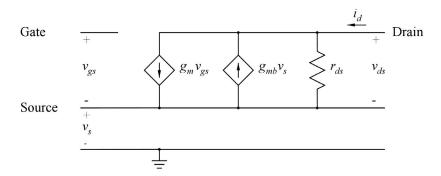

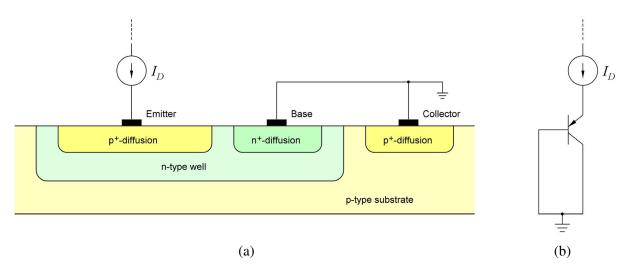

# CMOS ANALOG IC DESIGN FUNDAMENTALS

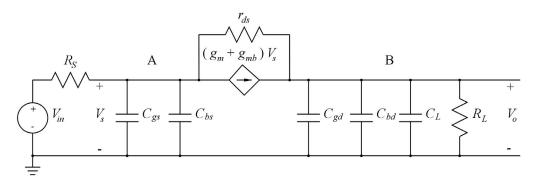

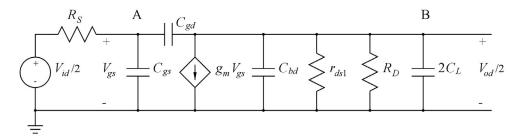

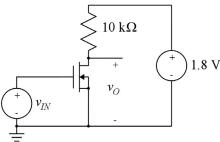

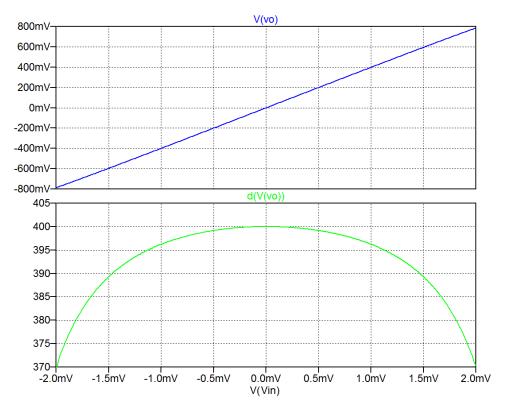

CMOS Analog IC Design: Fundamentals 3<sup>rd</sup> edition

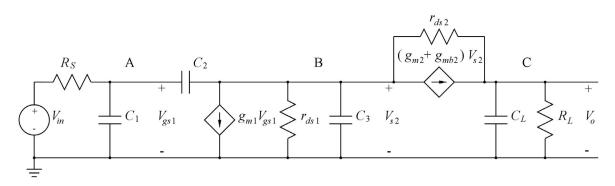

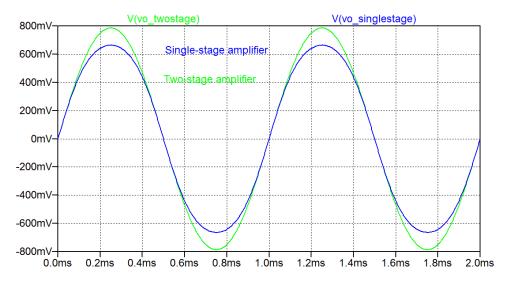

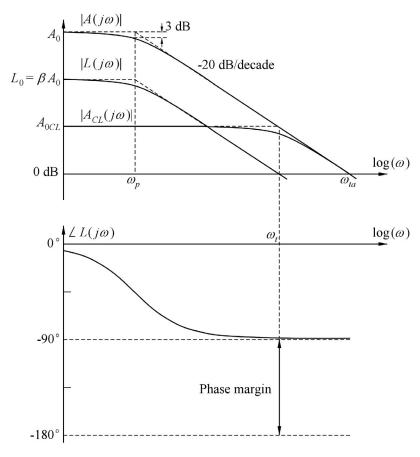

© 2022 Erik Bruun & <u>bookboon.com</u>

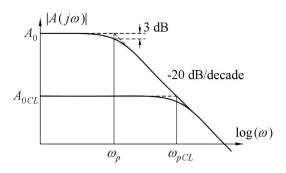

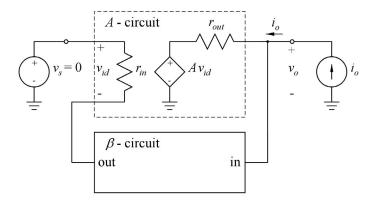

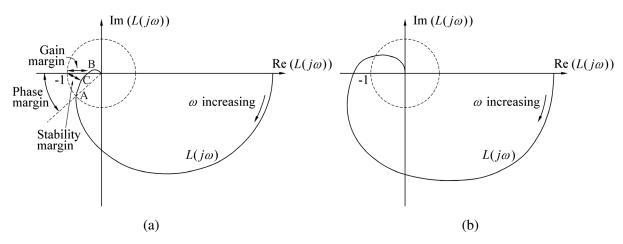

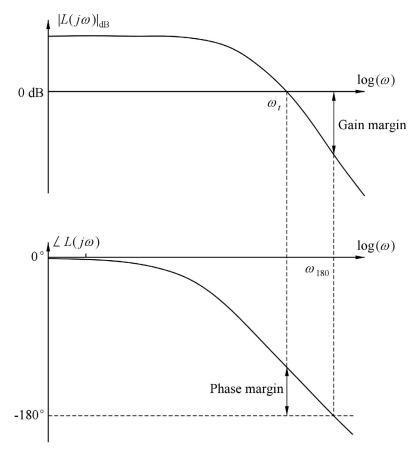

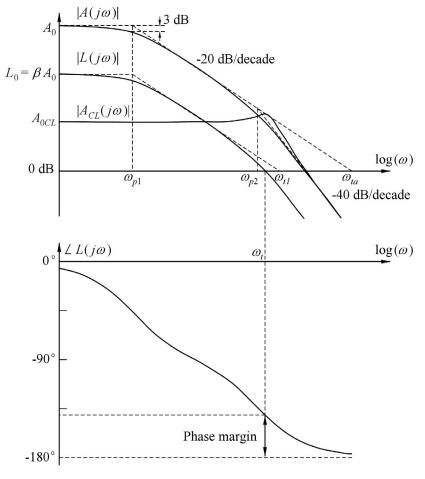

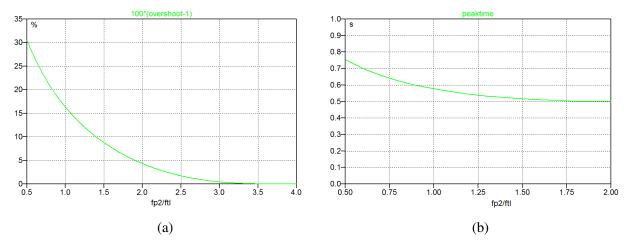

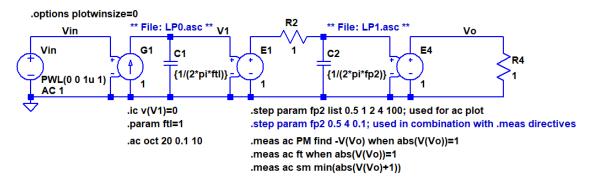

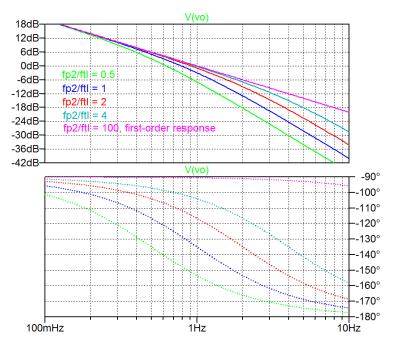

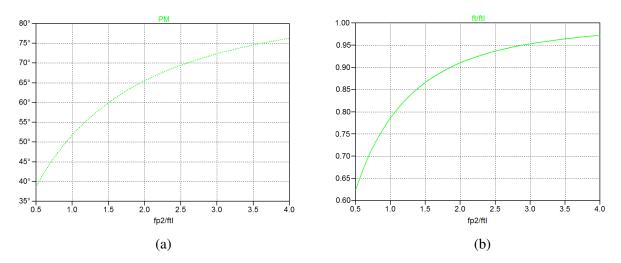

ISBN 978-87-403-4247-5

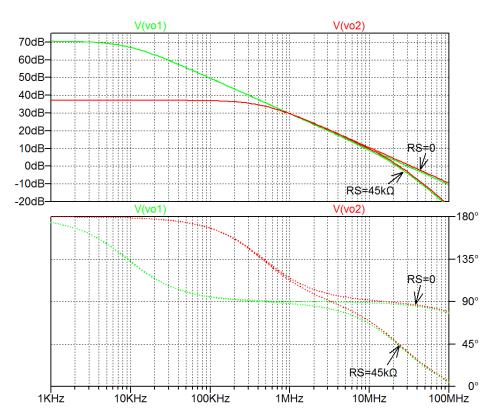

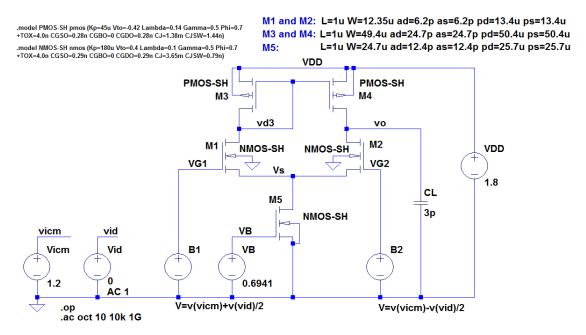

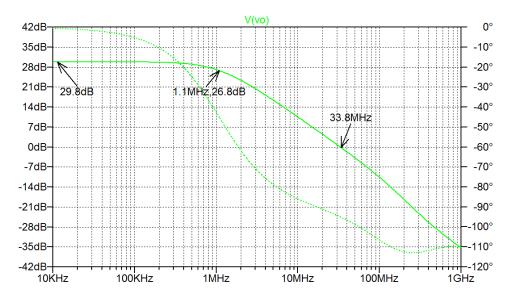

# **CONTENTS**

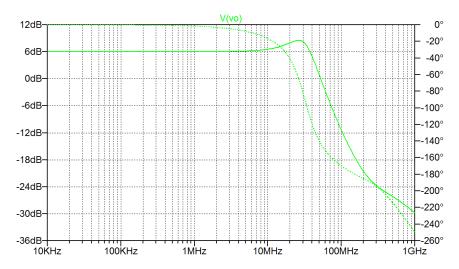

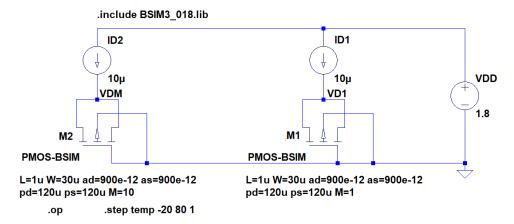

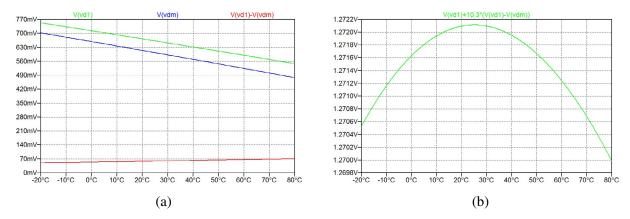

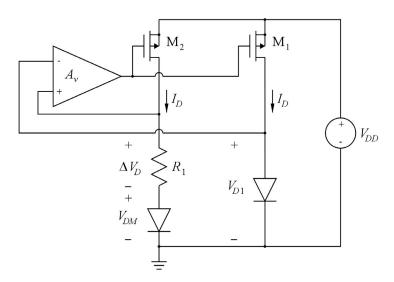

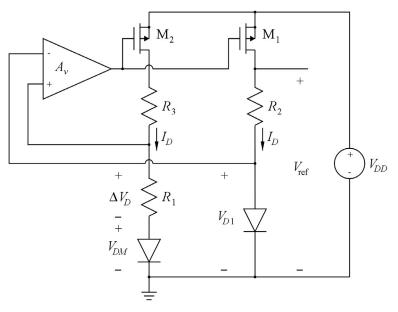

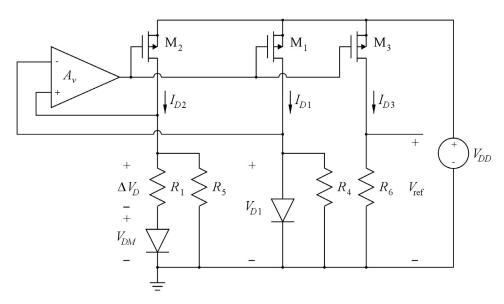

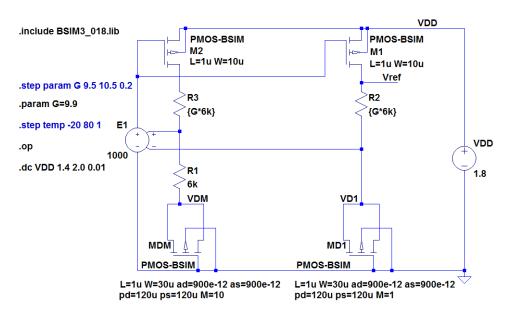

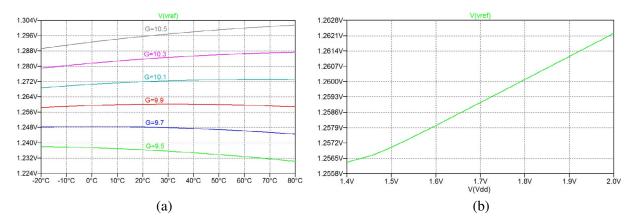

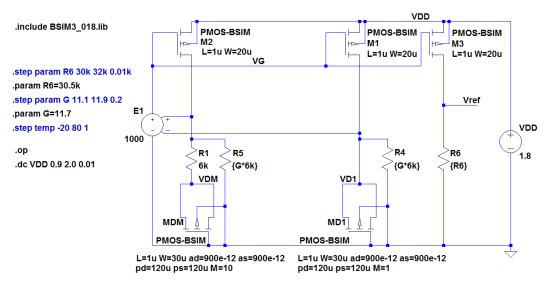

|     | Preface                                                                  | 7   |

|-----|--------------------------------------------------------------------------|-----|

|     | Chapter 1 – Introduction                                                 | 11  |

| 1.1 | CMOS technology                                                          | 11  |

| 1.2 | Why analog circuit design?                                               | 12  |

| 1.3 | Design methodology                                                       | 14  |

|     | References                                                               | 16  |

|     | Multiple-choice test                                                     | 17  |

|     | Chapter 2 – Basic Concepts                                               | 19  |

| 2.1 | Signals                                                                  | 19  |

| 2.2 | Circuit elements                                                         | 24  |

| 2.3 | Circuit theorems                                                         | 30  |

| 2.4 | Circuit analysis                                                         | 36  |

|     | References                                                               | 43  |

|     | Multiple-choice test                                                     | 43  |

|     | Problems                                                                 | 45  |

|     | Chapter 3 – The MOS Transistor                                           | 49  |

| 3.1 | Fundamentals of pn diodes                                                | 49  |

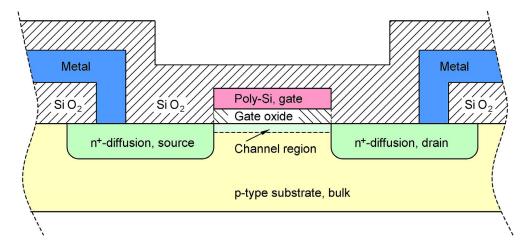

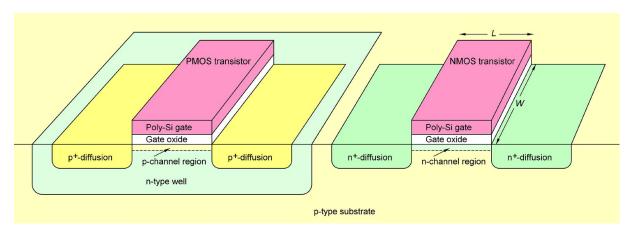

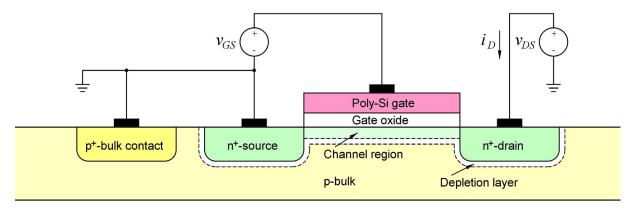

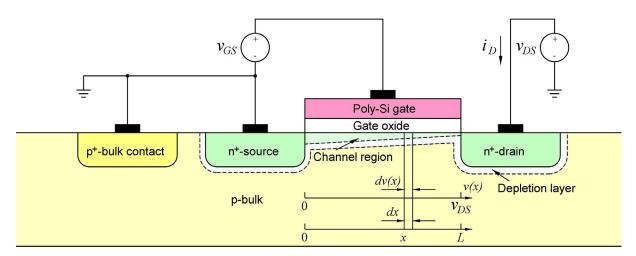

| 3.2 | Physical characteristics of the MOS transistor                           | 53  |

| 3.3 | Electrical characteristics of the MOS transistor                         | 56  |

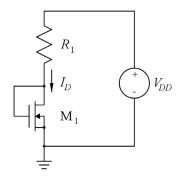

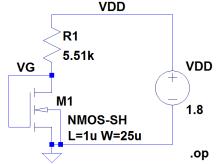

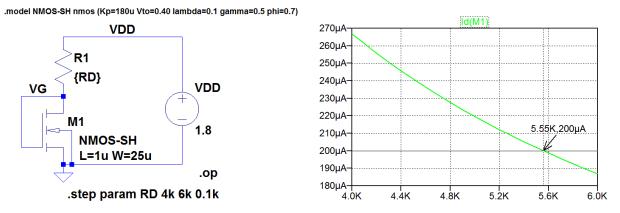

| 3.4 | Examples of the use of the Shichman-Hodges transistor model              | 65  |

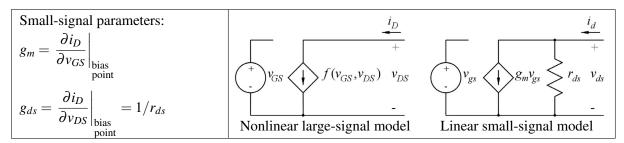

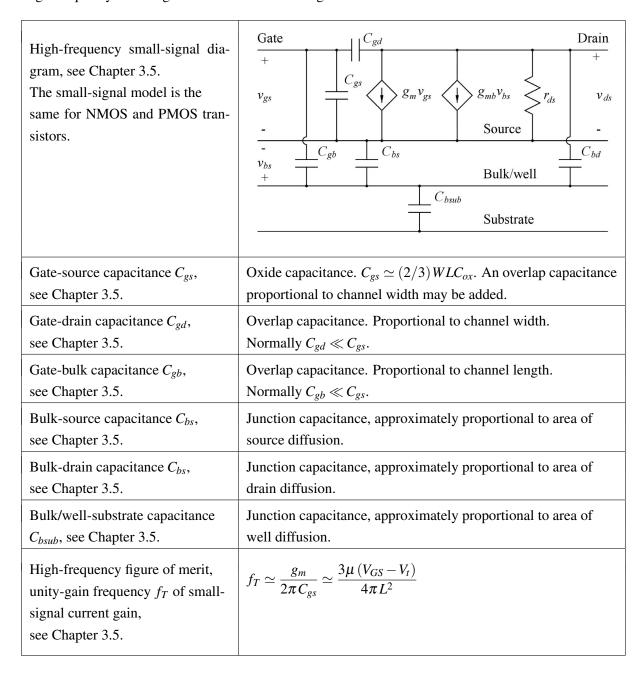

| 3.5 | Small-signal models                                                      | 72  |

| 3.6 | Deriving a small-signal equivalent circuit from a large-signal schematic | 87  |

| 3.7 | Advanced transistor models                                               | 93  |

|     | References                                                               | 97  |

|     | Multiple-choice test                                                     | 98  |

|     | Problems                                                                 | 100 |

|     | Chapter 4 – Basic Gain Stages                                            | 106 |

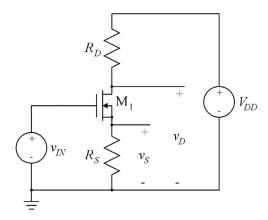

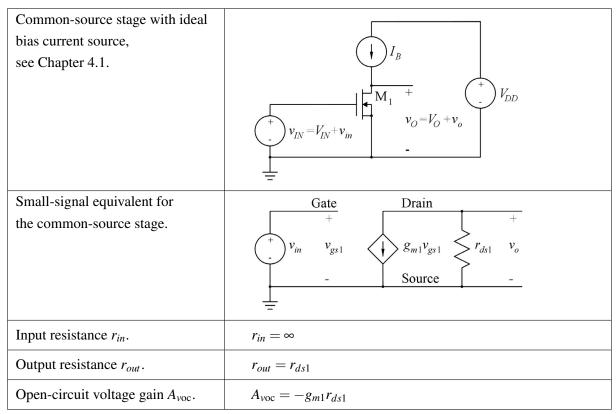

| 4.1 | The common-source stage at low frequencies                               | 107 |

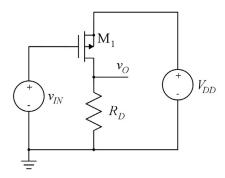

| 4.2 | The common-drain stage at low frequencies                                | 113 |

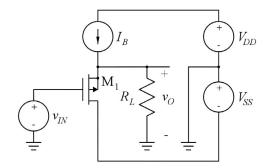

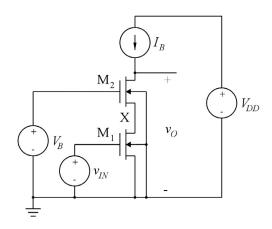

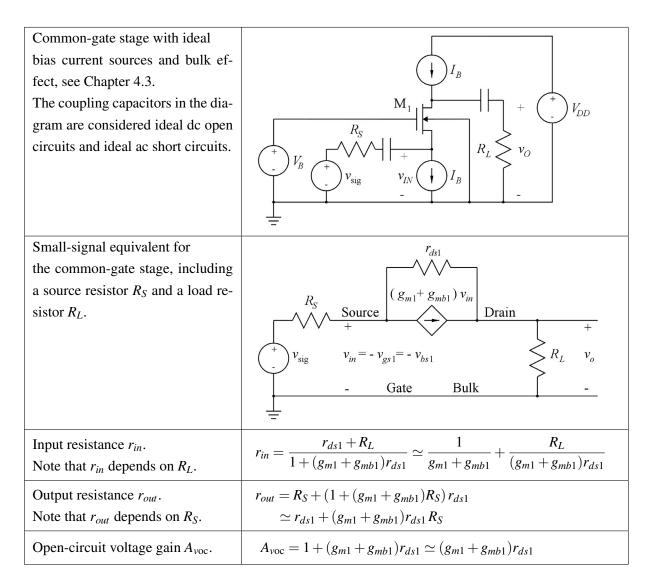

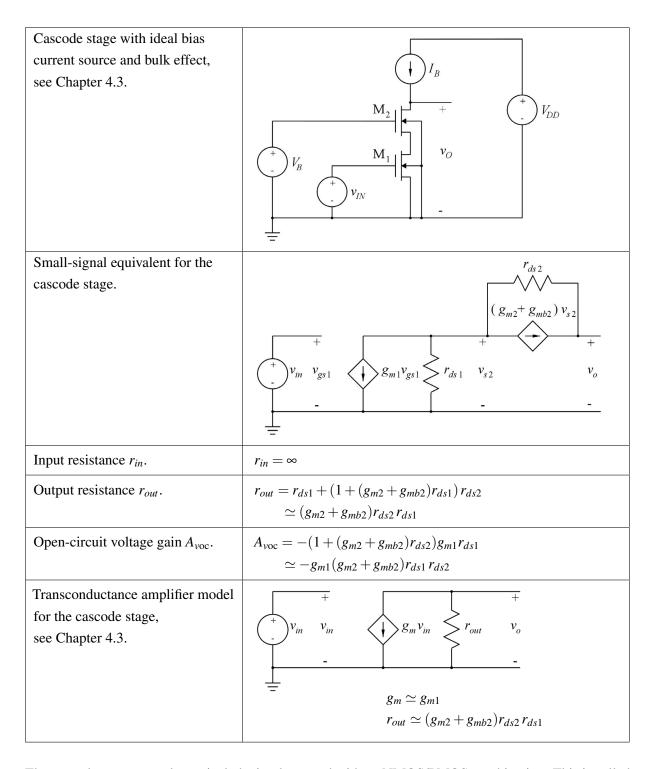

| 4.3 | The common-gate stage and the cascode stage at low frequencies           | 120 |

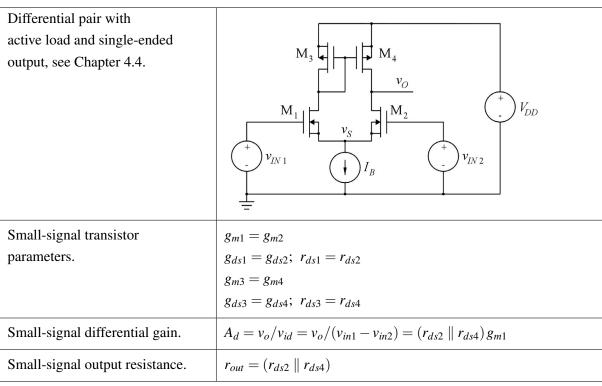

| 4.4 | The differential pair at low frequencies                                 | 132 |

| 4.5 | Frequency response of the basic gain stages                              | 152 |

|     | References                                                               | 170 |

|     | Multiple-choice test                                                     | 171 |

|     | Problems                                                                 | 175 |

|     | Chapter 5 – Multistage Amplifiers                            | 183 |

|-----|--------------------------------------------------------------|-----|

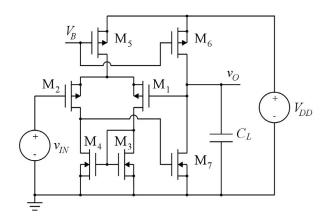

| 5.1 | Cascode opamps                                               | 185 |

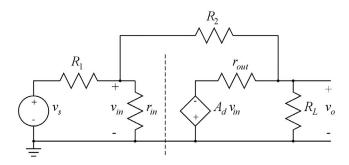

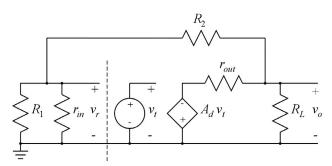

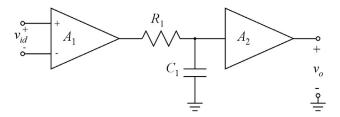

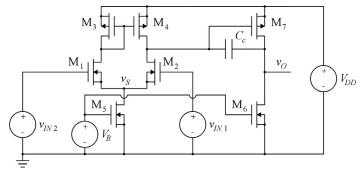

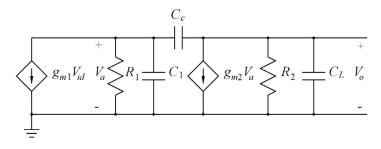

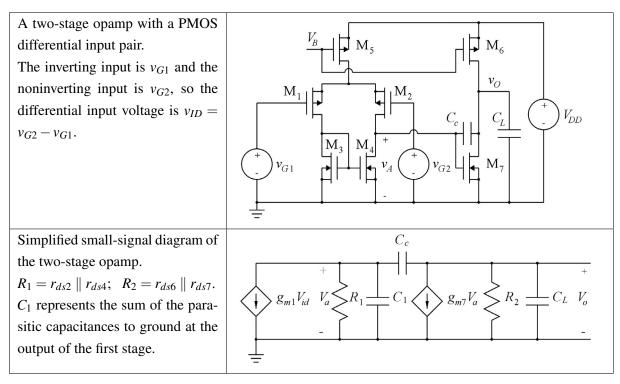

| 5.2 | The two-stage opamp                                          | 186 |

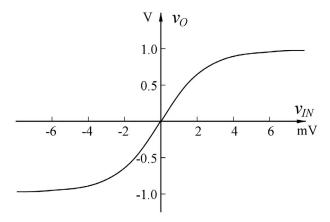

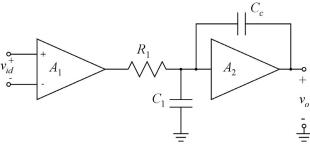

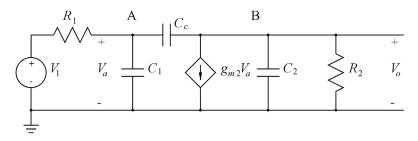

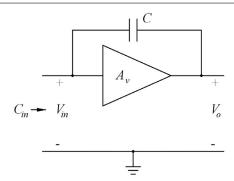

| 5.3 | The two-stage opamp with feedback                            | 191 |

|     | References                                                   | 195 |

|     | Multiple-choice test                                         | 196 |

|     | Problems                                                     | 198 |

|     | Chapter 6 – Feedback                                         | 201 |

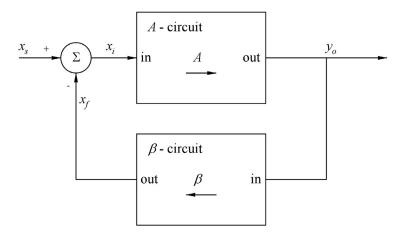

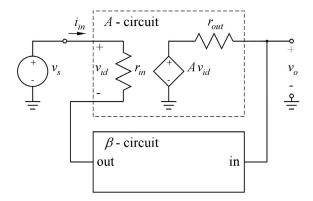

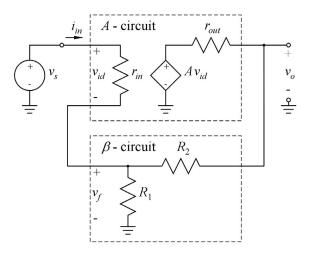

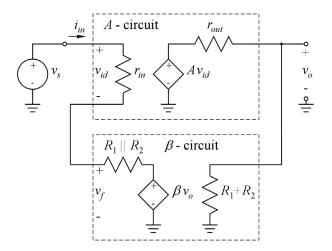

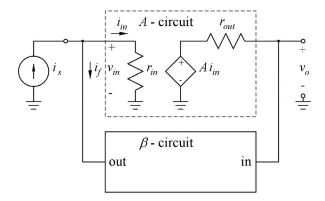

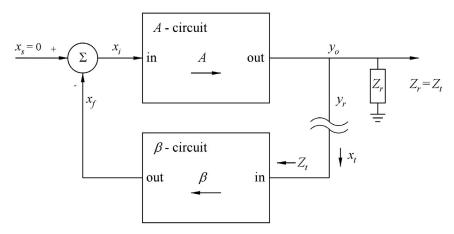

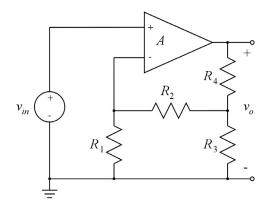

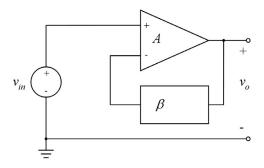

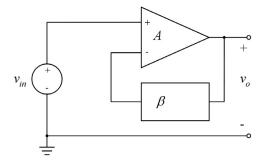

| 6.1 | The basic feedback structure                                 | 201 |

| 6.2 | Advantages of feedback                                       | 202 |

| 6.3 | Feedback topologies                                          | 211 |

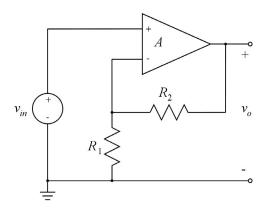

| 6.4 | The inverting amplifier                                      | 215 |

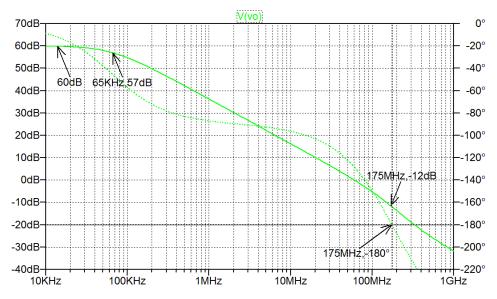

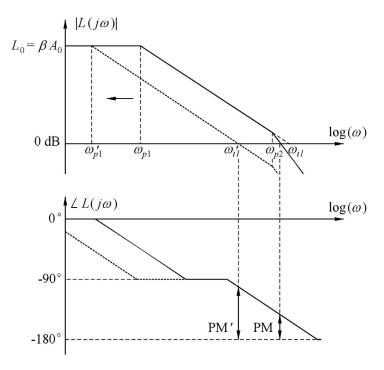

| 6.5 | Stability                                                    | 219 |

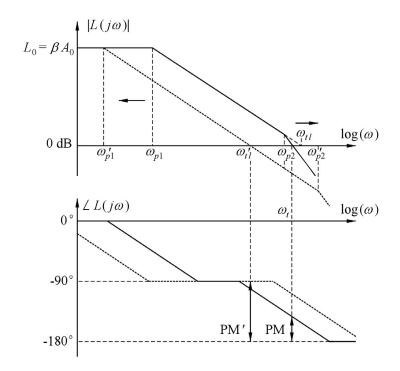

| 6.6 | Frequency compensation                                       | 238 |

|     | References                                                   | 248 |

|     | Multiple-choice test                                         | 249 |

|     | Problems                                                     | 251 |

|     | Chapter 7 – The Two-Stage Opamp                              | 257 |

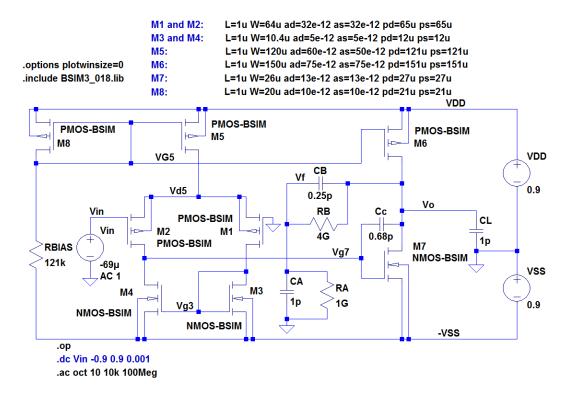

| 7.1 | Specifications for a design example                          | 258 |

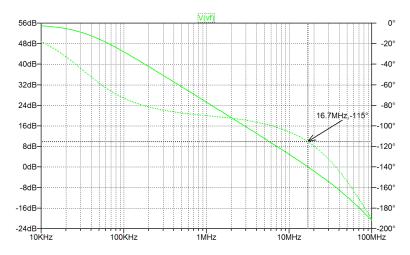

| 7.2 | Bandwidth and stability requirements                         | 260 |

| 7.3 | Bias point and transistor dimensions                         | 264 |

| 7.4 | Design verification and iteration                            | 269 |

|     | References                                                   | 273 |

|     | Multiple-choice test                                         | 273 |

|     | Problems                                                     | 275 |

|     | Chapter 8 – Bias Circuits, Bandgap References                |     |

|     | and Voltage Regulators                                       | 278 |

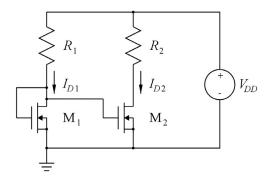

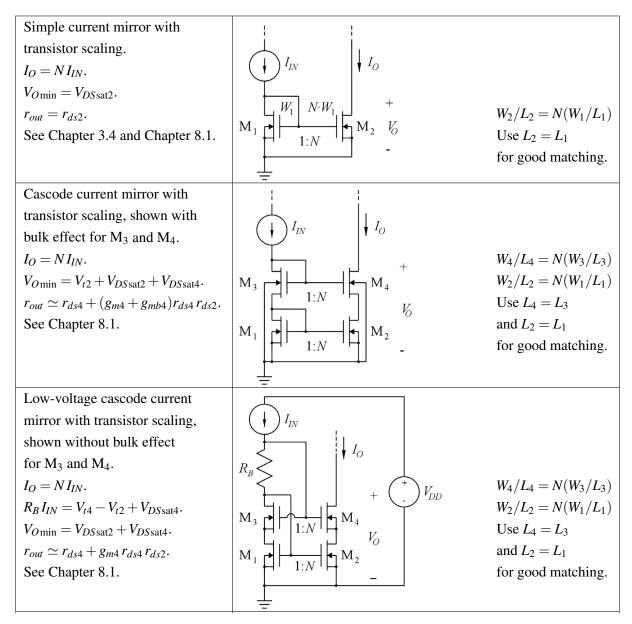

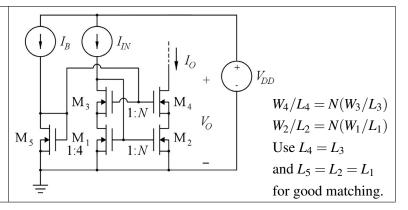

| 8.1 | Current mirrors                                              | 278 |

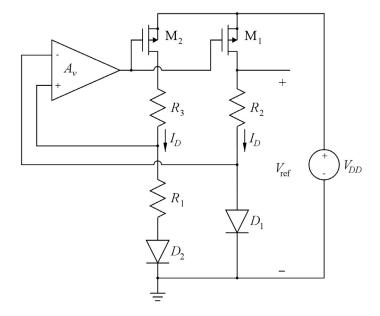

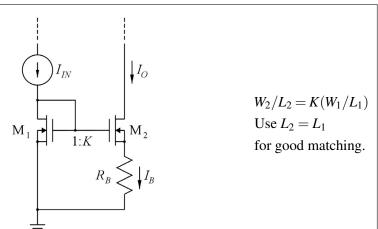

| 8.2 | Bias current circuits with reduced supply voltage dependency | 283 |

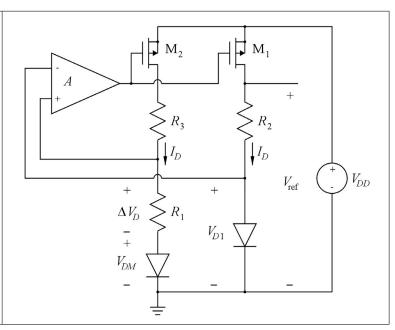

| 8.3 | Bandgap voltage references                                   | 288 |

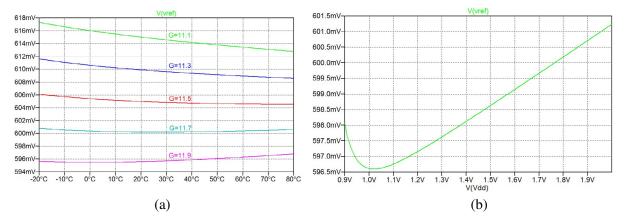

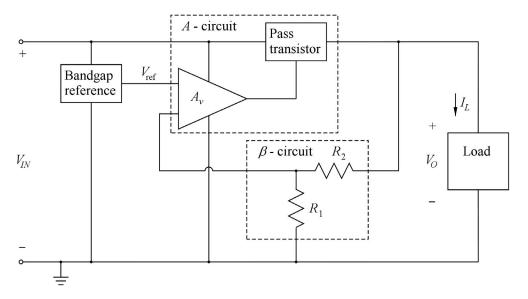

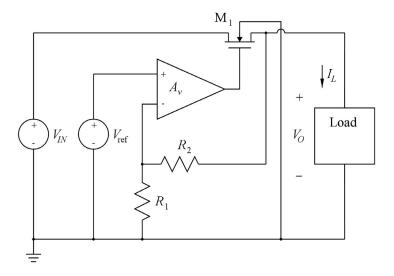

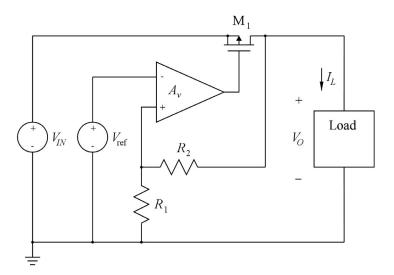

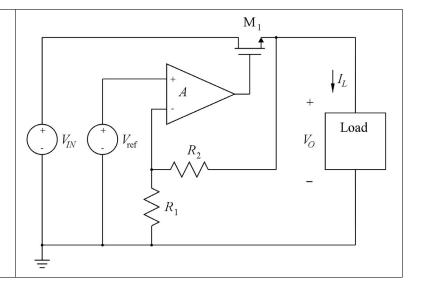

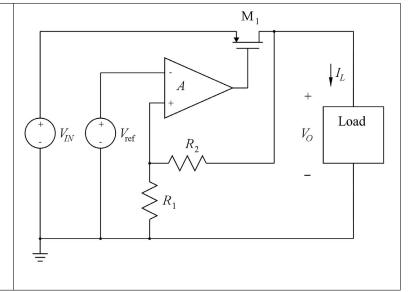

| 8.4 | Voltage regulators                                           | 296 |

|     | References                                                   | 302 |

|     | Multiple-choice test                                         | 303 |

|     | Problems                                                     | 305 |

|     | Chapter 9 – Essential Results and Equations                  | 312 |

| 9.1 | Design methodology                                           | 312 |

| 9.2 | Device models, linear passive devices                        | 314 |

| 9.3 | Device model, pn diode                                       | 314 |

|      | Index                                           | 340 |

|------|-------------------------------------------------|-----|

|      | Appendix C – Transistor Models                  | 339 |

|      | Appendix B – Answers to End-of-Chapter Problems | 334 |

|      | Appendix A – Answers to Multiple-Choice Tests   | 332 |

| 9.12 | Voltage regulators                              | 331 |

| 9.11 | Bandgap reference principle                     | 330 |

| 9.10 | Current mirrors and current sources             | 329 |

| 9.9  | The two-stage opamp                             | 328 |

| 9.8  | Feedback                                        | 325 |

| 9.7  | Frequency response of basic gain stages         | 324 |

| 9.6  | Basic gain stages at low frequency              | 319 |

| 9.5  | Device models, MOS transistors                  | 315 |

| 9.4  | Small-signal models                             | 314 |

## **Preface**

This book has been written with the specific goal to serve as a textbook for a first course in CMOS analog integrated circuit design. It is intended for electronics engineering students at bachelor level who have followed basic courses in mathematics, physics, circuit theory, electronics and signal processing.

A distinct feature of this book is the emphasis on the interaction between analytical methods and simulation methods. Traditionally, the teaching of circuit design is based on mathematical models of circuit elements and on basic circuit theorems. Often, simulations are just referred to as additional examples. In this book, simulations using the universally accepted program SPICE (Simulation Program with Integrated Circuit Emphasis) are used throughout. The simulations are integrated into the text, both in order to illustrate and verify the mathematically based theory and in order to develop design methods using the simulator for more accurate design of integrated circuits.

The material presented in this book has been adapted from material used by the author for many years of teaching an introductory one-semester course (5 ECTS credits) in CMOS analog integrated circuit design at the Technical University of Denmark.

Chapter 1 is an introduction to the subject, outlining the basic method for integrated circuit design with close interaction between hand calculations and simulations, and providing a motivation for the study of analog integrated circuit design.

Chapter 2 is a recapitulation of some of the basic theory which you are expected to know already. This recapitulation is used for setting the scene for the following chapters which form the bulk of the course.

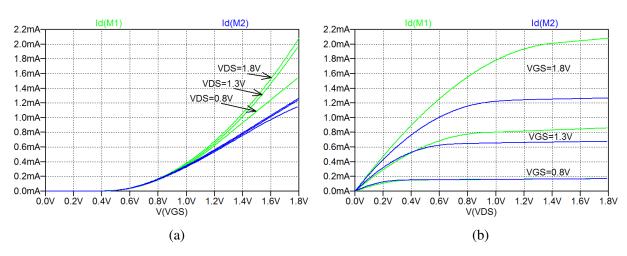

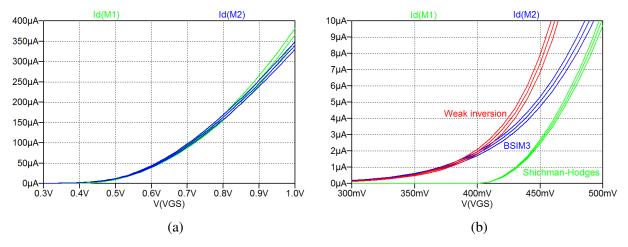

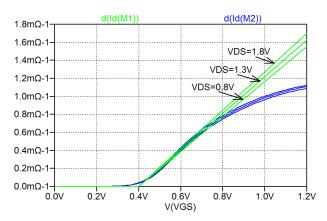

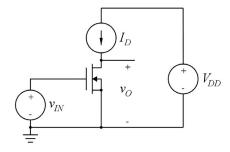

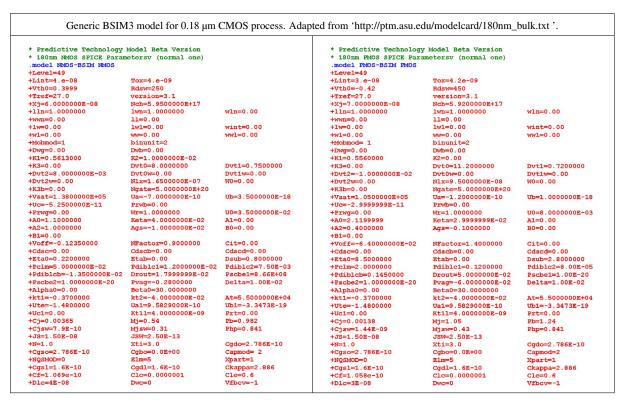

Chapter 3 presents the models used for MOS transistors in the book. For analytical purposes, hand calculations, the Shichman-Hodges model is used. For simulations, both the Shichman-Hodges model and BSIM transistor models are presented.

Chapter 4 describes the basic gain stages in analog CMOS design, i.e., the common-source stage, the common-drain stage, the common-gate stage and the differential pair. A thorough review of the concept of small-signal analysis is given with several examples showing how to build a small-signal model of a gain stage from the transistor schematic of the stage.

Chapter 5 is about multistage amplifiers. It is shown how a simple opamp can be designed by combining the stages introduced in Chapter 3.

Chapter 6 is a brief review of feedback theory. The use of feedback to improve many system parameters in an amplifier is explained. Additionally, conditions for stability in a feedback system are presented. The chapter is also included in order to be able to present a design of the two-stage opamp, considering that the main application of an opamp is as a gain element in a feedback system where the stability of the system is a critical parameter.

Chapter 7 reviews the two-stage opamp and presents a design where the issue of stability in a feedback system is a major consideration.

Chapter 8 gives a brief presentation of some circuits used for biasing of the amplifier circuits presented in the previous chapter.

Finally, Chapter 9 summarizes the essentials from the previous chapters. It is intended as a quick reference to the most important equations and conclusions from the book.

All chapters (except Chapter 1 and Chapter 9) include end-of-chapter problems, and answers to the questions are included in Appendix B. Fully worked-out solutions can be found in the companion book:

Bruun, E., CMOS Analog IC Design: Problems and Solutions, bookboon.

Available from: http://bookboon.com/en/cmos-analog-ic-design-problems-and-solutions-ebook

Also a selection of multiple-choice problems is included after each chapter as a quick practice test. This is meant as a quick tool for testing if the learning objectives defined in the beginning of the chapter have been accomplished. However, it is not a replacement for the end-of-chapter problems. The practical experience obtained by solving a substantial number of problems is essential for the learning process in a field such as integrated circuit design. More practical experience can be achieved from a supplementary book comprising a selection of problems covering many aspects of the design methods from the present book:

Bruun, E. & Jørgensen, I., 2022, CMOS Analog IC Design: Learning by Problem Solving, bookboon. Available from:

http://bookboon.com/en/cmos-analog-ic-design-ebook

The material presented in the present book has been found suitable for a course comprising 12 lectures (with problem solving sessions) and (optionally) an additional final wrap-up lecture. The duration of each lecture is about 2 hours including a 15 minutes break.

The lectures may be organized as follows:

- Lecture 1: Introduction and recapitulation of basic theory (Chapters 1 and 2).

- Lecture 2: MOS transistor basics, Shichman-Hodges transistor model (Chapter 3.1 3.4).

- Lecture 3: Small-signal transistor models and advanced transistor models (Chapter 3.5 3.7).

- Lecture 4: Common-source stage and common-drain stage at low frequencies (Chapter 4.1 4.2).

- Lecture 5: Common-gate stage and cascode stage at low frequencies (Chapter 4.3).

- Lecture 6: The differential gain stage (Chapter 4.4).

- Lecture 7: Frequency response of the basic gain stages (Chapter 4.5).

- Lecture 8: Introduction to multistage amplifies (Chapter 5).

Lecture 9: Feedback theory, basic properties of systems with feedback (Chapter 6.1 - 6.4).

Lecture 10: Stability in feedback systems (Chapter 6.5 - 6.7).

Lecture 11: Two-stage opamp design example (Chapter 7).

Lecture 12: Biasing circuits (Chapter 8).

**Prerequisites:** This book is aimed at a fundamental level in analog CMOS circuit design. The prerequisites needed are only a general background in mathematics and physics and a background in the fundamentals of signal processing, circuit theory and electronics. There are numerous courses and text-books which will provide an adequate background. Without this being an exhaustive list, it can be mentioned that the textbooks used in the introductory courses at the Technical University of Denmark in signal processing, circuit theory and electronics are the following:

Lathi, BP. 2009, *Signal Processing & Linear Systems*, International Second Edition, Oxford University Press, New York, USA.

Hambley, AR. 2018, *Electrical Engineering, Principles and Applications*, Seventh Edition, Pearson Education Ltd., Harlow, UK.

As already mentioned, an important feature of the present book is the extensive use of SPICE for verification of the mathematically based theory and for providing designs with properties which are closer to the properties obtained through actual experimental circuits. A very useful book for learning about LTspice (the version of SPICE used in this book) is the following, part of which is also used in an introductory course in circuit theory and electronics:

Bruun, E. 2020, *CMOS Integrated Circuit Simulation with LTspice*, Third Edition, bookboon. Available from: http://bookboon.com/en/cmos-integrated-circuit-simulation-with-ltspice-ebook

If you are not already familiar with LTspice, it is highly recommended to complete Tutorials 1 and 2 from this book concurrently with reading Chapter 2 in the present book.

**Further reading:** Hopefully, some readers of the present book find the subject of CMOS analog integrated circuit design so interesting that they wish to study the subject further. There are many excellent textbooks about analog CMOS design covering both the topics from the present book in more depth and covering many other subjects such as noise, data converters and filters. Also, details of semiconductor physics and VLSI technology are not dealt with in the present book. For such subjects, the reader is referred to more advanced textbooks, some of which are referred to in the following chapters. Again, without this being an exhaustive list, the following books are used in advanced courses at the Technical University of Denmark:

Chan Carusone, T., Johns, D. & Martin, K. 2012, *Analog Integrated Circuit Design*, Second Edition, International Student Version, John Wiley & Sons, Inc., Hoboken, USA.

Plummer, JD., Deal, M. & Griffin, PD. 2000, *Silicon VLSI Technology: Fundamentals, Practice, and Modeling*, First Edition, Pearson Education Ltd., Harlow, UK.

**Acknowledgements:** The author would like to acknowledge Dr. Lars Stenberg, former director of IC research and development at GN Hearing, for a careful review of the book, providing many suggestions for improving the text. Also, a particular acknowledgement goes to my colleagues Ivan Jørgensen, Pere Llimós Muntal and Nicolai Jerram Dahl who reviewed the entire manuscript of the book.

### Erik Bruun

Department of Electrical Engineering, Technical University of Denmark

# **Chapter 1 – Introduction**

This chapter gives an introduction to the subject of design of analog integrated circuits (ICs) in CMOS technology. A short background explaining the reason for focusing on CMOS technology is given, and the design methodology presented in this book is motivated. After having studied the chapter, you should be able to

- describe a few basic properties of CMOS technology.

- describe Moore's law.

- know the orders of magnitude of device geometries in a modern CMOS circuit.

- describe the basic steps in the development of a CMOS integrated circuit.

- explain the impact of device scaling on digital circuits and on analog circuits.

- describe and explain a generic model for the design of an electronic system.

### 1.1 CMOS technology

CMOS technology is the dominant fabrication technology used for today's electronic systems including computers, radios, TV sets, smartphones and also electronics embedded into other systems such as cars and household appliances.

CMOS is short for complementary metal-oxide-semiconductor and it is a technology for fabricating integrated circuits using both p-channel field-effect transistors (PMOS transistors) and n-channel field-effect transistors (NMOS transistors), the two dominant device types in most integrated circuits. In Chapter 3, we investigate the properties of MOS transistors in detail. The majority of CMOS integrated circuits are fabricated using silicon as the basic material.

The combination of PMOS and NMOS transistors makes it very easy to design digital circuit functions, and the transistors for digital circuit functions scale down in size as the fabrication technology improves and the manufacturers are able to control progressively smaller dimensions. The downscaling of device sizes implies that still more functions can be put into a single integrated circuit while maintaining or improving speed/power ratio for digital circuitry. In the beginning of the IC era (mid 1960s), device dimensions were counted in tens of  $\mu m$ . Today, device dimensions are counted in nm, i.e., a reduction in linear device size by more than three orders of magnitude. Contributing to the development towards more devices in a single IC is also an increase in the die size of an integrated circuit which can be manufactured with a reasonable yield (percentage of functional dies from a fabrication lot). In the 1960s, die sizes were counted in mm<sup>2</sup>. Today's ICs reach die sizes of more than 100 mm<sup>2</sup>, allowing tens of billions of devices to be integrated in a single IC (Altera's 30 billion transistor FPGA 2015).

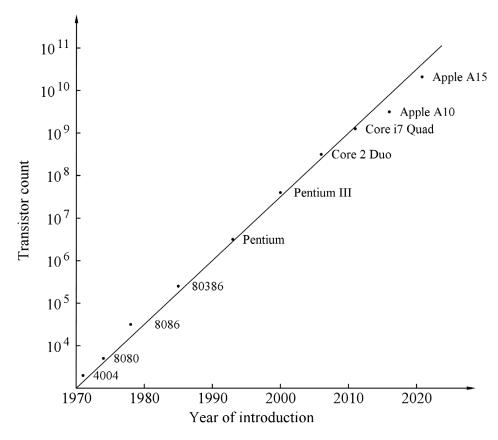

This scaling of semiconductor devices was predicted by Gordon Moore, one of the founders of Intel, already in 1965. In a famous paper published in *Electronics* (Moore 1965), he presented a graph showing that the number of components in an IC could be expected to increase by a factor of two per year, at least until 1975. This development has proved to be even more long-lived than originally foreseen by Gordon Moore, and in 1975, he revised the prediction and modified the rate of development to a factor of two in device count per die for every second year (Moore 1975), a prediction known as Moore's law.

Figure 1.1: Development in number of transistors per chip versus year of introduction. Adapted from Transistor count (2021).

This rate has been maintained for many years as shown in Fig. 1.1 for transistor count for selected microprocessors. The development is closely followed by IEEE IRDS, an organization which monitors the development in the semiconductor industry and regularly issues reports concerning this development (International Roadmap for Devices and Systems (IRDS<sup>TM</sup>) 2021).

### 1.2 Why analog circuit design?

The development towards smaller device dimensions is particularly beneficial for digital circuit functions which can be implemented using minimum-size devices. Closely linked to the downscaling of device dimensions is a downscaling of the supply voltage. This is advantageous for digital circuits as it leads to reduced power consumption, but it provides a challenge for analog circuit design because it means reduced signal swing without a corresponding reduction in noise voltages. Hence, analog circuit functions often need device geometries larger than the minimum size offered by the technology in order to achieve a useful performance with respect to noise properties, signal voltage swings, power consumption, etc. A consequence of this is that the growth rate of the complexity of digital systems is higher than that of analog systems, so today's electronic systems are mostly digital.

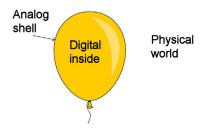

However, digital systems often need an analog interface to the physical world, for instance in the form of a transducer interface to a microphone, a loudspeaker, an ultrasound transponder, a light-sensitive device, a pressure sensor, or some other type of sensing device. Therefore, even though the growth of complexity in a digital system is higher than that in an analog system and an increasing number of system functions are handled by digital circuits, analog circuits remain an essential part of many electronic systems.

Figure 1.2: The analog balloon.

The situation may be illustrated as a balloon where the inside represents the digital functions, increasing in size as air is blown into the balloon, and the shell of the balloon, representing the analog interface, gets thinner and thinner as the balloon expands but remains to be an essential part in which a flaw would cause the balloon to collapse. If too much air is blown into the balloon, the analog shell may no longer be able to withstand the pressure and the balloon will explode. To avoid this situation, new developments in analog circuit design are needed for a stronger analog shell, including new fabrication technologies, new device types and new circuit techniques. This field of research and development is sometimes denoted 'More-than-Moore' (Arden et al. 2010). Thus, there is good reason to study the design of CMOS analog integrated circuits. This book is an introduction to this subject.

### 1.3 Design methodology

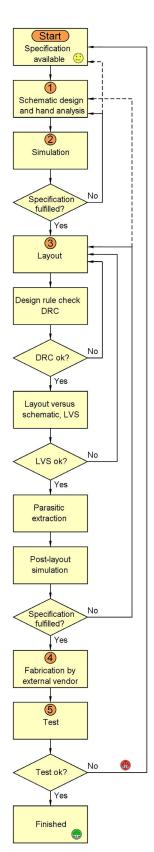

The design of an integrated circuit often follows a design flow as illustrated in Fig. 1.3. There are five major steps involved: (1) The schematic design using hand calculation and simplified analytical models, (2) the schematic simulation and design iteration using computer simulation, (3) the layout and layout verification using computer tools, (4) the fabrication of experimental test circuits, and (5) the experimental verification using measurements on the test circuits from the fabrication. After each of the steps in the design flow, it may be necessary to return to an earlier design step in order to correct deviations from the design goal. It may even be necessary to go back to start and revise the specifications if they turn out to be impossible to fulfill.

One of the characteristics of integrated circuit design is that the fabrication of test circuits is very time consuming and very expensive due to the fabrication of the IC wafers. This fabrication is carried out by specialized companies, and the normal turn-around time is counted in months while the cost is counted in thousands of dollars, even when achieving favorable university prices. For this reason, in IC design there is always a strong focus on achieving a first-time-right design, and this means that the verification steps in the design process (i.e., simulation, design rule check, layout versus schematic check, parasitic extraction, post-layout simulation) are very important, and a circuit design is not submitted for fabrication until these steps have been completed to perfection. Another reason for the extensive use of simulation is that debugging a circuit after fabrication is often much more difficult than debugging by simulation.

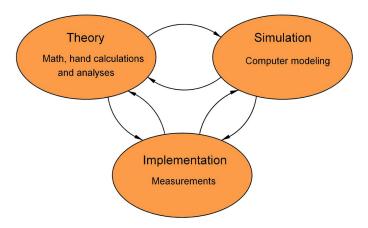

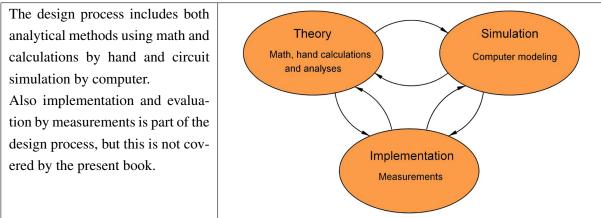

The phases illustrated in Fig. 1.3 can be treated in a generic development model as shown in Fig. 1.4 which is applicable to the development of electronic systems in general (Jørgensen 2015). In a commercial setting, it is absolutely vital to complete all three phases of development prior to the introduction of new products. In a university environment, all of the phases in the design flow cannot be covered in a single, one-semester university course.

This book is aimed at an introductory course, and for this, the focus is on the two initial steps in the design flow, the circuit design using hand calculations on the basis of a theoretical foundation and the circuit design aided by the use of computer simulation.

Figure 1.3: Development flow for IC design.

Figure 1.4: A generic model for the development of an electronic system.

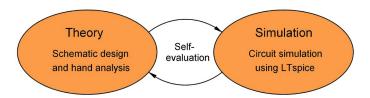

The two phases and the interaction between them are visualized in Fig. 1.5. The simulation serves not only as a design tool but also as a tool for the designer's self-evaluation of the design. As an introduction to the subject, the book covers only some basic circuit functions and circuit blocks which appear in almost any analog design, the fundamental gain stages, a basic design of an operational amplifier, and some additional circuits for providing bias currents and voltages to the analog circuit blocks.

Along the way, we review some of the fundamental issues which are required for the analytical design, including a brief repetition of basic principles for signals, electronic devices, circuit theorems and circuit analysis (Chapter 2). Also, an introduction to feedback theory is included (Chapter 6), and throughout the book, the analytical methods are complemented by simulations using the simulation program SPICE (Simulation Program with Integrated Circuit Emphasis) which is the de facto standard for simulating analog integrated circuits.

The SPICE simulator used throughout this book is LTspice. You may use alternative circuit simulators but LTspice has been chosen here because it is easily available from Analog Devices in a free version, (http://www.analog.com/en/design-center/design-tools-and-calculators/ltspice-simulator.html), and also it is fairly easy to learn how to use it for CMOS design. Contrary to most commercial IC design tools, it runs on both Windows PCs and Macs, and it does not require any sort of licenses. LTspice is optimized for simulating systems using integrated circuits from Analog Devices, but it is a general SPICE simulator, and it is also perfectly suited as a design tool for simulating CMOS integrated circuits. A free guide to the use of LTspice specifically for CMOS integrated circuits is available on the web (Bruun 2020).

Figure 1.5: The design phases illustrated in this book.

### References

Altera's 30 billion transistor FPGA 2015. *Gazettabyte*, 28 June 2015.

Retrieved from http://www.gazettabyte.com/home/2015/6/28/alteras-30-billion-transistor-fpga.html

Arden, W., Brillouët, M., Cogez P., Graef, M., Huizing, B. & Mahnkopf, R. (Editors) 2010, "More-than-Moore" White Paper, ITRS.

Available from: http://www.itrs2.net/uploads/4/9/7/7/49775221/irc-itrs-mtm-v2\_3.pdf

Bruun, E. 2020, CMOS Integrated Circuit Simulation with LTspice, Third Edition, bookboon.

Available from: http://bookboon.com/en/cmos-integrated-circuit-simulation-with-ltspice-ebook

International Roadmap for Devices and Systems (IRDS<sup>TM</sup>) 2021 Edition, *IEEE IRDS*. Retrieved from https://irds.ieee.org/editions/2021

Jørgensen, IHH. 2015, 'Three Step Development Model used for Active Learning in Electrical Engineering', *Proceedings of the 43rd Annual SEFI Conference*, Orléans, France.

Moore, GE. 1965, 'Cramming more components onto integrated circuits', *Electronics*, vol. 38, no. 4, pp. 114-117, 19 April 1965.

Moore, GE. 1975, 'Progress in Digital Integrated Electronics', *Technical Digest. International Electron Devices Meeting 1975*, IEEE pp. 11-13.

Transistor count 2021, Wikipedia. Retrieved from https://en.wikipedia.org/wiki/Transistor\_count

### Multiple-choice test

- 1. Complete the following statements by selecting the appropriate continuation from the table below.

- A: CMOS is an abbreviation for ...

- B: Modern CMOS processes normally use minimum device dimensions in range ...

- C: The most commonly used material for CMOS technology is ...

- D: Gordon Moore presented his first prediction of semiconductor device scaling in ...

- E: According to Moore's law, the number of devices per die increases ...

- F: Device downscaling is mostly beneficial for ...

- G: In analog integrated circuit design, the schematic design and analysis is verified through ...

- H: SPICE is an abbreviation for ...

Vil du være med til at sætte strøm til jernbanen?

Vi elektrificerer i disse år i alt 1362 km jernbane.

Eltog udleder langt mindre CO2, giver kortere rejsetider og mere stabil togdrift. Til glæde for et grønnere Danmark.

Lær os at kende på www.bane.dk eller følg os.

### Continuation:

| C-1.0.1.4.4.4.0.1. |                                                      |  |

|--------------------|------------------------------------------------------|--|

| 1:                 | circuit simulation.                                  |  |

| 2:                 | 1 - 100 mm.                                          |  |

| 3:                 | breadboarding.                                       |  |

| 4:                 | silicon.                                             |  |

| 5:                 | germanium.                                           |  |

| 6:                 | 1947.                                                |  |

| 7:                 | linearly with time.                                  |  |

| 8:                 | 1 - 100 μm.                                          |  |

| 9:                 | analog circuit.                                      |  |

| 10:                | digital circuits.                                    |  |

| 11:                | complementary metal-oxide-semiconductor.             |  |

| 12:                | carbon.                                              |  |

| 13:                | 1965.                                                |  |

| 14:                | Simulation Program with Integrated Circuit Emphasis. |  |

| 15:                | current-mode systems.                                |  |

| 16:                | exponentially with time.                             |  |

| 17:                | 1 - 1000 nm.                                         |  |

| 18:                | logarithmically with time.                           |  |

| 19:                | power electronics.                                   |  |

2. According to Moore's law from 1975, what is the expected factor of increase in device count per die per 10 years?

A: 10

B: 32

C: 1024

3. Assuming a constant die area and a device count increase by a factor of two in two years, what is the scaling factor per year of the linear device dimensions?

A: 0.84

B: 0.71

C: 0.50

4. Assuming a linear scaling factor of 0.84 per year, what would be a typical device dimension in 2024 if 28 nm is a typical device dimension in 2019?

A: 7 nm

B: 12 nm

C: 20 nm

# **Chapter 2 – Basic Concepts**

This chapter provides some of the information which you are expected to have as a background knowledge from previous studies. Here, the emphasis is on issues related to CMOS integrated circuit design. After having studied the chapter, you should be able to

- explain and describe analog signals in the time domain and in the frequency domain.

- explain and use device relations for passive components (resistors, capacitors and inductors).

- explain and use device relations for ideal voltage sources and current sources, both independent sources and controlled sources.

- explain and use basic circuit theorems (Kirchhoff's laws, Thévenin equivalents and Norton equivalents, superposition).

- calculate and simulate the step response in the time domain for simple RC networks.

- calculate and simulate transfer functions in the frequency domain for simple RC networks.

- explain the concepts of small-signal analysis and large-signal analysis and derive small-signal parameters from large-signal characteristics.

### 2.1 Signals

MOS integrated circuits are designed to process voltages and currents in an electronic system. Examples include the processing of information in a computer system, acoustic signals in an audio system, and power in a system for controlling LED lamps. Thus, one of the fundamental issues is the mathematical representation of voltages and currents or – more generally – signals. We start by considering a classification of signals.

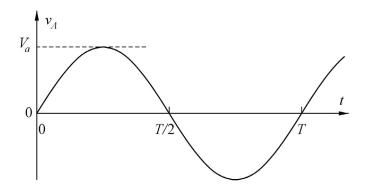

**Analog signals.** Analog signals are signals with a value varying continuously in time. An example is a voltage which is a function of the time t. Figure 2.1 shows a sinusoidal voltage signal. It is described by its amplitude  $V_a$  and its angular frequency  $\omega$  using the relation

$$v_a(t) = V_a \sin(\omega t) \tag{2.1}$$

It is a periodic signal with the period  $T=2\pi/\omega=1/f$  where f is the frequency. In general, a sinusoidal signal is described by  $v_a(t)=V_a\cos(\omega t+\theta)$  where  $\theta$  is the phase angle. Using  $\sin(x)=\cos(x-90^\circ)$ , we note that  $\theta=-90^\circ$  for the signal given by Eq. (2.1). The mean value of the signal over an integer number of periods is 0. A signal as the one shown in Fig. 2.1 is called an ac signal. The term 'ac' is short for 'alternating current', and in the short form, it is used for both currents and voltages.

Figure 2.1: A sinusoidal voltage signal.

Often a sinusoidal signal is described by its effective value or rms value (root-mean-square) rather than its amplitude. This is a concept derived from the power which can be delivered by a sinusoidal signal. A sinusoidal voltage with the rms value  $V_{R,rms}$  delivers the same average power to a load resistor with the value R as a constant voltage with the value  $V_{R,dc}$ . A constant voltage is also called a dc voltage, where the term 'dc' is short for 'direct current', and just as for the term 'ac', in the short form, it is used for both currents and voltages.

For the dc voltage, the power delivered to the resistor *R* is

$$P_{\rm dc} = \frac{V_{R,\rm dc}^2}{R} \tag{2.2}$$

For the ac voltage with an amplitude  $V_a$ , the average power delivered to the resistor R is

$$P_{\text{avg}} = \frac{1}{R} \frac{1}{T} \int_0^T V_a^2 \sin^2(\omega t) dt$$

(2.3)

Using  $\int_0^T \sin^2(\omega t) dt = \int_0^T \cos^2(\omega t) dt$  and  $(\sin^2(\omega t) + \cos^2(\omega t)) = 1$ , we can rewrite Eq. (2.3):

$$P_{\text{avg}} = \frac{1}{R} \frac{1}{T} \int_0^T V_a^2 \sin^2(\omega t) dt = \frac{1}{R} \frac{1}{T} \int_0^T V_a^2 \cos^2(\omega t) dt$$

$$= \frac{1}{2R} \frac{1}{T} \int_0^T V_a^2 (\sin^2(\omega t) + \cos^2(\omega t)) dt = \frac{1}{2R} \frac{1}{T} \int_0^T V_a^2 dt = \frac{V_a^2}{2R}$$

(2.4)

From Eqs. (2.2) and (2.4), it follows that the same average power is obtained from the dc source and the ac source if

$$V_{R,\text{rms}}^2 = V_{R,\text{dc}}^2 = \frac{V_a^2}{2} \Rightarrow V_a = \sqrt{2} V_{R,\text{rms}}$$

(2.5)

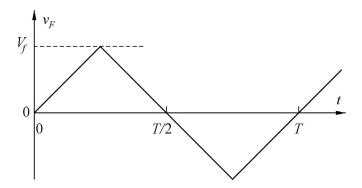

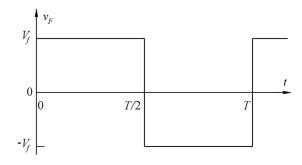

Figure 2.2 shows another analog signal, a triangular signal. Like the sinusoidal signal from Fig. 2.1, this is a periodic signal with a period T. It can be shown that any periodic signal can be decomposed into sine-wave signals with frequencies which are multiples of the basic frequency f = 1/T. The basic

Figure 2.2: A triangular voltage signal.

frequency is also called the fundamental frequency and the multiples of the fundamental frequency are the harmonic frequencies with 2f being the second harmonic, 3f the third harmonic, and so on. The decomposition of the time-varying signal into components with different frequencies is obtained using the Fourier transformation (Lathi 2009), and for the triangular signal shown in Fig. 2.2, the decomposition results in

$$v(t) = \frac{8V_f}{\pi^2} \sum_{n=0}^{\infty} (-1)^n \frac{\sin((2n+1)\omega t)}{(2n+1)^2}$$

$$= \frac{8V_f}{\pi^2} \left( \sin(\omega t) - \frac{1}{9} \sin(3\omega t) + \frac{1}{25} \sin(5\omega t) - \cdots \right)$$

(2.6)

We note that the triangular waveform contains only odd harmonics of the fundamental frequency and that the amplitude of the harmonics decreases with frequency.

Thus, using the Fourier transform, we can describe the signal in the frequency domain, rather than in the time domain.

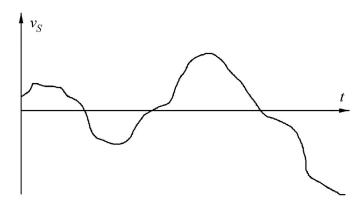

Figure 2.3: An arbitrary time-varying voltage signal.

Figure 2.3 shows an analog signal with an arbitrary, nonperiodic waveform. Also such a signal can be described in the frequency domain through the use of the Fourier transformation or the Laplace transformation (Lathi 2009). In this case, the resulting frequency spectrum is not discrete as for the periodic

signals but contains in principle all frequencies. For signals used in practice in electronic systems, the frequency spectrum is limited. Thus, for audio signals, the frequency range of interest is from about 20 Hz to 20 kHz, the audible frequency band. For radio transmission, several frequency bands are defined, ranging all the way from kHz-frequencies to GHz-frequencies.

The average value of the signals shown in the previous figures is 0. This is not always the case. Often, a signal can be treated as a sum of a constant dc value and an ac signal which is a sum of sinusoidal signals with an average value of 0. Transforming a time-varying signal into the frequency domain thus results in a dc value (a frequency component with f = 0) plus a spectrum of ac sinusoids.

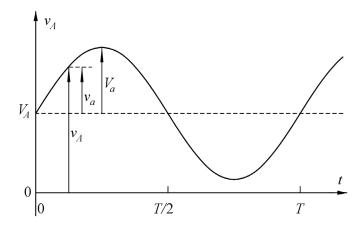

Figure 2.4: Signal notation.

When denoting a signal by a letter and a subscript, the standard convention used in many textbooks, including the present book, is as shown in Fig. 2.4 for a signal represented by a voltage. The total instantaneous value is denoted by a lowercase letter and an uppercase subscript. The dc value of the signal is denoted by an uppercase letter and an uppercase subscript. The ac value of the signal is denoted by a lowercase letter and a lowercase subscript. This means that

$$v_A(t) = V_A + v_a(t) \tag{2.7}$$

If the ac signal is a sinusoid, the amplitude of the sinusoid is denoted by an uppercase letter and a lowercase subscript, so

$$v_a(t) = V_a \sin(\omega t) \tag{2.8}$$

for the signal shown in Fig. 2.4.

Finally, when describing a signal in the frequency domain, we also use an uppercase letter and a lower-case subscript,  $V_a(j\omega)$  or  $V_a(s)$  where the complex frequency  $s = \sigma + j\omega$  is  $s = j\omega$  for physical frequencies (Lathi 2009), see examples in Section 2.4.

When using LTspice for simulating a circuit, an important issue is that LTspice is case-insensitive. This implies that you cannot use the conventions described above for distinguishing between dc values, ac

values, amplitudes, etc. You have to learn the signal concepts to a level where you can see from the context if a certain signal is a dc value, an ac signal, a sum of a dc value and an ac signal, or a signal in the frequency domain.

The distinction between (constant) dc values and time-varying signals superimposed on the dc values is extremely useful when analyzing electronic systems, especially if the variations in the ac signals are small enough that the electronic system can be described by linear equations with a reasonable accuracy. This leads to the concept of small-signal analysis which we will use extensively in this book.

A special category of time-varying signals is signals varying in a stochastic manner as a function of time. A stochastic signal is also called a noise signal and noise signals play an important role in all electronic systems. However, the treatment of noise signals is beyond the scope of this book.

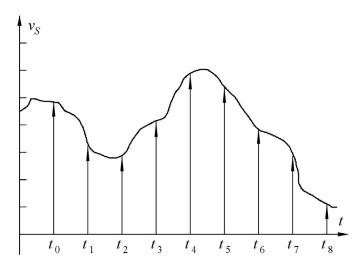

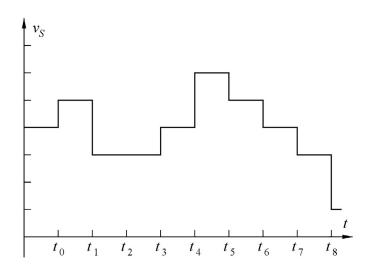

**Sampled analog signals.** Often in electronic systems, an analog signal is sampled at specific points in time as shown in Fig. 2.5. In this way, the signal is described by a series of signal values. Each of the samples may assume any value (within a limited range of signal values), and the series of values is called a sampled analog signal, discrete in time but continuous in value.

Figure 2.5: Sampling of an analog signal.

Also the values of each sample may be truncated into a finite number of values where each value is typically represented in a binary notation. The number of bits used for this notation determines the number of different signal values and the precision in the representation of the sampled signal values. If the signal shown in Fig. 2.5 is sampled in a system where each sample is discretized into one of 8 allowed values represented by 3 bits, the resulting sampled and digitized signal may be shown as the graph in Fig. 2.6.

Clearly, there is a difference between the original signal and the sampled signal with only 8 possible signal levels. The difference between the original signal and the quantized, sampled signal is an error

Figure 2.6: Sampled values truncated to 8 levels for the analog signal from Fig. 2.5.

signal called the quantization error or quantization noise since it can often be treated in the same way as a stochastic noise signal.

An extreme case of the quantized, sampled signal is a signal quantized into only two levels, represented by the logic values 0 and 1. Two different values of voltage (or current) correspond to the logic values 0 and 1. This is a binary digital signal and it is described by a stream of bits which can be processed in a computer or digital signal processing system.

The topic of the present book is analog circuits and systems for the processing of signals which are continuous in time and amplitude but the processing in digital systems is becoming ever more important, and often the purpose of analog electronic systems is to perform some sort of pre-processing of a signal before it can be sampled and quantized for further processing using digital signal processing.

### 2.2 Circuit elements

In CMOS integrated circuits, a number of passive and active circuit elements are available. They include the standard passive devices, i.e., resistors, capacitors and inductors, but the main feature of the CMOS technology is the availability of both p-channel and n-channel MOS transistors. In this section, we give a brief review of passive devices and ideal active devices (voltage sources and current sources) while the description of the real physical, active devices (MOS transistors) is the topic in Chapter 3.

**Resistors, capacitors and inductors.** An ideal resistor is characterized by the resistance value R and the relation Ohm's law, named after Georg Simon Ohm (1789-1854), a German physicist:

$$v = Ri \tag{2.9}$$

where v is the voltage across the resistor and i is the current flowing in the resistor. This relation applies both to a description in the time domain and in the frequency domain.

In most CMOS technologies, resistors can be designed to have values ranging from less than a  $k\Omega$  to several tens of  $k\Omega$  but they occupy a large area compared to the area of a typical MOS transistor. Therefore, for most designs, it is good practice to limit the number of resistors, or rather, the total value of resistance included in the design. Also, resistors in integrated circuits have parasitic components associated with them. Often resistors are implemented in a polysilicon resistive layer separated from the silicon surface by an insulating oxide layer, so a parasitic capacitance from the resistive layer to the silicon surface cannot be avoided.

An ideal capacitor is characterized by the capacitance value C. In the time domain, the following relations between capacitor charge Q(t), current and voltage apply:

$$Q(t) = Cv(t) (2.10)$$

$$i(t) = C \frac{dv(t)}{dt}$$

(2.11)

In the frequency domain, the relation is

$$I(s) = sCV(s); \quad s = j\omega \tag{2.12}$$

In CMOS technology, capacitors can be designed to have values ranging from fF to tens of pF. Since capacitors are often implemented using the plate capacitance between two conducting layers (or a conducting layer and the silicon substrate) separated by an insulating oxide layer, the capacitor value is proportional to the area of the capacitor. Therefore, it is important to keep the total capacitor value in a circuit small in order to avoid excessive use of silicon area for capacitors. The plate capacitors implemented using conducting layers separated by an insulating oxide layer have a parasitic capacitance from the bottom plate to the silicon surface which cannot be avoided.

Capacitors may also be implemented using a pn-junction biased in the reverse direction, see Chapter 3.1. In this case, the capacitor shows a nonlinear behavior, and the linear relations given by Eqs. (2.11) and (2.12) apply only to small signal variations from a bias point.

An ideal inductor is characterized by the inductance value L. In the time domain, the following relation between voltage and current applies:

$$v(t) = L\frac{di(t)}{dt} \tag{2.13}$$

In the frequency domain, the relation is

$$V(s) = sLI(s); \quad s = j\omega \tag{2.14}$$

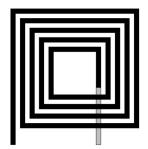

In CMOS technology, only rather poor inductors can be implemented. They are typically realized in one or more metal layers as spiral inductors with a planar layout, see Fig. 2.7. In practice, inductors can be designed to have values up to a few nH, and they are suffering from several parasitic elements, including capacitance to the substrate, series resistance, and loss due to induced currents in the substrate. Integrated

Figure 2.7: Layout examples of planar inductors in CMOS technology.

inductors are used mainly in circuits operating at GHz frequencies, and they will not be treated further in this book.

Except for the pn-junction capacitor, the devices described above are all linear devices (the relation between voltage and current is a linear equation), and in the frequency domain, they are all described by the relation

$$V(s) = Z(s)I(s) \tag{2.15}$$

where Z(s) with  $s = j\omega$  is the complex impedance of the device. For a resistor, Z(s) = R, for a capacitor, Z(s) = 1/(sC), and for an inductor, Z(s) = sL.

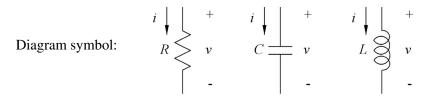

Figure 2.8 shows the standard textbook diagram symbols for the devices and the basic device equations. In LTspice, the device names are 'R', 'C' and 'L', respectively, and the symbols resemble those shown in Fig. 2.8.

Time domain:

$$v(t) = Ri(t) \qquad i(t) = C\frac{dv(t)}{dt} \qquad v(t) = L\frac{di(t)}{dt}$$

Frequency domain:

$$V(s) = RI(s)$$

$I(s) = sCV(s)$   $V(s) = sLI(s)$

Figure 2.8: Diagram symbols and basic device equations for resistors, capacitors and inductors.

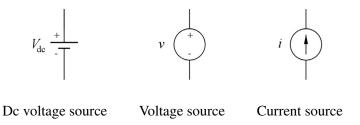

**Ideal active devices.** An active device is able to deliver energy or control the flow of energy in an electronic system. The ideal active devices include the independent voltage source, the independent current source, the controlled voltage source and the controlled current source.

The independent sources are not available in integrated circuit technology but they are used extensively as signal sources and power supply sources for CMOS integrated electronic systems. Physically, an example of an independent voltage source is a battery, and another example is a voltage regulator, generating a

constant voltage for supplying and electronic system with the dc power needed for its proper operation. The standard diagram symbols used in textbooks are shown in Fig. 2.9. In LTspice, the device names are 'V' and 'I', respectively, and the symbols resemble the circular symbols shown in Fig. 2.9. In LTspice, independent sources may be specified as dc sources, time-varying sources or sources in the frequency domain. To open a specification window for the source, you right-click on the symbol and left-click on 'Advanced' in the dialogue window (Bruun 2020, Tutorial 2.1).

Figure 2.9: Diagram symbols for independent sources. The leftmost symbol is only used for dc voltage sources (batteries).

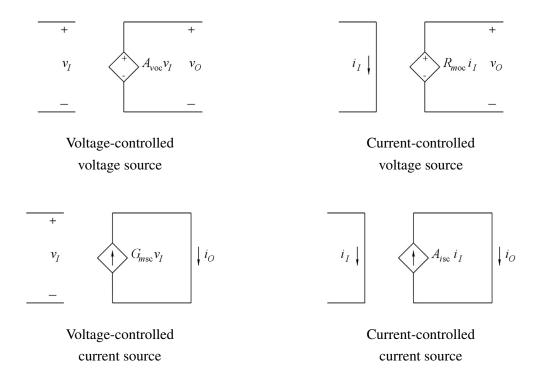

The controlled sources include four types: The voltage-controlled voltage source, the current-controlled voltage source, the voltage-controlled current source and the current-controlled current source. They are characterized by a voltage gain  $A_{voc}$ , a transresistance  $R_{moc}$ , a transconductance  $G_{msc}$  and a current gain  $A_{isc}$ , respectively (Hambley 2018). The subscript 'oc' denotes 'open circuit' and the subscript 'sc' denotes 'short circuit'. The symbols normally used in textbooks for controlled sources are shown in Fig. 2.10. Notice the diamond-shaped symbols. They serve to distinguish the controlled sources from the independent sources.

Figure 2.10: Diagram symbols for controlled sources.

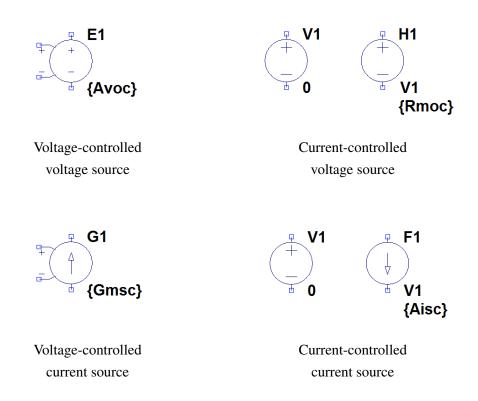

The controlled sources are also available in LTspice with the device names 'E', 'H', 'G' and 'F', respectively. The LTspice symbols are shown in Fig. 2.11. By default, the direction of the current in the current-controlled current source is downwards as shown in Fig. 2.11. In the figure, the values of gain in the different sources are shown as parameters, 'Avoc', 'Rmoc', 'Gmsc' and 'Aisc'. For the voltage-controlled sources ('E' and 'G'), the terminals for the controlling voltage are specifically shown in the symbols. For the current-controlled sources, the controlling current must be specified as the current through an independent voltage source with a value of 0 (Bruun 2020, Tutorial 1.3), and the name of this voltage source is specified in the 'Value'-line using a specification window opened by a right-click on the symbol. The gain ('{Rmoc}' or '{Aisc}') is specified in the 'Value2'-line.

Also notice that LTspice does not use a diamond-shaped symbol for controlled sources. You may actually modify the default LTspice symbol into a diamond-shaped symbol using the symbol editor in LTspice (Bruun 2020, Tutorial 1.2). LTspice also has available an 'arbitrary behavioral voltage source' (device type 'BV') and an 'arbitrary behavioral current source' (device type 'BI') where the relation between the controlled signal and the controlling signal is specified by an equation. It may be a linear equation as for the ideal amplifiers, or it may be a nonlinear equation describing a nonlinear relation between the controlled signal and the controlling signal.

Figure 2.11: LTspice symbols for controlled sources.

In CMOS technology, ideal controlled sources are not available, but as we shall see in Chapter 3, a MOS transistor provides an approximation to a voltage-controlled current source. However, it is nonlinear, and it has a fairly complicated relation between the current and the voltages applied to the transistor.

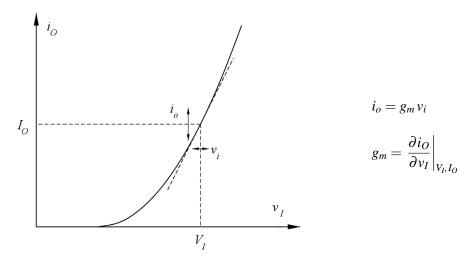

The fact that the relation between current and voltage is nonlinear for real devices in integrated circuits means that the equations for analyzing the behavior of a circuit become nonlinear, and in general, nonlinear equations are more difficult to solve than linear equations, especially when performing calculations by hand. In order to simplify circuit analysis, the nonlinear relation for a device can be linearized by calculating the partial derivative of the nonlinear relation and using this as a linear approximation for small signal variations from a bias point. Figure 2.12 illustrates this concept for a voltage-controlled current source where small signal variations around the bias point  $(V_I, I_O)$  can be analyzed using the tangent to the nonlinear relation as an approximation to the actual relation. This approach is called small-signal analysis, and it is extremely important in the analysis of analog circuits.

Figure 2.12: Small-signal modeling of a voltage-controlled current source.

### 2.3 Circuit theorems

The electrical behavior of a circuit is described mathematically by a few fundamental circuit theorems in combination with relations specifying the behavior of each of the circuit elements included in the circuit. In the previous section, we reviewed the relations describing some simple, ideal circuit elements. In the next chapter, we go into detail with the modeling of the MOS transistor which is the predominant device type in a CMOS integrated circuit. In this section, we briefly review some basic circuit theorems, and we describe some additional theorems which are useful for simplifying circuit structures when analyzing circuits by hand calculations.

**Kirchhoff's laws.** The two laws first described in 1845 by Gustav Kirchhoff (1824-87), a German physicist, are the fundamental, general equations in circuit analysis.

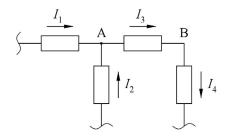

Kirchhoff's current law (KCL) states that the algebraic sum of currents flowing into a node equals zero. This is illustrated in Fig. 2.13, showing a small part (four devices) of a circuit. A node is a point where two ore more circuit elements are connected together. In Fig. 2.13, we can identify two nodes labeled A and B, respectively. Also, the currents in the circuit elements are labeled as shown in the figure with the arrow defining the positive direction of current. Applying KCL to the two nodes, we find the two node equations

Node A:

$$I_1 + I_2 - I_3 = 0$$

(2.16)

Node B:

$$I_3 - I_4 = 0$$

(2.17)

We note specifically that node B is a node where two circuit elements are connected in series, i.e., there are two and only two circuit elements connected to the node. Thus, KCL implies that the current in series-connected circuit elements is the same for all elements.

Figure 2.13: Circuit for illustrating Kirchhoff's current law, KCL.

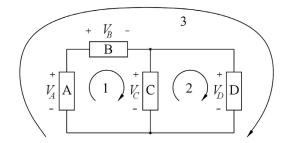

Kirchhoff's voltage law (KVL) states that the algebraic sum of voltages across circuit elements connected in a closed loop equals zero. This is illustrated in Fig. 2.14. In the circuit shown in the figure, we can identify three closed loops, loop 1, loop 2 and loop 3 with the positive directions defined by the arrows shown in the figure and the voltage across each element defined with signs as shown in the figure.

Figure 2.14: Circuit for illustrating Kirchhoff's voltage law, KVL.

Applying KVL to each of the loops, we find the loop equations

Loop 1:

$$-V_A + V_B + V_C = 0$$

(2.18)

Loop 2:

$$-V_C + V_D = 0$$

(2.19)

Loop 3:

$$-V_A + V_B + V_D = 0$$

(2.20)

We note specifically that loop 2 contains two circuit elements, C and D, connected in parallel, i.e., both ends are connected together. From Eq. (2.19), we see that  $V_D = V_C$ . KVL implies that the voltage across parallel-connected circuit elements is the same for all elements.

**Series connection of resistors, inductors and capacitors.** While Kirchhoff's laws are the fundamental theorems for analyzing circuits, there are several other rules derived from KCL and KVL which are very useful for reducing the complexity of a circuit by combining different circuit elements into simpler equivalents. This is particularly useful when performing circuit analysis by hand calculations. The first of such rules which we consider is the series connection of passive elements of identical type.

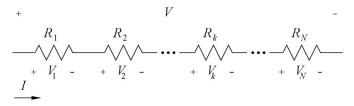

Figure 2.15: A series connection of N resistors.

Figure 2.15 shows a series connection of N resistors,  $R_1$ ,  $R_2$ , ...  $R_k$ , ...  $R_N$ . Applying KCL, KVL and Ohm's law to the series connection results in

$$I = I_1 = I_2 = \dots = I_k = \dots = I_N$$

(2.21)

and

$$V = V_1 + V_2 + \dots + V_k + \dots + V_N$$

=  $R_1 I_1 + R_2 I_2 + \dots + R_k I_k + \dots + R_N I_N$

=  $(R_1 + R_2 + \dots + R_k + \dots + R_N) I$  (2.22)

From Eq. (2.22), we see that the series connection of resistors  $R_1$  to  $R_N$  is equivalent to a single resistor with the value

$$R_{\rm eq} = R_1 + R_2 + \dots + R_N \tag{2.23}$$

We also find that the voltage across any resistor  $R_k$  in the series connection is given by

$$V_k = R_k I = \frac{R_k}{R_1 + R_2 + \dots + R_N} V \tag{2.24}$$

This is the voltage-divider rule for resistors.

For an inductor, we have V(s) = sLI(s), so using equations similar to Eqs. (2.21) and (2.22), we find that the equivalent inductance for a series connection of inductors is the sum of the inductances. Likewise, the voltage divider rule Eq. (2.24) applies to inductors as well as to resistors.

For a capacitor, we have

$$I(s) = sCV(s) \Rightarrow V(s) = \frac{1}{sC}I(s)$$

(2.25)

From Eq. (2.25), it follows – using equations similar to Eqs. (2.21) and (2.22) – that the equivalent capacitance  $C_{\rm eq}$  for a series connection of capacitors is given by

$$\frac{1}{C_{\text{eq}}} = \frac{1}{C_1} + \frac{1}{C_2} + \dots + \frac{1}{C_N}$$

(2.26)

Also, the voltage divider rule states that

$$V_k = \frac{1/C_k}{1/C_1 + 1/C_2 + \dots + 1/C_N} V$$

(2.27)

The expressions given by Eqs. (2.23) and (2.24) may be generalized for impedances in series:

$$Z_{\text{eq}} = Z_1 + Z_2 + ... + Z_N$$

(2.28)

$$V_k = \frac{Z_k}{Z_1 + Z_2 + \dots + Z_N} V (2.29)$$

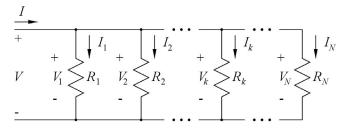

**Parallel connection of resistors, inductors and capacitors.** Applying KCL, KVL and Ohm's law to a parallel connection of resistors  $R_1$ ,  $R_2$ , ...  $R_k$ , ...  $R_N$  as shown in Fig. 2.16 results in

$$V = V_{1} = V_{2} = \dots = V_{k} = \dots = V_{N}$$

$$I = I_{1} + I_{2} + \dots + I_{k} + \dots + I_{N}$$

$$= \frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \dots + \frac{V_{k}}{R_{k}} + \dots + \frac{V_{N}}{R_{N}}$$

$$= V\left(\frac{1}{R_{1}} + \frac{1}{R_{2}} + \dots + \frac{1}{R_{k}} + \dots + \frac{1}{R_{N}}\right)$$

(2.30)

$$(2.31)$$

Figure 2.16: A parallel connection of N resistors.

From Eq. (2.31), we see that the parallel connection of resistors  $R_1$  to  $R_N$  is equivalent to a single resistor  $R_{eq}$  given by

$$\frac{1}{R_{\rm eq}} = \frac{1}{R_1} + \frac{1}{R_2} + \dots + \frac{1}{R_N}$$

(2.32)

For the parallel connection, we often use the notation

$$R_{\text{eq}} = R_1 \parallel R_2 \parallel \dots \parallel R_N \tag{2.33}$$

We also find that the current  $I_k$  in any resistor  $R_k$  in the parallel connection is given by

$$I_k = \frac{1/R_k}{1/R_1 + 1/R_2 + \dots + 1/R_N} I \tag{2.34}$$

This is the current-divider rule for resistors.

For a parallel connection of inductors, similar equations apply:

$$\frac{1}{L_{\text{eq}}} = \frac{1}{L_1} + \frac{1}{L_2} + \dots + \frac{1}{L_N}$$

(2.35)

and

$$I_k = \frac{1/L_k}{1/L_1 + 1/L_2 + \dots + 1/L_N} I \tag{2.36}$$

For a parallel connection of capacitors, equations similar to Eqs. (2.30) and (2.31) lead to

$$C_{\text{eq}} = C_1 + C_2 + \dots + C_N$$

(2.37)

and

$$I_k = \frac{C_k}{C_1 + C_2 + \dots + C_N} I \tag{2.38}$$

The expressions given by Eqs. (2.32), (2.33) and (2.34) may be generalized for impedances in parallel:

$$Z_{eq} = Z_1 || Z_2 || ... || Z_N$$

(2.39)

$$\frac{1}{Z_{\text{eq}}} = \frac{1}{Z_1} + \frac{1}{Z_2} + \dots + \frac{1}{Z_N}$$

(2.40)

$$I_k = \frac{1/Z_k}{1/Z_1 + 1/Z_2 + \dots + 1/Z_N} I \tag{2.41}$$

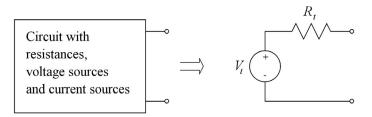

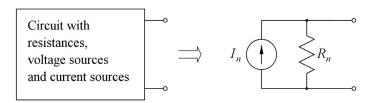

**Thévenin – Norton equivalent circuits.** In order to simplify circuits with both passive devices and active voltage sources and/or current sources, Thévenin and/or Norton equivalent circuits may be applied. The Thévenin theorem states that a linear two-terminal circuit consisting of resistances, voltage sources and current sources can be replaced by an equivalent circuit consisting of an independent voltage source in series with a resistor as shown in Fig. 2.17.

The Thévenin voltage  $V_t$  is found as the open-circuit voltage of the original network. The Thévenin resistance  $R_t$  is found from the Thévenin voltage  $V_t$  and the short-circuit current  $I_{\rm sc}$  flowing in a short circuit connected between the two terminals, i.e.,  $R_t = V_t/I_{\rm sc}$ . Alternatively, the Thévenin resistance can be found as the resistance between the two terminals with all independent voltage sources and current sources in the original circuit reset. Observe that resetting an independent voltage source means replacing it by a short circuit. Resetting an independent current source means replacing it by an open circuit, i.e., removing it completely.

Figure 2.17: Thévenin equivalent circuit.

In the original version of the theorem formulated in 1883 by Léon Thévenin, a French telegraph engineer (1857-1926), the theorem was stated for resistive circuits only. However, it also applies to linear circuits with capacitors and inductors, in which case  $R_t$  is replaced by a complex impedance  $Z_t$ .

An alternative to the Thévenin equivalent is the Norton equivalent described in 1926 by Edward Norton (1898-1983), an American electrical engineer. The Norton theorem states that a linear two-terminal circuit consisting of resistances, voltage sources and current sources can be replaced by an equivalent circuit consisting of an independent current source in parallel with a resistor as shown in Fig. 2.18.

Figure 2.18: Norton equivalent circuit.

The Norton current  $I_n$  is equal to the short-circuit current flowing in a short circuit connected between the two terminals. The Norton resistance is found from the Norton current and the open-circuit voltage  $V_{\rm oc}$  between the two terminals, i.e.,  $R_n = V_{\rm oc}/I_n$ . Alternatively, the Norton resistance can be found as the resistance between the two terminals with all independent voltage sources and current sources in the original circuit reset. By comparing the Thévenin equivalent and the Norton equivalent, we see that  $R_t = R_n = V_t/I_n$ .

Just as the Thévenin theorem, the Norton theorem is also applicable to linear circuits with capacitors and inductors.

**Superposition.** The superposition principle states that in a linear circuit with more independent sources, the total response is the sum of the responses to each of the independent sources acting alone with all other independent sources being reset.

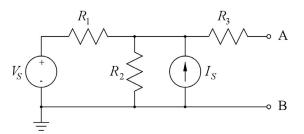

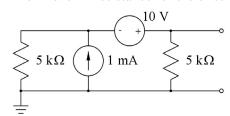

In order to illustrate both the superposition principle, the Thévenin equivalent and the Norton equivalent, we examine the circuit shown in Fig. 2.19.

Figure 2.19: Circuit example for illustrating superposition.

For finding the Thévenin voltage, we find the open-circuit voltage between the terminals A and B. The contribution from  $V_S$  with  $I_S$  reset, i.e.,  $I_S = 0$ , is

$$V_{\text{oc},1} = V_S \frac{R_2}{R_1 + R_2} \tag{2.42}$$

The contribution from  $I_S$  with  $V_S$  reset, i.e.,  $V_S = 0$ , is

$$V_{\text{oc}} = I_{S}(R_{1} \parallel R_{2}) \tag{2.43}$$

Thus, the total open-circuit voltage (and the Thévenin voltage) is

$$V_t = V_{\text{oc}} = V_{\text{oc},1} + V_{\text{oc},2} = V_S \frac{R_2}{R_1 + R_2} + I_S(R_1 \parallel R_2) = (V_S + I_S R_1) \frac{R_2}{R_1 + R_2}$$

(2.44)

The Thévenin resistance is found by resetting both  $V_S$  and  $I_S$  and finding the resistance between the terminals, i.e.,  $V_S$  is replaced by a short circuit and  $I_S$  is removed. By inspection, we find

$$R_t = R_3 + (R_1 \parallel R_2) \tag{2.45}$$

For finding the Norton equivalent, we place a short circuit between the terminals A and B and find the short-circuit current  $I_{sc}$ . The contribution from  $V_S$  with  $I_S$  reset, i.e.,  $I_S = 0$ , is

$$I_{\text{sc},1} = V_S \left( \frac{R_2 \parallel R_3}{R_1 + R_2 \parallel R_3} \right) \left( \frac{1}{R_3} \right) = V_S \frac{R_2}{R_1 R_2 + R_1 R_3 + R_2 R_3}$$

(2.46)

The contribution from  $I_S$  with  $V_S$  reset, i.e.,  $V_S = 0$ , is

$$I_{\text{sc},2} = I_S \frac{1/R_3}{1/R_3 + 1/(R_1 \parallel R_2)} = I_S \frac{R_1 R_2}{R_1 R_2 + R_1 R_3 + R_2 R_3}$$

(2.47)

Thus, the total short-circuit current (and the Norton current) is

$$I_n = I_{sc} = I_{sc,1} + I_{sc,2} = (V_S + I_S R_1) \frac{R_2}{R_1 R_2 + R_1 R_3 + R_2 R_3}$$

(2.48)

We may verify

$$R_n = R_t = \frac{V_t}{I_n} = \frac{R_1 R_2 + R_1 R_3 + R_2 R_3}{R_1 + R_2} = \frac{R_1 R_2}{R_1 + R_2} + R_3 = (R_1 \parallel R_2) + R_3$$

(2.49)

which is also the result given by Eq. (2.45).

### 2.4 Circuit analysis

In the design of analog CMOS integrated circuits, we apply both circuit analysis using hand calculations and circuit analysis using simulations. Hand calculations are often based on simplified circuit and device models while simulations by computer can be performed with complex device models. There are three types of analysis and simulation which are used throughout this book: dc steady-state analysis, time-domain analysis and frequency-domain analysis.

**Dc steady-state analysis.** The dc analysis serves the purpose of finding dc voltages and currents in a circuit with all time-varying signals reset. Once the values of dc voltages and currents have been found, linearized small-signal device models can be calculated using the approach illustrated in Fig. 2.12. The dc analysis is based on Kirchhoff's laws in combination with device models describing the behavior of devices in the circuit. For nonlinear devices, the nonlinear models must be used.

In LTspice, a dc analysis for fixed values of dc voltages and currents is performed using the simulation directive '.op'. It results in an output file with values for all node voltages and all device currents, and the error log file (opened with 'Ctrl-L') contains small-signal parameters, device voltages and device currents for the transistors and diodes in the circuit. The small-signal concept was illustrated in Fig. 2.12, and in Chapter 3, we investigate in detail the small-signal parameters for MOS transistors.

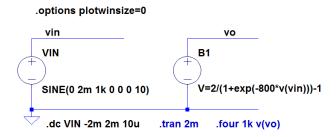

Often a dc steady-state analysis with one or more independent sources varied over a suitable range is performed. This analysis serves to find static (time-invariant) relations between voltages and currents in a circuit, for example the static relation between input voltage and output voltage for an amplifier. It is very useful for finding a suitable bias point for the operation of a circuit when time-varying signals are applied. In a dc analysis, there are no time-varying signals, implying that di(t)/dt and dv(t)/dt are both equal to zero for all voltages and currents. From Eqs. (2.11) and (2.13), it follows that all capacitor currents are zero and that all inductor voltages are zero, so in a dc steady-state analysis, capacitors are treated as open circuits and inductors are treated as short circuits.

In LTspice, a dc steady-state simulation with a variation of independent voltage sources or current sources is specified by the simulation directive '.dc' where one or more (up to three) signal sources can be specified with their range of variation and the increment between each value of the input signal. The simulation results in a plot window where the varying signal is by default the x-axis and node voltages and device currents can be selected for the y-axis (Bruun 2020, Tutorial 1.1).

**Time-domain analysis.** The time-domain analysis resembles the dc analysis with a sweep of the signal sources. However, in the time-domain analysis, signals are varied as a function of time, implying that both capacitors and inductors must be taken into account using the Eqs. (2.11) and (2.13). This complicates the analysis to a considerable extent, and hand calculations are normally performed only for simple circuits with linear circuit elements while circuit simulations can be performed for complex circuits including nonlinear circuit elements.

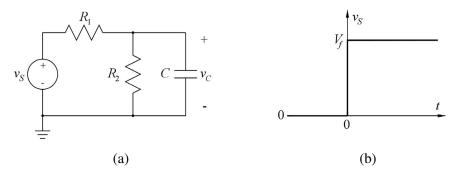

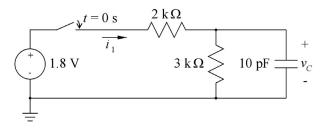

In order to illustrate a time domain analysis, consider the very simple RC network shown in Fig. 2.20.

**Figure 2.20:** RC network (a) and input voltage  $v_S(t)$  to the network (b).

For this, we may find the output voltage  $v_C(t)$  across the capacitor C when the input voltage changes as a step from 0 V to a value  $V_f$  at time t = 0 as also shown in Fig. 2.20. We first perform a hand calculation. For time t < 0, there are no changing signals, and we have the dc solution  $V_C = 0$  V. When the input voltage changes to  $v_S = V_f$ , Kirchhoff's current law at the output node gives in combination with the device equations for  $R_1$ ,  $R_2$  and C:

$$\frac{V_f - v_C(t)}{R_1} = \frac{v_C(t)}{R_2} + C\frac{dv_C(t)}{dt}$$

(2.50)

This is a differential equation for finding  $v_C(t)$  and the solution is:

$$v_C(t) = V_f \frac{R_2}{R_1 + R_2} (1 - \exp(-t/\tau))$$

(2.51)

where

$$\tau = \frac{1}{(R_1 \parallel R_2)C} \tag{2.52}$$

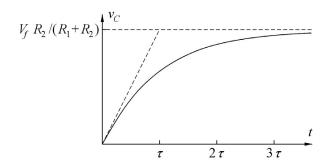

Figure 2.21: The capacitor voltage  $v_C(t)$  for the RC network from Fig. 2.20 with a step function applied to the input.

The voltage  $v_C(t)$  can be sketched as a function of time as shown in Fig. 2.21. We see that the capacitor voltage increases exponentially and approaches asymptotically a value of  $V_f R_2/(R_1 + R_2)$ .

In LTspice, a time-domain analysis is specified by the simulation directive '.tran' and the input signals must be specified as time-varying voltages and/or currents. For analyzing the circuit from Fig. 2.20, we may use the transient simulation in LTspice but this requires that we have numerical values for the

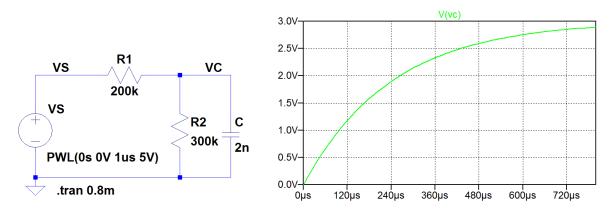

Figure 2.22: LTspice schematic and simulation results for the circuit in Fig. 2.20.

devices and voltages in the circuit. As an example, let us assume  $R_1 = 200 \text{ k}\Omega$ ,  $R_2 = 300 \text{ k}\Omega$ ,  $C_1 = 2 \text{ nF}$  and  $V_f = 5 \text{ V}$ . With these values, we can draw the schematic in LTspice as shown in Fig. 2.22, and we can specify the input signal as a piecewise-linear voltage.

Notice that we cannot have a rise time of 0 for the input specification. Instead, we select a rise time which is much smaller than the time constant  $\tau = 1/((R_1 \parallel R_2)C) = 240 \,\mu\text{s}$ . In order to show the capacitor voltage approaching  $V_f R_2(R_1 + R_2) = 3 \,\text{V}$ , we select a simulation time of 0.8 ms which is slightly more than  $3 \, \tau$ .

Figure 2.22 also shows the plot of the capacitor voltage  $v_C(t)$  resulting from the simulation. The resemblance with the analytically derived plot, Fig. 2.21, is apparent, so here we have an example of verification by simulation of the results achieved by hand analysis.

**Frequency-domain analysis.** In the frequency-domain analysis, a circuit is analyzed using the device equations valid in the frequency domain. For nonlinear devices, a linearization of the device equations is done first, so the frequency-domain analysis is always performed using linear device models, i.e., small-signal models. In general, the first step in a frequency-domain analysis by hand calculations is to establish a small-signal diagram for the circuit. For the circuit shown in Fig. 2.20, all devices are linear already, so the small-signal diagram is identical to the circuit shown in Fig. 2.20 with the input voltage defined as an ac voltage  $V_s(s)$  in the frequency domain. In later chapters, we examine several examples of circuits with nonlinear devices, mostly transistors, and we investigate in detail how the small-signal diagram for such circuits can be established, but for the circuit in Fig. 2.20, we can directly apply KCL at the output node  $V_c(s)$  using the device equations in the frequency domain with  $s = j\omega$ :

$$\frac{V_s(j\omega) - V_c(j\omega)}{R_1} = \frac{V_c(j\omega)}{R_2} + j\omega C V_c(j\omega)$$

(2.53)

This results in a transfer function  $H(j\omega) = V_c(j\omega)/V_s(j\omega)$  given by

$$H(j\omega) = \frac{V_c(j\omega)}{V_s(j\omega)} = \left(\frac{R_2}{R_1 + R_2}\right) \left(\frac{1}{1 + j(\omega/\omega_0)}\right)$$

(2.54)

where  $\omega_0 = 1/\tau = 1/((R_1 \parallel R_2)C)$ .

Often the result of a frequency domain analysis is shown graphically in a Bode plot where a logarithmic frequency axis is used and the transfer function is shown as a gain function in dB, i.e.,  $|H(j\omega)|_{\rm dB} = 20 \log(|H(j\omega)|)$  and a phase in degrees,  $\phi = \angle H(j\omega)$ . The Bode plot is named after the American engineer Hendrik Bode (1905-82). For the transfer function given by Eq. (2.54), we find:

$$|H(j\omega)| = \left(\frac{R_2}{R_1 + R_2}\right) \left(\frac{1}{\sqrt{1 + (\omega/\omega_0)^2}}\right)$$

(2.55)

$$\angle H(j\omega) = -\arctan(\omega/\omega_0) \tag{2.56}$$

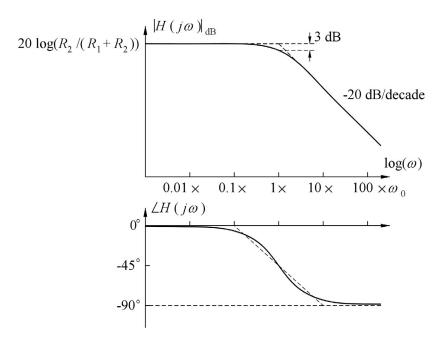

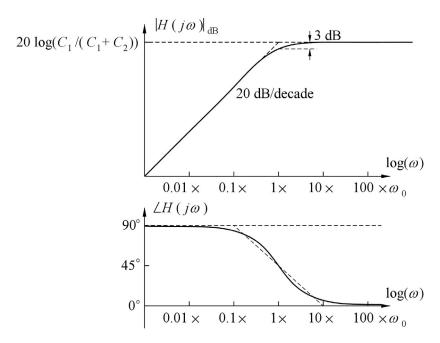

This results in the plots shown in Fig. 2.23.

Figure 2.23: Bode plot for the lowpass filter function given by Eq. (2.54).

Examining Eq. (2.55), we see that when  $\omega$  is very small,  $|H(j\omega)|$  approaches the constant value  $R_2/(R_1+R_2)$  whereas when  $\omega$  is very large, the transfer function is inversely proportional to the frequency. Thus, a piecewise-linear approximation to the gain plot is a horizontal line for small values of  $\omega$  and a line with a slope of -20 dB per decade of frequency for large values of  $\omega$ . The intersection between the two line segments is given by  $\omega = \omega_0$ , and for this frequency, the -3 dB bandwidth, the gain has dropped by a factor of  $\sqrt{2}$  from the low-frequency value, corresponding to -3 dB.

From Eq. (2.56), we find that the phase of  $H(j\omega)$  is 0° for very small frequencies,  $-90^{\circ}$  for very high frequencies and  $-45^{\circ}$  for  $\omega = \omega_0$ . For the phase characteristics, a piecewise-linear approximation may also be applied as shown in Fig. 2.23. For frequencies below  $\omega_0/10$  and above  $10\omega_0$ , horizontal lines are used, and for frequencies between  $\omega_0/10$  and  $10\omega_0$ , the phase is approximated by a straight line with a slope of  $-45^{\circ}$  per decade of frequency.

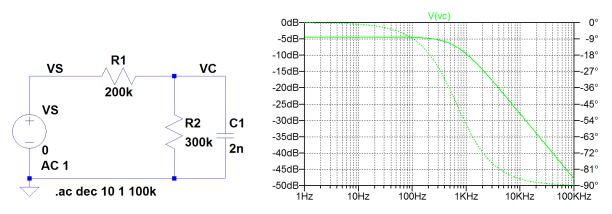

In LTspice, a frequency-domain analysis is specified by the simulation directive '.ac' and the input signal must be specified as an ac signal. For the '.ac' directive, the upper and lower limit of the frequency range is specified, and also the number of points per decade (or octave) must be specified. Using an amplitude of 1 directly gives the transfer function in the frequency domain. The simulation results in a Bode plot with the frequency  $f = \omega/(2\pi)$  as the x-axis, see the simulation for the circuit from Fig. 2.22 in Fig. 2.24. Again, we notice that the simulation results provide a verification of the analytical results achieved using math and hand calculations. We also note that the simulation provides a very easy way of achieving the exact gain and phase plots, rather than the asymptotic piecewise-linear approximations.

Figure 2.24: LTspice schematic and ac simulation results for the circuit in Fig. 2.20.

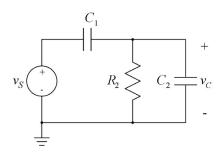

As the final example in this chapter, we show the frequency-domain analysis for the circuit shown in Fig. 2.25. It is derived from the circuit in Fig. 2.20 by replacing  $R_1$  with a coupling capacitor  $C_1$ . Also, the capacitor in parallel with  $R_2$  has been renamed to  $C_2$ .

Figure 2.25: RC highpass filter.

Using KCL, we find

$$(V_s(j\omega) - V_c(j\omega))j\omega C_1 = \frac{V_c(j\omega)}{R_2} + j\omega C_2 V_c(j\omega)$$

(2.57)

From this, we find the transfer function  $H(j\omega) = V_c(j\omega)/V_s(j\omega)$

$$H(j\omega) = \frac{V_c(j\omega)}{V_s(j\omega)} = \frac{j\omega C_1 R_2}{1 + j\omega R_2 (C_1 + C_2)}$$

(2.58)

For this transfer function, we find

$$|H(j\omega)| = \frac{\omega C_1 R_2}{\sqrt{1 + (\omega R_2 (C_1 + C_2))^2}}$$

(2.59)

$$\angle H(j\omega) = 90^{\circ} - \arctan(\omega R_2(C_1 + C_2))$$

(2.60)

We see that at low frequencies, the gain is proportional to the frequency, giving a positive slope of 20 dB/decade in the Bode plot, and for high frequencies, the gain approaches a constant value of  $C_1/(C_1+C_2)$ , corresponding to a capacitive voltage division between  $C_2$  and  $C_1$ . The intersection between the two asymptotic line segments in the Bode plot is given by the frequency  $\omega_0 = 1/(R_2(C_1+C_2))$ .

From Eq. (2.60), we find that the phase of  $H(j\omega)$  is 90° for very small frequencies, 0° for very high frequencies and 45° for  $\omega = \omega_0$ .

Figure 2.26 shows the Bode plot corresponding to this analysis.

Figure 2.26: Bode plot for the highpass filter function given by Eq. (2.58).

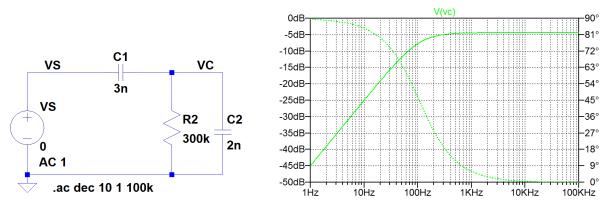

Figure 2.27: LTspice schematic and ac simulation results for the circuit in Fig. 2.25.

Again, for a numerical example, the circuit can be simulated using LTspice. The schematic for this and the resulting Bode plot is shown in Fig. 2.27 where we have used  $C_1 = 3$  nF.

The circuit examples shown here contain only linear circuit elements, so the frequency-domain analysis can be performed directly on the schematics shown. For circuits including nonlinear devices, LTspice automatically derives small-signal models for all devices and performs the ac simulation using a linearized small-signal diagram with a bias point as found from a '.op' simulation of the nonlinear circuit. It is always very important to check that the ac simulation is performed using reasonable values of bias voltages and currents. Often, an analysis of a circuit by simulation will start by using a dc analysis ('.dc') for finding a suitable bias point, then an operating point analysis ('.op') to verify the bias point, and then an ac analysis ('.ac') for investigation of the frequency response.

### References

Bruun, E. 2020, *CMOS Integrated Circuit Simulation with LTspice*, Third Edition, bookboon. Available from: http://bookboon.com/en/cmos-integrated-circuit-simulation-with-ltspice-ebook

Hambley, AR. 2018, *Electrical Engineering, Principles and Applications*, Seventh Edition, Pearson Education Ltd., Harlow, UK.

Lathi, BP. 2009, *Signal Processing & Linear Systems*, International Second Edition, Oxford University Press, New York, USA.

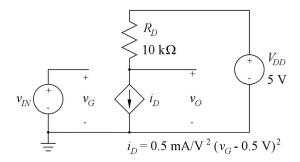

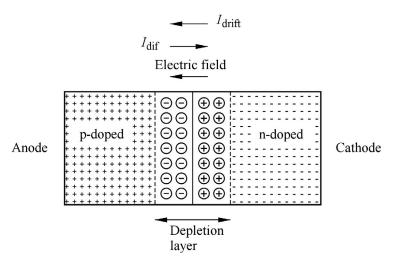

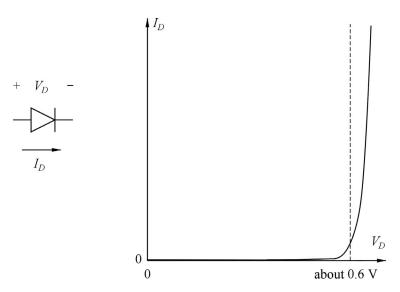

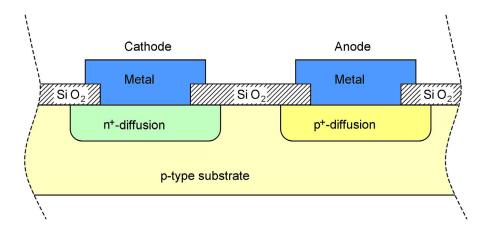

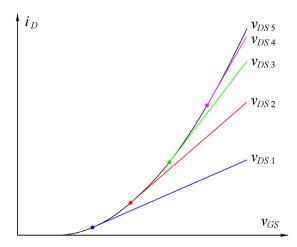

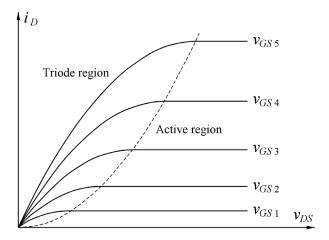

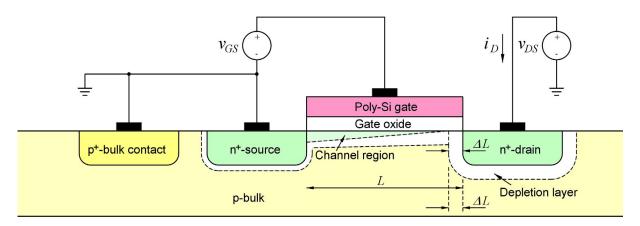

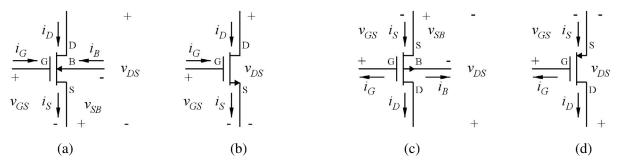

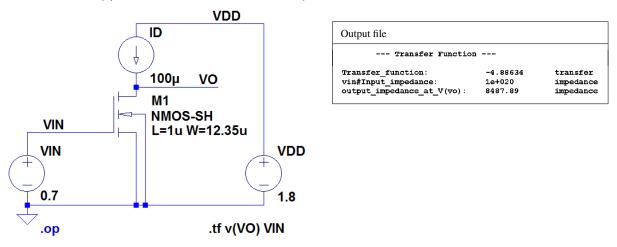

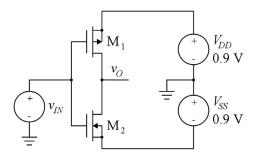

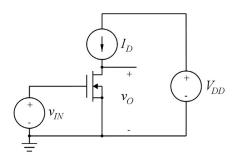

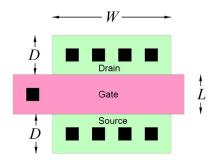

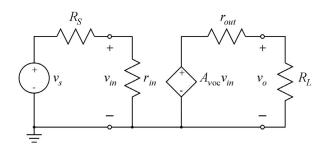

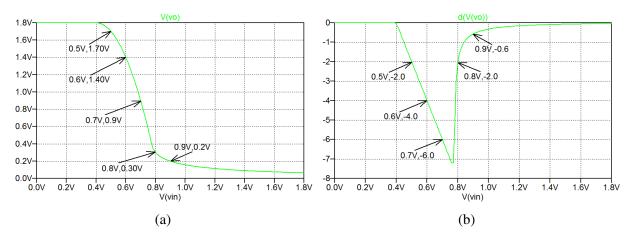

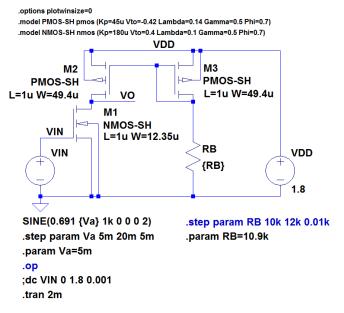

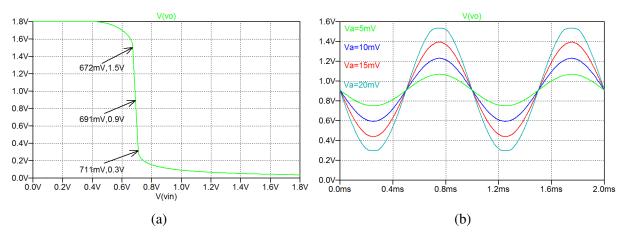

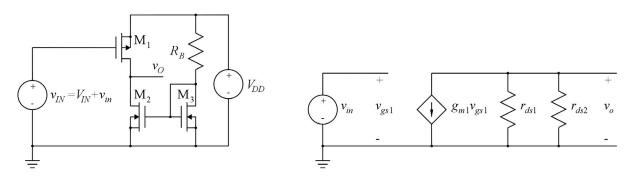

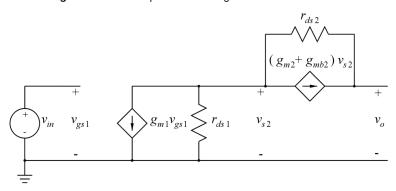

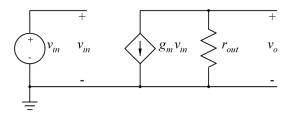

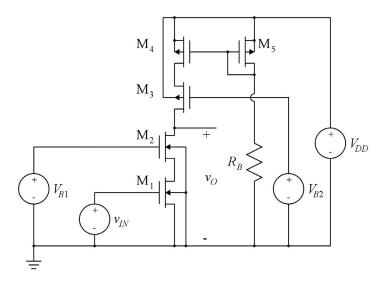

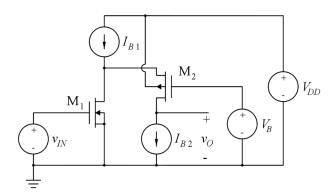

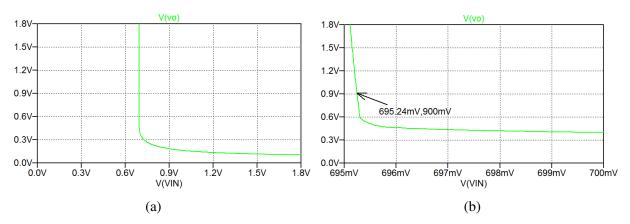

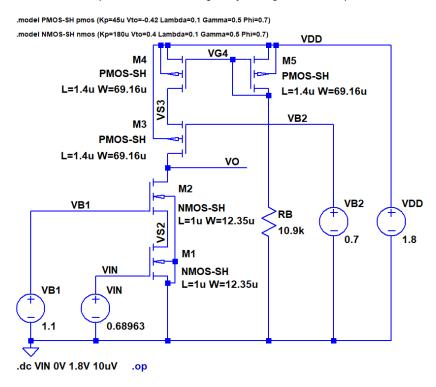

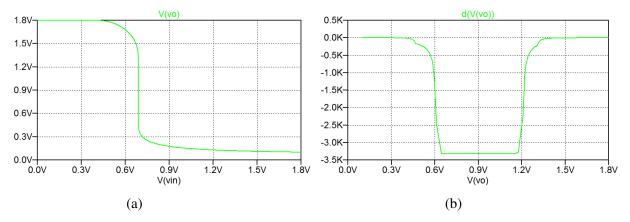

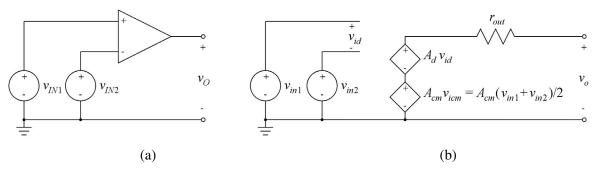

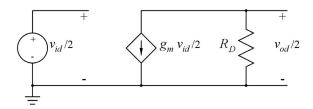

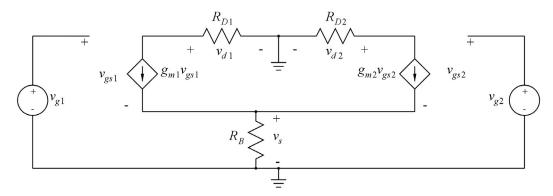

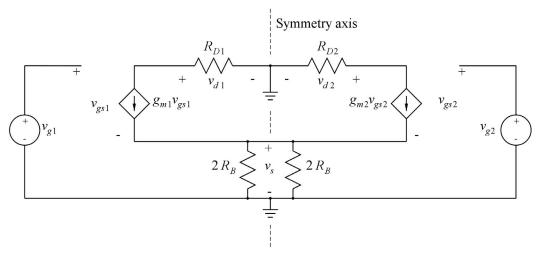

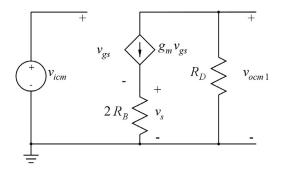

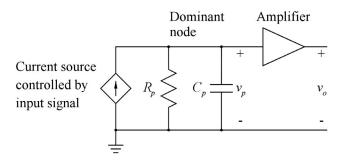

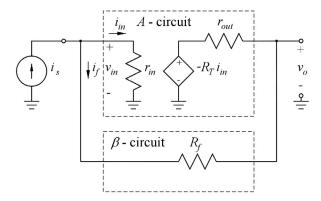

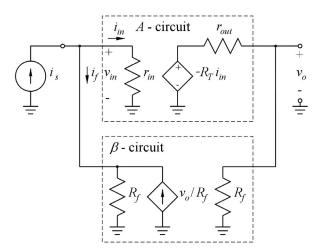

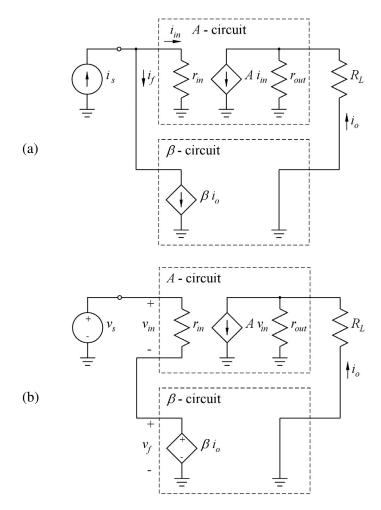

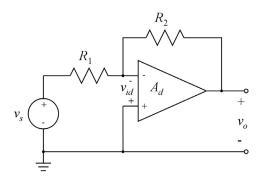

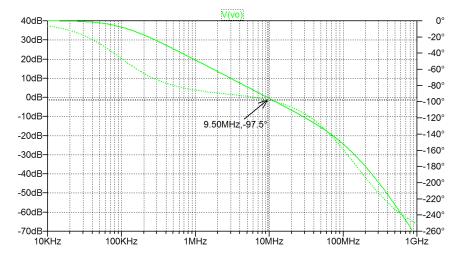

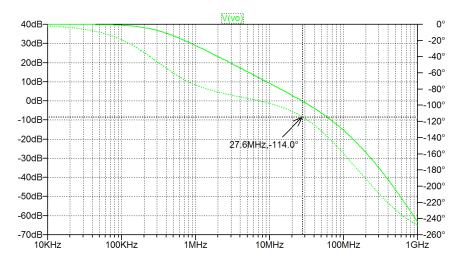

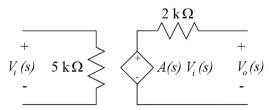

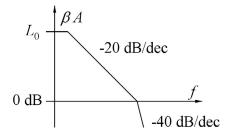

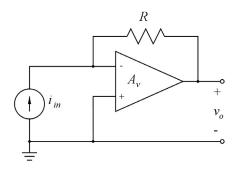

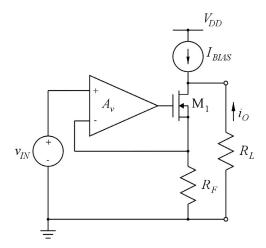

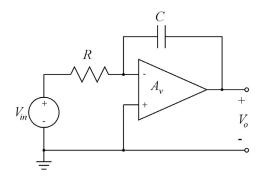

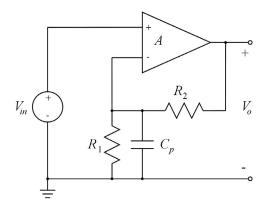

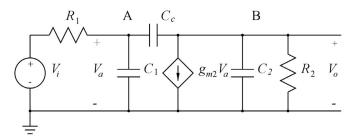

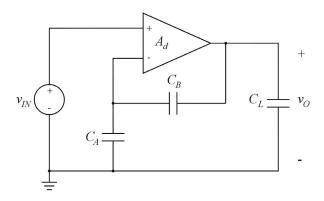

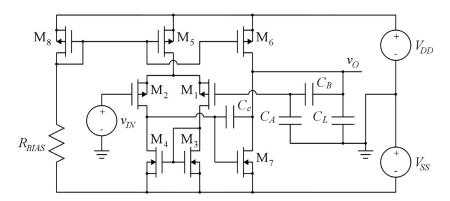

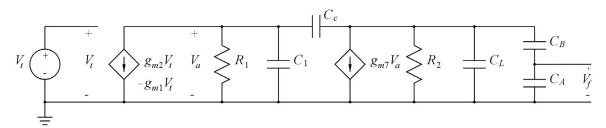

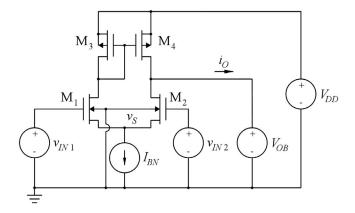

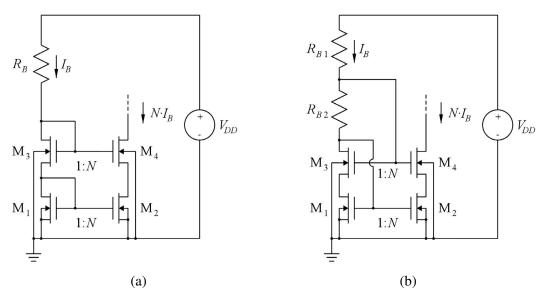

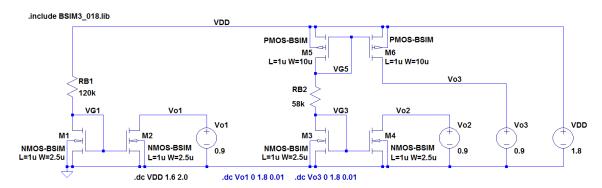

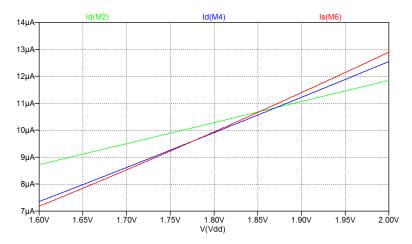

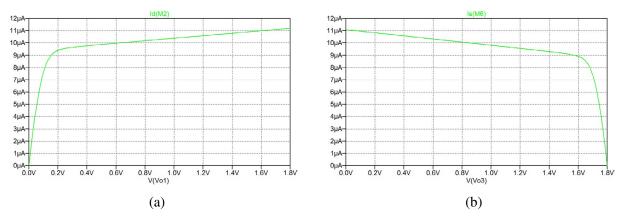

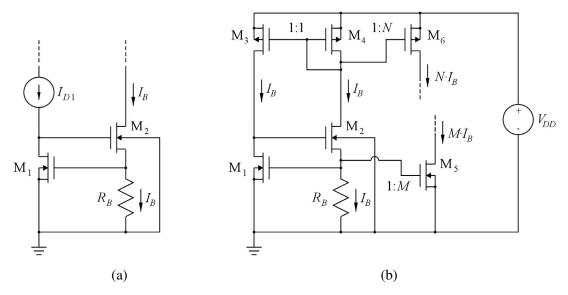

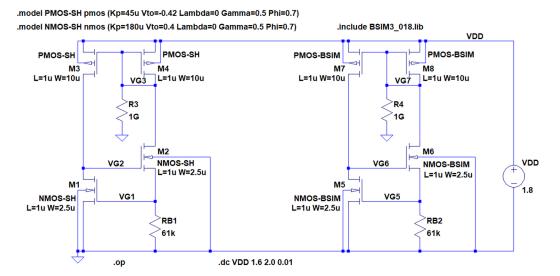

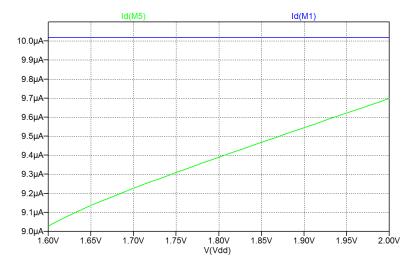

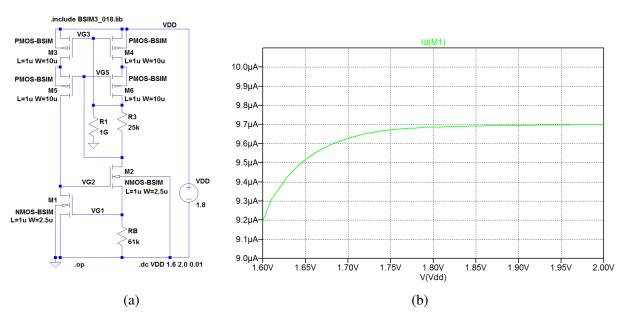

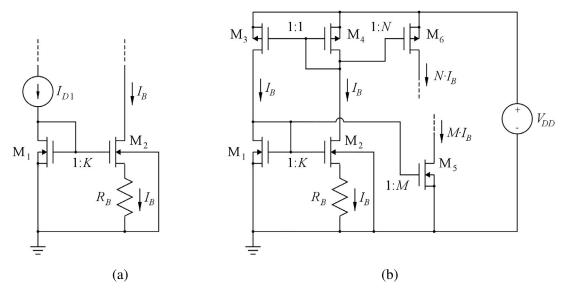

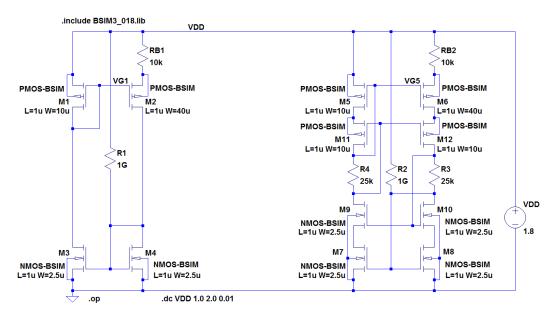

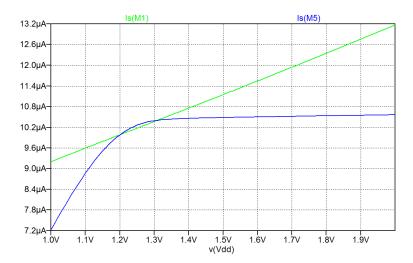

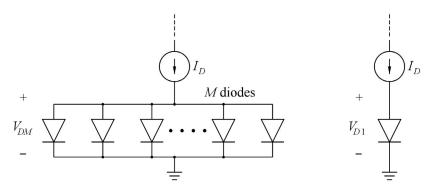

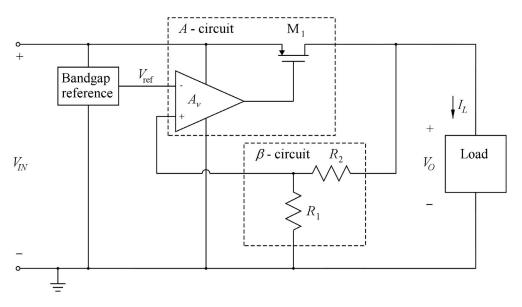

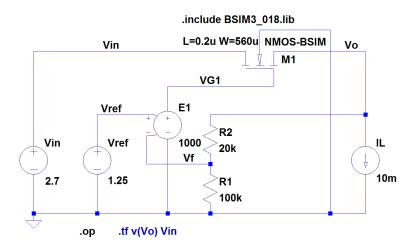

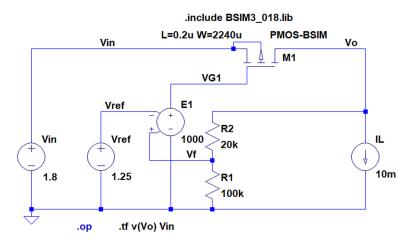

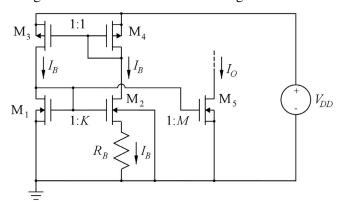

# Multiple-choice test