**DTU Library**

### High Efficiency Power Converter for Low Voltage High Power Applications

Nymand, Morten

Publication date: 2010

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Nymand, M. (2010). High Efficiency Power Converter for Low Voltage High Power Applications. Technical University of Denmark.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Morten Nymand

# High Efficiency Power Converter for Low Voltage High Power Applications

PhD thesis, January 2010

### **High Efficiency Power Converter for Low Voltage High Power Applications**

**Author:**

Morten Nymand

**Supervisor:**

Michael A. E. Andersen

#### **DTU Electrical Engineering**

Technical University of Denmark Ørsteds Plads Building 349 DK-2800 Kgs. Lyngby Denmark

www: http://www.elektro.dtu.dk/

Tel: (+45) 45 25 38 00 Fax: (+45) 45 93 16 34

Publishing date: January 2010

Classification: Public

Edition: 1<sup>st</sup> Edition

Note: This thesis is submitted in partial fulfillment of the requirements

for obtaining the PhD degree at the Technical University of

Denmark.

Copyright: Morten Nymand, 2010

### **Preface**

This thesis is submitted in partial fulfillment of the requirements for obtaining the PhD degree at the Technical University of Denmark, DTU Elektro, Electronics Group. The work was carried out during the period from September 2006 until January 2010 and was supervised by Professor Michael A. E. Andersen at the Technical University of Denmark. This work was supported by the Danish Energy Association (Dansk Energi - Net) under the national Public Service Obligation Program, project number 338-032 entitled "Modular Power Electronic Converters in the Power Range 1 to 10 kW,". The work is conducted as part of a joint research cooperation between the universities Aalborg University, Technical University of Denmark, and University of Southern Denmark and the industrial companies Grundfos A/S, Danfoss A/S, KK-electronic A/S, and IRD A/S.

# Acknowledgment

In doing this PhD, I have become deeply indebted and grateful to all of those who has stood by me and helped me throughout this project.

My special thanks, love and appreciation goes to:

- My dear family, Susanne, Marcus and Victoria for their love and never ending support, tolerance and endurance during this project.

- My supervisor, Michael A. E. Andersen for giving me this opportunity and his support, encouragement, and endless confidence in me.

- My dear friend Ole Seiersen for all his good advices and encouragement.

- All of my colleagues for their help, support, and for giving me this opportunity.

### **Abstract**

The topic of this thesis is the design of high efficiency power electronic dc-to-dc converters for high-power, low-input-voltage to high-output-voltage applications. These converters are increasingly required for emerging sustainable energy systems such as fuel cell, battery or photo voltaic based energy systems. Applications include systems for emergency power back-up (UPS), de-centralized combined heat and power systems, traction applications such as hybrid electrical vehicles, forklift trucks and special applications such as low emission power generation for truck and ship containers, and remote power generation for light towers, camper vans, boats, beacons, and buoys etc.

In chapter 2, a review of current state-of-the-art is presented. The best performing converters achieve moderately high peak efficiencies at high input voltage and medium power level. However, system dimensioning and cost are often determined by the performance at the system worst case operating point which is usually at minimum input voltage and maximum power. Except for the non-regulating V6 converters, all published solutions exhibit a very significant drop in conversion efficiency at minimum input voltage and maximum output power.

In chapter 3, a detailed analysis of dominant loss factors in high power converters for low voltage applications is presented. The analysis concludes that:

- Power transformers for low voltage high power, if properly designed, will have extremely low leakage inductance.

- If optimally designed, boost converters will be much more efficient than comparable buck type converters for high power low voltage applications.

- The use of voltage clamp circuits to protect primary switches in boost converters is no longer needed for device protection. On the other hand, they will dramatically increase power losses. Moreover, if a converter is properly designed, primary side voltage clamp circuits will not even work in low voltage high power converters.

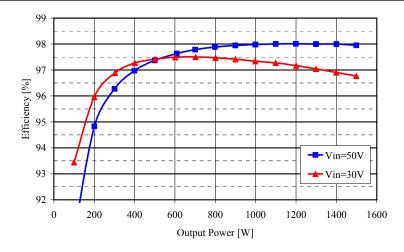

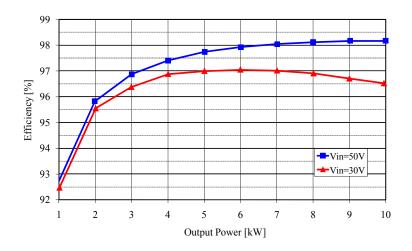

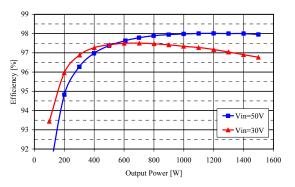

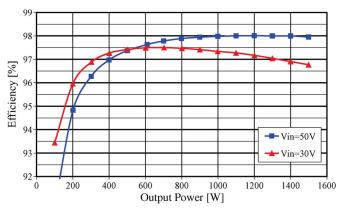

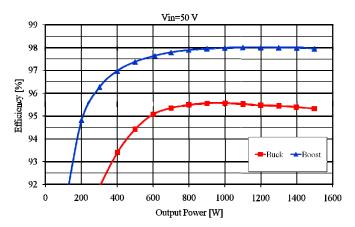

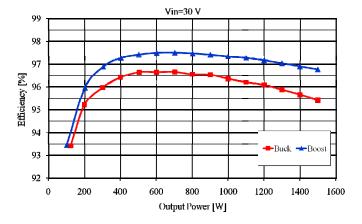

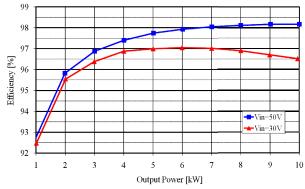

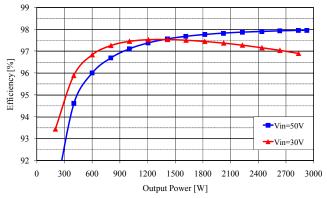

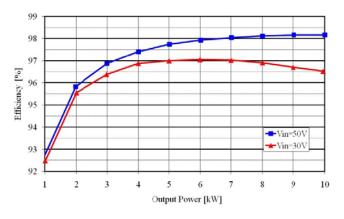

- Very high conversion efficiency can be achieved. Peak efficiency of 98% and worst case minimum efficiency of 96.8% are demonstrated on a 1.5 kW converter.

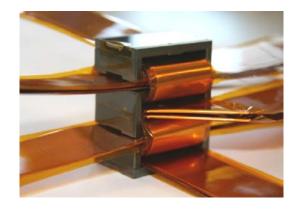

In chapter 4, the ability to - and challenges involved in - scaling of power converters for low voltage applications in the power range of 1-10 kW are analyzed. The analysis concludes that power MOSFETs needs to be paralleled extensively to scale power level to 10 kW. Maintaining fast current switching and reliable current sharing is essential. Further, the high ac-current carrying loop on the converter primary side will become increasingly difficult to scale due to fundamental issues such as physical size of components and penetration depth in copper.

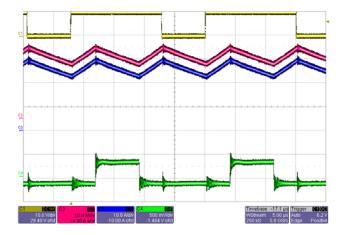

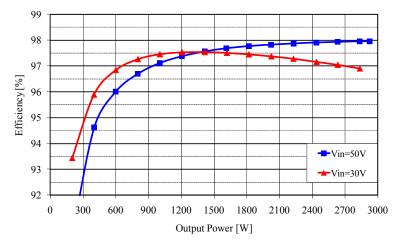

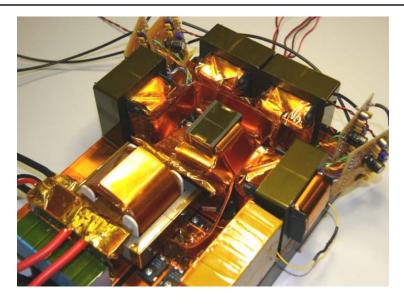

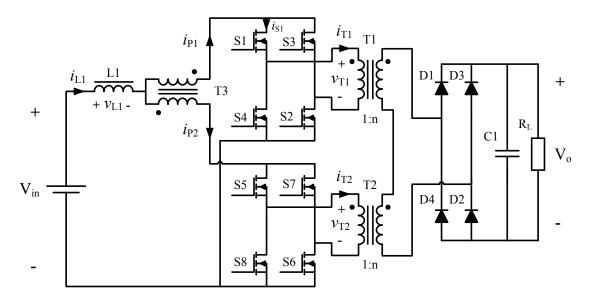

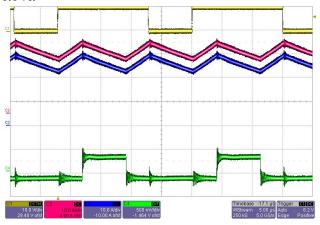

Finally in chapter 5, a new method for partial paralleling of multiple primary power stages in isolated boost converters is presented. Maximum benefit of scaling in terms of higher efficiency and lower cost is preserved by only paralleling primary switches and the critical high ac-current loop. Dynamic current sharing is inherently guaranteed between parallel power stages. The principle can be applied to all isolated boost type converters and, in principle, an unlimited number of power stages can be paralleled. Feasibility and operation of the new topology are demonstrated on a dual 3 kW and a quad 10 kW prototype converter. Measured peak efficiency is 98.2% and worst case minimum efficiency is between 96.5% and 96.9%.

### Resumé

Emnet for denne Ph.d. afhandling er design af effektelektroniske dc-dc konvertere med meget høj virkningsgrad til anvendelser med høj udgangseffekt, lav indgangsspænding samt høj udgangsspænding. Disse konvertere anvendes i stigende grad indenfor vedvarende energisystemer baseret på brændselsceller, batterier eller solceller. Anvendelserne omfatter nødstrømsanlæg (UPS), decentrale mikro-kraftvarmeanlæg, transportsystemer så som elektriske hybridbiler, gaffeltrucks samt særlige anvendelser indenfor generering af elektrisk energi til kølecontainere på lastvogne og skibe samt forsyning af fjerntliggende fyrtårne, campingvogne, både, afmærkningsbøjer m.m.

I kapitel 2, gennemgås state-of-the-art på området. De bedste af de præsenterede konvertere opnår rimelige høje virkningsgrader ved høje indgangsspændinger og lavere effekter. Men da de fleste systemers størrelse og pris afhænger af virkningsgraden i det kritiske arbejdspunkt, bliver virkningsgraden ved minimal indgangsspænding og maksimal udgangseffekt afgørende for det samlede system. Bortset fra en ureguleret V6 konverter udviser alle offentliggjorte konvertere dog kraftigt faldende virkningsgrader ved lav indgangsspænding og høj udgangseffekt.

I kapitel 3, foretages en detaljeret analyse af de væsentligste tabsfaktorer i konvertere til høje effekter og lave indgangsspændinger. Analysen konkluderer at:

- Korrekt dimensionerede effekttransformatorer til lav indgangsspænding og høj effekt vil have særdeles lav spredningsinduktans.

- Hvis boost konvertere designes optimalt, vil disse kunne opnå langt højere virkningsgrad end tilsvarende buck konvertere.

- Anvendelsen af voltage clamp kredsløb til beskyttelse imod overspændinger på switchkontakterne i boost konvertere vil øge tabene kraftigt. Voltage clamps er ikke længere nødvendige og virker i øvrigt ikke, hvis konverteren er korrekt designet.

- Det er muligt at opnå særdeles høj virkningsgrad. Virkningsgrader på op til 98% er demonstreret på en 1,5 kW konverter. Worst case virkningsgraden er 96,8%.

I kapitel 4, gennemgås mulighederne for at skalere udgangseffekten på konverteren i området fra 1-10 kW. Der skal parallelkobles et stort antal power MOSFETs for at opnå en udgangseffekt på 10 kW. Der er behov for pålidelig og robust parallelkobling, som ikke nedsætter switch tiderne. Endvidere viser analysen, at de høje vekselstrømme på primærsiden vil være svære at skalere p.g.a. komponenternes fysiske størrelse kombineret med indtrængningsdybden i kobber.

Endelig, præsenteres der i kapitel 5 en ny metode til delvis parallelkobling af flere effekttrin i isolerede boost konvertere. Ved at begrænse parallelkoblingen til de få kritiske områder med høj belastning opnås en kosteffektiv løsning med høj virkningsgrad. Løsningen sikrer automatisk strømdelingen mellem alle parallelkoblede effekttrin. Løsningen kan endvidere anvendes i alle typer boost konvertere og kan – i princippet – udvides til parallelkobling af et ubegrænset antal effekttrin. Det nye princip er demonstreret i 2 prototype konvertere; en dobbelt 3 kW konverter og en firdobbelt 10 kW konverter. Der er målt virkningsgrader op til 98,2%, og de laveste virkningsgrader ved lav indgangsspænding og højeste udgangseffekt ligger imellem 96,5% og 96,9%.

## TABLE OF CONTENT

| PREFAC  | E                                                         | 2  |

|---------|-----------------------------------------------------------|----|

| ACKNO   | WLEDGMENT                                                 | 2  |

| ABSTRA  | ст                                                        | 3  |

| RESUM   | É                                                         | 4  |

| NOMEN   | ICLATURE                                                  | 8  |

| 1       | INTRODUCTION                                              | 10 |

| 1.1     | SCOPE                                                     | 10 |

| 1.2     | BACKGROUND AND MOTIVATION                                 | 10 |

| 1.3     | PROJECT OBJECTIVES                                        | 11 |

| 1.4     | COMMON SPECIFICATION                                      | 12 |

| 1.5     | PROJECT PLAN AND CONTENT                                  | 12 |

| 1.6     | THESIS STRUCTURE AND CONTENT                              | 13 |

| 2       | STATE-OF-THE-ART                                          | 16 |

| 2.1     | ISOLATED BOOST TYPE CONVERTERS                            | 16 |

| 2.1.1   | ISOLATED PUSH-PULL BOOST CONVERTER                        | 17 |

| 2.1.2   | ISOLATED TWO-INDUCTOR BOOST CONVERTER                     | 17 |

| 2.1.3   | ISOLATED FULL-BRIDGE BOOST CONVERTER                      | 18 |

| 2.2     | ISOLATED BUCK TYPE CONVERTERS                             | 20 |

| 2.2.1   | ISOLATED FULL-BRIDGE BUCK CONVERTERS                      | 20 |

| 2.2.2   | ISOLATED THREE PHASE FULL-BRIDGE BUCK CONVERTERS          | 21 |

| 2.3     | SUMMARY OF STATE-OF-THE-ART ANALYSIS                      | 22 |

| 3       | DESIGN OF HIGH-POWER LOW-VOLTAGE CONVERTERS               | 24 |

| 3.1     | LOW IMPEDANCE LEVEL IN HIGH-POWER LOW-VOLTAGE CONVERTERS  | 25 |

| 3.2     | BASIC OPERATION OF ISOLATED FULL-BRIDGE CONVERTERS        | 25 |

| 3.2.1   | ISOLATED FULL-BRIDGE BOOST CONVERTER                      | 25 |

| 3.2.2   | ISOLATED FULL-BRIDGE BUCK CONVERTER                       | 28 |

| 3.3     | TRANSFORMER DESIGN FOR HIGH-POWER LOW-VOLTAGE CONVERTERS  | 30 |

| 3.3.1   | PROXIMITY EFFECT IN LOW-VOLTAGE HIGH-POWER TRANSFORMERS   | 31 |

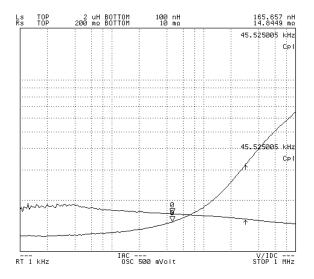

| 3.3.2   | LEAKAGE INDUCTANCE IN LOW-VOLTAGE HIGH-POWER TRANSFORMERS | 31 |

| 3.3.3   | ANALYSIS OF FOUR ALTERNATIVE WINDING DESIGNS              | 33 |

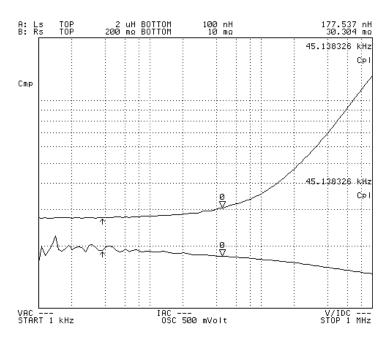

| 3.3.4   | EXPERIMENTAL VERIFICATION/RESULTS                         | 35 |

| 3.4     | POWER MOSFET LOSSES                                       | 36 |

| 3.4.1   | MOSFET CONDUCTION LOSSES                                  | 36 |

| 3.4.2   | POWER MOSFETS RATED FOR REPETITIVE AVALANCHE              | 39 |

| 3.4.3   | POWER MOSFET TURN-OFF LOSSES                              | 39 |

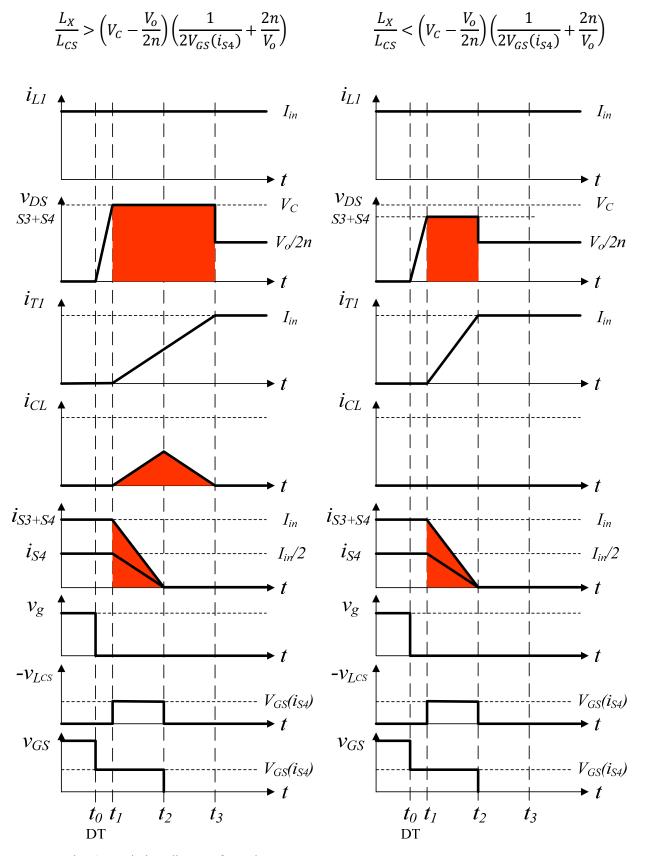

| 3.4.3.2 | VOLTAGE LIMITED CURRENT COMMUTATION – MODE 1              | 41 |

| 3.4.3.3 | POWER MOSFET LIMITED CURRENT COMMUTATION – MODE 2         | 44 |

| 3.4.3.4 | MODE 1 VERSUS MODE 2 CURRENT COMMUTATION                  | 46 |

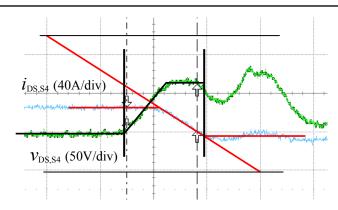

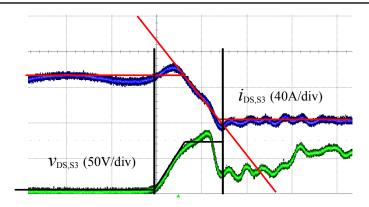

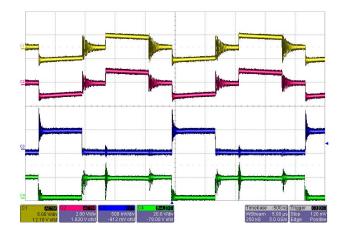

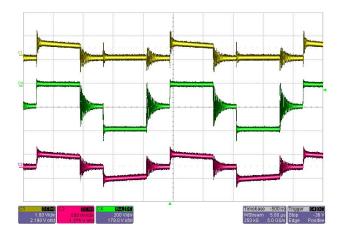

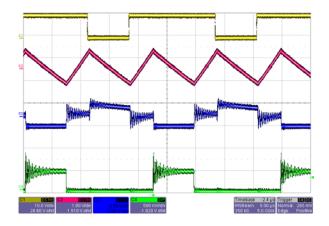

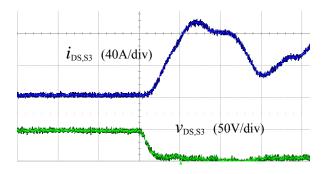

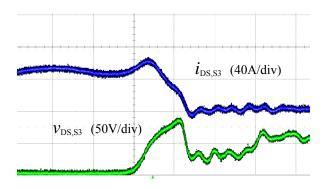

| 3.4.3.5 | EXPERIMENTAL RESULTS                                   | . 47 |

|---------|--------------------------------------------------------|------|

| 3.4.4   | SWITCH TURN-ON LOSSES                                  | . 50 |

| 3.5     | CIRCUIT DESIGN AND INTERCONNECTIONS                    | . 50 |

| 3.5.1   | VOLTAGE CLAMP CIRCUITS                                 | . 51 |

| 3.5.2   | LOW INDUCTANCE AND AC RESISTANCE INTERCONNECTION       | . 52 |

| 3.6     | HIGH VOLTAGE SILICON CARBIDE SCHOTTKY DIODES           | . 54 |

| 3.6.1   | RECTIFIER CONDUCTION LOSSES                            | . 54 |

| 3.6.2   | RECTIFIER SWITCHING LOSSES                             | . 55 |

| 3.6.3   | ANALYSIS OF RECTIFIER LOSSES IN 1.5 KW BOOST CONVERTER | . 56 |

| 3.7     | EXPERIMENTAL RESULTS FROM 1.5 KW BOOST CONVERTER       | . 57 |

| 3.8     | CONCLUSION ON DESIGN OF HIGH-CURRENT CONVERTERS        | . 58 |

| 4       | SCALABILITY OF CONVERTER                               | . 60 |

| 4.1     | PARALLELING OF CONVERTERS                              | . 60 |

| 4.1.1   | INTERLEAVING OF CONVERTERS                             | . 60 |

| 4.1.2   | SERIAL CONNECTION OF INPUTS- AND/OR OUTPUTS            | . 61 |

| 4.2     | MINIMUM PARALLELING APPROACH                           | . 61 |

| 4.3     | SCALABILITY LIMITATIONS IN ISOLATED BOOST CONVERTERS   | . 62 |

| 4.3.1   | INPUT FILTER SCALABILITY                               | . 62 |

| 4.3.2   | SCALING OF OUTPUT RECTIFIERS                           | . 63 |

| 4.3.3   | SCALING OF PRIMARY SWITCHES                            | . 64 |

| 4.3.4   | TRANSFORMER SCALABILITY                                | . 64 |

| 4.3.5   | SCALING OF INTERCONNECTION WIRING                      | . 65 |

| 4.4     | SUMMARY/CONCLUSION ON SCALABILITY                      | . 66 |

| 5       | NEW PARTIAL PARALLELING METHOD                         | . 67 |

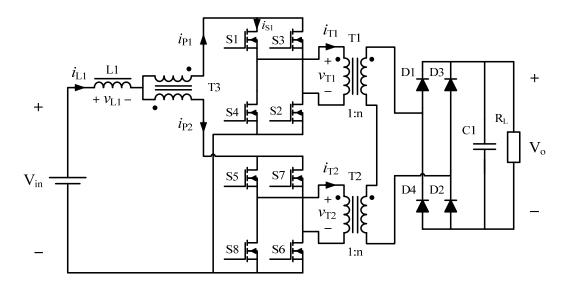

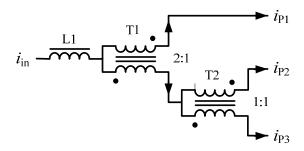

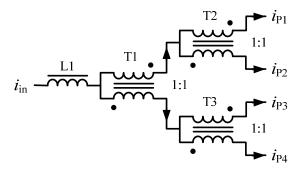

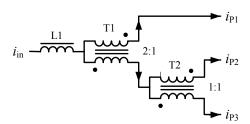

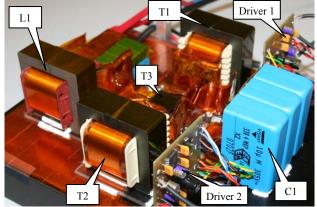

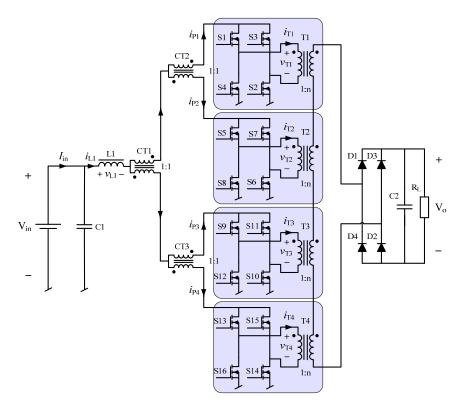

| 5.1     | NEW PARTIAL PARALLEL 3 KW ISOLATED BOOST CONVERTER     | . 70 |

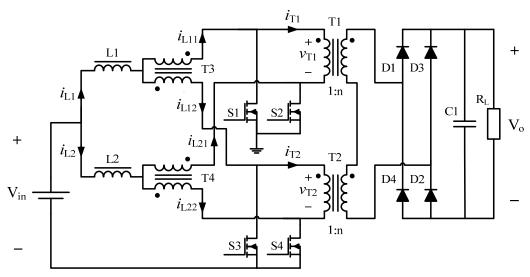

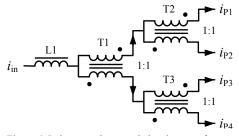

| 5.2     | NEW PARTIAL PARALLEL 10 KW ISOLATED BOOST CONVERTER    | . 71 |

| 5.3     | CONCLUSION ON EXTENDING POWER IN 1-10 KW RANGE         | . 74 |

| 6       | CONCLUSION AND FUTURE WORK                             | . 75 |

| 6.1     | SUMMERY AND CONCLUSION                                 | . 75 |

| 6.2     | FUTURE WORK                                            | . 78 |

| REFERE  | NCES                                                   | . 79 |

| APPEND  | DIX A                                                  | . 82 |

| APPEND  | DIX A1                                                 | . 83 |

| APPEND  | DIX A2                                                 | . 84 |

| APPEND  | DIX A3                                                 | . 85 |

| APPEND  | DIX A4                                                 | .86  |

| APPEND  | DIX A5                                                 | . 87 |

| APPEND  | DIX A6                                                 | . 88 |

| APPEND  | DIX A7                                                 | . 89 |

# **Nomenclature**

| D                    | Switch duty cycle                                                                    |

|----------------------|--------------------------------------------------------------------------------------|

| $D_L$                | Inductor duty cycle                                                                  |

| $f_S$                | Converter switching frequency                                                        |

| T                    | Converter period time, $T=1/f_S$                                                     |

| $T_L$                | Inductor period time, $T_L = T/2$                                                    |

| $T_1$                | Period time one                                                                      |

| n                    | Transformer turns ratio, $n=N_S/N_P$                                                 |

| $F_R$                | AC resistance factor, $F_R = R_{ac}/R_{dc}$                                          |

| $F_{R,P}$            | AC resistance factor of primary winding                                              |

| $F_{R,S}$            | AC resistance factor of secondary winding                                            |

| $F_{R,T}$            | AC resistance factor of complete transformer                                         |

| $h^{n,1}$            | Height of conductor                                                                  |

| $h_P$                | Height of $P^{th}$ winding portion                                                   |

| $h_{\Delta}$         | Height of primary-secondary intersection                                             |

| $h_w$                | Total height of transformer winding                                                  |

| $\overset{\circ}{H}$ | Magnetic field strength                                                              |

| B                    | Flux density                                                                         |

| w                    | Stored energy in magnetic volume                                                     |

| δ                    | Penetration depth in material                                                        |

| $\varphi$            | Conductor height in penetration depth at fundamental frequency, $\varphi = h/\delta$ |

| p                    | Winding portion                                                                      |

| m                    | Number of layers in winding portion                                                  |

| $l_w$                | Mean turn length                                                                     |

| $b_w$                | Breadth of winding                                                                   |

| M                    | Number of primary-secondary intersections                                            |

| N                    | Number of winding turns                                                              |

| $N_P$                | Number of primary turns                                                              |

| $N_S$                | Number of secondary turns                                                            |

| $\mu_0$              | Permeability of free space                                                           |

| $V_e$                | Magnetic volume                                                                      |

| X                    | Distance from H-field zero crossing, $0 \le x \le h_P$                               |

| $E_C$                | Stored energy in diode capacitance                                                   |

| κ                    | Primary switch loss factor                                                           |

| $N_{sw}$             | Number of parallel power MOSFETs in switch                                           |

| $L_{LK}$             | Transformer leakage inductance                                                       |

| $L_{LK,P}$           | Transformer leakage inductance referred to primary side                              |

| $L_{LK,S}$           | Transformer leakage inductance referred to secondary side                            |

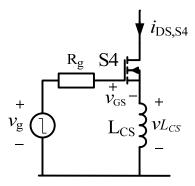

| $L_{CS}$             | Common source inductance                                                             |

| $L_X$                | Commutation inductance, $L_X = L_{SP} + L_{LK} + L_{SS}/n^2$                         |

| $L_{SP}$             | Primary stray inductance                                                             |

| $L_{SS}$             | Secondary stray inductance                                                           |

| $L_S$                | Stray inductance of interconnection wiring                                           |

| $L_{loop}$           | Total parasitic circuit inductance of loop                                           |

| $\eta$               | Converter conversion efficiency                                                      |

| $V_{in}$             | Converter input voltage                                                              |

| $V_o$                | Converter output voltage                                                             |

| $V_{in,min}$         | Converter minimum input voltage                                                      |

| $V_{(BR)DSS}$        | Rated drain-source break down voltage                                                |

$v_{LCS}$  Induced voltage across common source inductance

$v_{GS}$  Instantaneous gate-source voltage

$V_{GS}$  Gate-source dc voltage  $v_g$  Gate driver output voltage  $V_C$  Voltage clamp level

$V_{S4}$  Switch drain-source voltage  $V_D$  Diode forward voltage drop  $V_R$  Diode reverse voltage

$v_L$  Loop voltage driving current change

Switch rms current  $I_{S,rms}$ DC input current  $I_{in}$ Inductor L1 current  $I_{L1}$ Drain-source current  $i_{DS}$ DC output current  $I_o$ Transformer current  $i_{TI}$ Switch current  $I_{S4}$ Diode current  $I_D$

$R_{DS(on)}$  Power MOSFET drain-source on-resistance

$R_{S(on)}$  Total primary switch on-resistance  $R_{in,min}$  Minimum converter dc input resistance  $P_{in,max}$  Maximum converter input power

Power MOSFET conduction loss

$P_{DS,con}$  Power MOSFET conduction loss  $P_{CL}$  Total current commutation loss

$P_{CC-VL}$  Converter current commutation loss in voltage limited mode (mode 1) Converter current commutation loss in current limited mode (mode 2)

$P_{D.con.}$  Diode conduction loss

$P_{D,SW}$  Diode switching loss (capacitive)  $P_R$  Total converter rectifier losses

$P_{R,con}$  Total converter rectifier conduction losses

$P_{R,SW}$  Total rectifier switching losses

$P_{FB,con}$  Total primary full-bridge conduction loss

### 1 Introduction

### 1.1 Scope

The scope of this report is to present the results obtained in the PhD project "Modular Power Electronic Converters with Galvanic Isolation in the Power Range 1 to 10 kW," performed by the author during the period from September 2006 through January 2010. Many of the scientific results obtained in the project have been published in the form of peer reviewed conference and journal papers and a patent application. The published papers form an integral part of this thesis and are included in appendix [A1]-[A7].

The objective of this report is to supplement the already published information in [A1]-[A7] by placing the published papers in the context of the overall project and thereby present a more coherent and complete overview of the work and results obtained.

Further, it is the hope that this thesis can serve as a small condensed "designer's theoretical handbook" on key fundamental issues related to the design and optimization of high power converters for low voltage applications.

### 1.2 Background and Motivation

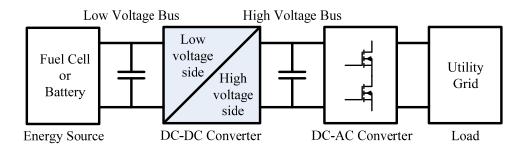

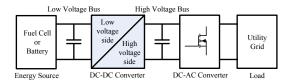

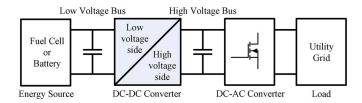

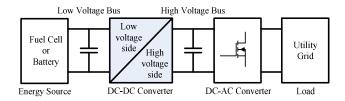

The background and motivation for this work is the emerging need for high power converters to boost voltage levels from low voltage electrical power sources to higher voltages required by the load. Figure 1, presents the typical power architecture of these systems.

Fig. 1. Typical power system architecture for high-power low-voltage application.

An isolated dc-dc converter boosts the unregulated low voltage supply to a much higher dc voltage, typically 400 V for single phase and 7-800 V for three phase utility grid interface. Wide input voltage range, typically in the range of 30-60 V, is normally required.

Subsequently, a dc-ac inverter will typically convert high voltage dc output into single- or three phase ac voltage for interface to the utility grid or control of electrical motors etc.

Since the dc-ac converter operates at high voltage and is well known from other high power applications such as in UPSs, motor drives, solar inverters etc., the objective of this study is to focus on achieving high efficiency in the critical low voltage to high voltage dc-dc converter.

Typical systems include fuel cell systems, battery powered systems and even some photovoltaic systems. Applications include systems for emergency power back-up (UPS), de-centralized combined heat and power systems, traction applications such as hybrid electrical vehicles, forklift trucks and special applications such as low emission power generation for truck and ship containers and remote power generation for light towers, camper vans, boats, beacons, and buoys etc. [1]-[2].

Common to all of these applications is that cost of initial investment is high due to high cost of fuel cells, batteries or solar cells. Low conversion efficiency in the power electronic converter will significantly increase the required investment since more/larger cells will be needed. High cost of fuel (hydrogen etc.) will further add to the total cost. Even size and cost of the electronic power converter itself may increase as a consequence of higher dissipated power and consequently increased thermal stress of components and system.

Achieving higher conversion efficiency in the power electronic converter required for boosting the low source voltage to the higher voltage required by the application, will therefore become a major competitive parameter in these applications.

In recent years, significant research effort has been devoted internationally to address the diminishing conversion efficiency which has been seen in high power low voltage applications [1]-[3].

A large number of alternative converter topologies and implementations have been proposed [4]-[5], [9]-[37] typically achieving high conversion efficiency at the medium to high input voltage range and at medium power levels. Best designs achieve peak efficiencies up to 96% [4], [9], [10], [15], [27], [28], [32]-[35]. At maximum output power and minimum input voltage, however, efficiency typically drops significantly to 90 % or below.

In fuel cell applications (and many others), peak power is reached at minimum input voltage, and available system peak power is directly affected by the decreased efficiency of the power converter. Thus, power source needs to be oversized in order to compensate for the reduced efficiency of the power converter. Furthermore, thermal design of the power converter itself needs to be dimensioned for this high peak power dissipation further increasing size and cost of the power electronic converter.

### 1.3 Project Objectives

The primary objective of this project is to study and demonstrate the absolutely maximum achievable conversion efficiency in high power converters for low-input-voltage to high-output-voltage applications.

In view of the requirements for fuel cell applications, the project focuses on solutions that provide galvanic isolation between input and output and are capable of operating over a wide input voltage range of typically a factor 2:1 [38].

Special consideration has to be given to achieving high conversion efficiency in the worst case operating point i.e. at maximum output power and minimum input voltage.

A second objective is to analyze and suggest the most efficient way - in terms of conversion efficiency and cost – to scale power level in the power range from 1 to 10 kW.

### 1.4 Common Specification

To ensure clear and ambitious goals for the research work, a list of high level converter requirements was formulated, see table I. The purpose of the list is to ensure that the project outcome will be adaptable to the relevant applications and thus constitute useful solutions.

A second purpose is to allow comparison of achieved results with a similar PhD study being conducted by Mr. Pawel Klimczak at the University of Aalborg on non-isolated converters for the same specification.

In order to avoid unnecessary limitation of creativity, the list of requirements only contain fundamentally needed high level requirements thus ensuring that solutions can realistically be applied to the applications foreseen [1]-[3], [38]-[41].

Thus, the primary focus is to achieve maximum conversion efficiency while still satisfying real life requirements to input voltage range, current and voltage control, and ripple currents. Such that presented results are realistic, and conclusions are valid for typical applications.

Value **Comments Parameter** Maximum achievable power in 1000 W Output power  $P_{out}$ single converter Input voltage range  $V_{\rm in}$  $30-50~V_{DC}$ Start-up voltage up to 60V Output voltage  $V_{\rm o}$  $400\;V_{DC}$ Galvanic isolation required Converter efficiency to be optimized 98 % Efficiency target  $\eta$ at low input voltage. For full control of input current Output power regulation 0-100 % transients Input current ripple <15 % For load range 15-100% >10kHz Input current slew rate <3 A/sSlow dynamics of fuel cell

TABLE I. CONVERTER SPECIFICATION

### 1.5 Project Plan and Content

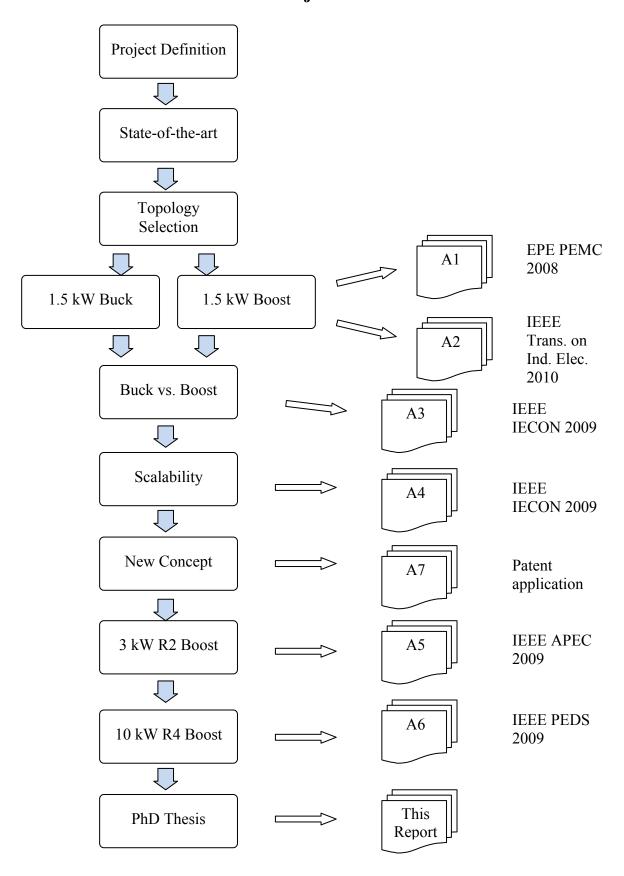

A flow chart presenting the work packages carried out during this PhD project is shown in fig. 2. The flow chart also illustrates how the published papers, articles, and the patent application relate to key parts of the work carried out.

Following definition of project objectives including the target specification presented in table I, a state-of-the-art analysis is performed in order to establish current status on achievable conversion efficiency and proposed solutions.

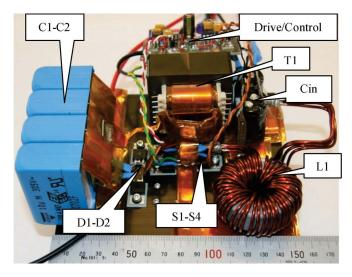

In parallel with the detailed design of a 1.5 kW isolated boost converter [A1]-[A2], a detailed analysis of converter losses in high power converters for low voltage applications is carried out. The analysis confirms the choice of boost converter as the most efficient converter topology - but only because voltage rating of primary switches has been dramatically reduced by

eliminating primary side clamping circuits. To further verify the analysis, an isolated full-bridge buck converter is designed, built, tested, and compared with the 1.5 kW boost converter [A3].

Next phase is to analyze and suggest possibilities for increasing power level within the power range of 1-10 kW. Instead of immediately reverting to paralleling of complete converter modules - which will definitely be feasible - it is decided to identify those particular areas in the boost topology, where scaling of power is critical – and thus will benefit the most from paralleling. Apart from the obvious need to parallel power MOSFETs, it is found that the high ac-current loop from primary switches to the transformer primary windings is a particularly critical area with respect to scaling of power level.

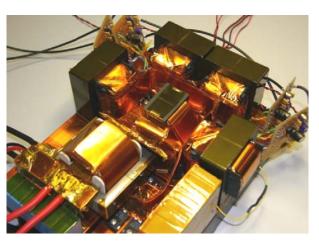

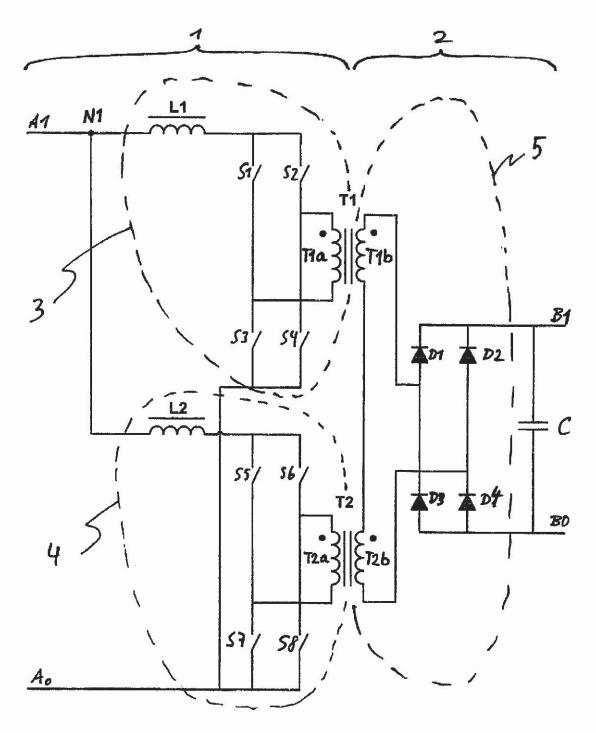

A new method for partial paralleling of isolated boost converters is then proposed [A5]-[A7]. A patent application covering the new principle is filed [A7]. Two prototype converters are designed, built, and tested to demonstrate the feasibility of the new principle. The 3 kW dual version is published in [A5] and the quad 10 kW converter is published in [A6].

### 1.6 Thesis Structure and Content

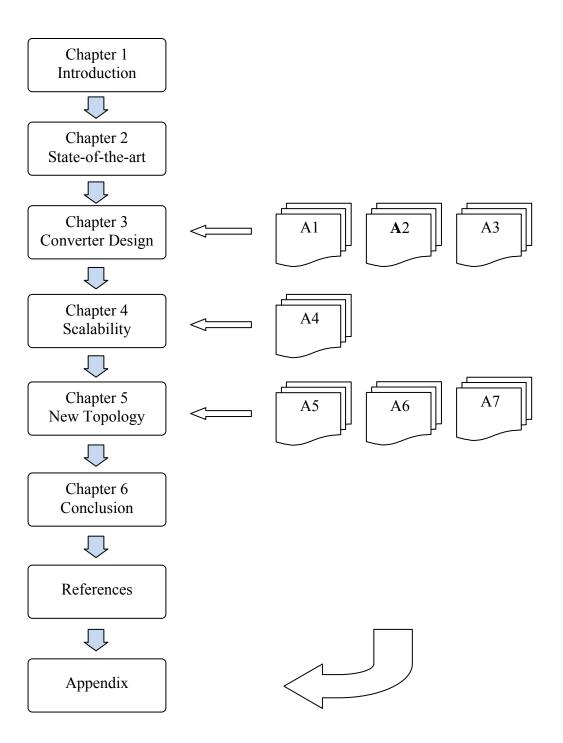

The structure, organization and content of this PhD thesis is visualized in the flow chart presented in fig. 3.

The published journal paper, conference papers and the patent application [A1]-[A7] form an integral part of this PhD thesis and are therefore appended. As illustrated in fig. 2, the published papers cover a broad range of the work performed in this PhD study.

The purpose of this report is therefore to complement the already published papers by providing a condensed and coherent presentation of the overall project and its results. Special focus will be devoted to presenting a coherent derivation of the key fundamental theoretical aspects of this project.

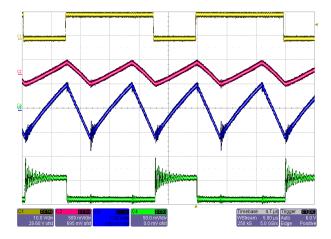

Since most of the experimental results are already included in the published material [A1]-[A7], they are only included in a very restricted form in this thesis. And mostly where it serves the purpose of extending analysis of experimental results in order to verify or illustrate significance of the theoretical results.

Generally, the thesis is organized to reflect the general research approach adopted in the project i.e. definition of objective => state-of-the-art analysis => detailed design and analysis => demonstration of single converter => extension of power level => conclusion. The intension of this thesis organization is to present the project results in a condensed and straightforward manner.

### **PhD Project Overview**

Fig. 2. PhD project work plan.

### **PhD Thesis Structure**

Fig. 3. PhD thesis structure.

### 2 State-of-the-Art

The purpose of this chapter is to present an overview of the present state-of-the-art within isolated dc-dc converters for low voltage high power applications. Recent published literature primarily in the form of journal papers, conference papers and tutorial notes, has been searched and analyzed to establish the present state-of- the-art. Main focus has been devoted to material presenting technical results, preferably supported by experimental results, useful for or relating to the overall specification defined for this project (table I).

In recent years, research on improving conversion efficiency in high power low voltage dc-dc converters for fuel cell applications, has attracted widespread international attention. Consequently, a significant amount of scientific literature has been published on the subject. Despite this fact, achieved efficiency results are often not published. Even when results are published, test conditions are often not reported. Further, measuring efficiencies in the high nineties are not trivial requiring strict attention to measurement tolerances and calibration of test set-up. Reliable efficiency results are thus scarce and generally very difficult to compare across alternative solutions.

Despite the general lack of reliable efficiency data, this chapter attempts to present an overview of published solutions, techniques and correspondingly achieved efficiencies for low voltage high power dc-dc converters.

For each published solution, a short description of the proposed solution is given together with a short summary of the published efficiency data. For a more in-depth presentation of the published material, the reader is referred to the full papers on the CD-ROM attached in the back of this thesis.

To best be able to compare efficiency data across the many different solutions, two sets of data have been selected. The maximum (or peak) efficiency achieved simply because it is often the only available data published i.e. the data that everyone wants to publish. However, much more useful data is the efficiency at minimum input voltage and maximum output power. Since this is most often the system-wise worst-case-point and therefore the driving parameter for overall system performance, size, and cost.

Papers published as part of this project are not included in the state-of-the-art analysis, they are attached in appendix A. However, they are included for reference in table II: "Comparative efficiency of low voltage high power converters."

## 2.1 Isolated Boost Type Converters

This section lists selected published isolated boost type converter designs intended for high efficiency conversion of low input voltage high power to high output voltage. For each published design, a brief description of the topology used and the published efficiency results are provided.

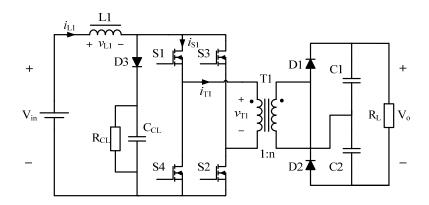

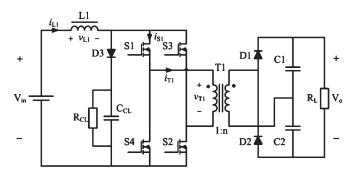

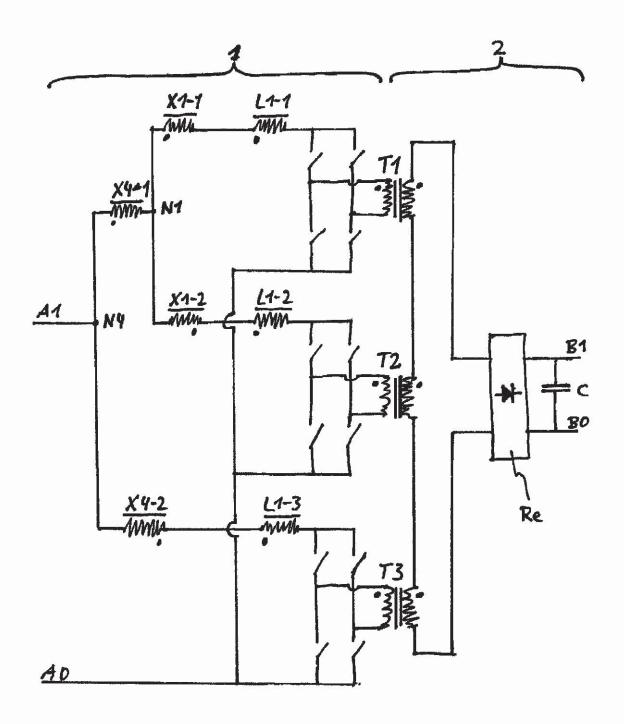

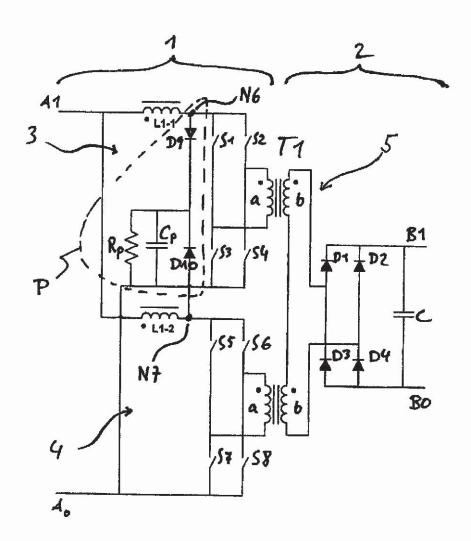

Figure 4, presents a generic isolated boost converter including voltage clamp circuit across primary switches.

Fig. 4. Isolated full-bridge boost with voltage doubler and voltage clamp circuit.

#### 2.1.1 Isolated Push-Pull Boost Converter

#### PP Boost 1:

A 1 kW fuel cell converter consisting of an isolated push-pull boost dc-dc converter followed by an H-bridge dc-ac converter is presented in [4]. The push-pull converter is hard switched and uses a common voltage clamp circuit across both primary switches.

Input voltage range is 25-45 V, and output voltage is 350-400 V. Maximum measured efficiency reaches 96.4% at 300 W output and 42 V input. At maximum output power and minimum input voltage (900 W at 25 V input) efficiency is 91%.

#### PP Boost 2:

A 1.5 kW fuel cell power converter consisting of an isolated resonant push-pull dc-dc converter followed by an H-bridge dc-ac converter is presented in [5]. A voltage doubler on output is used to tune converter current resonance such as to reduce output diode reverse recovery losses. Active clamp circuits are used across the two primary switches.

Input voltage range is 30-70 V and dc-dc converter output voltage is 350 V. System peak efficiency reaches 94% at 70 V input and 700 W output. Minimum efficiency is 92.5% at 1.5 kW output and 30 V input. No separate efficiency measurements for the dc-dc converter are provided.

#### 2.1.2 Isolated Two-Inductor Boost Converter

The isolated two-inductor boost converter was first presented by P. J. Wolfs in 1993 [6]. The converter topology is the boost version of a HY-Bridge rectifier, also known as the current doubler, invented by O. S. Seiersen [7]-[8].

A large number of papers related to the high power low input voltage application of the two-inductor boost have been published, among these [9]-[15].

#### TI Boost 1:

A 500 W isolated two-inductor boost with active clamping is presented in [9]. An active clamp and reset circuit is used to clamp the allegedly severe voltage overshoot on primary switches due to the stored energy in the transformer leakage inductance. Primary switch currents are

triangular having large rms values. Input voltage range is not published, output voltage is 380 V. Peak efficiency is 96% measured at 300 W output and approximately 52 V input.

#### TI Boost 2:

A 1 kW modified isolated two-inductor boost with active clamping and reset is presented in [10]. Two transformers with individual rectifiers are effectively in parallel on input and in series on output. Due to the active clamping switch currents are triangular. Input voltage range is 26-50 V and output voltage is 400 V. Measured maximum efficiency is 95.6% at 600 W output power. Input voltage condition for the measured efficiency is not published.

#### TI Boost 3:

Two phase shifted two-inductor boost power stages are interleaved in [11]. Two voltage doubler rectifiers are in parallel on output sharing the same capacitors. By operating close to discontinuous conduction mode, current sharing between parallel power stages is achieved. A 200 W prototype converter verifies operation.

#### TI Boost 4:

A 1 kW two-inductor boost converter with active clamping is presented in [12]. Input voltage is 48 V and output voltage is 350 V. Peak efficiency of approximately 87% is reached at 500 W. At 1 kW output, efficiency has dropped to 77%. A comparable full-bridge boost converter is claimed to be 6-10% less efficient.

#### TI Boost 5

A 1 kW two-inductor boost stage is presented in [13] as part of a two-stage dc-dc converter for fuel cell applications. Input voltage is 80 V and output voltage is 400 V. At 750 W output power, efficiency is 67%.

#### TI Boost 6:

In [14], a 300 W two-inductor boost with soft turn-off snubbers is presented. Input voltage range is 18-32 V and output voltage is 48 V. Maximum efficiency is 92% at 28 V input and 300 W output power.

#### TI Boost 7:

A 1.5 kW bi-directional two-inductor boost intended for bi-directional interface between a 28 V and a 270 V aircraft power bus is presented in [15]. Active clamping and reset is used on low voltage side to clamp switch overvoltage. A phase-shift plus pulse-width modulation is used to create near square-wave low rms switch currents. Input voltage range is 22-32 V. Peak efficiency in boost mode is 96% at 32 V input and 750 W output. At 22 V input and 1.5 kW output, efficiency drops below 89%.

### 2.1.3 Isolated Full-Bridge Boost Converter

Isolated full-bridge boost converters have also been proposed extensively for high power low voltage applications, among these [16]-[27].

#### FB Boost 1:

A 5 kW isolated full-bridge boost converter is proposed for fuel cell electrical vehicles in [16]. Input voltage is 24 V and output voltage is 300 V. A passive voltage clamp circuit is used to limit voltage spikes across primary switches due to transformer leakage inductance. Peak efficiency at maximum output power is 94%. Very few design details or test results are given.

#### FB Boost 2:

A 1.2 kW interleaved isolated full-bridge boost converter is presented in [17]. Two separate isolated full-bridge boost converters with voltage doubler rectifiers are series connected on output and parallel connected on input. The series connected outputs guarantee average current sharing between converter stages, but at the expense of higher rectifier losses. Voltage clamp circuits across primary switches are used to clamp over voltages caused by transformer leakage inductance. Input voltage is 33 V and output voltage is 400 V. Maximum measured efficiency is 90.5% at 1.2 kW output.

#### FB Boost 3:

A 1 kW isolated full-bridge boost converter with zero current switching (ZCS), is presented in [18]. Large series resonant inductance and parallel capacitance form a slow resonant commutation during primary switch overlap time i.e. the storage inductor charging time. Zero current turn-on and zero current turn-off in primary switches are thereby obtained. Voltage- and load regulation is performed by wideband frequency modulation in order to achieve constant storage inductor charging time and thereby maintain zero current switching. Input voltage range is 22-27 V and output voltage is 1 kV. Peak efficiency is 92% at 1 kW output and 27 V input. At 22 V input and 1 kW output, efficiency is 88%.

#### FB Boost 4:

A 1.4 kW resonant isolated full-bridge boost converter is presented in [19]. Adding resonant capacitors across primary switches in addition to the series parallel resonant tank used in [18], a full resonant converter is obtained. Zero voltage and current turn-on and zero voltage turn-off are achieved. Regulation is performed by narrowband frequency control (250-370 kHz). Input voltage is 100 V and output voltage is 374 V. Maximum efficiency is below 90%.

#### FB Boost 5:

A 20 kW isolated full-bridge boost converter is analyzed in [20]-[22]. Input voltage range is 90-200 V and output voltage is 700 V. The converter is only tested up to 10 kW input power and no efficiency results are published. An active voltage clamp circuit designed to clamp 5-10% of converter output power is presented in [22]. At 9 kW input power, measured clamping energy is 505 W. Measured transformer stray inductance is 750 nH. Primary switches are rated for 600 V.

#### FB Boost 6:

Three bi-directional isolated full-bridge boost converters intended for electrical vehicles are presented in [23]-[25]. Specifications are quite similar, low voltage battery terminal is 8-15 V and output voltage is in the range of 250-450 V.

In [23]-[24] maximum boost mode power is 1.6 kW and maximum buck mode power is 5 kW. An active voltage clamp circuit as described in [26] is used to clamp primary switch over voltages caused by large transformer leakage inductance. Following a design rule of thumb in [24], voltage rating on primary switches is 55 V i.e. more than 3 times maximum input voltage.

In [25], boost power is up to 3 kW and maximum buck power is 2 kW. A soft commutation method to reduce voltage clamping energy is presented. By keeping secondary switches on, transformer secondary winding is shorted during current commutation right after primary switches have been turned off. The full clamp voltages are thus available for current commutation thereby reducing current switching time and consequently clamp energy.

Maximum efficiency in boost mode is approximately 94% at 10 V input and 1500 W output power. At 2.5 kW output and 8.5 V input, efficiency drops below 82%.

#### FB Boost 7:

A 500 W three phase isolated boost converter with active clamp circuit is presented in [27]. Three half-bridge primary switching legs operate in interleaved mode, each sequentially transferring the input current to output through three power transformers and a three phase rectifier. Due to the active clamp circuit, switch current is triangular having high rms value. Input voltage is 30-60 V and output voltage is 400 V. Maximum efficiency is 96% at 200 W output. Input voltage condition for the measured efficiency is not published.

### 2.2 Isolated Buck Type Converters

This section lists selected published isolated buck type converter designs intended for high efficiency conversion of low input voltage high power to high output voltage. For each published design, a brief description of the topology used and the published efficiency results are provided.

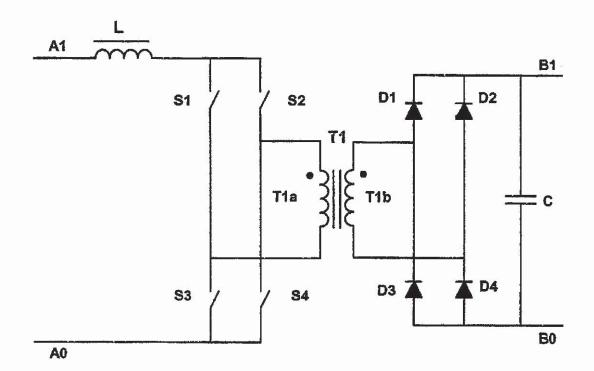

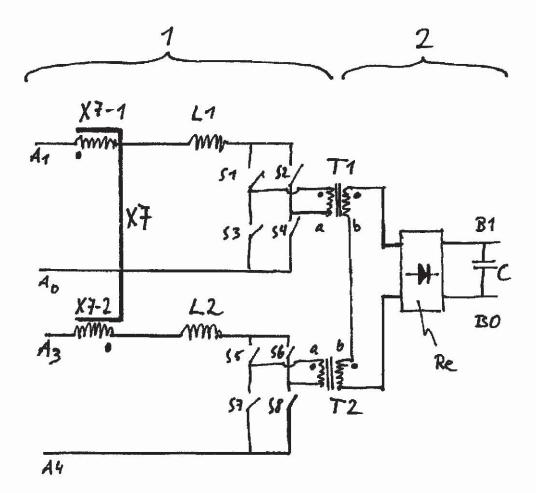

Figure 5, presents a generic isolated buck converter.

Fig. 5. Isolated full-bridge buck converter with full-bridge rectifier.

### 2.2.1 Isolated Full-Bridge Buck Converters

A number of isolated full-bridge buck converters for high power low voltage applications have been presented, among these [28]-[32].

#### FB Buck 1:

A 75 kW isolated full-bridge buck converter for fuel cell applications is presented in [28]. Input voltage range is 200-380 V and output voltage is 380 V. Measured efficiency is approximately 95%. No design details are published.

#### FB Buck 2:

A 5 kW isolated full-bridge buck converter is presented as part of a power system for fuel cell applications [29]. A single primary full-bridge inverter supplies two power transformers in parallel, each having separate full-bridge rectifiers and output filters. The two outputs are series connected in order to reduce rectifier voltage stress. Input voltage range is 22-41 V and output

voltage is 400 V. Measured efficiency of dc-dc converter is 90% at 4.4 kW output. Input voltage condition for the measured efficiency is not published.

#### FB Buck 3:

A system of multiple phase-shifted full-bridge buck converters is proposed in [30]. By introducing storage inductors between primary inverter phase legs of neighboring phase shifted power stages, conduction loss of primary switches is reduced. The design of a 500 W per bridge converter is analyzed. No test results are published. Simulated efficiency projects an efficiency of 95% for a 24-40 V input and 400 V output converter – when switching at 256 kHz.

#### FB Buck 4:

A 1.2 kW isolated full-bridge buck converter with a lossless output diode clamp circuit is presented in [31]. Using a new lossless output diode clamp circuit and phase shift control of primary switches, zero voltage and zero current switching of primary switches can be achieved. Input voltage range is 27-46 V and output voltage is approximately 200 V. Maximum measured efficiency is 94.2% at 32 V input and 700 W output power. At 28 V input and 1.2 kW output, efficiency is 92.5%.

#### FB Buck 5:

Finally, a 3 kW isolated full-bridge converter for fuel cell applications is proposed in [32]. The converter is unregulated operating at fixed 50% duty cycle. Adaptation to variable input voltage (due to fuel cell output voltage drop) is achieved by sequentially adding transformer secondary windings - by means of relay switching - to increase transformer turns ratio. Input voltage range is 44-96 V and output voltage is variable in the range 217-310 V. A maximum efficiency of approximately 96.5% is achieved at 60 V input and 1 kW output power. Efficiency drops to 94% at 45 V input and 2 kW output power.

### 2.2.2 Isolated Three Phase Full-Bridge Buck Converters

This section is mainly devoted to the much published three phase isolated buck converter also known as the V6 topology. Although it is basically an interleaved derivative of the phase shift controlled full-bridge buck converter, the number of publications related to this topology – and its apparently high performance – justifies the creation of a special section.

#### FB Buck V6:

The isolated three phase V6 converter presented in [33]-[37] consists of three phase-shift controlled full-bridge inverter stages which are interleaved by means of phase-shifting each inverter stage 120 degree apart. Each H-bridge inverter stage drives the primary winding of a single phase transformer. The secondary windings of the three power transformers are star-connected (Y-connected) and fed to a common 6-pulse three phase rectifier followed by a single storage inductor and output capacitor.

Since all three power stages are controlled by the same phase angle (however phase shifted 120 degree apart), a single common controller can control all three power stages. Current sharing between power stages is guaranteed by the common output inductor. Due to cancellation, input ripple current is significantly reduced and ripple frequency at input and output is tripled.

The star-connection of transformer secondary windings reduces transformer turns ratio by a factor of two. Input power is shared between three parallel power stages, reducing ac-current

levels in each power stage by a factor of 3 thereby reducing susceptibility to resistive and inductive losses ( $i^2R$  and  $Li^2$ ) in interconnections.

Very high efficiencies have been reported for this topology. In [33]-[34], a 3 kW converter intended for fuel cell applications is presented. Input voltage range is 20-50 V and output voltage is 200 V. Measured efficiency seems to peak just below 97% at half output power. At maximum output power, efficiency is 96%. Measurement tolerances are however  $\pm 1\%$  and input and output voltage conditions for the measured efficiency curve are not published.

Furthermore, the converter is tested in the efficiency sweet spot at a phase angle of 150 degree where the converter is operating as a dc-transformer without any possibility of control. At phase angles below  $120^{\circ}$  when converter is in regulation, rms-current in primary switches will be significantly higher than in comparable full-bridge buck converters. Published efficiency data for the V6 converter operated in regulated mode ( $\alpha$ <120°) has not been found.

### 2.3 Summary of State-of-the-Art Analysis

Twenty-two different converter designs intended for low voltage high power applications have been identified and analyzed. In table II, the published efficiency performance is listed for comparison.

Unfortunately, published efficiency results are generally rare and difficult to compare since important operating test conditions such as input voltage level, output voltage levels and measurement tolerances are often not published.

To perform the best possible comparison of the available data, both best case efficiency and the more important worst case efficiency data are compared.

For comparison, efficiency data from the three boost converters [A1]-[A2], [A5], and [A6], as well as the buck converter [A3], published as part of this PhD project is included in table II.

The system performance, cost, and size critical worst case efficiency column is highlighted in red. Best performance within each topology group is highlighted in light blue, and overall best performance is highlighted in blue.

In addition to the comparison of achieved efficiencies, a number of observations and conclusions can be drawn from the study of the published literature:

- 1. Many converter designs achieve modest to high efficiency at high input voltage and medium power. However, except for the V6 converters (though not in regulation) and the converters presented in this PhD project, all converters exhibit a very significant drop in efficiency in the critical low-input-voltage and maximum-output-power point.

- 2. High power transformers for low voltage applications have high leakage inductance [9], [20]-[22]. Further, power transformers with high turns ratio have high leakage inductance [24], [33], [35], [42]. Large transformer leakage inductance is generally considered a significant source of switching losses in boost type converters. None of the published papers have substantiated this claim or analyzed transformer ac-resistance and leakage inductance.

- 3. Primary switch voltage rating must be oversized by a factor of 2-3 in boost converters [10], [20]-[25] to allow headroom for the voltage clamp circuits to operate. Alternatively, active clamp- or reset circuits introduce additional switches and create triangular current waveforms thus increasing conduction losses.

- 4. Voltage clamp circuits are needed on boost converter primary switches [2], [4], [9], [10], [12], [14], [15], [20]-[27]. As a consequence of the allegedly large transformer leakage inductance, many forms of voltage clamping techniques and circuits are widely used to clamp voltage spikes across primary switches in boost type converters.

- 5. Soft switching is needed to achieve high conversion efficiency in low voltage applications [2], [3], [26], [27], [33], [35]. None of the published papers have presented any measured or analyzed data on switching losses.

The validity of these five key-design-assumptions will be analyzed in the next chapter.

TABLE II.

COMPARATIVE EFFICIENCY OF LOW VOLTAGE HIGH POWER CONVERTERS

| Topology              | No. | Power<br>Level | Input Output<br>Voltage Voltage |         | Best case<br>Efficiency |     |       | Worst case<br>Efficiency |     |       | Reference                |

|-----------------------|-----|----------------|---------------------------------|---------|-------------------------|-----|-------|--------------------------|-----|-------|--------------------------|

|                       |     | [W]            | [V]                             | [V]     | η                       | Vin | Pout  | η                        | Vin | Pout  |                          |

| Push-Pull             | 1   | 1000           | 25-45                           | 350-400 | 96.4                    | 42  | 300   | 91                       | 25  | 900   | [4]                      |

| Boost                 | 2   | 1500           | 30-70                           | 350     | 94                      | 70  | 700   | 92.5                     | 30  | 1500  | [5] <sup>1</sup>         |

|                       | 1   | 500            | 60                              | 380     | 96                      | 52  | 300   | -                        | -   | -     | [9]                      |

|                       | 2   | 1000           | 26-50                           | 400     | 95.6                    | -   | 600   | -                        | -   | -     | [10]                     |

| Two-                  | 3   | 200            | -                               | -       | -                       | -   | -     | -                        | -   | -     | [11]                     |

| Inductor              | 4   | 1000           | 48                              | 350     | 87                      | 48  | 500   | 77                       | 48  | 100   | [12]                     |

| Boost                 | 5   | 1000           | 80                              | 400     | 67                      | -   | 750   | -                        | ı   | -     | [13]                     |

|                       | 6   | 300            | 18-32                           | 48      | 92                      | 28  | 300   | -                        | 1   | -     | [14]                     |

|                       | 7   | 1500           | 22-32                           | 270     | 96                      | 32  | 750   | <89                      | 22  | 1500  | [15]                     |

|                       | 1   | 5000           | 24                              | 300     | 94                      | 24  | 4500  | -                        | •   | -     | [16]                     |

|                       | 2   | 1200           | 33                              | 400     | 90.5                    | 33  | 1200  | -                        | -   | -     | [17]                     |

|                       | 3   | 1000           | 22-27                           | 1000    | 92                      | 27  | 1000  | 88                       | 22  | 1000  | [18]                     |

|                       | 4   | 1400           | 100                             | 374     | <90                     | 100 | 1000  | -                        | -   | -     | [19]                     |

| Full-                 | 5   | 10000          | 90-200                          | 700     | -                       | -   | -     | -                        | -   | -     | [20]-[22]                |

| Bridge                | 6   | 3000           | 8-15                            | 250-450 | 94                      | 10  | 1500  | <82                      | 8   | 2500  | [23]-[26]                |

| Boost                 | 7   | 500            | 30-60                           | 400     | 96                      | -   | 200   |                          |     |       | [27]                     |

|                       | 8   | 1500           | 30-60                           | 400     | 98                      | 50  | 1200  | 96.8                     | 30  | 1500  | $[A1]-[A2]^2$            |

|                       | 9   | 3000           | 30-60                           | 400     | 98                      | 50  | 2900  | 96.9                     | 30  | 2850  | $\left[ A5\right] ^{2}$  |

|                       | 10  | 10000          | 30-60                           | 7-800   | 98.2                    | 50  | 9000  | 96.5                     | 30  | 10000 | $\left[A6\right]^2$      |

|                       | 1   | 75000          | 200-<br>380                     | 380     | 95                      | 200 | 75000 | 1                        | -   | -     | [28]                     |

| Full-                 | 2   | 5000           | 22-41                           | 400     | 90                      | -   | 4400  | -                        | ı   | -     | [29]                     |

| Bridge                | 3   | 500            | 24-40                           | 400     | -                       | ı   | -     | -                        | •   | -     | [30]                     |

| Buck                  | 4   | 1200           | 27-46                           | 200     | 94.2                    | 32  | 700   | 92.5                     | 28  | 1200  | [31]                     |

|                       | 5   | 3000           | 44-96                           | 217-310 | 96.5                    | 60  | 1000  | 94                       | 45  | 2000  | $[32]^3$                 |

|                       | 6   | 1500           | 30-60                           | 400     | 96.7                    | 30  | 600   | 95.4                     | 30  | 1500  | $[A3]^2$                 |

| Full-<br>Bridge<br>V6 | 1   | 3000           | 20-50                           | 200     | <97                     | -   | 1500  | 96                       | -   | 3000  | [33]-[35] <sup>3,4</sup> |

- No data available.

- 1 Efficiency data include dc-ac converter losses

- 2 Converter designs published in this project

- 3 Converter operated in unregulated dc-transformer mode

- 4 Input voltage and output voltage conditions are not published

# 3 Design of High-Power Low-Voltage Converters

In this chapter some fundamental issues related to design of high-power low-voltage converters are analyzed.

In the state-of-the-art analysis in chapter 2, a number of more or less generally accepted and widely adopted design approaches (myths) were identified:

- 1. High power transformers for low voltage applications and power transformers with high turns ratio have high leakage inductance.

- 2. Primary switch voltage rating must be oversized by a factor of 2-3 in boost converters.

- 3. Voltage clamp circuits are needed on boost converter primary switches.

- 4. Soft switching is needed to achieve high conversion efficiency in low voltage applications.

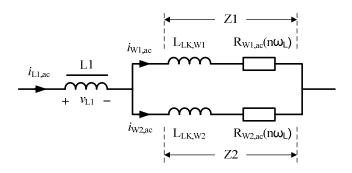

Following the analysis and presentation in this chapter, it becomes evident that all of these assumptions are wrong. Further, this chapter points out the special design issues that are particularly important in achieving high conversion efficiency in high-power low-voltage converters. These are:

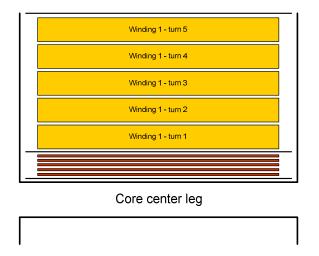

- a) Extensive interleaving of transformer windings is needed to reduce/avoid high conduction losses due to proximity effect.

- b) Transformer leakage inductance does not depend on transformer turns ratio.

- c) Transformer leakage inductance is proportional to number of turns squared.

- d) The extensive interleaving required to reduce proximity effect in combination with the low number of primary turns will result in extremely low primary side transformer leakage inductances.

- e) Voltage clamp circuits are effectively bypassed by the extremely low transformer leakage inductance rendering voltage clamps superfluous.

- f) Current switching speed is critical in achieving high conversion efficiency.

- g) Low stray inductance and low ac-resistance layout are very important in high-power low-voltage converters.

Finally, comparative analysis of buck and boost converters for low voltage high power applications shows that boost converters have fundamentally lower conduction losses in primary switches as well as lower reverse voltage stress on rectifier diodes. Thus, properly optimized boost converters will achieve higher conversion efficiency than comparable buck converters.

These findings are obviously very important in the process of selecting optimum converter topology and in the detailed design and optimization of high-power low-voltage converters.

### 3.1Low Impedance Level in High-Power Low-Voltage Converters

High-power low-input-voltage converters have extremely low primary side impedance levels.

Minimum converter steady state dc input resistance is given by

$$R_{in,min} = \frac{V_{in,min}^2}{P_{in,max}}. (1)$$

The extremely low impedance levels seen on converter primary side essentially turn the converter circuit into a current switching circuit where resistive and inductive elements are far more important to losses than capacitive elements.

In order to process power efficiently at these low impedance levels, all circuit elements including primary switches, transformers and interconnection wiring have to exhibit comparatively low impedance levels. For a 1% power loss, any resistive series element has to be lower than 1% of the minimum input impedance.

All circuit impedances in a high efficiency circuit therefore have to scale according to the minimum circuit impedance level. From (1), it therefore becomes evident that it is extremely important to achieve low conduction impedances (resistances and inductances) in low-voltage high-power circuits.

### 3.2 Basic Operation of Isolated Full-Bridge Converters

As a reference for the analysis made in the following chapters, the basic operating principles of the isolated full-bridge boost and full-bridge buck converters are presented in the following sections.

### 3.2.1 Isolated Full-Bridge Boost Converter

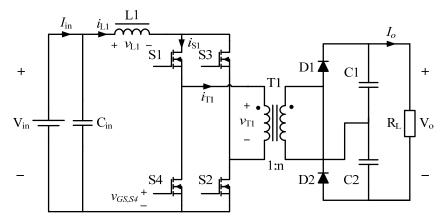

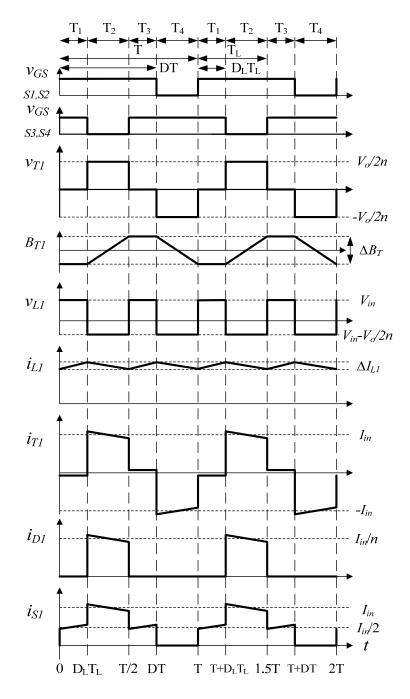

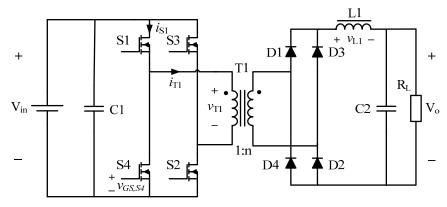

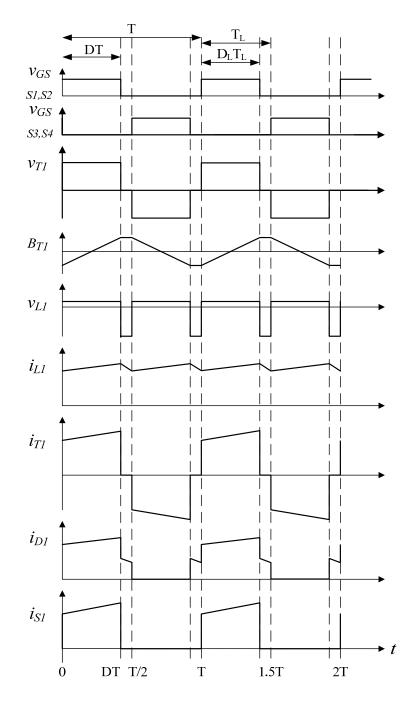

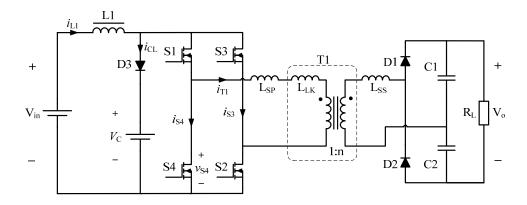

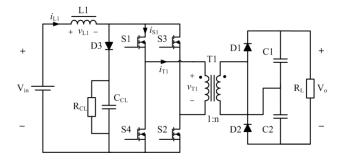

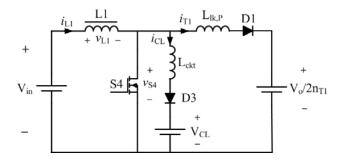

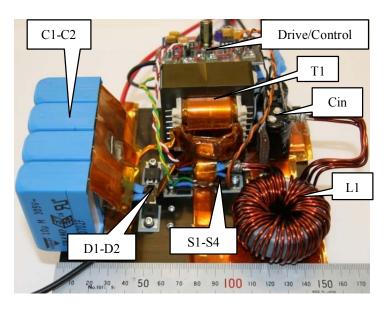

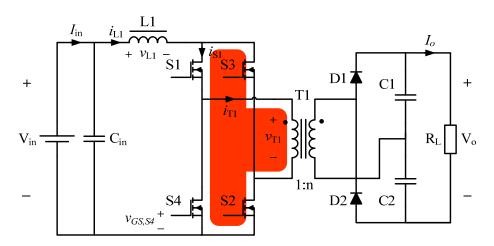

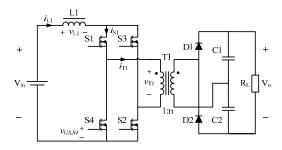

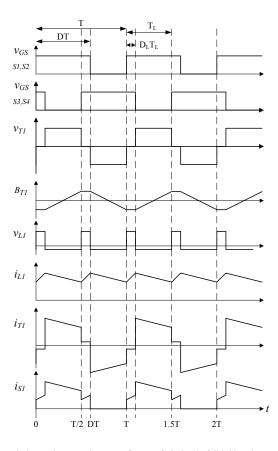

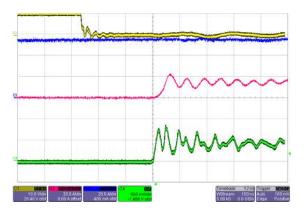

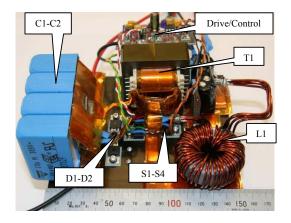

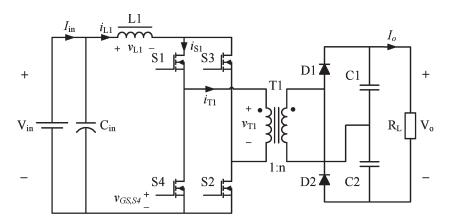

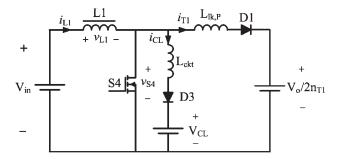

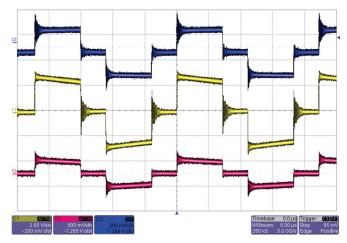

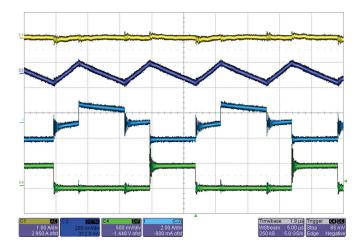

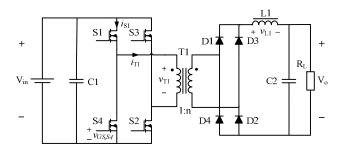

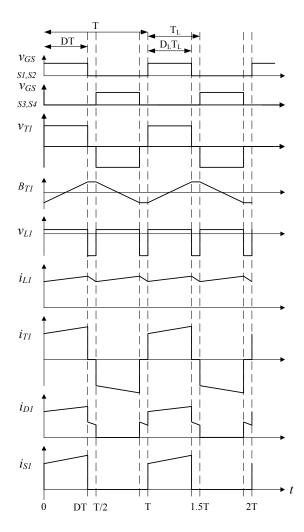

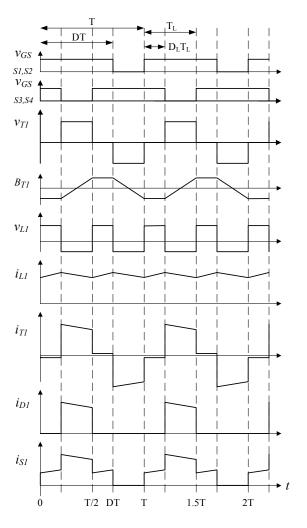

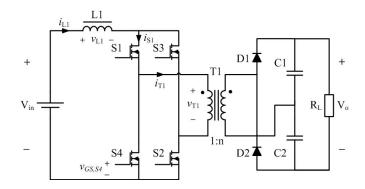

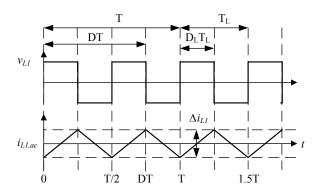

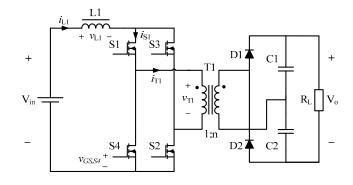

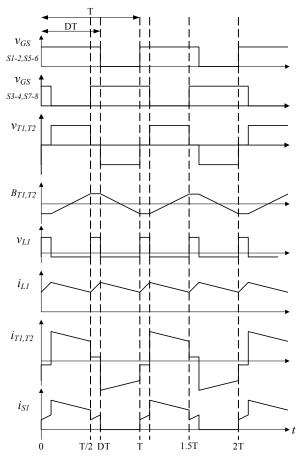

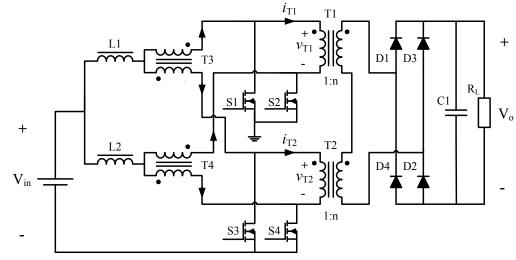

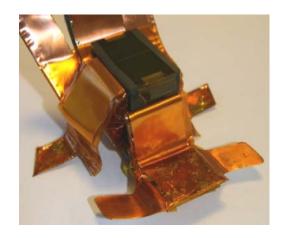

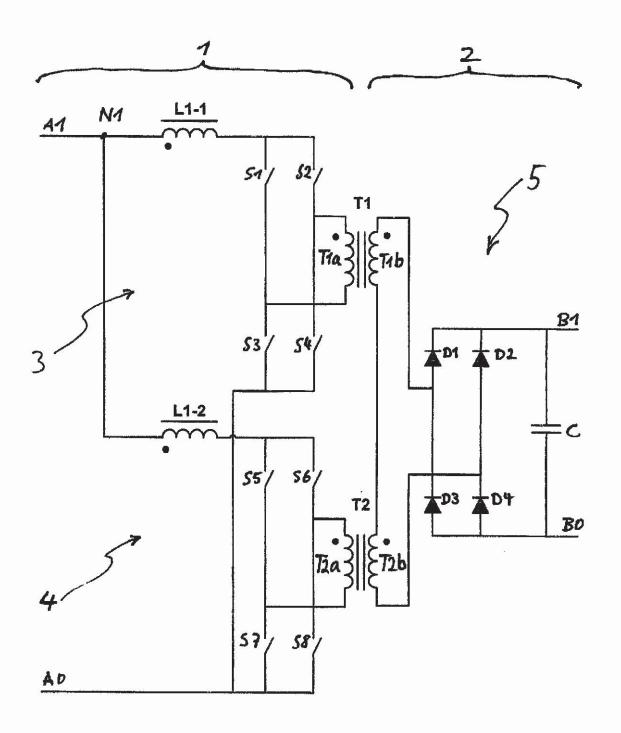

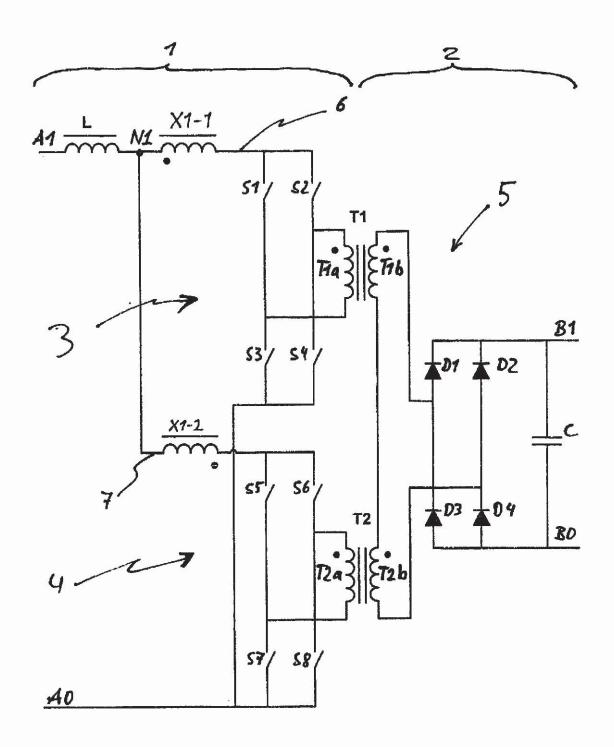

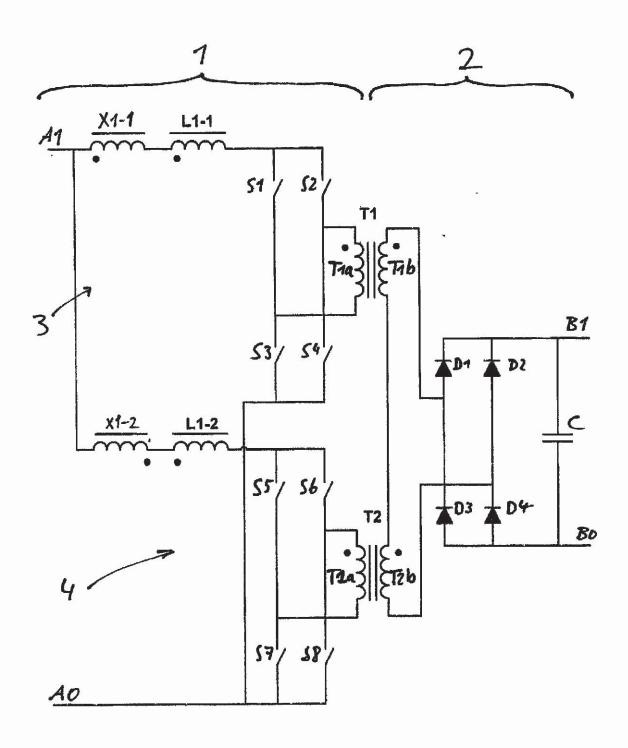

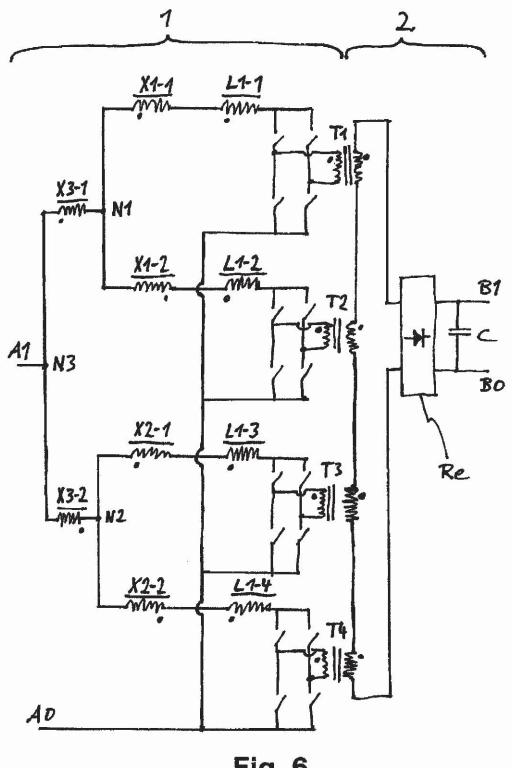

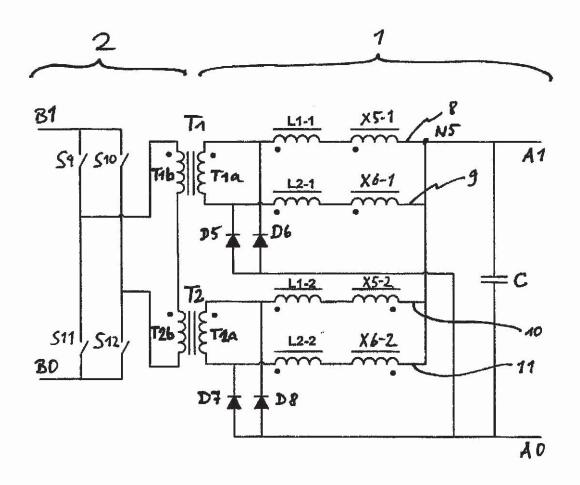

A schematic of the isolated full-bridge boost converter is presented in fig. 6. Timing diagram with basic operating waveforms is presented in fig. 7.

Output rectifier configuration is a voltage doubler, effectively saving two rectifier diodes and reducing transformer turns ratio by a factor of two at the expense of larger output capacitors. The input capacitor,  $C_{in}$ , effectively removes the residual input ripple current i.e. the inductor ripple current,  $\Delta i_{L1}$ .

#### 3.2.1.1 Basic isolated boost converter operation

Primary switches, S1-S4, are hard switched and operated in pairs, S1-S2 and S3-S4 respectively. Drive signals are 180 degree phase shifted. Switch transistor duty cycle, D, is above 50 percent to ensure switch overlap and thus a continuous current path for the inductor, L1, current.

Basic converter operation can be divided into four main states, T<sub>1</sub>-T<sub>4</sub>.

Fig. 6. Isolated full-bridge boost converter with voltage doubler.

Fig. 7. Timing diagram and basic waveforms for isolated full-bridge boost converter.

#### State 1, First inductor charging period, $T_1$ :

A first inductor charging period, T<sub>1</sub>, starts when switches, S1-S2, are turned on. All switches, S1-S4, are on and the inductor current, i<sub>L1</sub>, is increasing. The inductor current is shared between the two parallel branches, S1-S4 and S3-S2. Both rectifier diodes, D1-D2, are off and current in the transformer secondary winding is zero. The small transformer magnetizing current circulates in the transformer primary winding through switches, S2-S4 and/or S1-S3. Output capacitors, C1 and C2, supply the load current. The period ends when primary switches, S3 and S4, are turned off. The duration of the inductor charging period is

$$T_1 = D_L T_L = \left(D - \frac{1}{2}\right) T \tag{2}$$

Where the inductor duty cycle, D<sub>L</sub>, and inductor period time, T<sub>L</sub>, is defined as

$$D_L \equiv 2D - 1 \tag{3}$$

And

$$T_L \equiv \frac{T}{2} \tag{4}$$

#### State 2, First energy transfer period, T<sub>2</sub>:

A first energy transfer period,  $T_2$ , starts when switches, S3 and S4, are turned off. Inductor current,  $i_{L1}$ , flows through primary switch, S1, transformer, T1, rectifier diode, D1, and output capacitor, C1, and returns to input through primary switch S2. Inductor current,  $i_{L1}$ , discharges. The period ends when primary switches, S3 and S4, are turned on again. The duration of the energy transfer period is

$$T_2 = (1 - D)T. (5)$$

#### State 3, Second inductor charging period, T<sub>3</sub>:

A second inductor charging period,  $T_3$ , similar to the first is initiated when switches, S3 and S4 are turned on. Only minor difference from the first inductor charging period is that transformer magnetizing current is flowing in the opposite direction in the transformer primary winding. The period ends when switches, S1 and S2, are turned off. Period time is equal to the first inductor charging period,  $T_3 = T_1$ .

#### State 4, Second energy transfer period, T<sub>4</sub>:

Finally, a second energy transfer cycle,  $T_4$ , starts when switches, S1 and S2, are turned off. Inductor current  $i_{L1}$ , flows through switch, S3, transformer, T1 (in opposite direction compared with first energy transfer period), rectifier diode, D2, and output capacitor,, C2, and returns to input through primary switch, S4. The period ends when switches, S1 and S2, are turned on again. Period is equal to the first energy transfer period time,  $T_4 = T_2$ .

Total converter period time is the sum of the four state period times, T<sub>1</sub>-T<sub>4</sub>.

$$T = T_1 + T_2 + T_3 + T_4 \tag{6}$$

The ideal lossless converter transfer function in continuous steady state is:

$$\frac{V_o}{V_{in}} = \frac{n}{1 - D} \tag{7}$$

Where transformer turns ratio is defined as the ratio of secondary winding turn number to primary winding turn number.

$$n \equiv \frac{N_S}{N_P} \tag{8}$$

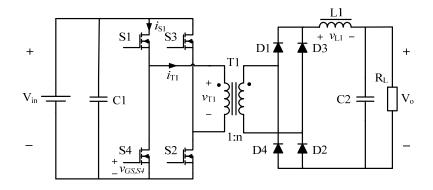

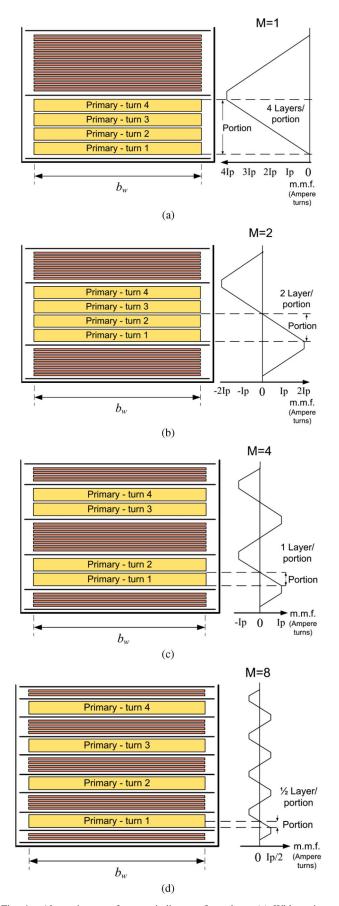

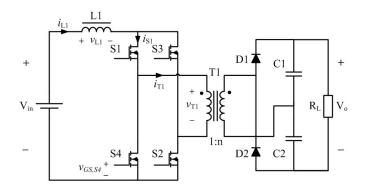

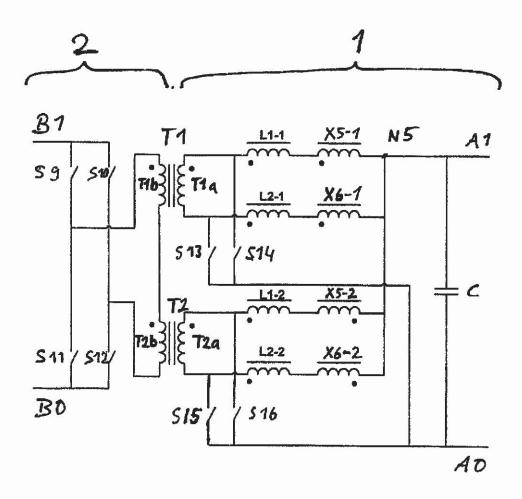

### 3.2.2 Isolated Full-Bridge Buck Converter

A schematic of the isolated full-bridge buck converter is presented in fig. 8. (Same as fig. 5, but repeated here for convenience). Timing diagram with basic operating waveforms are presented in fig. 9.

To minimize the voltage on output rectifiers as much as possible, a full-wave full-bridge rectifier consisting of D1-D4 is used. Since buck type converters have large discontinuous input currents, a large input ripple filter, represented by C1, is required to reduce input ripple current to acceptable levels.

#### 3.2.2.1 Basic isolated buck converter operation

Primary switches, S1-S4, are hard switched and operated in pairs, S1-S2 and S3-S4 respectively. Drive signals are 180 degree phase shifted. Switch transistor duty cycle, D, is below 50 percent to avoid switch overlap and thus short circuit of input.

Basic converter operation can be divided into four main states.

#### State 1, First on-period, $T_1$ :

A first converter on-period, T<sub>1</sub>, starts when switches, S1-S2, are turned on. Switches, S3-S4, and diodes, D3-D4, are off. Reflected inductor current flows from input capacitor, C1, through switch, S1, transformer, T1, diode, D1, and inductor, L1 to the output, and returns to input through diode, D2, and switch, S2. The period ends when switches, S1 and S2, are turned off again. Duration of the on-period is

$$T_1 = DT. (9)$$

#### **State 2, First off-period, T<sub>2</sub>:**

A first converter off-period,  $T_2$ , starts when switches, S1 and S2, are turned off. All primary switches are off. Inductor current,  $i_{L1}$ , is free-wheeling through the two parallel branches, D1-D4 and D3-D2, to output. Inductor current is discharging. Transformer magnetizing current circulates in the transformer secondary winding and the diodes, D1-D3 and/or D2-D4. The period ends when switches, S3 and S4 are turned on.

#### State 3, Second on-period, T<sub>3</sub>:

A second on-period similar to the first is initiated when switches, S3 and S4,, are turned on. Reflected inductor current flows from input capacitor, C1, through switch,, S3, transformer, T1, (in opposite direction compared to first on-period) diode, D3, and inductor, L1, to the output. Current returns to input through diode, D4, and switch, S4. The period ends when switches, S3 and S4, are turned off again. Period time is equal to the first on-period,  $T_3 = T_1$ .

Fig. 8. Isolated full-bridge buck converter.

Fig. 9. Timing diagram and basic waveforms for isolated full-bridge buck converter.

#### State 4, Second off-period, T<sub>4</sub>:

Finally, a second off-period starts when switches, S3 and S4, are turned off. All primary switches are off. Inductor current,  $i_{L1}$ , is free-wheeling through the two parallel branches, D1-D4 and D3-D2, to output. Inductor current is discharging. Transformer magnetizing current circulates in the transformer secondary winding (in opposite direction to first off-period) and the diodes, D1-D3 and/or D2-D4. The period ends when switches, S1 and S2, are turned on. Period time is equal to the first off-period time,  $T_4 = T_2$ . Duration of the off-period is

$$T_2 = \left(\frac{1}{2} - D\right)T. \tag{10}$$

Total converter period time is the sum of the four state period times  $T_1$ - $T_4$ , and given by (6).

The ideal lossless converter transfer function in continuous steady state is:

$$\frac{V_o}{V_{in}} = 2nD \tag{11}$$

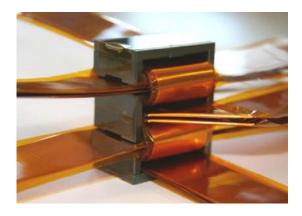

# 3.3 Transformer Design for High-Power Low-Voltage Converters

Transformer design for high power converters with high voltage gain is basically not different from designing any other high frequency power transformers. However, there seems to be a widespread misconception that high transformer turns ratio, as required in high gain applications, will result in large transformer leakage inductance [24], [33], [35], [42].

This assumption of large transformer leakage inductance due to high turns ratio has led to the proposal of numerous new topologies and techniques to deal with the supposedly high transformer leakage inductance. Proposed techniques include regenerative voltage clamp circuits [14], [15] and active clamp and transformer reset circuits [5], [9], [10], [12], [15], [22]-[24], [26], [27] as well as new topologies with lower transformer turns ratio such as the three phase V6 topology [33]-[37], [42].

However, as will be explained in section 3.3.1 below, the real issue in designing high frequency power transformers with high current windings is to avoid high winding ac-resistance due to severe proximity effect.

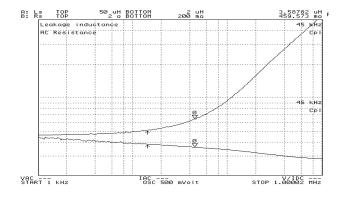

An analysis of transformer leakage inductance, in section 3.3.2, shows that not only does transformer leakage inductance not depend on transformer turns ratio, but that the extensive interleaving of primary and secondary windings needed to reduce proximity effect will dramatically reduce transformer leakage energy.

Finally, as the leakage inductance referenced to a particular winding is proportional to the number of turns squared, the very few primary turns needed on the low voltage primary winding will yield extremely small primary side leakage inductance.

The widespread acceptance that a high power transformer for low input voltage, having high turns ratio, will have high leakage inductance, is simply not correct.

### 3.3.1 Proximity Effect in Low-Voltage High-Power Transformers

High input current in high power fuel cell converters requires large wire copper cross section area in transformer primary windings.

Foil windings are very efficient in providing large copper cross section areas with a minimum conductor thickness. However, as power levels increase, even foil winding thicknesses quickly approach or exceed penetration depths in copper. Proximity effect can thereby cause very significant increases in winding ac-resistances thus leading to significantly increased power losses [43], [44].

In principle, Litz wire could be used. However, the very large copper cross section and few turns required on transformer primary side, make use of Litz wire difficult and impractical. Furthermore, due to the large number of individually insulated strands in Litz wires, copper space-factor is much lower than in solid copper foil windings leading to increased dc-resistance.

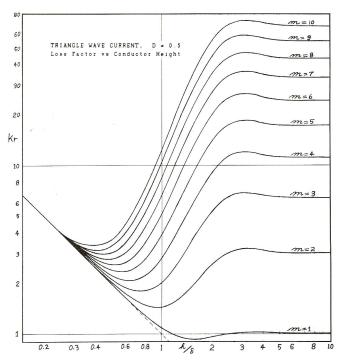

Using the work of Dowel [43] and Hurley [45], the increase in winding ac-resistance,  $R_{ac}$ , relative to winding dc-resistance,  $R_{dc}$ , at a specific frequency i.e. with sinusoidal excitation, due to eddy current effect is

$$F_R = \frac{R_{ac}}{R_{dc}} = \varphi \frac{\sinh 2\varphi + \sin 2\varphi}{\cosh 2\varphi - \cos 2\varphi}.$$

(12)

For single layer windings  $\varphi = h/\delta$ , and for half layer windings  $\varphi = h/2\delta$ .

In multi layer windings (m > 1) an additional term covering the proximity effect is added, thus the resistance factor becomes

$$F_R = \frac{R_{ac}}{R_{dc}} = \varphi \frac{\sinh 2\varphi + \sin 2\varphi}{\cosh 2\varphi - \cos 2\varphi} + \frac{2(m^2 - 1)}{3} \varphi \frac{\sinh \varphi - \sin \varphi}{\cosh \varphi + \cos \varphi}.$$

(13)

Where  $\varphi = h/\delta$ .

Since number of turns and winding thickness are different on primary and secondary windings  $(n \neq 1)$ , ac-resistance factors have to be calculated separately for primary,  $F_{R,P}$ , and secondary,  $F_{R,S}$ , windings. The combined effective ac-resistance for the transformer can be found as the weighted sum of the primary and secondary factors. If primary and secondary windings occupy equal winding spaces, the weighting factor becomes 0.5.

$$F_{R,T} = \frac{F_{R,P} + F_{R,S}}{2} \tag{14}$$

### 3.3.2 Leakage Inductance in Low-Voltage High-Power Transformers

Again, using the work of Dowel [43] and Snelling [44], an analytical expression of the transformer low frequency leakage inductance can be derived. This analytical expression is very useful in fully understanding the impact of transformer turns ratio and winding technique on transformer leakage inductance.

Stored energy in a magnetic volume,  $V_e$  is

$$w = V_e \int_0^{\Delta B} H \, dB \tag{15}$$

Where flux density of free space is  $B = \mu_0 H$ .

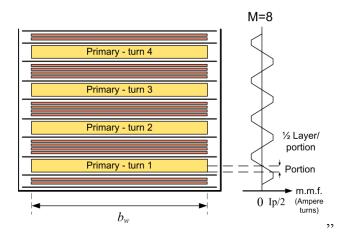

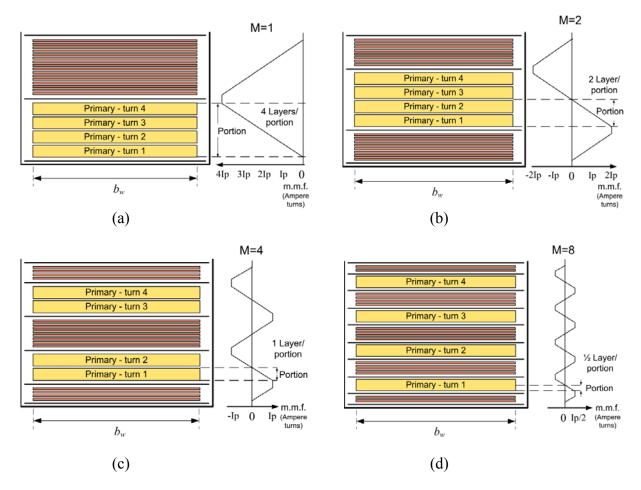

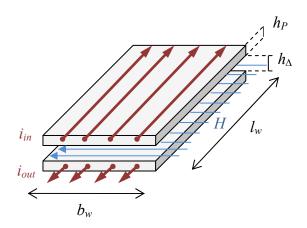

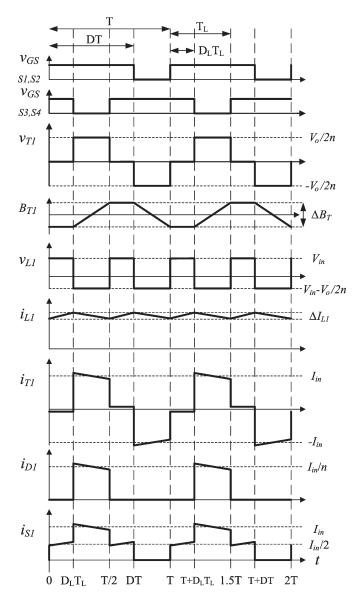

The transformer windings can be grouped into a number of winding portions and intersections according to their magnetomotive force (m.m.f.) diagram as presented in fig. 10. Winding intersections constituting small volumes,  $V_{\perp} = l_w b_w h_{\perp}$ , of constantly high magnetic field strength H. Portions being volumes,  $V_P = l_w b_w h_P$ , of winding space where magnetic field strength, H, is increasing linearly from zero to maximum.

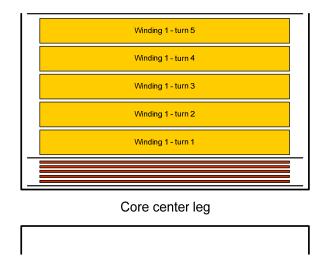

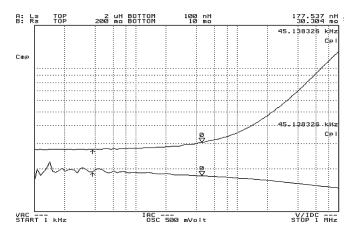

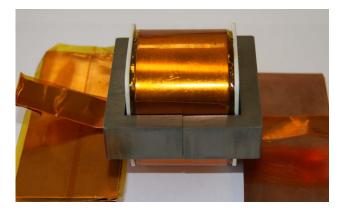

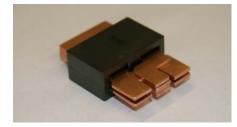

Fig. 10. Transformer winding configuration with 8 intersections, 16 portions and ½ layer primary winding.

To find the stored energy in each volume element, we integrate magnetic field strength squared,  $H^2$ , over the height of the volume element

$$w(V_P) = \frac{1}{2} \mu_0 l_w b_w \int_0^{h_P} H(x)^2 dx.$$

(16)

Where x, is the distance from the zero crossing of the magnetic field strength, H, (and m.m.f.) and is defined in the range  $0 \le x \le h_P$ .

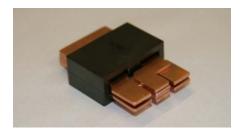

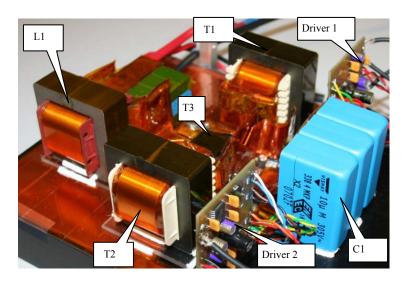

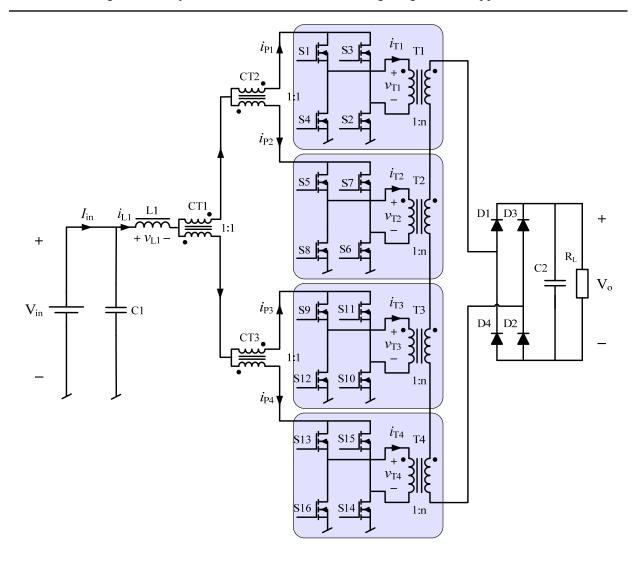

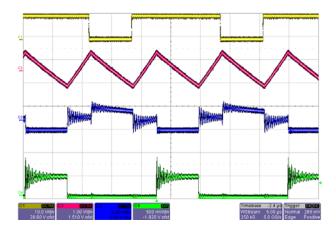

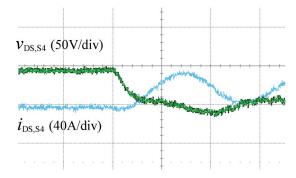

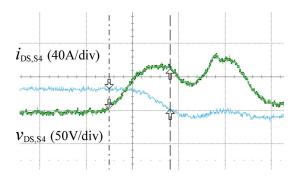

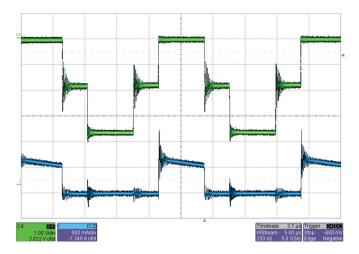

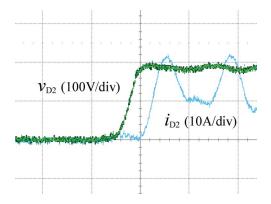

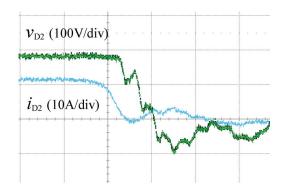

Knowing the shape of the magnetic field strength as presented in each of the winding configuration drawings fig. 11, we can calculate the stored energy.